Изобретение относится к контрольно-измерительной и вычислительной технике и может быть использовано для контроля электрических (статических и динамических) па- .раметров и функционирования цифровых логических больших интегральных схем (БИС) в частности схем с эмиттерно-связанной логикой.

Целью изобретения является повышение точности контроля.

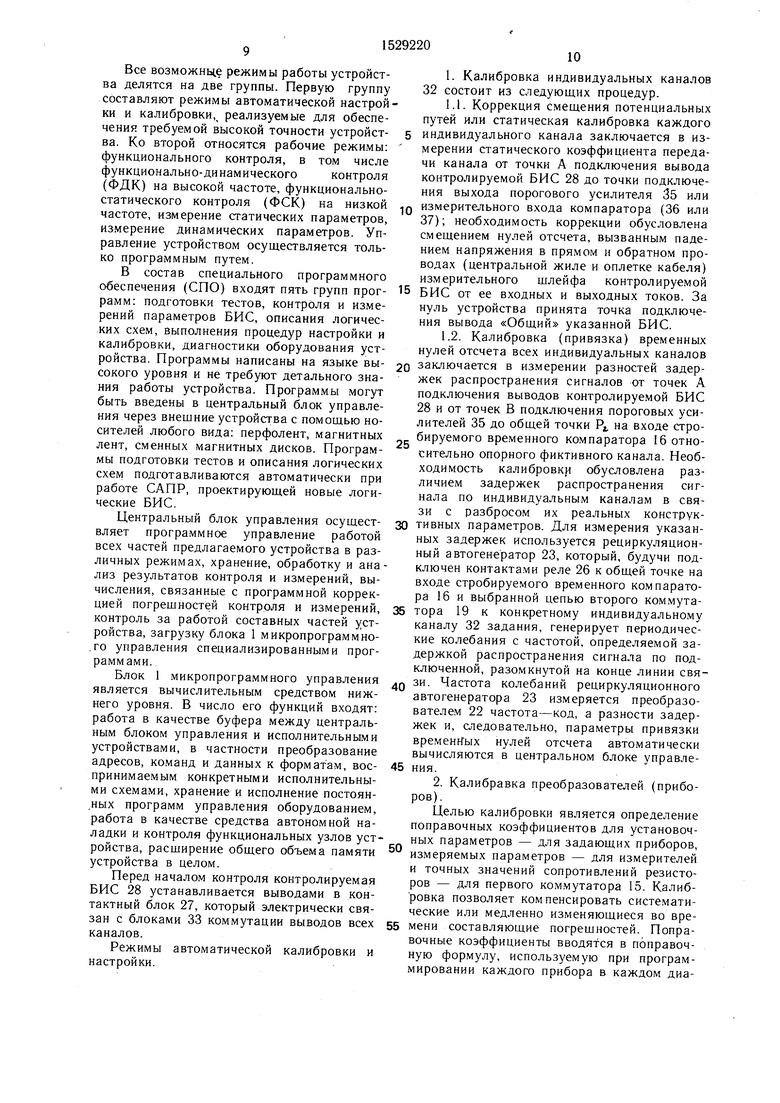

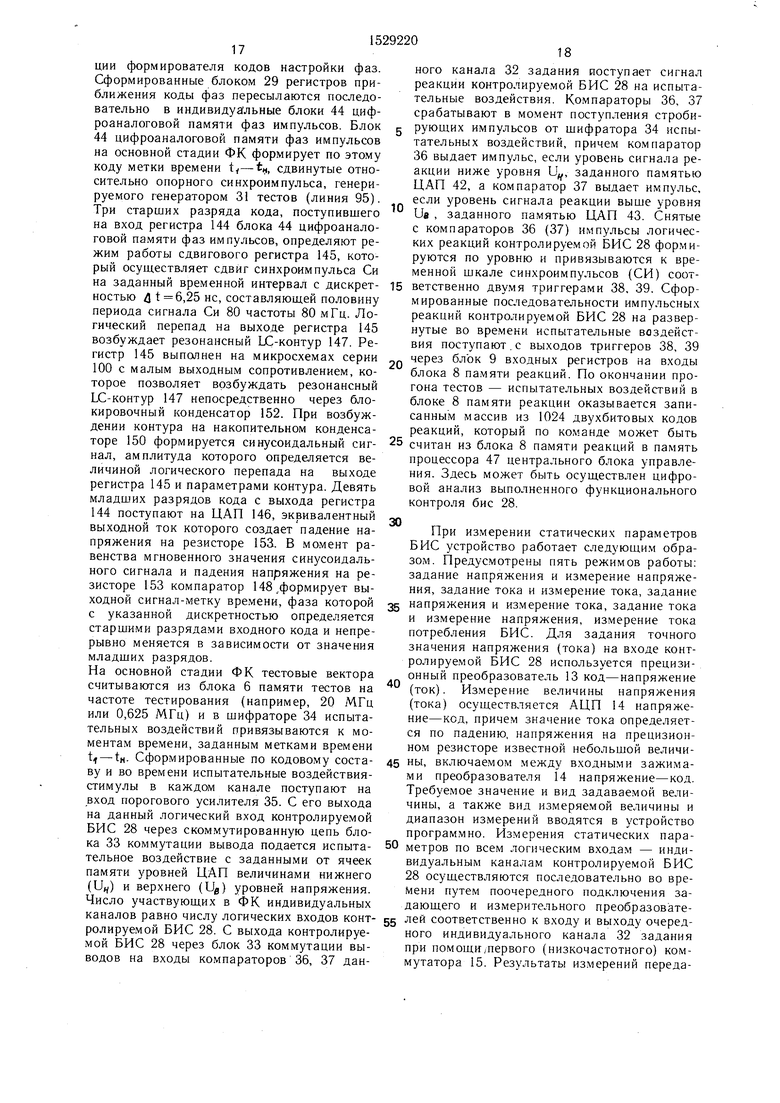

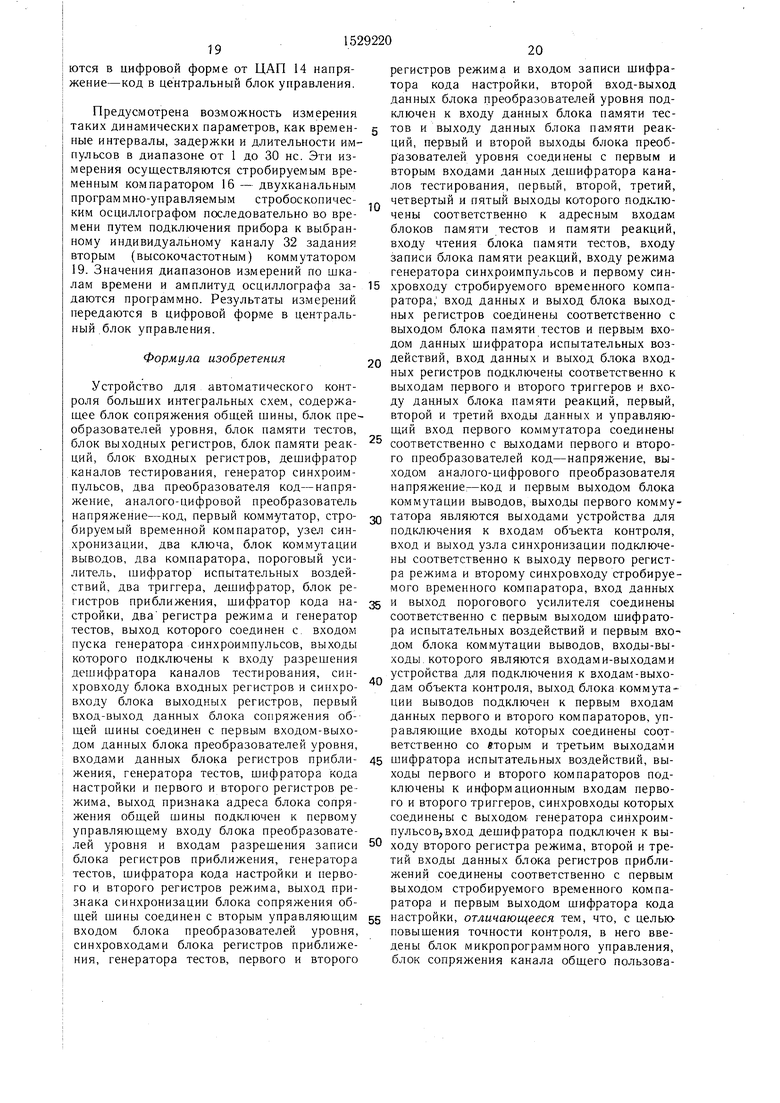

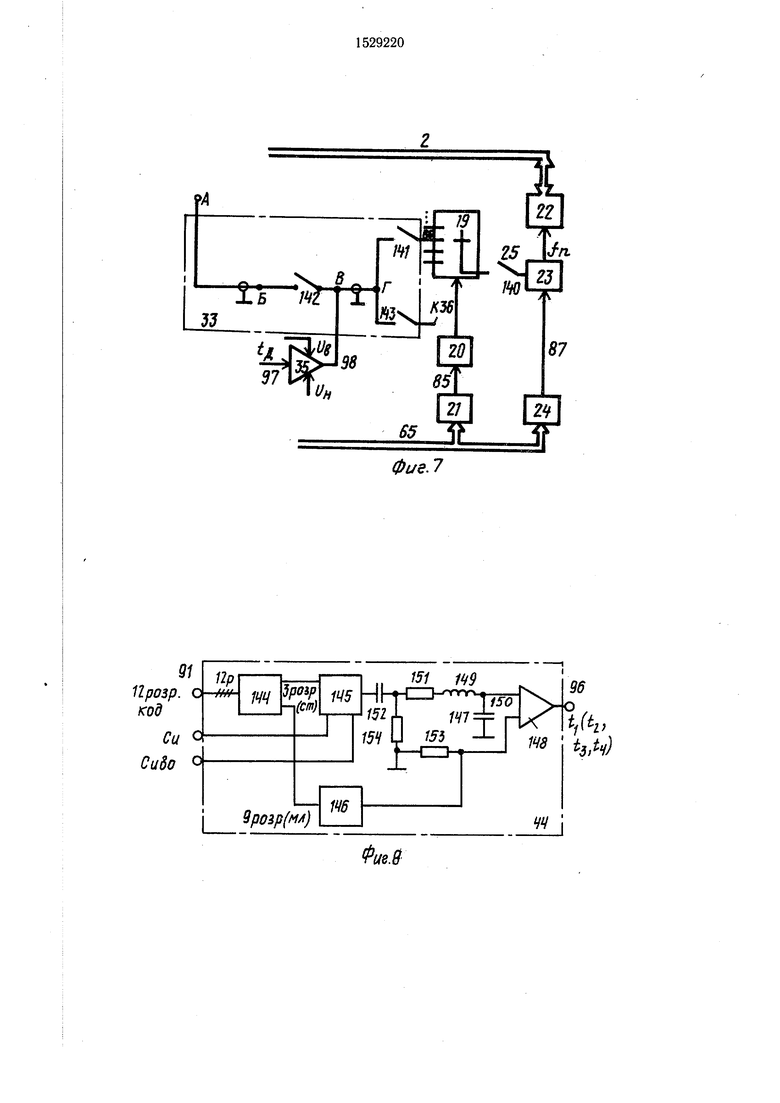

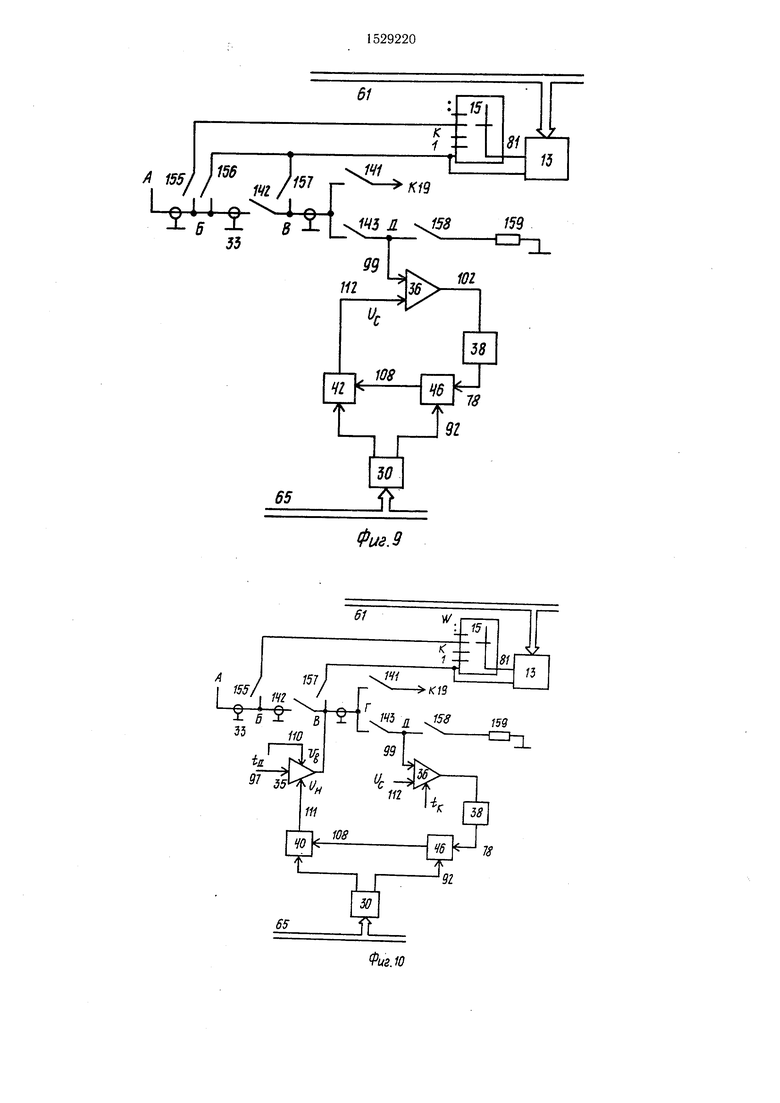

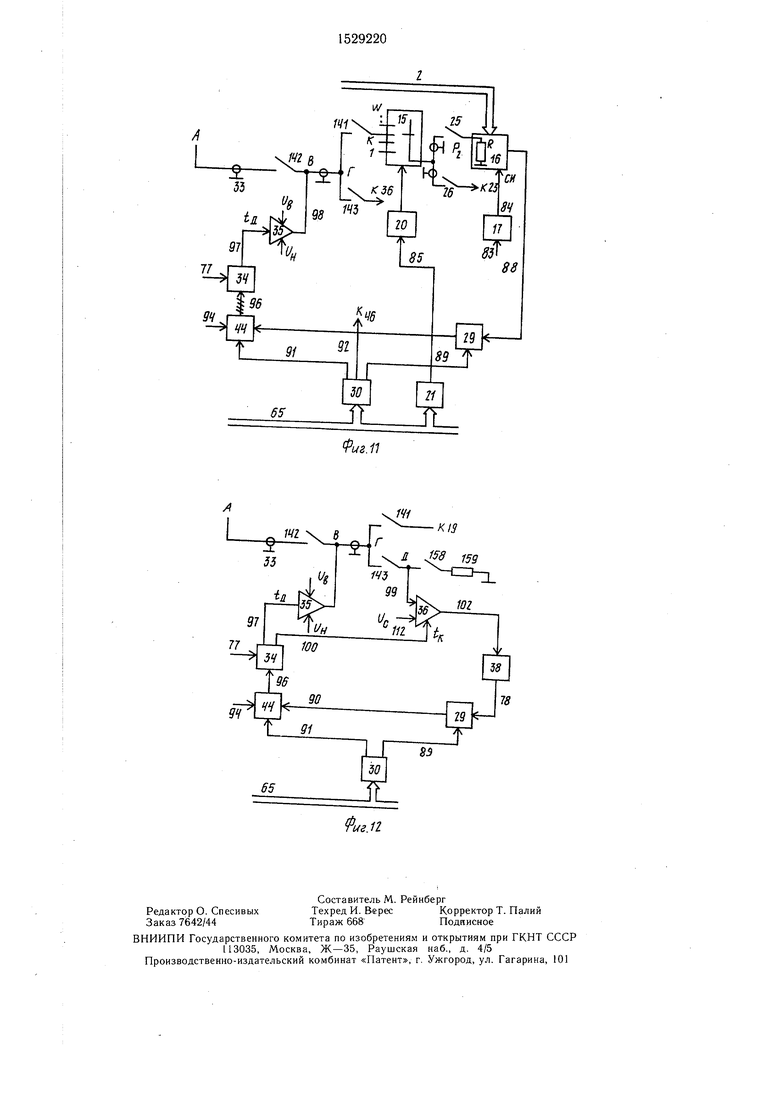

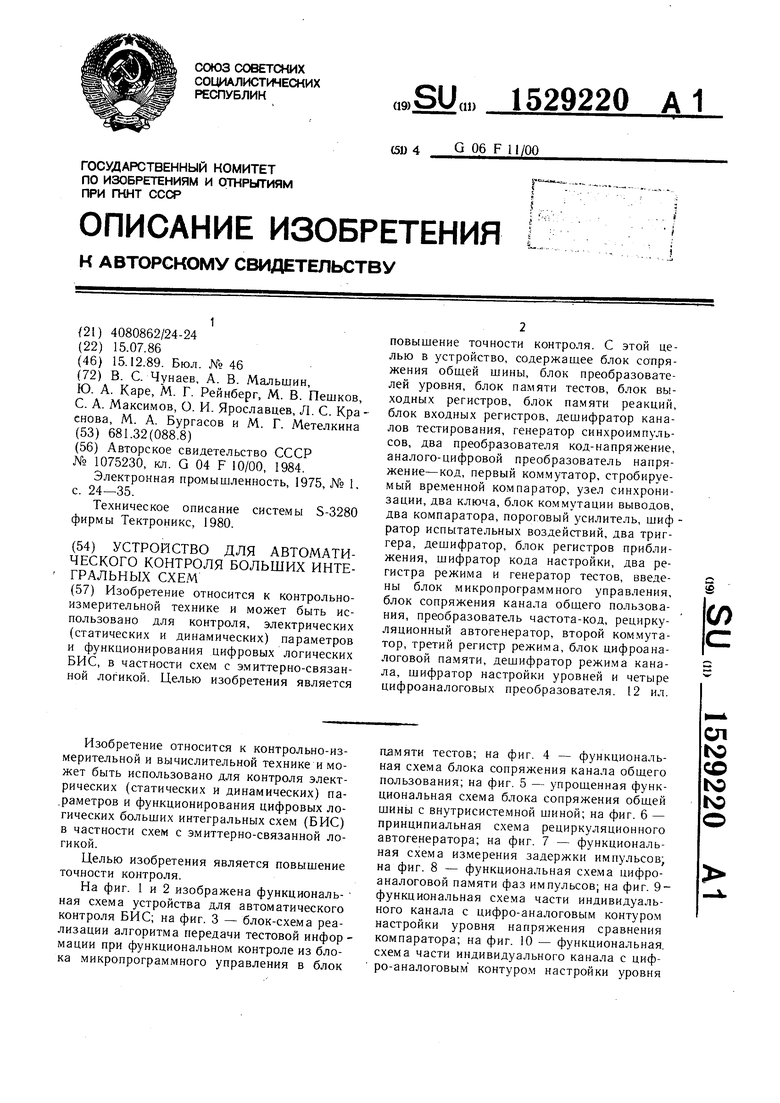

На фиг. 1 и 2 изображена функциональная схема устройства для автоматического контроля БИС; на фиг. 3 - блок-схема реализации алгоритма передачи тестовой инфор мации при функциональном контроле из блока микропрограммного управления в блок

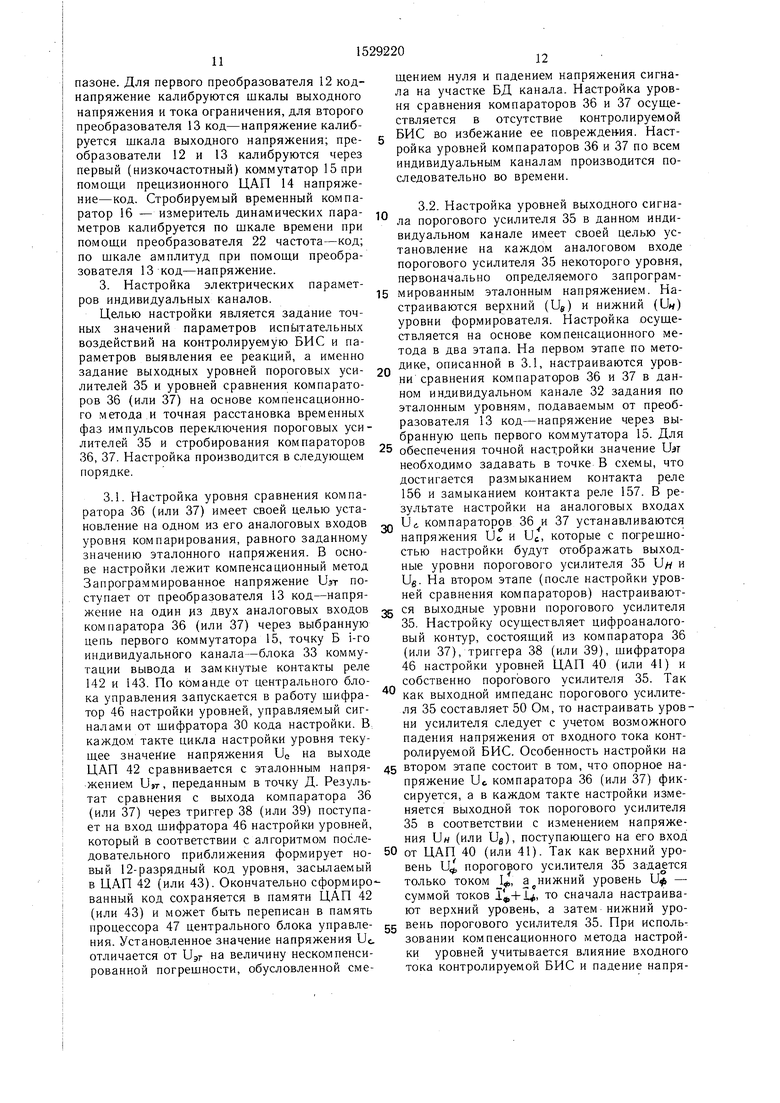

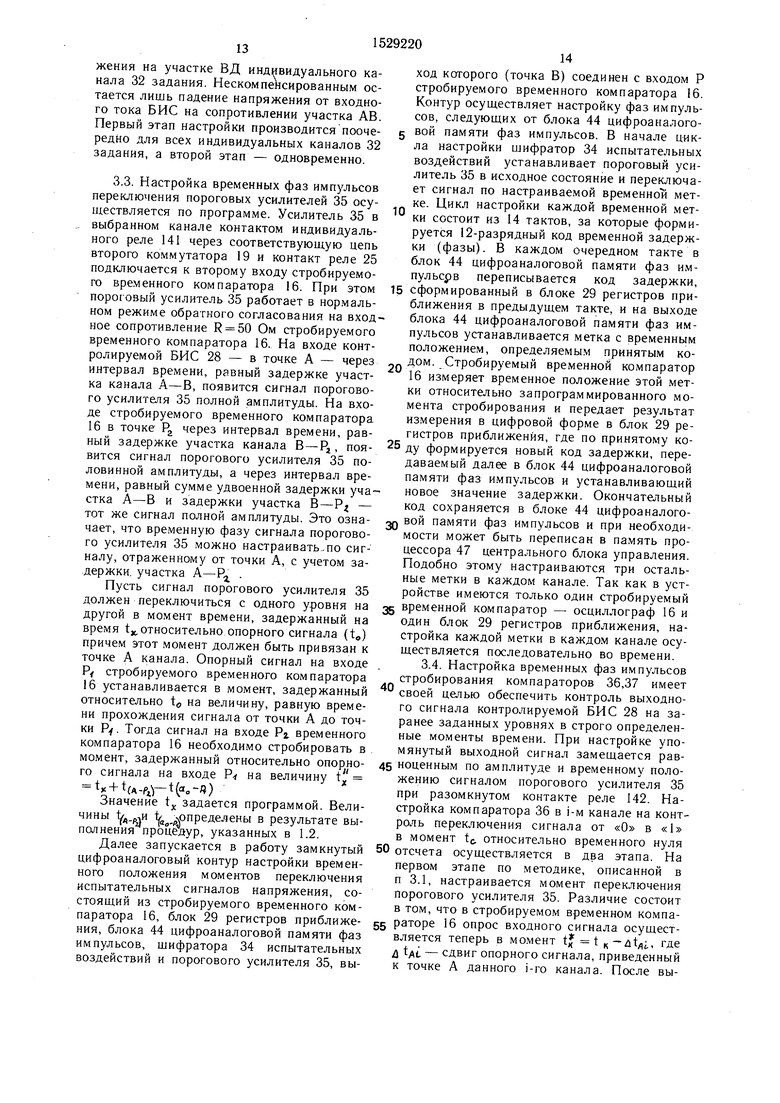

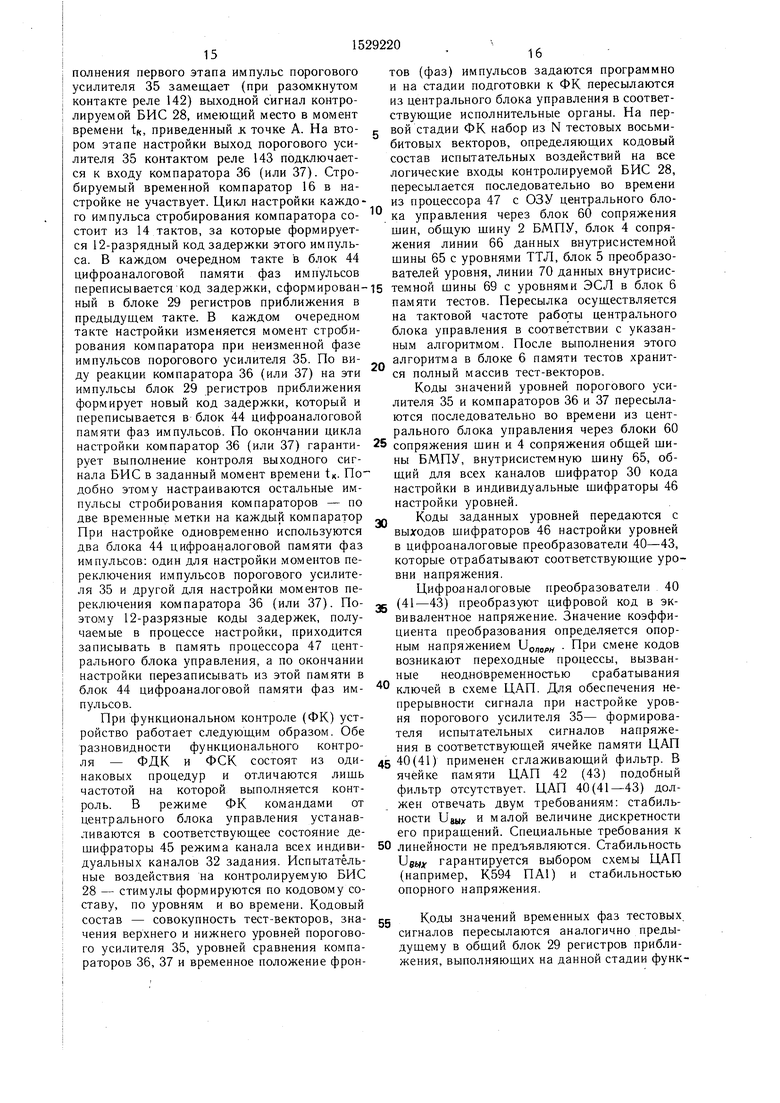

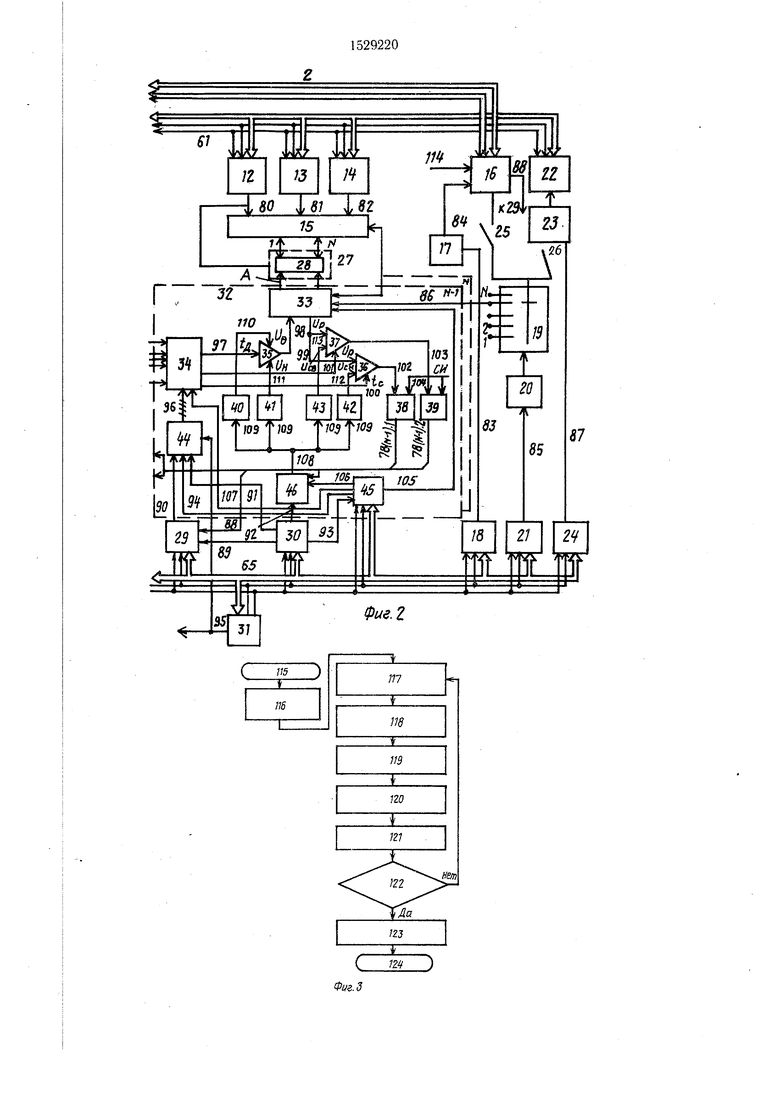

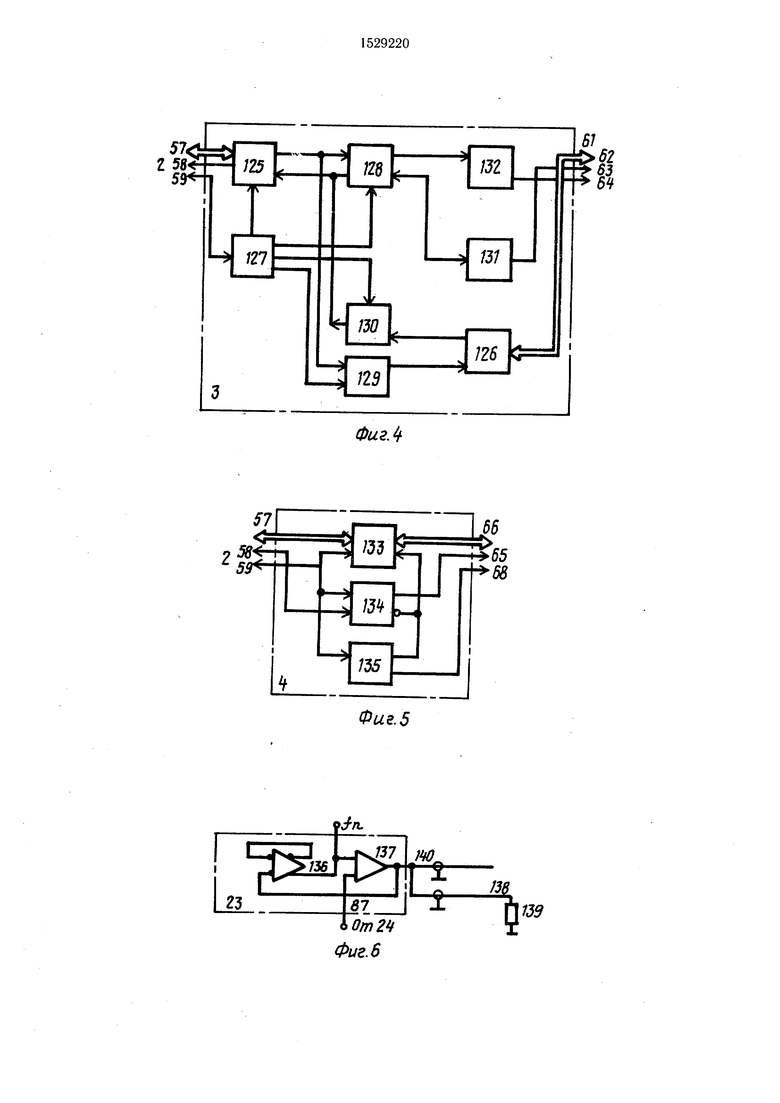

памяти тестов; на фиг. 4 - функциональная схема блока сопряжения канала общего пользования; на фиг. 5 - упрощенная функциональная схема блока сопряжения общей шины с внутрисистемной шиной; на фиг. 6 - принципиальная схема рециркуляционного автогенератора; на фиг. 7 - функциональная схема измерения задержки импульсов; на фиг. 8 - функциональная схема цифро- аналоговой памяти фаз импульсов; на фиг. 9- функциональная схема части индивидуального канала с цифро-аналоговым контуром настройки уровня напряжения сравнения компаратора; на фиг. 10 - функциональная, схема части индивидуального канала с цифро-аналоговым контуро.м настройки уровня

СЛ tsD

со

Ю

to

|на выходе порогового усилителя; на фиг. 11- : функциональная схема части индивидуально- : го канала с цифро-аналоговым контуром настройки моментов переключения импульсов порогового усилителя; на фиг. 12 - 1 функциональная схема части индивидуаль- : ного канала с цифроаналоговым контуром i настройки моментов опроса выходного.сигнала контролируемой БИС компаратором.

Устройство содержит (фиг. 1 и 2) блок 1 микропрограммного управления (БМПУ) с интерфейсом 2 типа общая шина БМПУ, блок 3 сопряжения канала общего пользования, блок 4 сопряжения общей щины БМПУ, блок 5 преобразователей уровня, блок 6 памяти тестов, блок 7 выходных регистров, блок 8 памяти реакций, блок 9 входных регистров, дешифратор 10 канала тестирования, генератор 11 синхроимпульсов, первый и второй преобразователи 12 и 13 код- напряжение, аналого-цифровой преобразователь (АЦП) 14 напряжение-код, первый (низкочастотный) коммутатор 15, стробируе- мый временной компаратор 16, узел 17 синхронизации компаратора, первый регистр 18 режима, связанный с узлом 17 синхронизации, второй (высокочастотный) коммутатор 19, дешифратор 20, второй регистр 21 режима, преобразователь 22 частота-код, рециркуляционный автогенератор 23, третий регистр 24 режима, связанный с рециркуляционным автогенератором 23, два ре.ле 25 и 26, блок 27 контактный для подключения контролируемой большой интегральной схемы (БИС) 28, блок 29 регистров приближения, шифратор 30 кода настройки и гене- ратор 31 тестов.

Кроме того, устройство содержит индивидуальные каналы 32 задания испытательных воздействий и измерения реакций, число ко- торых равно N, причем каждый канал 32 содержит блок 33 коммутации вывода, шиф- ратор 34 испытательных воздействий, поро- говый усилитель 35, первый и второй компа- раторы 36 и 37, первый и второй триггеры 38 и 39, четыре цифроаналоговых преобра- зователя (ЦАП) 40-43, блок 44 цифро аналоговой памяти фаз импульсов, дешифратор 45 режима канала и шифратор 46 настройки уровней.

Устройство подключено к центральному блоку управления, в качестве которого может быть использована малая ЭВМ, напри-, мер ЭВМ модели «Электроника 100-25 или СМ-1420. Центральный блок управления состоит из процессора 47 с оперативным за- поминаюшим устройством (ОЗУ) и периферийных устройств - накопителя 48 на магнитных дисках, накопителя 49 на магнитной ленте, печатающего устройства 50, блока 51 интерфейсного и электронно-лучевых дисплеев 52. Связь периферийных устройств и аппаратуры устройства с процессом ЭВМ

осуществляется по двунаправленной магистрали 53 типа общей шины, содержащей линии 54-56 данных, адреса и управления соответственно.

Связь между блоком 1 микропрограммного управления и внешними по отношению к нему устройствами осуществляется по двунаправленной магистрали 2 типа общей шины БМПУ, которая содержит шестнадцать линий 57 данных, шестнадцать линий 58 ад реса и двадцать пять линий 59 управления и синхронизации. Двусторонняя связь между обшей шиной 53 центрального блока управления и общей шиной 2 блока. 1 микропрограммного управления осушествляется через

блок 60 сопряжения шин, который преобразует форматы информационных посылок и синхронизирует работу передающего и переменного устройств. К магистрали 2 «Общая шина БМПУ, кроме того, подключены

первые входы-выходы блока 3 сопряжения канала 61 общего пользования (КОП), состоящего из двунаправленных линий 62-64 данных, адреса и управления соответственно входы-выходы данных, признака адреса и управления соответственно входы-выходы дан5 ных, признака адреса и управления строби- руемого временного компаратора 16, первые входы-выходы блока 4 сопряжения с двунаправленной внутрисистемной шиной 65, имеющей уровни ТТЛ.

К двунаправленным линиям 62-64 ка- нала общего пользования 61 подключены входы данных двух преобразователей 12 и 13 код-напряжение, цифровые входы-выходы АЦП 14 напряжение-код и преобразователя 22 частота-код. К линиям 66-68

g данных, адреса и синхронизации двунаправленной внутрисистемной шины 65 с уровнями ТТЛ подсоединены соответствующие первые входы-выходы блока 5 преобразователей уровня, входы данных, адреса и син- хровходы шифратора 30 кода настройки, ге нератора 31 тестов, регистров 18, 21 и 24 режима, аналогичные первые входы блока 29 регистров приближения и дешифратора 45 режима канала.

Вторые входы-выходы блока 5 преоб5 разователей уровня (ТТЛ/ЭСЛ и ЭСЛ/ТТЛ) подключены к двунаправленной внутрисистемной шине 69 с уровнями ЭСЛ, которая содержит линии 70-72 данных, адреса и управления. Линии 70 данных шины 69 соединены с соответствующими входами блока

0 6 памяти тестов и выходами блока 8 памяти реакций. Линии 71 и 72 адреса и управления подключены к соответствующим входам дешифратора 10 каналов тестирования. Разрешающий вход дешифратора 10 соединен с

g выходом генератора 11 синхроимпульсов. Выход дешифратора 10 линией 73.1 связан с управляющими входами блока 6 памяти тестов и блока 8 памяти реакций, линией

73.2 - с входам команды «Чтение блока 6 памяти тестов, а линией 73.3 - с входом команды «Запись блока 8 памяти реакций. Выходы данных блока 6 памяти тестов индирому управляющему входу блока 29 регистров приближения.

Выход блока 29 регистров приближения четырьмя линиями связан с первыми входавидуальными линиями 74у.-74у,;, .;., 74дг - 5 ми данных блоков 44 цифроаналоговой па74 ; связаны с соответствующими входами 75 блока 7 выходных регистров. Выходы 76 блока 7 линиями 77у;у .t - /v; соединены с индивидуальнь1ми вход ами данных шифраторов 34 испытательных воздействий всех индивидуальных каналов 32 задания испытательных воздействий и приема реакций, число которых равно N (первым индексом от I до N обозначен номер канала, вторым индексом от 1 до 8 - номер цифрового входа данного канала).

10

мяти фаз импульсов всех каналов. Второй - четвертый выходы шифратора 30 кода настройки подключены соответственно к вторым входам данных блоков 44 цифро анало- говой памяти фаз импульсов, входам данных шифраторов 46 настройки уровней и дешифраторов 45 режима канала во всех каналах (через линии 90-93).

Между функциональными элементами 15 каждого индивидуального канала 32 задания испытательных воздействий и измерения реакций имеются следующие связи. Третий вход блока 44 цифроаналоговой памяти фаз импульсов линией 94 соединен с выходом

щими в ходами блока 9 входных регистров, Q дешифратора 45 режима канала. Четвертый

вход блока 44 цифроаналоговой памяти фаз

Выходы триггеров 38 и 39 каждого индивидуального канала линиями 78.,/-78, , соединены с соответствуюа выходы последнего линиями 79 -.ь - .i .i связаны с соответствующими входами блока 8 памяти реакций.

Первый - третий входы данных первого коммутатора 15 линиями 80-82 соединены соответственно с выходами первого и второго преобразователей 12 и 13 код-напряжение, входом АЦП 14 напряжение-код, а выходы первого коммутатора 15 с первого по N-й являются входами блока 27 контакт25

импульсов линией 95 соединен с выходом генератора 31 тестов, который связан также с входом генератора 11 синхроимпульсов. Четыре раздетьных выхода блока 44 цифроана- логоБОЙ памяти фаз импульсов соединены линиями 96 с соответствующими четырьмя входами щифратора 34 испытательных воздействий. Вход данных и выход порогового усилителя 35 линиями 97 и 98 соединены соимпульсов линией 95 соединен с выходом генератора 31 тестов, который связан также с входом генератора 11 синхроимпульсов. Четыре раздетьных выхода блока 44 цифроана логоБОЙ памяти фаз импульсов соединены линиями 96 с соответствующими четырьмя входами щифратора 34 испытательных воздействий. Вход данных и выход порогового усилителя 35 линиями 97 и 98 соединены соного для подключения контролируемой БИС до ответственно с первым выходом щифратора

28. Кроме того, выход первого преобразователя 12 код-напряжение соединен с. входом питания блока 27 контактного.

Выход первого регистра 18 режима линией 83 соединен с входом узла 17 синхронизации, выход которого через линию 84 подключен к синхровходу стробируемого временного компаратора 16. Выход второго регистра 21 режима линие й 85 соединен с входом данных дешифратора 20, выход которого подключен к управляющему входу коммутатора 19, общий информационный вход которого через контакты первого и второго реле 25 и 26 соединен с первыми выходами соответственно стробируемого временного ком35

40

34 испытательных воздействий и первым входом блока 33 коммутации вывода, входы- выходы которого являются входами-выходами блока 27 контактного для подключения контролируемой БИС 28. Выход блока 33 коммутации вывода подключен через линию 99 к входам данных первого и второго компараторов 36 и 37, входы для стробирующих сигналов которых линиями 100 и 101 соединены соответственно с вторым и третьим выходами щифратора 34 испытательных воздействий. Выходы первого и второго компараторов 36 и 37 линиями 102 и 103 подключены к информационным- входам первого и второго триггеров 38 и 39, синхровходы которых линией 104 соединены с выходом гепаратора 16 и рециркуляционного генерато- 45 нератора 11 синхроимпульсов. Выходы дера 23. Каждый индивидуальный выход с первого по N-й второго коммутатора 19 через линию 86 подключен к второму входу блока 33 коммутации вывода соответствующего канала. В-ыход третьего регистра 24 режима линией 87 соединен с управляющим входом рециркуляционного генератора 23, второй выход которого подключен к входу преобразователя 22 частота-код. Второй выход стробируемого временного компаратора 16 линией 88 соединен с вторым управляющим входом блока 29 регистров приближения. Первый выход шифратора 30 кода настройки через линию 89 подключен к втощифратора 45 режима канала с первого по четвертый соединены соответственно с третьим входом блока 33 коммутации вывода (через линию 105), вторым входом шифратора 46 настройки уровней (через линию

106), управляющи.м входом шифратора 34 испытательных воздействий (через линию 107). Выход шифратора 46 настройки уровней линией 108 соединен с цифровыми входами 109 первого - четвертого ЦАП 40-43,

55 выходы которого подключены соответственно к первому и второ.му управляющим входам порогового усилителя 35 (через линии 110 и 11) и вторым входам данных первого и

рому управляющему входу блока 29 регистров приближения.

Выход блока 29 регистров приближения четырьмя линиями связан с первыми входа ми данных блоков 44 цифроаналоговой пами данных блоков 44 цифроаналоговой па

мяти фаз импульсов всех каналов. Второй - четвертый выходы шифратора 30 кода настройки подключены соответственно к вторым входам данных блоков 44 цифро анало- говой памяти фаз импульсов, входам данных шифраторов 46 настройки уровней и дешифраторов 45 режима канала во всех каналах (через линии 90-93).

25

импульсов линией 95 соединен с выходом генератора 31 тестов, который связан также с входом генератора 11 синхроимпульсов. Четыре раздетьных выхода блока 44 цифроана- логоБОЙ памяти фаз импульсов соединены линиями 96 с соответствующими четырьмя входами щифратора 34 испытательных воздействий. Вход данных и выход порогового усилителя 35 линиями 97 и 98 соединены содо ответственно с первым выходом щифратора

до ответственно с первым выходом щифратора

35

40

34 испытательных воздействий и первым входом блока 33 коммутации вывода, входы- выходы которого являются входами-выходами блока 27 контактного для подключения контролируемой БИС 28. Выход блока 33 коммутации вывода подключен через линию 99 к входам данных первого и второго компараторов 36 и 37, входы для стробирующих сигналов которых линиями 100 и 101 соединены соответственно с вторым и третьим выходами щифратора 34 испытательных воздействий. Выходы первого и второго компараторов 36 и 37 линиями 102 и 103 подключены к информационным- входам первого и второго триггеров 38 и 39, синхровходы которых линией 104 соединены с выходом гещифратора 45 режима канала с первого по четвертый соединены соответственно с третьим входом блока 33 коммутации вывода (через линию 105), вторым входом шифратора 46 настройки уровней (через линию

106), управляющи.м входом шифратора 34 испытательных воздействий (через линию 107). Выход шифратора 46 настройки уровней линией 108 соединен с цифровыми входами 109 первого - четвертого ЦАП 40-43,

55 выходы которого подключены соответственно к первому и второ.му управляющим входам порогового усилителя 35 (через линии 110 и 11) и вторым входам данных первого и

второго компараторов 36 и 37 (через линии 112 и 113).

Дешифратор 10 канала тестирования че- рез линию 114 подключен к второму входу данных стробируемого временного компаратора 16. Блок 1 микропрограммного управления может быть выполнен, например, на секционированном микропроцессорном наборе серии 585 ТТЛ-типа с диодами Шоттки. Алгоритм работы блока (фиг. 3) содержит программные блоки 115-124 соответ- ственнб вхождения в программу, записи «lis в программный счетчик числа каналов, блока выбора режима для первого индивидуального канала, записи в ЦАП 40 и 41 кодов уровней «О и «1 порогового усилителя 35 и в ЦАП 42 и 43 кодов уровней сравнения компараторов 36 и 37, записи в блок 44 цифроаналоговой памяти фаз импульсов кодов временных меток для порогового усилителя 35 и компараторов 36 и 37, записи форматов тестовых сигналов первого канала в блок 6 памяти тестов, добавления «1 к числу, хранящемуся в программное счетчике числа каналов, сравнения содержимого счетчика 116 с максимальным чис.,1ом каналов, например N-96, выхода из цикла и запуска параллельной передачи тестовой информации в индивидуальные каналы 32 задания.

Блок 3 сопряжения канала общего поль- I зования. содержит (фиг. 4) два двунаправ- I ленных буферных регистра 125 и 126 дан- I ных, дешифратор 127 адреса, регистры 128- 130 команд и состояний шифратор 131 управления каналом, узел 132 синхронизации. Блок 4 сопряжения общей щины БМПУ содержит (фиг. 5) буферные регистры 133- 135 данных, адреса и сигналов управления I соответственно.

j Рециркуляционный автогенератор 23 со- I держит (фиг. 6) широкополосный усилитель 136 (У1) с, симметричной передаточной характеристикой, выполненный на мик- j росхеме 597СА1, и широкополосный инвер- I тирующий усилитель 137 (У2) с выходо.м, I выполненным по схеме генератора тока. Ши- ; рокополосный инвертирующий усилитель 137 : охвачен местной положительной обратной связью, обеспечивающей получение релей- ной передаточной характеристики. Обратная ; связь с выхода усилителя 137 на вход щи- ; рокополосного усилителя 136 обеспечивает : генерацию зондирующих импульсов. Частота : колебаний автогенератора, работающего че- : рез отрезок линии 138 связи на согласующий : резистор 139, определяется удвоенной вели- i чиной задержки в разомкнутой линии 140 связи, конец которой находится либо в точке А при замкнутом контакте реле либо в точке В при разомкнутом контакте этого реле. Измерение разности задержек двух линий связи физически одинаковой длины осуществляется с пикосекундной точностью. Рециркуляционный автогенератор 23 предназначен для определения реальных величин задержек сигналов в индивидуальных каналах 32 задания для последующего вычисления значений их разностей, используемых при автокоррекции погрешностей измерения динамических параметров БИС. Рециркуляционный генератор 23 в соответствии с функциональной схемой измерения задержки импульса подключается (фиг. 7), к линии связи выбранного канала через контакт реле 26, выбранную по программе цепь второго коммутатора 19 и контакты реле 141 и 142 при разомкнутом контакте реле 143, отключаю- ш,ем канал от первого коммутатора 15 и преобразователя 13 код-напряжение.

Блок 44 цифроаналоговой памяти фаз импульсов (фиг. 8) может быть выполнен в виде схемы, которая содержит 12-разрядный Q запоминающий регистр 144, трехразрядный сдвиговый регистр 145, девятиразрядный ЦАП 146, резонансный LC-контур 147 и компаратор 148. Резонансный контур 147, в свою очередь, содержит индуктивность 149, накопительный конденсатор 150, токоограничи- тельный резистор 151. Конденсатор 152 является блокировочным. Кроме того, в состав блока 44 входят резисторы 153 и 154.

На функциональных схемах частей индивидуального канала (фиг. 9-12) показа- 0 ны дополнительно контакты 155-158 реле (ключей) и резистор 159.

ЦАП 40 (41-43), являющийся памятью уровня напряжения, может быть выполнен в виде 12-разрядного устройства для запоминания текущего цифрового кода уровня, 5 связанного с ним цифровыми входами 12- разрядного ЦАП и выходного сглаживающего фильтра. В качестве устройства для запоминания уровней порогового усилителя 35 может быть использован реверсивный счетчик, а в аналогичных ЦАП 42 и 43 для запоминания уровней сравнения компараторов 36 и 37 может быть использован регистр.

Первый преобразователь 12 код-напряжение может быть выполнен в виде стандартного программируемого источника пи- 5 тания Б5-46.

Второй преобразователь 13 код-напряжение может быть выполнен в виде стандартного прецизионного источника напряжения Б6-8.

АЦП 14 напряжение-код может быть 0 выполнен в виде универсального программируемого цифрового вольтметра В7-34.

В качестве стробируемого временного

компаратора 16 может быть использован

двухканальный цифровой стробоскопичес5 кий осциллограф «Синтез (система осцил.лографическая 1019).

Устройство работает следующим образом.

0

Все возможные режимы работы устройства делятся на две группы. Первую группу составляют режимы автоматической настройки и калибровки,, реализуемые для обеспечения требуемой высокой точности устройства. Ко второй относятся рабочие режимы: функционального контроля, в том числе функционально-динамического контроля (ФДК) на высокой частоте, функционально- статического контроля (ФСК) на низкой частоте, измерение статических параметров, измерение динамических параметров. Управление устройством осуществляется только программным путем.

В состав специального программного обеспечения (СПО) входят пять групп программ: подготовки тестов, контроля и измерений параметров БИС, описания логических схем, выполнения процедур настройки и калибровки, диагностики оборудования устройства. Программы написаны на языке высокого уровня и не требуют детального знания работы устройства. Программы могут быть введены в центральный блок управления через внешние устройства с помощью носителей любого вида: перфолент, магнитных лент, сменных магнитных дисков. Программы подготовки тестов и описания логических схем подготавливаются автоматически при работе САПР, проектирующей новые логические БИС.

Центральный блок управления осуществляет программное управление работой всех частей предлагаемого устройства в различных режимах, хранение, обработку и анализ результатов контроля и измерений, вычисления, связанные с программной коррекцией погрешностей контроля и измерений, контроль за работой составных частей устройства, загрузку блока 1 микропрограммно- то управления специализированными программами. .

Блок 1 микропрограммного управления является вычислительным средством нижнего уровня. В число его функций входят: работа в качестве буфера между центральным блоком управления и исполнительными устройствами, в частности преобразование адресов, команд и данных к форматам, воспринимаемым конкретными исполнительными схемами, хранение и исполнение постоян- ,ных программ управления оборудованием, работа в качестве средства автономной наладки и контроля функциональных узлов устройства, расширение общего объема памяти устройства в целом.

Перед началом контроля контролируемая БИС 28 устанавливается выводами в контактный блок 27, который электрически связан с блоками 33 коммутации выводов всех каналов.

Режимы автоматической калибровки и настройки.

5

1.Калибровка индивидуальных каналов 32 состоит из следующих процедур.

1.1.Коррекция смещения потенциальных путей или статическая калибровка каждого

индивидуального канала заключается в измерении статического коэффициента передачи канала от точки А подключения вывода контролируемой БИС 28 до точки подключения выхода порогового усилителя 35 или

Q измерительного входа компаратора (36 или 37); необходимость коррекции обусловлена смещением нулей отсчета, вызванным падением напряжения в прямом и обратном проводах (центральной жиле и оплетке кабеля) измерительного шлейфа контролируемой

5 БИС от ее входных и выходных токов. За нуль устройства принята точка подключения вывода «Общий указанной БИС.

1.2.Калибровка (привязка) временных нулей отсчета всех индивидуальных каналов

0 заключается в измерении разностей задержек распространения сигналов от точек А подключения выводов контролируемой БИС 28 и от точек В подключения пороговых усилителей 35 до общей точки Р, на входе стро- бируемого временного компаратора 16 относительно опорного фиктивного канала. Необходимость калибровки обусловлена различием задержек распространения сигнала по индивидуальным каналам в связи с разбросом их реальных конструк0 тивных параметров. Для измерения указанных задержек используется рециркуляционный автогенератор 23, который, будучи подключен контактами реле 26 к общей точке на входе стробируемого временного ко.мпарато- ра 16 и выбранной цепью второго коммута5 тора 19 к конкретному индивидуальному каналу 32 задания, генерирует периодические колебания с частотой, определяемой задержкой распространения сигнала по подключенной, разомкнутой на конце линии свяQ зи. Частота колебаний рециркуляционного автогенератора 23 измеряется преобразователем 22 частота-код, а разности задержек и, следовательно, параметры привязки временН ых нулей отсчета автоматически вычисляются в центральном блоке управле5 ния.

2.Калибравка преобразователей (приборов).

Целью калибровки является определение поправочных коэффициентов для установочных параметров - для задающих приборов, измеряемых параметров - для измерителей и точных значений сопротивлений резисторов - для первого коммутатора 15. Калибровка позволяет компенсировать систематические или медленно из.меняющиеся во вре- 5 мени составляющие погрешностей. Поправочные коэффициенты вводятся в поправочную формулу, используемую при программировании каждого прибора в каждом диа0

пазоне. Для первого преобразователя 12 код- напряжение калибруются шкалы выходного напряжения и тока ограничения, для второго преобразователя 13 код-напряжение калибруется шкала выходного напряжения; преобразователи 12 и 13 калибруются через первый (низкочастотный) коммутатор 15 при помощи прецизионного ЦАП 14 напряжение-код. Стробируемый временный компаратор 16 - измеритель динамических параметров калибруется по шкале времени при помош,и преобразователя 22 частота-код; по шкале амплитуд при помош,и преобразователя 13 код-напряжение.

3. Настройка электрических параметров индивидуальных каналов.

Целью настройки является задание точных значений параметров испЬ1тательных воздействий на контролируемую БИС и параметров выявления ее реакций, а именно задание выходных уровней пороговых усилителей 35 и уровней сравнения компараторов 36 (или 37) на основе компенсационного метода и точная расстановка временных фаз импульсов переключения пороговых усилителей 35 и стробирования компараторов 36, 37. Настройка производится в следующем порядке.

3.1. Настройка уровня сравнения компаратора 36 (или 37) имеет своей целью установление на одном из его аналоговых входов уровня ком парирования, равного заданному значению эталонного напряжения. В основе настройки лежит компенсационный метод Запрограммированное напряжение Уэт поступает от преобразователя 13 код-напряжение на один из двух аналоговых входов компаратора 36 (или 37) через выбранную цепь первого коммутатора 15, точку Б i-ro индивидуального канала-блока 33 коммутации вывода и замкнутые контакты реле 142 и 143. По команде от центрального блока управления запускается в работу шифратор 46 настройки уровней, управляемый сигналами от шифратора 30 кода настройки. В каждом такте цикла настройки уровня текущее значение напряжения Uo на выходе ЦАП 42 сравнивается с эталонным напряжением UjT, переданным в точку Д. Результат сравнения с выхода компаратора 36 (или 37) через триггер 38 (или 39) поступает на вход шифратора 46 настройки уровней, который в соответствии с алгоритмом последовательного приближения формирует новый 12-разрядный код уровня, засылаемый в ЦАП 42 (или 43). Окончательно сформированный код сохраняется в памяти ЦАП 42 (или 43) и может быть переписан в память процессора 47 центрального блока управления. Установленное значение напряжения Uc. отличается от на величину нескомпенсированной погрешности, обусловленной сме0

щением нуля и падением напряжения сигнала на участке БД канала. Настройка уровня сравнения компараторов 36 и 37 осуществляется в отсутствие контролируемой БИС во избежание ее поврежден-ия. Настройка уровней компараторов 36 и 37 по всем индивидуальным каналам производится последовательно во времени.

3.2. Настройка уровней выходного сигна- ла порогового усилителя 35 в данном индивидуальном канале имеет своей целью установление на каждом аналоговом входе порогового усилителя 35 некоторого уровня, первоначально определяемого запрограммированным эталонным напряжением. Настраиваются верхний (Ug) и нижний (Ум) уровни формирователя. Настройка осуществляется на основе компенсационного метода в два этапа. На первом этапе по методике, описанной в 3., настраиваются уровни сравнения компараторов 36 и 37 в данном индивидуальном канале 32 задания по эталонным уровням, подаваемым от преобразователя 13 код-напряжение через выбранную цепь первого коммутатора 15. Для

5 обеспечения точной настройки значение U.JT необходимо задавать в точке В схемы, что достигается размыканием контакта реле 156 и замыканием контакта реле 157. В результате настройки на аналоговых входах

Q Uu компараторов 36 и 37 устанавливаются напряжения Uc и Uc, которые с погрещно- стью настройки будут отображать выходные уровни порогового усилителя 35 U/y и Ug. На втором этапе (после настройки уровней сравнения компараторов) настраивают5 ся выходные уровни порогового усилителя 35. Настройку осуществляет цифроаналого- вый контур, состоящий из компаратора 36 (или 37), триггера 38 (или 39), шифратора 46 настройки уровней ЦАП 40 (или 41) и собственно порогового усилителя 35. Так как выходной импеданс порогового усилителя 35 составляет 50 Ом, то настраивать уровни усилителя следует с учетом возможного падения напряжения от входного тока контролируемой БИС. Особенность настройки на

5 втором этапе состоит в том, что опорное напряжение Uc компаратора 36 (или 37) фиксируется, а в каждом такте настройки изменяется выходной ток порогового усилителя 35 в соответствии с изменением напряжения UH (или Ug), поступающего на его вход

0 от ЦАП 40 (или 41). Так как верхний уровень и порогового усилителя 35 задается только током 1, а нижний уровень U - суммой токов 1ф+1, то сначала настраивают верхний уровень, а затем нижний уро5 вень порогового усилителя 35. При использовании компенсационного метода настройки уровней учитывается влияние входного тока контролируемой БИС и падение напря0

жения на участке ВД индивидуального канала 32 задания. Нескомпенсированным остается лишь падение напряжения от входного тока БИС на сопротивлении участка АВ. Первый этап настройки производится поочередно для всех индивидуальных каналов 32 задания, а второй этап - одновременно.

3.3. Настройка временных фаз импульсов переключения пороговых усилителей 35 осуществляется по программе. Усилитель 35 в выбранном канале контактом индивидуального реле 141 через соответствующую цепь второго коммутатора 19 и контакт реле 25 подключается к второму входу стробируемо- го временного компаратора 16. При этом пороговый усилитель 35 работает в нормальном режиме обратного согласования на входное сопротивление R 50 Ом стробируемого временного компаратора 16. На входе контролируемой БИС 28 - в точке А - через интервал времени, равный задержке участка канала А-В, появится сигнал порогового усилителя 35 полной амплитуды. На входе стробируемого временного компаратора 16 в точке РЗ через интервал времени, равный задержке участка канала В-Р, появится сигнал порогового усилителя 35 половинной амплитуды, а через интервал времени, равный сумме удвоенной задержки участка А-В и задержки участка В-Р - тот же сигнал полной амплитуды. Это означает, что временную фазу сигнала порогового усилителя 35 можно настраивать-по сигналу, отраженному от точки А, с учетом задержки, участка А-Р, .

Пусть сигнал порогового усилителя 35 должен переключиться с одного уровня на другой в момент времени, задержанный на время 1,.относительно опорного сигнала (to) причем этот момент должен быть привязан к точке А канала. Опорный сигнал на входе PY стробируемого временного компаратора 16 устанавливается в момент, задержанный относительно t, на величину, равную времени прохождения сигнала от точки А до точки Ру. Тогда сигнал на входе Р временного компаратора 16 необходимо стробировать в момент, задержанный относительно опорного сигнала на входе Р на величину tj tx + t((a,-;))

Значение tj. задается программой. Величины ti-a в .допределены в результате выполнения процедур, указанных в 1.2.

Далее запускается в работу замкнутый цифроаналоговый контур настройки временного положения моментов переключения испытательных сигналов напряжения, состоящий из стробируемого временного компаратора 16, блок 29 регистров приближения, блока 44 цифроаналоговой памяти фаз импульсов, шифратора 34 испытательных воздействий и порогового усилителя 35, вы0

ход которого (точка В) соединен с входом Р стробируемого временного компаратора 16. Контур осуществляет настройку фаз импульсов, следующих от блока 44 цифроаналого- g вой памяти фаз импульсов. В начале цикла настройки шифратор 34 испытательных воздействий устанавливает пороговый усилитель 35 в исходное состояние и переключает сигнал по настраиваемой временной метке. Цикл настройки каждой временной метки состоит из 14 тактов, за которые формируется 12-разрядный код временной задержки (фазы). В каждом очередном такте в блок 44 цифроаналоговой памяти фаз им- пульсрв переписывается код задержки,

5 сформированный в блоке 29 регистров приближения в предыдущем такте, и на выходе блока 44 цифроаналоговой памяти фаз импульсов устанавливается метка с временным положением, определяемым принятым ко- дом. Стробируемый временной компаратор 16 измеряет временное положение этой метки относительно запрограммированного момента стробирования и передает результат измерения в цифровой форме в блок 29 регистров приближения, где по принятому коS ду формируется новый код задержки, передаваемый далее в блок 44 цифроаналоговой памяти фаз импульсов и устанавливающий новое значение задержки. Окончательный код сохраняется в блоке 44 цифроакалогоQ вой памяти фаз импульсов и при необходимости может быть переписан в память процессора 47 центрального блока управления. Подобно этому настраиваются три остальные метки в каждом канале. Так как в устройстве имеются только один стробируемый

g временной компаратор - осциллограф 16 и один блок 29 регистров приближения, настройка каждой метки в каждом канале осуществляется последовательно во времени.

3.4. Настройка временных фаз импульсов стробирования компараторов 36,37 имеет

0

своей целью обеспечить контроль выходного сигнала контролируемой БИС 28 на заранее заданных уровнях в строго определенные моменты времени. При настройке упомянутый выходной сигнал замещается рав5 ноценным по амплитуде и временному положению сигналом порогового усилителя 35 при разомкнутом контакте реле 142. Настройка компаратора 36 в i-м канале на контроль переключения сигнала от «О в «I в момент tc, относительно временного нуля

0 отсчета осуществляется в два этапа. На первом этапе по методике, описанной в п 3.1, настраивается момент переключения порогового усилителя 35. Различие состоит в том, что в стробируемом временном компа5 раторе 16 опрос входного сигнала осуществляется теперь в момент t t ,., где Л - сдвиг опорного сигнала, приведенный к точке А данного i-ro канала. После выполнения первого этапа импульс порогового усилителя 35 замещает (при разомкнутом контакте реле 142) выходной сигнал контролируемой БИС 28, имеющий место в момент времени 1к, приведенный к точке А. На втором этапе настройки выход порогового усилителя 35 контактом реле 143 подключается к входу компаратора 36 (или 37). Стро- бируемый временной компаратор 16 в настройке не участвует. Цикл настройки каждого импульса стробирования компаратора состоит из 14 тактов, за которые формируется 12-разрядный код задержки этого импульса. В каждом очередном такте в блок 44 цифроаналоговой памяти фаз импульсов переписывается код задержки, сформированный в блоке 29 регистров приближения в предыдущем такте. В каждом очередном такте настройки изменяется момент стробирования компаратора при неизменной фазе импульсов порогового усилителя 35. По виду реакции компаратора 36 (или 37) на эти импульсы блок 29 регистров приближения формирует новый код задержки, который и переписывается в блок 44 цифроаналоговой памяти фаз импульсов. По окончании цикла настройки компаратор 36 (или 37) гарантирует выполнение контроля выходного сигнала БИС в заданный момент времени tx. По добно этому настраиваются остальные импульсы стробирования компараторов - по две временные метки на каждый компаратор При настройке одновременно используются два блока 44 цифроаналоговой памяти фаз импульсов: один для настройки моментов переключения импульсов порогового усилителя 35 и другой для настройки моментов переключения компаратора 36 (или 37). Поэтому 12-разрязные коды задержек, получаемые в процессе настройки, приходится записывать в память процессора 47 центрального блока управления, а по окончании настройки перезаписывать из этой памяти в блок 44 цифроаналоговой памяти фаз импульсов.

При функциональном контроле (ФК) устройство работает следующим образом. Обе разновидности функционального контроля - ФДК и ФСК состоят из одинаковых процедур и отличаются лищь частотой на которой выполняется контроль. В режиме ФК командами от центрального блока управления устанавливаются в соответствующее состояние дешифраторы 45 режима канала всех индивидуальных каналов 32 задания. Испытательные воздействия на контролируемую БИС 28 - стимулы формируются по кодовому составу, по уровням и во времени. Кодовый состав - совокупность тест-векторов, значения верхнего и нижнего уровней порогового усилителя 35, уровней сравнения компараторов 36, 37 и временное положение фронтов (фаз) импульсов задаются программно и на стадии подготовки к ФК пересылаются из центрального блока управления в соответствующие исполнительные органы. На первой стадии ФК набор из N тестовых восьми- битовь1х векторов, определяющих кодовый состав испытательных воздействий на все логические входы контролируемой БИС 28, пересылается последовательно во времени из процессора 47 с ОЗУ центрального бло- ка управления через блок 60 сопряжения шин, общую щину 2 БМПУ, блок 4 сопряжения линии 66 данных внутрисистемной шины 65 с уровнями ТТЛ, блок 5 преобразователей уровня, линии 70 данных внутрисистемной щины 69 с уровнями ЭСЛ в блок 6 памяти тестов. Пересылка осуществляется на тактовой частоте работы центрального блока управления в соответствии с указанным алгоритмом. После выполнения этого

алгоритма в блоке 6 памяти тестов хранится полный массив тест-векторов.

Коды значений уровней порогового усилителя 35 и компараторов 36 и 37 пересылаются последовательно во времени из центрального блока управления через блоки 60

5 сопряжения шин и 4 сопряжения общей шины БМПУ, внутрисистемную шину 65, общий для всех каналов шифратор 30 кода настройки в индивидуальные шифраторы 46 настройки уровней.

Q Коды заданных уровней передаются с выходов шифраторов 46 настройки уровней в цифроаналоговые преобразователи 40-43, которые отрабатывают соответствующие уровни напряжения.

Цифроаналоговые преобразователи 40

g (41-43) преобразуют цифровой код в эквивалентное напряжение. Значение коэффициента преобразования определяется опорным напряжением опорн Р смене кодов возникают переходные процессы, вызванные неодновременностью срабатывания ключей в схеме ЦАП. Для обеспечения непрерывности сигнала при настройке уровня порогового усилителя 35- формирователя испытательных сигналов напряжения в соответствующей ячейке памяти ЦАП

540(41) применен сглаживающий фильтр. В ячейке памяти ЦАП 42 (43) подобный фильтр отсутствует. ЦАП 40(41-43) должен отвечать двум требованиям: стабильности UgKx и малой величине дискретности его приращений. Специальные требования к

0 линейности не предъявляются. Стабильность Ugkix гарантируется выбором схемы ЦАП (например, К594 ПА1) и стабильностью опорного напряжения.

5 Коды значений временных фаз тестовых, сигналов пересылаются аналогично предыдущему в общий блок 29 регистров приближения, выполняющих на данной стадии функции формирователя кодов настройки фаз. Сформированные блоком 29 регистров приближения коды фаз пересылаются последовательно в индивидуагльные блоки 44 циф- роаналоговой памяти фаз импульсов. Блок 44 цифроаналоговой памяти фаз импульсов на основной стадии ФК формирует по этому коду метки времени ty-t, сдвинутые отноного канала 32 задания поступает сигнал реакции контролируемой БИС 28 на испытательные воздействия. Компараторы 36, 37 срабатывают в момент поступления строби- g рующих импульсов от шифратора 34 испытательных воздействий, причем компаратор 36 выдает импульс, если уровень сигнала реакции ниже уровня и, заданного памятью ЦАП 42, а компаратор 37 выдает импульс, если уровень сигнала реакции выше уровня Ue , заданного памятью ЦАП 43. Снятые с компараторов 36 (37) импульсы логических реакций контролируемой БИС 28 формируются по уровню и привязываются к временной шкале синхроимпульсов (СИ) соот10

сительно опорного синхроимпульса, генерируемого генератором 31 тестов (линия 95). Три старших разряда кода, поступившего на вход регистра 144 блока 44 цифроаналоговой памяти фаз импульсов, определяют режим работы сдвигового регистра 145, который осуществляет сдвиг синхроимпульса Си на заданный временной интервал с дискрет- 15 ветственно двумя триггерами 38, 39. Сфор- ностью 4 t 6,25 НС, составляюш,ей половину мированные последовательности импульсных периода сигнала Си 80 частоты 80 мГц. Ло- реакций контролируемой БИС 28 на развер- гический перепад на выходе регистра 145 возбуждает резонансный ЬС-контур 147. Регистр 145 выполнен на микросхемах серии через блок 9 входных регистров на входы 100 с малым выходным сопротивлением, ко- блока 8 памяти реакций. По окончании прогона тестов - испытательных воздействий в блоке 8 памяти реакции оказывается записанным массив из 1024 двухбитовых кодов реакций, который по команде может быть

нутые во времени испытательные воздействия поступают, с выходов триггеров 38, 39

торое позволяет возбуждать резонансный ЬС-контур 147 непосредственно через блокировочный конденсатор 152. При возбуждении контура на накопительном конденсаторе 150 формируется синусоидальный сиг- 25 считан из блока 8 памяти реакций в память

нал, амплитуда которого определяется величиной логического перепада на выходе регистра 145 и параметрами контура. Девять младших разрядов кода с выхода регистра 144 поступают на ЦАП 146, эквивалентный выходной ток которого создает падение напряжения на резисторе 153. В момент равенства мгновенного значения синусоидального сигнала и падения напряжения на резисторе 153 компаратор 148 формирует вы30

процессора 47 центрального блока управления. Здесь мо.жет быть осушествлен цифровой анализ выполненного функционального контроля бис 28.

При из.мерении статических параметров БИС устройство работает следуюши.м образом. Предусмотрены пять режимов работы: задание напряжения и измерение напряжения, задание тока и измерение тока, задание

ходной сигнал-метку времени, фаза которой 35 напряжения и измерение тока, задание тока

ного канала 32 задания поступает сигнал реакции контролируемой БИС 28 на испытательные воздействия. Компараторы 36, 37 срабатывают в момент поступления строби- рующих импульсов от шифратора 34 испытательных воздействий, причем компаратор 36 выдает импульс, если уровень сигнала реакции ниже уровня и, заданного памятью ЦАП 42, а компаратор 37 выдает импульс, если уровень сигнала реакции выше уровня Ue , заданного памятью ЦАП 43. Снятые с компараторов 36 (37) импульсы логических реакций контролируемой БИС 28 формируются по уровню и привязываются к временной шкале синхроимпульсов (СИ) соот

ветственно двумя триггерами 38, 39. Сфор- мированные последовательности импульсных реакций контролируемой БИС 28 на развер- через блок 9 входных регистров на входы блока 8 памяти реакций. По окончании прогона тестов - испытательных воздействий в блоке 8 памяти реакции оказывается записанным массив из 1024 двухбитовых кодов реакций, который по команде может быть

ветственно двумя триггерами 38, 39. Сфор- мированные последовательности импульсных реакций контролируемой БИС 28 на развер- через блок 9 входных регистров на входы блока 8 памяти реакций. По окончании прогона тестов - испытательных воздействий в блоке 8 памяти реакции оказывается записанным массив из 1024 двухбитовых кодов реакций, который по команде может быть

нутые во времени испытательные воздействия поступают, с выходов триггеров 38, 39

процессора 47 центрального блока управления. Здесь мо.жет быть осушествлен цифровой анализ выполненного функционального контроля бис 28.

При из.мерении статических параметров БИС устройство работает следуюши.м образом. Предусмотрены пять режимов работы: задание напряжения и измерение напряжения, задание тока и измерение тока, задание

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый генератор синусоидальных колебаний | 1986 |

|

SU1460768A1 |

| Многоканальное устройство для ввода аналоговых данных | 1985 |

|

SU1273911A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU839046A1 |

| Устройство для спектрально-временного анализа сигналов | 1989 |

|

SU1711109A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля электрических /статических и динамических/ параметров и функционирования цифровых логических БИС, в частности схем с эмиттерно-связанной логикой. Целью изобретения является повышение точности контроля. С этой целью в устройство, содержащее блок сопряжения общей шины, блок преобразователей уровня, блок памяти тестов, блок выходных регистров, блок памяти реакций, блок входных регистров, дешифратор каналов тестирования, генератор синхроимпульсов, два преобразователя код-напряжение, аналого-цифровой преобразователь напряжение-код, первый коммутатор, стробируемый временной компаратор, узел синхронизации, два ключа, блок коммутации выводов, два компаратора, пороговый усилитель, шифратор испытательных воздействий, два триггера, дешифратор, блок регистров приближения, шифратор кода настройки, два регистра режима и генератор тестов, введены блок микропрограммного управления, блок сопряжения канала общего пользования, преобразователь частота-код, рециркуляционный автогенератор, второй коммутатор, третий регистр режима, блок цифроаналоговой памяти, дешифратор режима канала, шифратор настройки уровней и четыре цифроаналоговых преобразователя. 12 ил.

с указанной дискретностью определяется старшими разрядами входного кода и непрерывно меняется в зависимости от значения младших разрядов.

На основной стадии ФК тестовые вектора считываются из блока 6 памяти тестов на частоте тестирования (например, 20 МГц или 0,625 МГц) и Б шифраторе 34 испытательных воздействий привязываются к моментам времени, заданным метками времени

40

и измерение напряжения, измерение тока потребления БИС. Для задания точного значения напряжения (тока) на входе конт- ролируе.мой БИС 28 используется прецизионный преобразователь 13 код-напряжение (ток). Измерение величины напряжения (тока) осуществляется АЦП 14 напряжение-код, причем значение тока определяется по падению, напряжения на прецизионном резисторе известной небольшой величиt - tn. Сформированные по кодовому соста- 45 чь, включаемом между входными зажимаву и во времени испытательные воздействия- стимулы в каждом канале поступают на вход порогового усилителя 35. С его выхода на данный логический вход контролируемой БИС 28 через скоммутированную цепь блока 33 коммутации вывода подается испытательное воздействие с заданными от ячеек памяти уровней ЦАП величинами нижнего (U) и верхнего (Ug) уровней напряжения. Число участвующих в ФК индивидуальных

ми преобразователя 14 напряжение-код. Требуемое значение и вид задаваемой величины, а также вид измеряемой величины и диапазон измерений вводятся в устройство программно. Измерения статических пара- 50 метров по всем логическим входам - индивидуальным каналам контролируемой БИС 28 осуществляются последовательно во времени путем поочередного подключения задающего и измерительного преобразовате- каналов равно числу логических входов конт- 55 соответственно к входу и выходу очеред- ролируемой БИС 28. С выхода контролируе-ного индивидуального канала 32 задания

мой БИС 28 через блок 33 коммутации вы- при помощи,первого (низкочастотного) ком- водов на входы компараторов 36, 37 дан- мутатора 15. Результаты измерений переда40

и измерение напряжения, измерение тока потребления БИС. Для задания точного значения напряжения (тока) на входе конт- ролируе.мой БИС 28 используется прецизионный преобразователь 13 код-напряжение (ток). Измерение величины напряжения (тока) осуществляется АЦП 14 напряжение-код, причем значение тока определяется по падению, напряжения на прецизионном резисторе известной небольшой величи 45 чь, включаемом между входными зажимами преобразователя 14 напряжение-код. Требуемое значение и вид задаваемой величины, а также вид измеряемой величины и диапазон измерений вводятся в устройство программно. Измерения статических пара- 50 метров по всем логическим входам - индивидуальным каналам контролируемой БИС 28 осуществляются последовательно во времени путем поочередного подключения заются в цифровой форме от ЦАП 14 напряжение-код в центральный блок управления.

Предусмотрена возможность измерения таких динамических парам етров, как временные интервалы, задержки и длительности импульсов в диапазоне от 1 до 30 не. Эти измерения осуществляются стробируемым временным компаратором 16 - двухканальным программно-управляемым стробоскопическим осциллографом последовательно во времени путем подключения прибора к выбранному индивидуальному каналу 32 задания вторым (высокочастотным) коммутатором 19. Значения диапазонов измерений по шкарегистров режима и входом записи шифратора кода настройки, второй вход-выход данных блока преобразователей уровня подключен к входу данных блока намяти тес- 5 тов и выходу данных блока памяти реакций, первый и второй выходы блока преобразователей уровня соединены с первым и вторым входами данных дешифратора каналов тестирования, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к адресным входам блоков памяти тестов и памяти реакций, входу чтения блока памяти тестов, входу записи блока памяти реакций, входу режима генератора синхроимпульсов и первому син10

лам времени и амплитуд осциллографа за- 15 хровходу стробируемого временного компадаются программно. Результаты измерений передаются в цифровой форме в центральный,блок управления.

Формула изобретения

Устройство для автоматического контроля больших интегральных схем, содержащее блок сопряжения общей шины, блок преобразователей уровня, блок памяти тестов.

20

ратора; вход данных и выход блока выходных регистров соединены cooTBeTctBeHHO с выходом блока памяти тестов и первым входом данных шифратора испытательных воздействий, вход данных и выход блока входных регистров подключены соответственно к выходам первого и второго триггеров и входу данных блока памяти реакций, первый, второй и третий входы данных и управляющий вход первого коммутатора соединены

блок выходных регистров, блок памяти реак- соответственно с выходами первого и второ

ций, блок входных регистров, дешифратор каналов тестирования, генератор синхроимпульсов, два преобразователя код-напряжение, аналого-цифровой преобразователь

го преобразователей код-напряжение, выходом аналого-цифрового преобразователя напряжение;-код и первым выходом блока коммутации выводов, выходы первого коммунапряжение-код, первый коммутатор, стро- о татора являются выходами устройства для

подключения к входам объекта контроля, вход и выход узла синхронизации подключены соответственно к выходу первого регистра режима и второму синхровходу стробируемого временного компаратора, вход данных и выход порогового усилителя соединены соответственно с первым выходом шифратора испытательных воздействий и первым входом блока коммутации выводов, входы-выходы, которого являются входами-выходами устройства для подключения к входам-выходам объекта контроля, выход блока коммутации выводов подключен к первым входам данных первого и второго компараторов, управляющие входы которых соединены соответственно со вторым и третьим выходами

оируемыи временной компаратор, узел синхронизации, два ключа, блок коммутации выводов, два компаратора, пороговый усилитель, шифратор испытательных воздействий, два триггера, дешифратор, блок регистров приближения, шифратор кода настройки, два регистра режима и генератор тестов, выход которого соединен с. входом пуска генератора синхроимпульсов, выходы которого подключены к входу разрешения дешифратора каналов тестирования, син- хровходу блока входных регистров и синхро- входу блока выходных регистров, первый вход-выход данных блока сопряжения общей шины соединен с первым входом-выходом данных блока преобразователей уровня.

35

40

подключения к входам объекта контроля, вход и выход узла синхронизации подключены соответственно к выходу первого регистра режима и второму синхровходу стробируемого временного компаратора, вход данных и выход порогового усилителя соединены соответственно с первым выходом шифратора испытательных воздействий и первым входом блока коммутации выводов, входы-выходы, которого являются входами-выходами устройства для подключения к входам-выходам объекта контроля, выход блока коммутации выводов подключен к первым входам данных первого и второго компараторов, управляющие входы которых соединены соответственно со вторым и третьим выходами

входами данных блока регистров прибли- 45 шифратора испытательных воздействий, выжения, генератора тестов, шифратора кода настройки и первого и второго регистров режима, выход признака адреса блока сопряжения общей шины подключен к первому управляющему входу блока преобразователей уровня и входам разрешения записи блока регистров приближения, генератора тестов, шифратора кода настройки и первого и второго регистров режима, выход признака синхронизации блока сопряжения общей шины соединен с вторым управляющим входом блока преобразователей уровня, синхровходами блока регистров приближения, генератора тестов, первого и второго

регистров режима и входом записи шифратора кода настройки, второй вход-выход данных блока преобразователей уровня подключен к входу данных блока намяти тес- тов и выходу данных блока памяти реакций, первый и второй выходы блока преобразователей уровня соединены с первым и вторым входами данных дешифратора каналов тестирования, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к адресным входам блоков памяти тестов и памяти реакций, входу чтения блока памяти тестов, входу записи блока памяти реакций, входу режима генератора синхроимпульсов и первому син

ратора; вход данных и выход блока выходных регистров соединены cooTBeTctBeHHO с выходом блока памяти тестов и первым входом данных шифратора испытательных воздействий, вход данных и выход блока входных регистров подключены соответственно к выходам первого и второго триггеров и входу данных блока памяти реакций, первый, второй и третий входы данных и управляющий вход первого коммутатора соединены

соответственно с выходами первого и второ

го преобразователей код-напряжение, выходом аналого-цифрового преобразователя напряжение;-код и первым выходом блока коммутации выводов, выходы первого коммутатора являются выходами устройства для

подключения к входам объекта контроля, вход и выход узла синхронизации подключены соответственно к выходу первого регистра режима и второму синхровходу стробируемого временного компаратора, вход данных и выход порогового усилителя соединены соответственно с первым выходом шифратора испытательных воздействий и первым входом блока коммутации выводов, входы-выходы, которого являются входами-выходами устройства для подключения к входам-выходам объекта контроля, выход блока коммутации выводов подключен к первым входам данных первого и второго компараторов, управляющие входы которых соединены соответственно со вторым и третьим выходами

0

5

ходы первого и второго компараторов подключены к информационным входам первого и второго триггеров, синхровходы которых соединены с выходом- генератора синхроимпульсов, вход дешифратора подключен к выходу второго регистра режима, второй и третий входы данных блока регистров приближений соединены соответственно с первым выходом стробируемого временного компаратора и первым выходом шифратора кода настройки, отличающееся тем, что, с целью- повышения точности контроля, в него введены блок микропрограммного управления, блок сопряжения канала общего пользов а21

ния, преобразователь частота-код, рециркуляционный автогенератор, второй коммутатор, третий регистр режима, блок цифро- аналоговой памяти, дешифратор режима канала, шифратор настройки уровней и четыре цифроаналоговых преобразователя, выходы которых подключены соответственно к первому и второму управляющим входам порогового усилителя и вторым входам данных первого и второго компараторов, первый и второй синхровходы, вход управления режима, информационный вход и выход блока цифроаналоговой памяти соединены соответственно с выходом блока регистров приближения, выходом генератора тестов, первым выходом дешифратора режима канала, вторым выходом шифратора кода настройки и вторым информационным входом шифратора испытательных воздействий, разрешающий вход которого подключен к второму выходу дешифратора режима канала, первый и второй входы данных, разрешающий вход и выход дешифратора настройки уровней соединены соответственно с выходом шифратора настройки, выходами первого и -второго триггеров, третьим выходом дешифратора режима канала и входами первого, второго третьего четвертого цифроаналоговых преобразователей, четвертый выход дешифратора режима канала подключен ко второму входу блока коммутации выводов, третий вход которого соединен с выходом второго коммутатора, управляющий вход которого подключен к выходу дешифратора, вход и первый выход рециркуляционного генератора соединены соответственно с выходом третьего регистра режима и тактовым входом преобразователя частота-код, вход данных вто рого коммутатора через первый и второй

ключи соединен со вторыми выходами соот

1529220

22

15

5 также входом синхровходом

ветственно рециркуляционного генератора и стробируемого временного компаратора, входы данных дешифратора режима канала и третьего регистра режима подключены

5 к первому входу-выходу .данных блока сопряжения обшей шины, выход признака адреса и выход признака синхронизации которого соединены соответственно с первым и вторым разрешающими входами деьйифра Q тора режима канала, а также входом разрешения записи и синхровходом третьего регистра режима, первый вход-выход данных блока сопряжения канала общего пользования подключен к входу-выходу данных преобразователя частота-код и входам данных первого и второго преобразователей код-напряжение и аналого-цифрового преобразователя напряжение-код, выход признака адреса и выход признака синхронизации блока сопряжения канала обшего пользования соединены соответственно с входами разрешения записи и входами синхронизации преобразователя частота-код, первого и второго преобразователей код- напряжение и аналого-цифрового преобразователя напряжение-код, второй вход- выход данных блока сопряжения общей щи- ны подключен к адресному входу блока микропрограммной памяти и входу данных стробируемого временного компаратора и второму входу-выходу данных блока сопря0 жения канала обшего пользования, первый и второй выходы блока микропрограммного управления соединены соответственно с вхо дам.и разрешения записи и синхровходами блока сопряжения общей шины, блока сопряжения канала общего пользования, а разрешения записи и вторым стробируемого временного

0

5

компаратора.

7

п.м

.М8

Z 5Г 59

Ш

127

От 24 Фиг.6

128

/52

S1

§ II

131

Фиг.

Фиг. 5

м

5

7J5

±б-

35

Фие.7

А 155

Ч

г

53

65

11

Фиг.9

т

18

N

iV

wy ЧK -

1-

:S:

95

к 36

т

г

97

Т 91

65

г-

. f 5 D«

к 36

СИ 84

85

W

91

89

Л

л

| Измеритель времени задержки кабельных линий связи | 1982 |

|

SU1075230A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Электронная промышленность, 1975, № 1 с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| ЛЫЖНЫЙ САМОКАТ | 1925 |

|

SU3280A1 |

Авторы

Даты

1989-12-15—Публикация

1986-07-15—Подача