Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), широкополосных и избирательных усилителях, фильтрах и т.п.).

Известны схемы дифференциальных усилителей (ДУ) с параллельным включением двух параллельно-балансных каскадов [1-15]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с одиночными параллельно-балансными каскадами, стали основным усилительным элементом многих микросхем аналоговых интерфейсов (например, LM121 и др.). Предлагаемое изобретение относится к данному подклассу устройств.

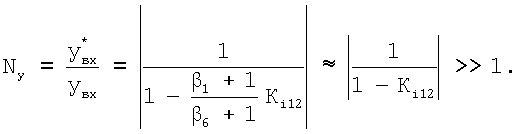

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №6917257 В2 (фиг.1), H03F 3/45, содержащий входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 выходы, транзистор источника опорного тока 6, коллектор которого связан с общей эмиттерной цепью 7 входного параллельно-балансного каскада 1, а эмиттер соединен с шиной источника питания 8 через токостабилизирующий двухполюсник 9, первый 10 и второй 11 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами параллельно-балансного каскада 1, а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости.

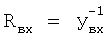

Существенный недостаток известного ДУ состоит в том, что он имеет небольшое входное дифференциальное сопротивление (Rвх), зависящее от абсолютных значений коэффициента усиления по току базы (β) применяемых транзисторов и их статического режима. Для повышения  в известных ДУ применяется местная отрицательная обратная связь (вводятся эмиттерные резисторы). Однако при этом ухудшаются многие параметры ДУ - коэффициент усиления по напряжению, напряжение смещения нуля, коэффициент подавления помехи по питанию, крутизна усиления ДУ и др.

в известных ДУ применяется местная отрицательная обратная связь (вводятся эмиттерные резисторы). Однако при этом ухудшаются многие параметры ДУ - коэффициент усиления по напряжению, напряжение смещения нуля, коэффициент подавления помехи по питанию, крутизна усиления ДУ и др.

Основная цель предлагаемого изобретения состоит в повышении на один-два порядка входного сопротивления ДУ. Дополнительная - в достижении статических входных токов.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 выходы, транзистор источника опорного тока 6, коллектор которого связан с общей эмиттерной цепью 7 входного параллельно-балансного каскада 1, а эмиттер соединен с шиной источника питания 8 через токостабилизирующий двухполюсник 9, первый 10 и второй 11 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами параллельно-балансного каскада 1, а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости, предусмотрены новые связи - база транзистора источника опорного тока 6 связана с объединенными эмиттерами первого 10 и второго 11 вспомогательных транзисторов, коллектор первого 10 вспомогательного транзистора соединен со входом первого 12 дополнительного токового зеркала, коллектор второго 11 вспомогательного транзистора связан со входом второго 13 дополнительного токового зеркала, причем выход первого 12 дополнительного токового зеркала соединен с базой первого 10 вспомогательного транзистора, а выход второго 13 дополнительного токового зеркала связан с базой второго вспомогательного транзистора 11.

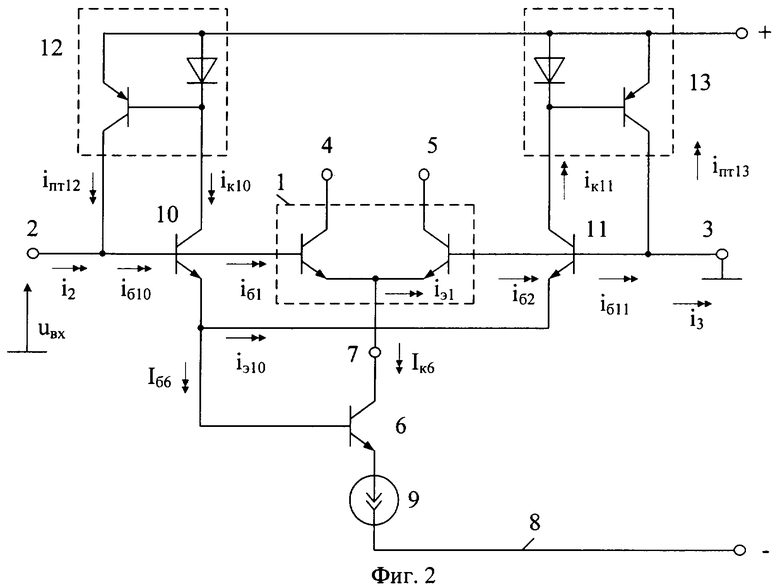

На чертеже фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

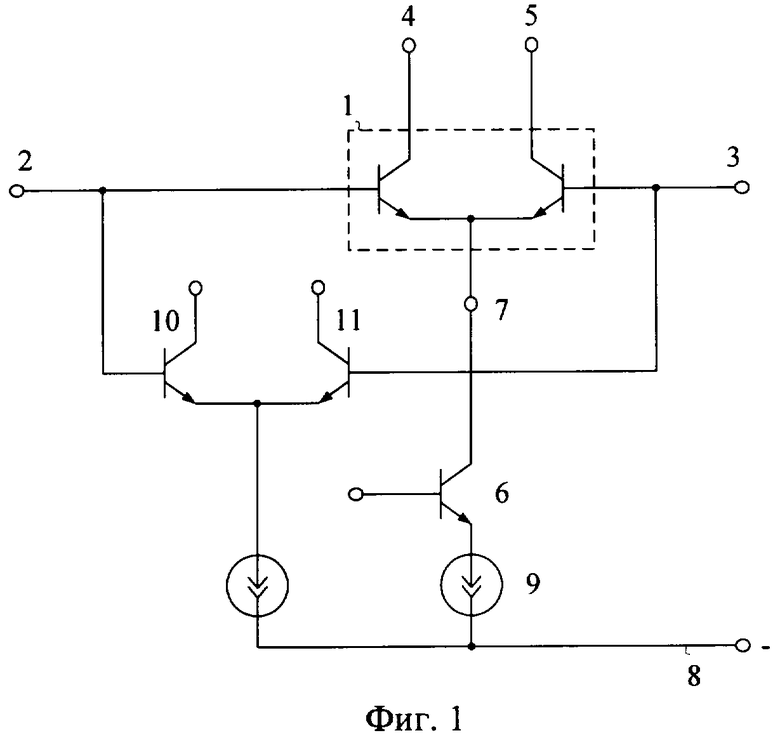

На чертеже фиг.3 показаны схемы известного и заявляемого ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». При этом в качестве дополнительных токовых зеркал 12 и 13 здесь используются идеальные подсхемы, имеющие единичный коэффициент передачи по току (Gain=l).

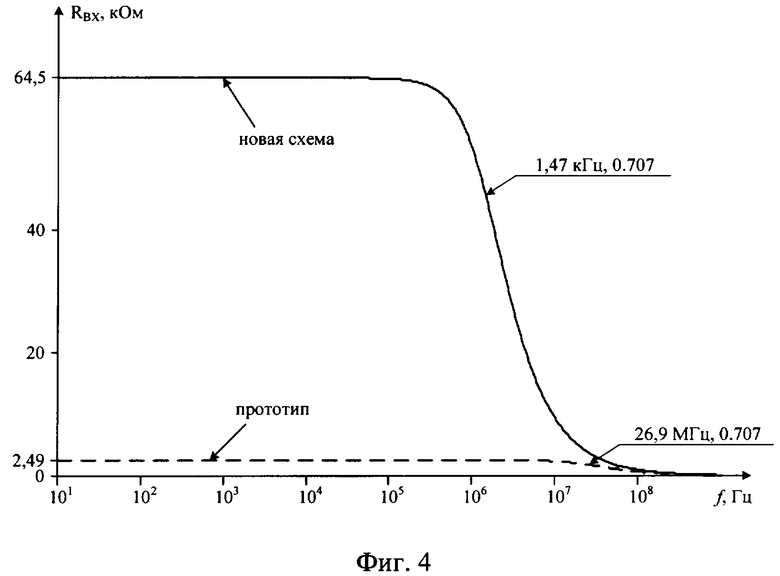

График фиг.4 иллюстрирует частотную зависимость входного дифференциального сопротивления известного и заявляемого (фиг.3) устройств.

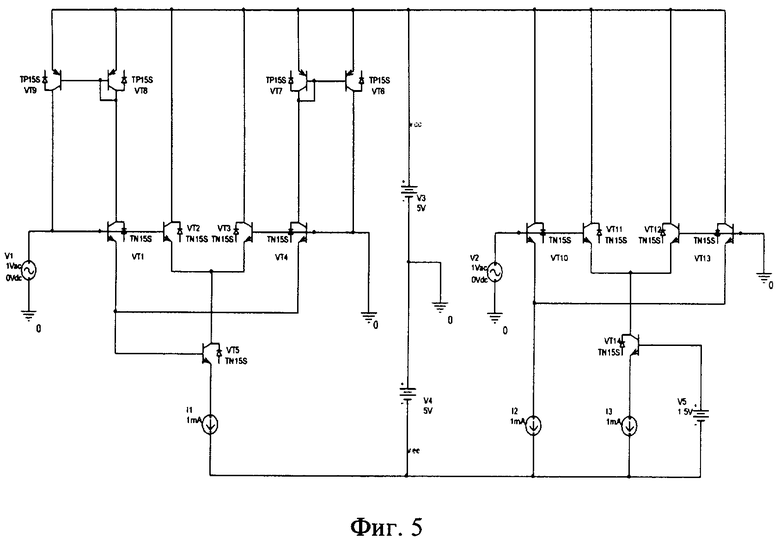

На чертеже фиг.5 показаны схемы известного и заявляемого ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда в качестве дополнительных токовых зеркал 12 и 13 используются классические подсхемы.

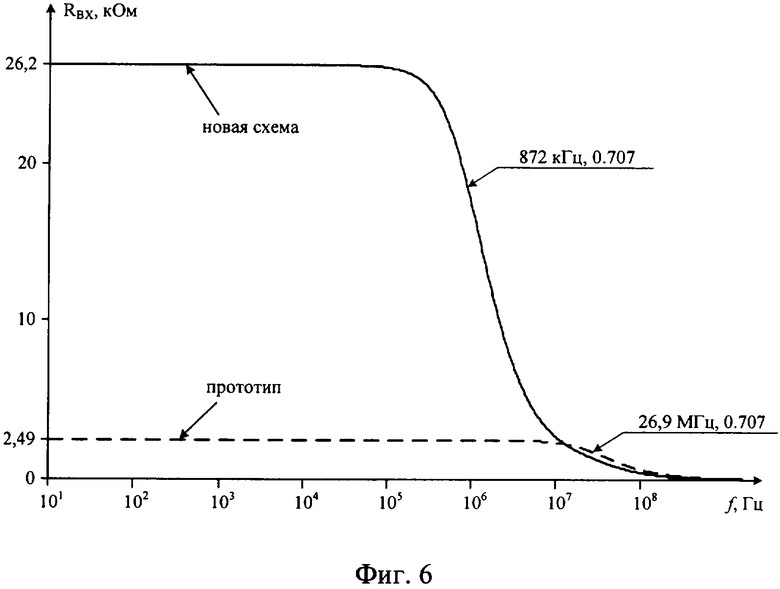

График фиг.6 иллюстрирует частотную зависимость входного дифференциального сопротивления известного и заявляемого (фиг.5) устройств.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 выходы, транзистор источника опорного тока 6, коллектор которого связан с общей эмиттерной цепью 7 входного параллельно-балансного каскада 1, а эмиттер соединен с шиной источника питания 8 через токостабилизирующий двухполюсник 9, первый 10 и второй 11 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами параллельно-балансного каскада 1, а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости. База транзистора источника опорного тока 6 связана с объединенными эмиттерами первого 10 и второго 11 вспомогательных транзисторов, коллектор первого 10 вспомогательного транзистора соединен со входом первого 12 дополнительного токового зеркала, коллектор второго 11 вспомогательного транзистора связан со входом второго 13 дополнительного токового зеркала, причем выход первого 12 дополнительного токового зеркала соединен с базой первого 10 вспомогательного транзистора, а выход второго 13 дополнительного токового зеркала связан с базой второго вспомогательного транзистора 11.

Рассмотрим работу схемы фиг.2.

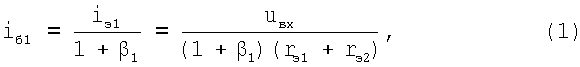

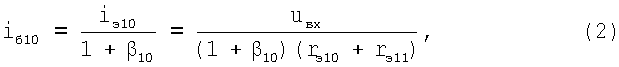

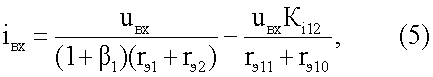

Если на вход 2 подается напряжение uвх, то это вызывает приращение тока базы

где β1>>1 - коэффициент усиления по току базы левого входного транзистора каскада 1;

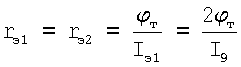

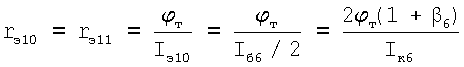

- сопротивление эмиттерного перехода входных транзисторов каскада 1;

- сопротивление эмиттерного перехода входных транзисторов каскада 1;

φт=26 мВ - температурный потенциал;

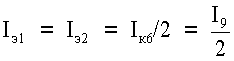

- статический эмиттерный ток входных транзисторов каскада 1;

- статический эмиттерный ток входных транзисторов каскада 1;

I9 - ток через двухполюсник 9.

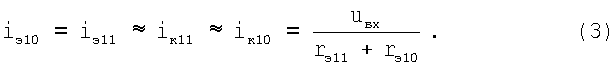

Аналогично можно найти ток базы iб10 транзистора 10

где β10 - коэффициент усиления по току базы транзистора 10;

- сопротивление эмиттерных переходов транзисторов 10 и 11.

- сопротивление эмиттерных переходов транзисторов 10 и 11.

С другой стороны, эмиттерный и коллекторный токи транзисторов 10 и 11

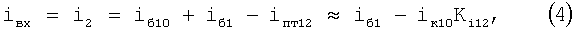

Входной ток ДУ определяется суммой токов

где Kil2≈1 - коэффициент передачи по току подсхемы 12.

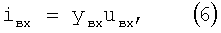

С учетом того, что Kil2=1, из (4) находим, что входной ток ДУ определяется формулой

или

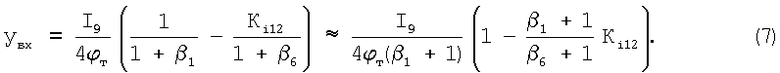

где увх - входная проводимость ДУ, причем

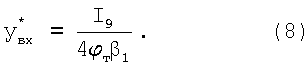

В ДУ-прототипе входная проводимость принимает достаточно большое значение:

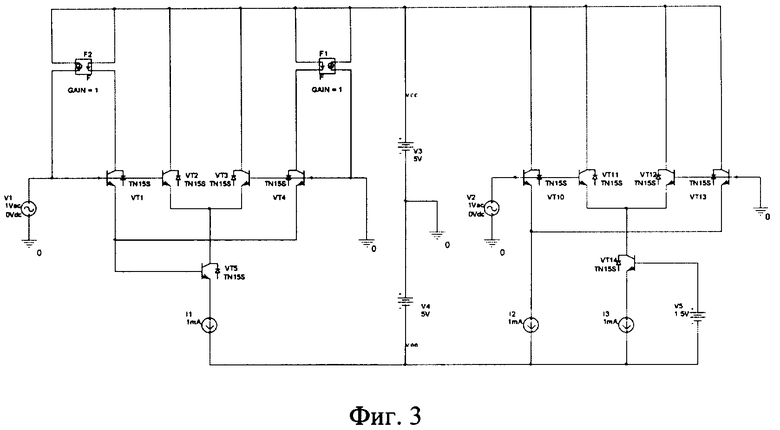

Таким образом, в заявляемой схеме при β1≈β6 увх улучшается в N-раз, где

Полученные выше теоретические выводы подтверждаются результатами моделирования в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» (фиг.5), выигрыш по Rвх - более чем на порядок.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. А.св. СССР №459780

2. Патент Японии JP 2004040157

3. Патентная заявка США №2004/0061544

4. Патентная заявка США №2003/0155959

5. Патентная заявка США №2003/0141919

6. Патент США №6292033

7. Патент США №5936468

8. Патент США №4866397

9. Патент США №4331929

10. Патент DE №10321442

11. Патент США №6262628

12. Патент США №6172551

13. Патент США №5461342

14. Патент США №5373741

15. Патент США №6917257

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346386C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2008 |

|

RU2346387C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346388C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

Изобретение относится к области радиотехники и связи для усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), широкополосных и избирательных усилителях, фильтрах и т.п.). Технический результат - повышение входного сопротивления и достижение статических входных токов. Дифференциальный усилитель содержит входной параллельно-балансный каскад (ВПБК) (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) выходы, транзистор (Т) источника опорного тока (6), коллектор которого связан с общей эмиттерной цепью (7) ВПБК (1), а эмиттер соединен с шиной источника питания (8) через токостабилизирующий двухполюсник (9), первый (10) и второй (11) вспомогательные Т, базы которых соединены с первым (2) и вторым (3) входами ВПБК (1), а эмиттеры связаны друг с другом, причем все основные Т схемы имеют один тип проводимости. База Т источника опорного тока (6) связана с объединенными эмиттерами первого (10) и второго (11) вспомогательных Т, коллектор первого (10) вспомогательного Т соединен со входом первого (12) дополнительного токового зеркала (ДТЗ), коллектор второго (11) вспомогательного Т связан со входом второго (13) ДТЗ, причем выход первого (12) ДТЗ соединен с базой первого (10) вспомогательного Т, а выход второго (13) ДТЗ связан с базой второго (11) вспомогательного Т. 6 ил.

Дифференциальный усилитель с повышенным входным сопротивлением, содержащий входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) выходы, транзистор источника опорного тока (6), коллектор которого связан с общей эмиттерной цепью (7) входного параллельно-балансного каскада (1), а эмиттер соединен с шиной источника питания (8) через токостабилизирующий двухполюсник (9), первый (10) и второй (11) вспомогательные транзисторы, базы которых соединены с первым (2) и вторым (3) входами параллельно-балансного каскада (1), а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости, отличающийся тем, что база транзистора источника опорного тока (6) связана с объединенными эмиттерами первого (10) и второго (11) вспомогательных транзисторов, коллектор первого (10) вспомогательного транзистора соединен со входом первого (12) дополнительного токового зеркала, коллектор второго (11) вспомогательного транзистора связан со входом второго (13) дополнительного токового зеркала, причем выход первого (12) дополнительного токового зеркала соединен с базой первого (10) вспомогательного транзистора, а выход второго (13) дополнительного токового зеркала связан с базой второго (11) вспомогательного транзистора.

| US 6917257 В2, 12.07.2005 | |||

| Дифференциальный усилитель | 1985 |

|

SU1246340A1 |

| US 4451800, 29.05.1984 | |||

| US 3551832, 29.12.1970. | |||

Авторы

Даты

2009-09-20—Публикация

2008-02-12—Подача