Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Известны схемы дифференциальных усилителей (ДУ) на основе двух параллельно включенных дифференциальных каскадов (ДК) с токостабилизирующими двуполюсниками в эммитерных цепях входных транзисторов [1-15]. В связи с высокой популярностью такой архитектуры ДУ, на их модификации выдано более 20 патентов для ведущих производителей микроэлектронных изделий. Предлагаемое изобретение относится к данному подклассу устройств. Однако известные ДУ имеют недостаточно высокий коэффициент ослабления (Кос.сф) синфазных сигналов и небольшую величину входного сопротивления (Rвх.с) для синфазных сигналов.

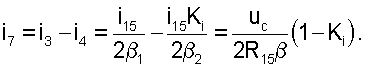

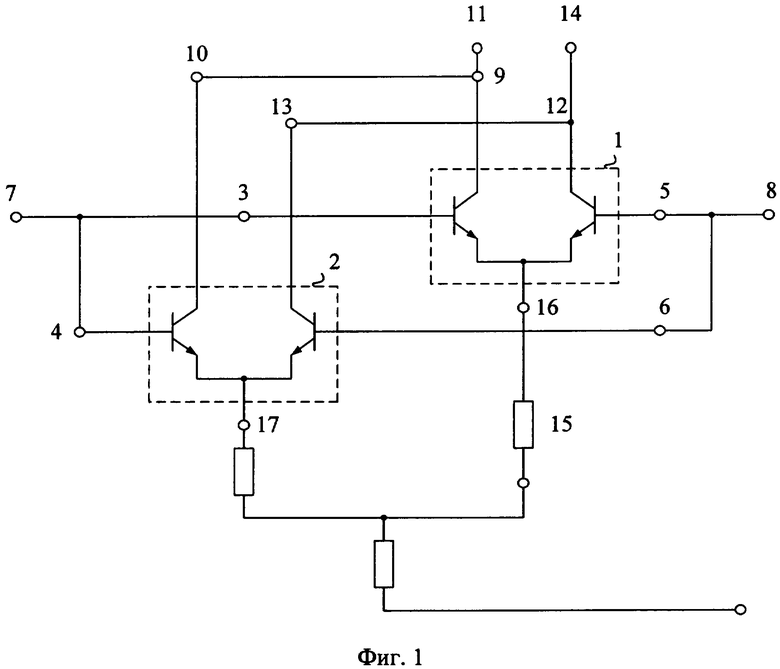

Ближайшим прототипом (фиг.1) данного устройства является дифференциальный усилитель, описанный в патенте США №4460872, содержащий первый 1 и второй 2 параллельно балансные каскады, синфазные входы которых 3, 4 и 5, 6 связаны друг с другом и подключены к соответствующим входам 7 и 8 дифференциального усилителя, инвертирующий выход 9 первого параллельно балансного каскада 1 соединен с инвертирующим выходом 10 второго параллельно балансного каскада 2 и связан с инвертирующим выходом 11 дифференциального усилителя, неинвертирующий выход 12 первого 1 параллельно балансного каскада соединен с неинвертирующим выходом 13 второго 2 параллельно балансного каскада и связан с неинвертирующим выходом 14 дифференциального усилителя, токостабилизирующий резистор 15, первый вывод которого связан с общим эмиттерным входом 16 первого 1 параллельно балансного каскада, причем второй 2 параллельно балансный каскад имеет общий эмиттерный вход 17.

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно высокое ослабление синфазных сигналов (коэффициент Кос.сф) и низкое входное сопротивление (Rвх.c) для синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов и увеличении входного сопротивления для синфазных сигналов.

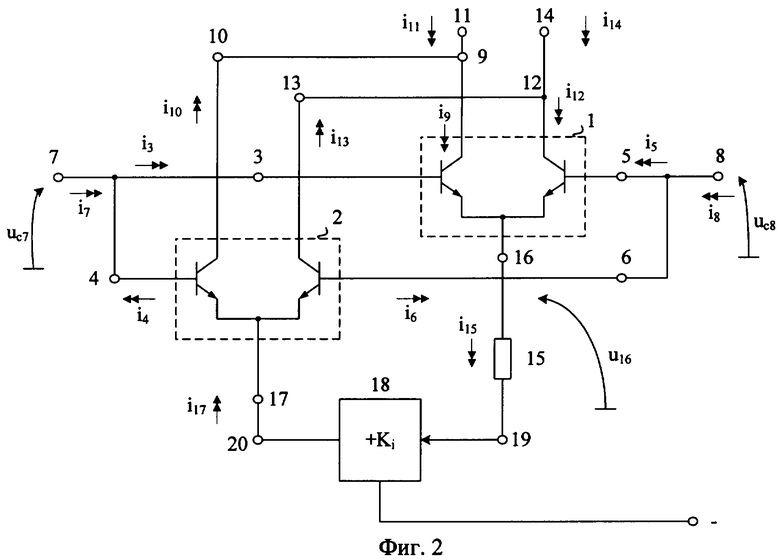

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 и второй 2 параллельно балансные каскады, синфазные входы которых 3, 4 и 5, 6 связаны друг с другом и подключены к соответствующим входам 7 и 8 дифференциального усилителя, инвертирующий выход 9 первого параллельно балансного каскада 1 соединен с инвертирующим выходом 10 второго параллельно балансного каскада 2 и связан с инвертирующим выходом 11 дифференциального усилителя, неинвертирующий выход 12 первого 1 параллельно балансного каскада соединен с неинвертирующим выходом 13 второго 2 параллельно балансного каскада и связан с неинвертирующим выходом 14 дифференциального усилителя, токостабилизирующий резистор 15, первый вывод которого связан с общим эмиттерным входом 16 первого 1 параллельно балансного каскада, причем второй 2 параллельно балансный каскад имеет общий эмиттерный вход 17, вводятся новые элементы и связи - в схему введен дополнительный неинвертирующий повторитель тока 18, вход 19 которого связан со вторым выводом токостабилизирующего двухполюсника 15, а выход 20 подключен к общему эмиттерному входу 17 второго 2 параллельно балансного каскада.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на чертеже фиг.2.

На фиг.3 изображен вариант построения дополнительного неинвертирующего повторителя тока 18 на биполярном транзисторе 21 (п.2 формулы изобретения).

На фиг.4 показан вариант построения дополнительного неинвертирующего повторителя тока 18 на полевом транзисторе 24 (п.3 формулы изобретения).

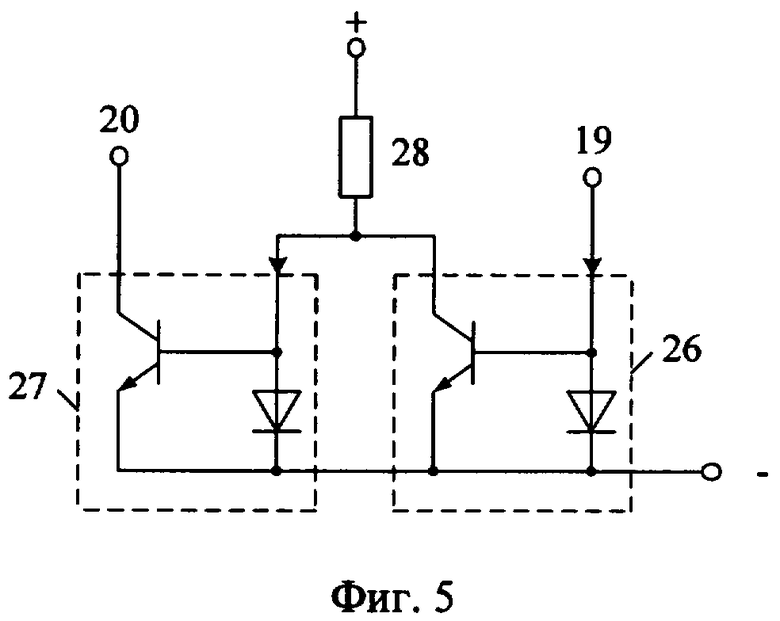

На фиг.5 показан вариант построения дополнительного неинвертирующего повторителя тока 18 на двух дополнительных токовых зеркалах 26 и 27 (п.4 формулы изобретения).

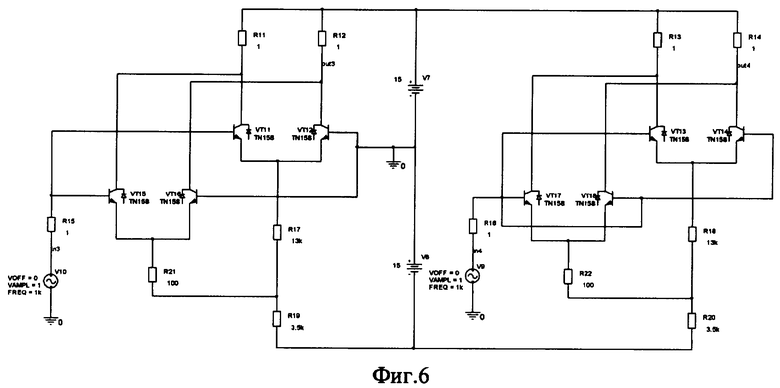

На фиг.6 изображена схема ДУ - прототипа фиг.1, которая исследовалась авторами в среде PSpice на степень ослабления входных синфазных сигналов и величину входного сопротивления Rвх.с.

На фиг.7 показана схема заявляемого ДУ фиг.2 среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» при воздействии на его входы синфазного сигнала.

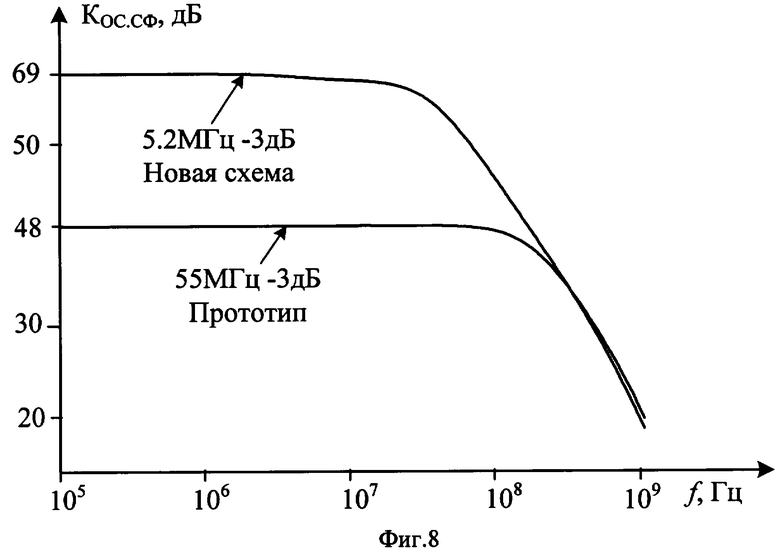

На фиг.8 изображены частотные зависимости коэффициента ослабления входных синфазных сигналов Кос.сф, полученные при исследовании схем фиг.6 и 7 в среде PSpice.

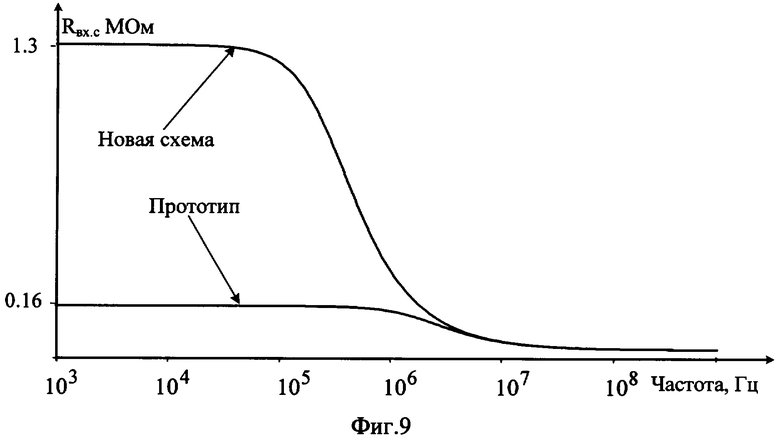

На фиг.9 изображены частотные зависимости входного сопротивления Квх.c, полученные при исследовании схем фиг.6 и 7.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 параллельно балансные каскады, синфазные входы которых 3, 4 и 5, 6 связаны друг с другом и подключены к соответствующим входам 7 и 8 дифференциального усилителя, инвертирующий выход 9 первого параллельно балансного каскада 1 соединен с инвертирующим выходом 10 второго параллельно балансного каскада 2 и связан с инвертирующим выходом 11 дифференциального усилителя, неинвертирующий выход 12 первого 1 параллельно балансного каскада соединен с неинвертирующим выходом 13 второго 2 параллельно балансного каскада и связан с неинвертирующим выходом 14 дифференциального усилителя, токостабилизирующий резистор 15, первый вывод которого связан с общим эмиттерным входом 16 первого 1 параллельно балансного каскада, причем второй 2 параллельно балансный каскад имеет общий эмиттерный вход 17. В схему введен дополнительный неинвертирующий повторитель тока 18, вход 19 которого связан со вторым выводом токостабилизирующего двухполюсника 15, а выход 20 подключен к общему эмиттерному входу 17 второго 2 параллельно-балансного каскада.

На фиг.3, в соответствии с п.2 формулы изобретения, дополнительный неинвертирующий повторитель тока 18 выполнен на первом вспомогательном биполярном транзисторе 21, эмиттер которого связан с первым вспомогательным резистором 22 и является входом 19 дополнительного неинвертирующего повторителя тока 18, база подключена к источнику напряжения смещения 23, а коллектор является выходом 20 дополнительного неинвертирующего повторителя тока 18.

На фиг.4, в соответствии с п.3 формулы изобретения, дополнительный неинвертирующий повторитель тока 18 выполнен на полевом транзисторе с управляющим р-n переходом 24, исток которого соединен с входом 19 дополнительного неинвертирующего повторителя тока 18 и вспомогательным резистором 25, а сток подключен к выходу 20 дополнительного неинвертирующего повторителя тока 18.

На фиг.5, в соответствии с п.4 формулы изобретения, дополнительный неинвертирующий повторитель тока 18 содержит первое дополнительное токовое зеркало 26, второе дополнительное токовое зеркало 27 и вспомогательный резистор 28, причем выход первого 26 дополнительного токового зеркала подключен к входу второго 27 дополнительного токового зеркала и вспомогательному резистору 28, выход второго 27 дополнительного токового зеркала соединен с выходом 20 дополнительного неинвертирующего повторителя тока 18, а вход первого 26 дополнительного токового зеркала является входом 19 дополнительного неинвертирующего повторителя тока 20.

Рассмотрим работу заявленного ДУ.

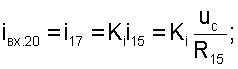

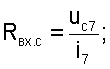

Если на входы 7 и 8 ДУ фиг.2 подаются входные напряжения uc7 и uc8, имеющие синфазную составляющую uc=uc7=uc8, то это приводит к передаче uс в общую эммитерную цепь 16 каскада 1 и изменению тока i15 через двухполюсник 15 и входного и выходного токов подсхемы 18.

u16≈uc;

iвх.19=i15,

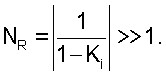

где R15 - сопротивление резистора 15; Кi - коэффициент передачи тока повторителя тока 18.

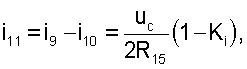

Приращения i15 и i15 передаются в общую эмиттерную цепь каскадов 1 и 2. Поэтому токи в выходной цепи:

i11=Sсф.11uc,

i14=Sсф.14uc,

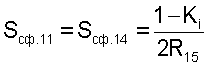

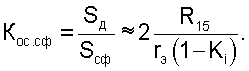

где  - крутизна преобразования входного синфазного сигнала (uc) в выходной ток i11 (i14).

- крутизна преобразования входного синфазного сигнала (uc) в выходной ток i11 (i14).

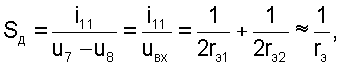

Крутизна передачи дифференциального сигнала ДУ фиг.2:

где rэ1≈rэ2≈rэ - дифференциальные сопротивления эммитерного р-n перехода входных транзисторов первого (1) и второго (2) дифференциальных каскадов. Следовательно,

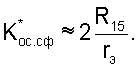

С другой стороны  ДУ - прототипа:

ДУ - прототипа:

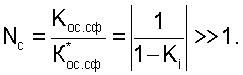

Следовательно, улучшение, которое дает предлагаемое схемотехническое решение:

Аналогично, можно показать, что для входного синфазного сопротивления по входу 7:

Поэтому в заявляемой схеме:

где β - коэффициент усиления по току базы применяемых транзисторов.

Следовательно, заявляемая схема дает улучшение Rвх.с в NR - раз, где

Полученные выше выводы моделирования предлагаемой схемы в подтверждаются результатами в среде PSpice, показанными на чертежах фиг.8 и 9.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. А.с. СССР №459780.

2. Патент Японии JP 2004040157.

3. Патентная заявка США №2004/0061544.

4. Патентная заявка США №2003/0155959.

5. Патентная заявка США №2003/0141919.

6. Патент США №6292033.

7. Патент США №5936468.

8. Патент США №4866397.

9. Патент США №4460872 (фиг.1).

10. Патент DE №10321442.

11. Патент США №6262628.

12. Патент США №6172551.

13. Патент США №5461342.

14. Патент США №5373741.

15. Патент США №6917257.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| ДВУХКАНАЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2452078C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ ОСЛАБЛЕНИЯ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2317633C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Дифференциальный усилитель содержит первый (1) и второй (2) параллельно балансные каскады, синфазные входы которых (3), (4) и (5), (6) связаны друг с другом и подключены к соответствующим входам (7) и (8) дифференциального усилителя, инвертирующий выход (9) первого параллельно балансного каскада (1) соединен с инвертирующим выходом 10 второго параллельно балансного каскада (2) и связан с инвертирующим выходом (11) дифференциального усилителя, неинвертирующий выход (12) первого (1) параллельно балансного каскада соединен с неинвертирующим выходом (13) второго (2) параллельно балансного каскада и связан с неинвертирующим выходом (14) дифференциального усилителя, токостабилизирующий резистор (15) первый вывод которого связан с общим эмиттерным входом (16) первого (1) параллельно балансного каскада, причем второй (2) параллельно балансный каскад имеет общий эмиттерный вход (17). В схему введен дополнительный неинвертирующий повторитель тока (18), вход (19) которого связан со вторым выводом токостабилизирующего двухполюсника (15), а выход (20) подключен к общему эмиттерному входу (17) второго (2) параллельно балансного каскада. Технический результат - повышение коэффициента ослабления входных синфазных сигналов и увеличение входного сопротивления для синфазных сигналов. 3 з.п. ф-лы, 9 ил.

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2278466C1 |

| Импульсный операционный усилитель | 1974 |

|

SU459780A1 |

| US 2004251982, 16.12.2004. | |||

Авторы

Даты

2009-02-10—Публикация

2008-02-01—Подача