Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления разности двух сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно-включенных дифференциальных каскадов (ДК) с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов (так называемые «dual input stage») и выходных каскадов, выполненных на транзисторах по схеме с общей базой [1-7]. Это самые широкополосные ДУ. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм. Причем в качестве токостабилизирующих двухполюсников каждого из параллельно включенных ДК таких ДУ применяются резисторы [8-11] - если усилитель не работает с синфазным сигналом. Последний вариант построения ДУ практически не используется в структуре операционных усилителей и компараторов, т.к. он не дает приемлемых значений коэффициента ослабления входного синфазного сигнала (Кос.сф), а также коэффициента подавления помехи по питанию (Кос.пп). Это связано с тем, что для получения больших значений Кос.сф необходимо выбирать сопротивление токостабилизирующих резисторов на уровне сотен килоом, что создает проблемы со статическим режимом при низковольтном питании (ЕП=1,5÷5 В). В технической литературе по аналоговой схемотехнике хорошо известно следующее правило построения ДУ - «в качестве токостабилизирующих двухполюсников ДУ не следует применять резисторы» (Ежков Ю.С. Справочник по схемотехнике усилителей, М., Радиософт, 2002. - С.81, 3 абзац сверху).

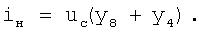

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5.291.149 (фиг.1 патента), содержащий первый 1 входной параллельно-балансный каскад на n-p-n транзисторах 2 и 3 и первом токостабилизирующем двухполюснике 4 в его общей эмиттерной цепи, первый вывод которого соединен с эмиттерами n-p-n транзисторов 2 и 3, второй 5 входной параллельно-балансный каскад на p-n-p транзисторах 6 и 7 и втором токостабилизирующем двухполюснике 8 в его общей эмиттерной цепи, первый вывод которого соединен с эмиттерами p-n-p транзисторов 6 и 7, причем синфазные входы первого 1 и второго 5 входных параллельно-балансных каскадов (базы транзисторов 2 и 6, 3 и 7) соединены друг с другом и являются входами двухтактного дифференциального усилителя 9 и 10, выход 11 первого 1 входного параллельно-балансного каскада соединен с первым входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, а выход 15 второго 5 входного параллельно-балансного каскада соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов, а также помех по питанию. Прежде всего, данный недостаток проявляется при использовании в качестве токостабилизирующих двухполюсников 4 и 8 резисторов или простейших источников тока на транзисторах с малым напряжением Эрли, которые при милиамперных токах имеют выходное сопротивление порядка 30-60 кОм.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ и коэффициента подавления помехи по питанию при относительно небольших внутренних сопротивлениях токостабилизирующих двухполюсников. При этом в заявляемом ДУ в качестве токостабилизирующих двухполюсников 4 и 8 при низковольтном питании могут применяться сравнительно низкоомные резисторы (единицы килоом).

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 входной параллельно-балансный каскад на n-p-n транзисторах 2 и 3 и первом токостабилизирующем двухполюснике 4 в его общей эмиттерной цепи, первый вывод которого соединен с эмиттерами n-p-n транзисторов 2 и 3, второй 5 входной параллельно-балансный каскад на p-n-p транзисторах 6 и 7 и втором токостабилизирующем двухполюснике 8 в его общей эмиттерной цепи, первый вывод которого соединен с эмиттерами p-n-p транзисторов 6 и 7, причем синфазные входы первого 1 и второго 5 входных параллельно-балансных каскадов соединены друг с другом и являются входами двухтактного дифференциального усилителя 9 и 10, выход 11 первого 1 входного параллельно-балансного каскада соединен с первым входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, выход 15 второго 5 входного параллельно-балансного каскада соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17, вводятся новые элементы и связи - выход 11 первого входного параллельно-балансного каскада 1 соединен с первым входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, через первый дополнительный неинвертирующий усилитель тока 18, второй вывод второго токостабилизирующего двухполюсника 8 соединен со входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, выход 15 второго 5 входного параллельно-балансного каскада соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17, через второй дополнительный неинвертирующий усилитель тока 19, а второй вывод первого токостабилизирующего двухполюсника 4 соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17.

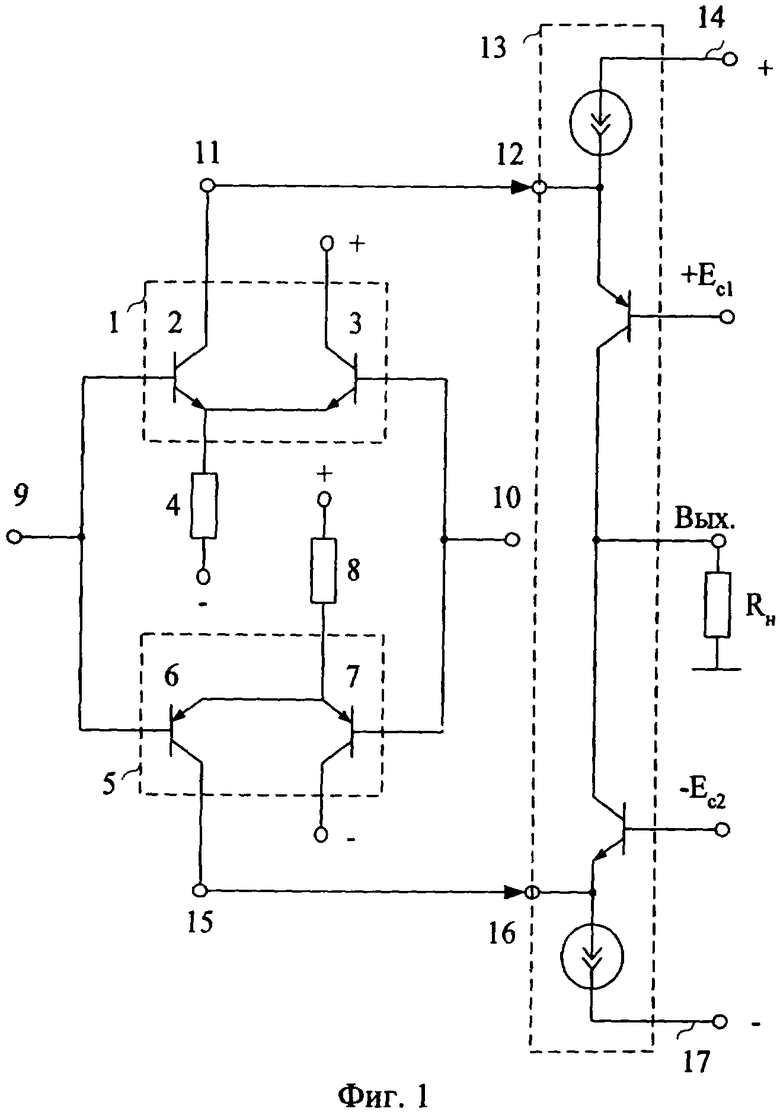

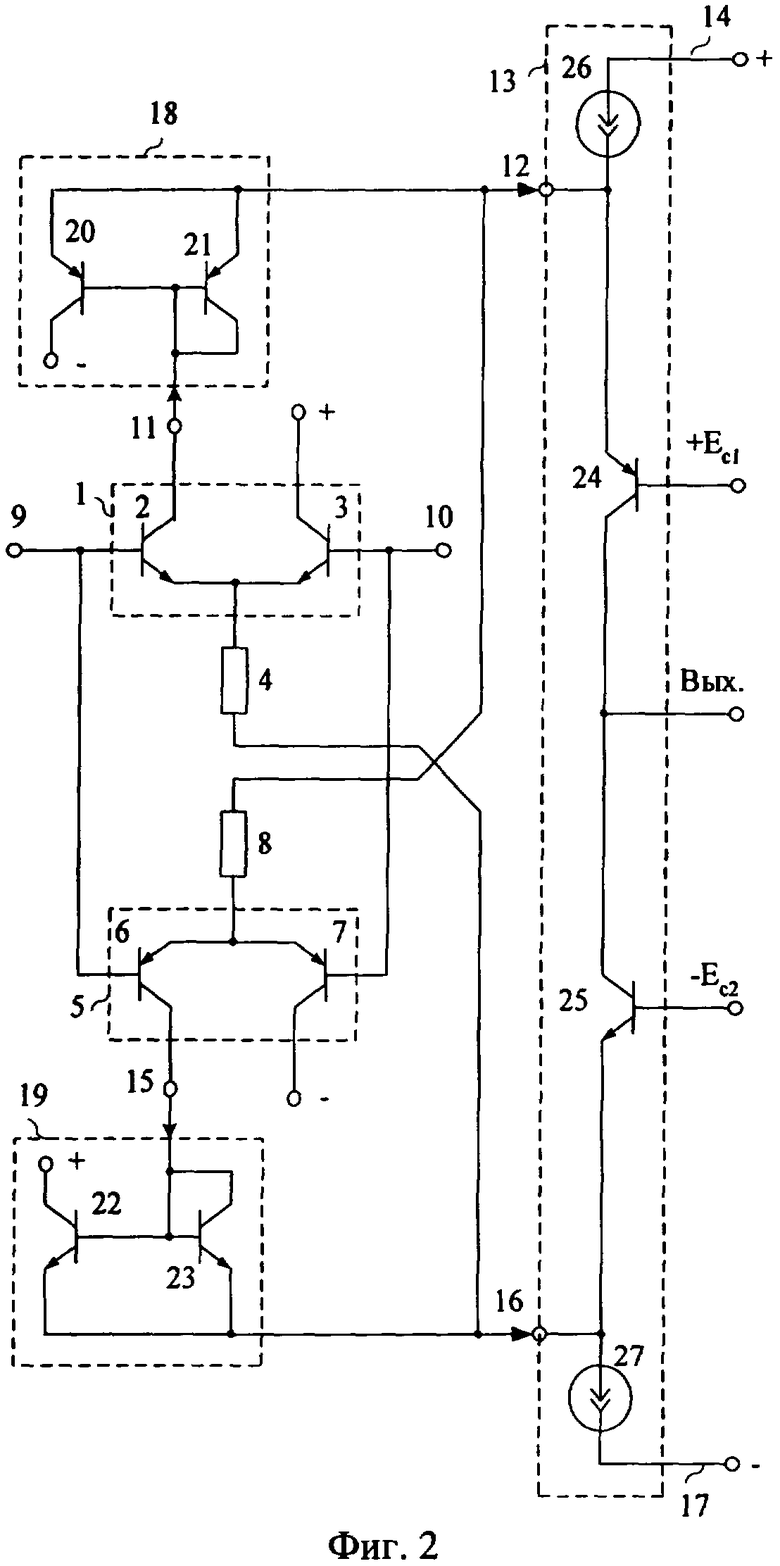

Схема заявляемого устройства в соответствии с п.1, п.2, п.3 формулы изобретения показана на фиг.2.

На фиг.3 показан ДУ, соответствующий п.4 формулы изобретения.

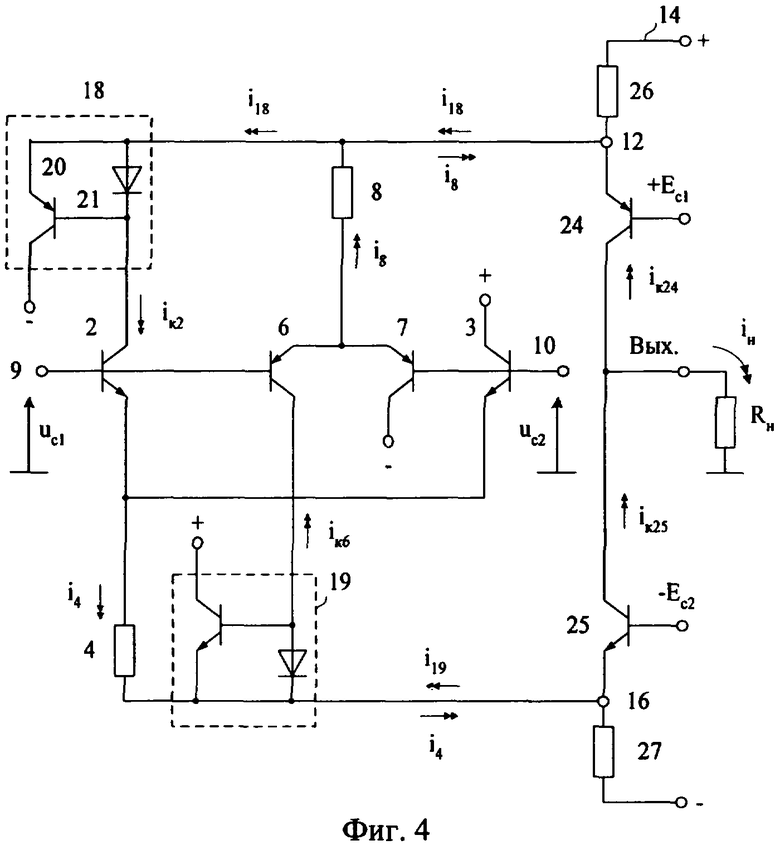

Переменные токи и напряжения в заявляемом ДУ фиг.2 при воздействии на его входы 9 и 10 синфазного сигнала uc1=uc2=uc показаны на фиг.4.

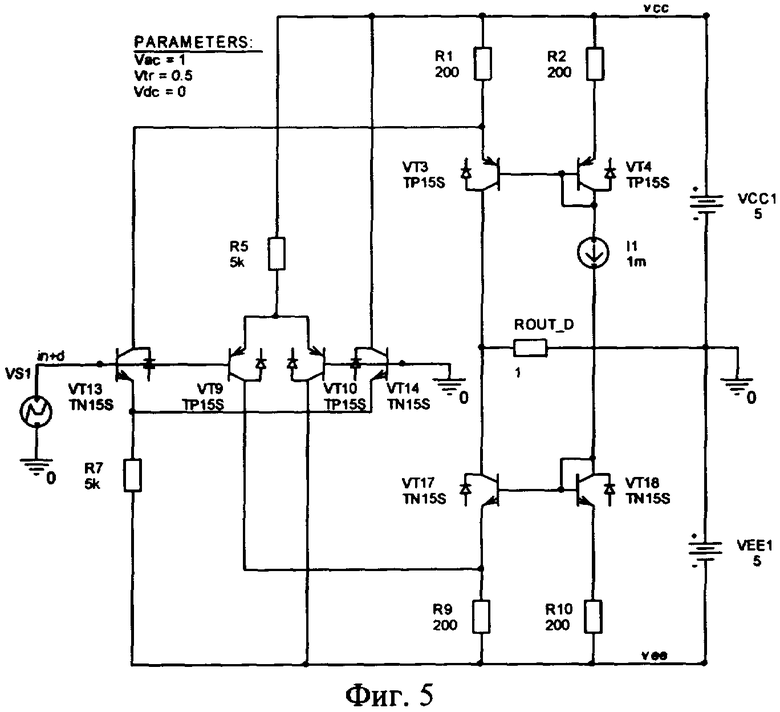

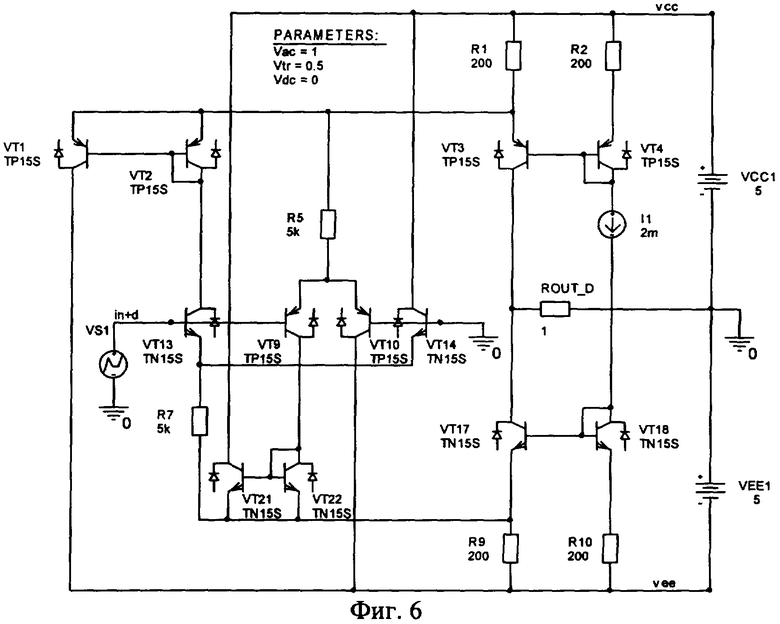

На фиг.5 изображена схема ДУ-прототипа фиг.1, которая исследовалась авторами в среде PSpice на степень ослабления синфазных сигналов. На фиг.6 показана схема заявляемого ДУ (при воздействии на его входы синфазного сигнала Uc) на моделях интегральных транзисторов ФГУП НПП «Пульсар».

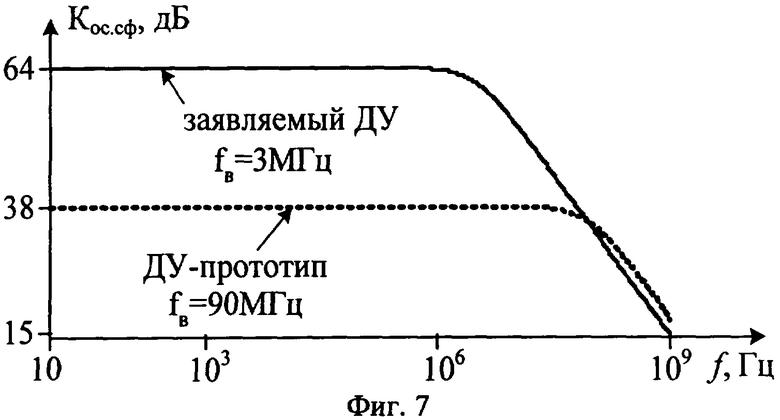

На фиг.7 показаны результаты компьютерного моделирования схем фиг.5 и фиг.6 - зависимость их коэффициентов ослабления входных синфазных сигналов (Кос.сф) от частоты.

Дифференциальный усилитель фиг.2 содержит первый 1 входной параллельно-балансный каскад на n-p-n транзисторах 2 и 3 и первом токостабилизирующем двухполюснике 4 в его общей эмиттерной цепи, первый вывод которого соединен с эмиттерами n-p-n транзисторов 2 и 3, второй 5 входной параллельно-балансный каскад на p-n-p транзисторах 6 и 7 и втором токостабилизирующем двухполюснике 8 в его общей эмиттерной цепи, первый вывод которого соединен с эмиттерами p-n-p транзисторов 6 и 7, причем синфазные входы первого 1 и второго 5 входных параллельно-балансных каскадов соединены друг с другом и являются входами двухтактного дифференциального усилителя 9 и 10, выход 11 первого 1 входного параллельно-балансного каскада соединен с первым входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, выход 15 второго 5 входного параллельно-балансного каскада соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17. Выход 11 первого входного параллельно-балансного каскада 1 соединен с первым входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, через первый дополнительный неинвертирующий усилитель тока 18, второй вывод второго токостабилизирующего двухполюсника 8 соединен со входом 12 выходного каскада 13, согласованным с шиной положительного источника питания 14, выход 15 второго 5 входного параллельно-балансного каскада соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17, через второй дополнительный неинвертирующий усилитель тока 19, а второй вывод первого токостабилизирующего двухполюсника 4 соединен со входом 16 выходного каскада 13, согласованным с шиной отрицательного источника питания 17.

В схеме фиг.2, в соответствии с п.2 формулы изобретения, первый 18 и второй 19 дополнительные неинвертирующие усилители тока выполнены в виде токовых зеркал на p-n-p (20, 21) и n-p-n (22, 23) транзисторах, входами которых являются входы токовых зеркал, а выходами - общие эмиттерные цепи токовых зеркал.

В схеме фиг.2, в соответствии с п.3 формулы изобретения, выходной каскад 13 выполнен на p-n-p 24 и n-p-n 25 выходных транзисторах, включенных по схеме с общей базой, коллекторы которых объединены и подключены к выходу двухтактного дифференциального усилителя, а эмиттеры являются соответственно входами 12 и 16, согласованными соответственно с шиной положительного 14 и отрицательного 17 источников питания.

В схеме фиг.3, соответствующей п.4 формулы изобретения, выходной каскад 13 выполнен в виде дополнительных токовых зеркал 28, 29 на вспомогательных p-n-p транзисторах 30, 31 и вспомогательных n-p-n транзисторах 32, 33, причем выходы этих дополнительных токовых зеркал 28, 29 соединены с выходом двухтактного дифференциального усилителя, а входы дополнительных токовых зеркал 28 и 29 являются входами 12 и 16 выходного каскада 13, согласованными соответственно с шинами положительного (14) и отрицательного (17) источников питания.

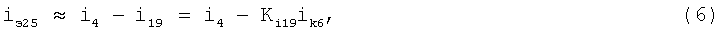

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.4.

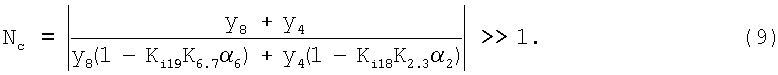

Изменение входного синфазного напряжения на входах ДУ 9 и 10 на величину uc=uc1=uc2 приводят к изменению токов через двухполюсники 4 и 8:

где y8, y4 - проводимости двухполюсников 8 и 4.

Поэтому коллекторные токи транзисторов 6 и 2:

где K6.7(K2.3)≈0,5 - коэффициент деления тока i8 между эмиттерами транзисторов VT6, VT7 (VT2, VT3);

α6≈1, α2≈1 - коэффициенты передачи по току эмиттеров транзисторов VT6, VT2.

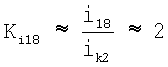

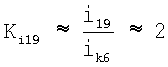

Коллекторные токи транзисторов 2 и 6 усиливаются в Ki18 ≈ Ki19 ≈ 2-раз дополнительными неинвертирующими усилителями тока 18, 19 (токовыми зеркалами 18 и 19). Поэтому эмиттерные токи транзисторов 24 и 25 (при больших сопротивлениях двухполюсников 26 и 27)

где  - коэффициент усиления по току дополнительного неинвертирующего усилителя тока 18 (токового зеркала 18);

- коэффициент усиления по току дополнительного неинвертирующего усилителя тока 18 (токового зеркала 18);

- коэффициент усиления по току дополнительного неинвертирующего усилителя тока 19 (токового зеркала 19).

- коэффициент усиления по току дополнительного неинвертирующего усилителя тока 19 (токового зеркала 19).

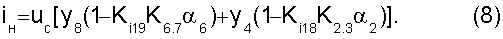

После преобразования (5) и (6) с учетом (3) и (4) можно найти ток нагрузки ДУ, обусловленный синфазным сигналом uc:

или

Учитывая, что Ki19K6.7α6≈1, Ki18K2.3α2≈1, из (8) следует, что в заявляемом ДУ существенно ослабляется влияние проводимостей y8 и y4 на передачу синфазного сигнала на выход, которая в идеальном случае должна быть близка нулю. С другой стороны, выходной ток, обусловленный синфазным сигналом в ДУ-прототипе (фиг.1)

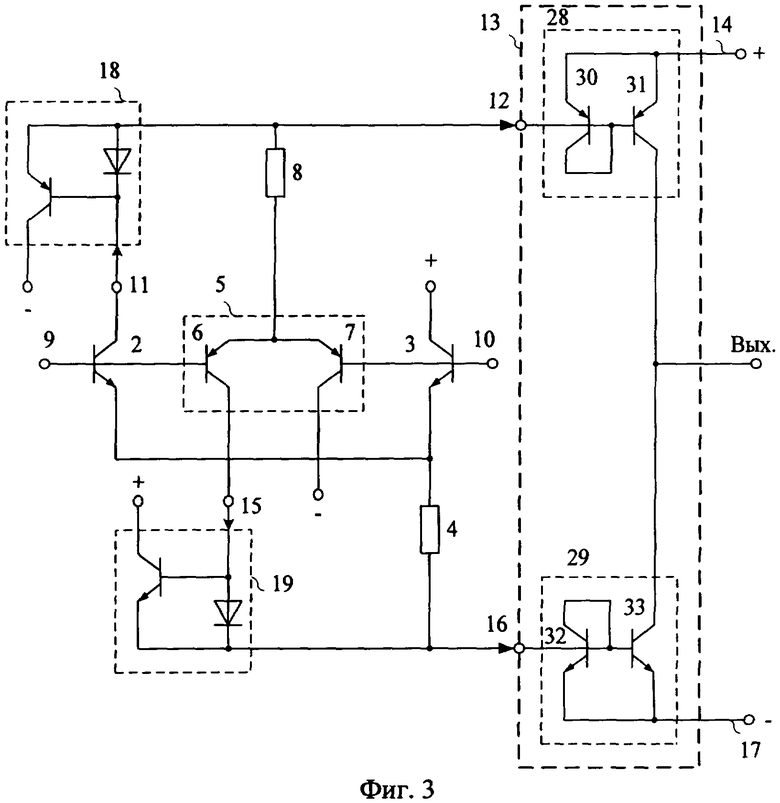

Поэтому коэффициент ослабления входных синфазных сигналов в ДУ фиг.2 улучшается в сравнении с ДУ-прототипом как минимум в Nc-раз:

Аналогичным анализом можно показать, что в заявляемом ДУ улучшается в Nn≈Nc - раз и другой важный параметр коэффициент подавления помехи по питанию.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва) (фиг.7) - заявляемый ДУ имеет более чем на порядок лучшие значения коэффициента ослабления входных синфазных сигналов (26 дБ).

Литература

1. Патент США №5.291.149, фиг.1.

2. Патент РФ №2.193.273, H03f 3/45.

3. Справочник: операционные усилители и компараторы (Авербух В.Д. и др.). - М.: Изд-во «Додэка-XXI», 2001, С.122 (НА2539).

4. Патент США №4.600.893, фиг.3.

5. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989, стр.103, рис.6. 11 (ОУ НА5190).

6. Патент США №4.837.522, фиг.1.

7. Ежков Ю.С.Справочник по схемотехнике усилителей. - М., Радиософт, 2002, с.87, рис.5.21.

8. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с. - стр.156 рис.4.25.

9. Патент США №4.131.809, H03FK.

10. Патент США №3.323.070 H03F 3/45.

11. Патент ЕР №1.351.381 A1, H03F 3/30.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2008 |

|

RU2346387C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХПРОЦЕССА | 2014 |

|

RU2571579C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346388C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319294C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

Изобретение относится к области радиотехники и связи для использования в качестве устройства усиления разности двух сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов. Двухтактный дифференциальный усилитель (ДДУ) содержит первый (1) и второй (5) входные параллельно-балансный каскады (ПБК) на n-p-n (2) и (3), p-n-p (6) и (7) транзисторах (Т), и первом (4) и втором (8) токостабилизирующих двухполюсниках (ТД) в их общей эмиттерной цепи, причем синфазные входы первого (1) и второго (5) ПБК соединены друг с другом и являются входами (9) и (10) ДДУ, выход (11) соединен с первым входом (12) выходного каскада (13), выход (15) соединен со входом (16) выходного каскада (13). Выход (11) соединен с первым входом (12) выходного каскада (13) через первый дополнительный неинвертирующий усилитель тока (18), второй вывод второго ТД (8) соединен со входом (12) выходного каскада (13), выход (15) соединен со входом (16) выходного каскада (13) через второй дополнительный неинвертирующий усилитель тока (19), а второй вывод первого ТД (4) соединен со входом (16) выходного каскада (13). 3 з.п. ф-лы, 7 ил.

| US 5291149 А, 01.03.1994 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| US 4600893, 15.07.1986 | |||

| US 4131809, 26.12.1978 | |||

| ПОЛОННИКОВ Д.Е | |||

| Операционные усилители: Принципы построения, теория, схемотехника | |||

| - М.: Энергоатомиздат, 1983, с.156, рис.4.25. | |||

Авторы

Даты

2008-03-10—Публикация

2006-07-13—Подача