Предлагаемое изобретение относится к устройствам согласования высокоомного выхода пьезодатчика для контроля вибрации и измерительной аппаратуры для контроля вибрации.

Пьезоэлектрические датчики вибрации на собственной резонансной частоте имеют существенный подъем амплитудно-частотной характеристики. Превышение резонансного уровня над уровнем рабочего участка может превышать 50 дБ. При наличии входных воздействий на датчик составляющих с частотами, близкими к резонансным, или при ударных воздействиях формируются сигналы высокой амплитуды за счет подъема амплитудно-частотной характеристики на резонансе, который вызывает перегрузку входного усилителя, при которой этот усилитель попадает в состояние насыщения, что нарушает правильную работу обратной связи этого усилителя. В результате на выходе этого усилителя формируется длительный сигнал высокой амплитуды, представляющий ложное низкочастотное колебание, искажающее результаты измерения [IES Recommended Practice 012.1. Handbook for Dynamic Data Acquisition and Analysis// Institute of Environmental Sciences. 1995 г., стр.101].

Для подавления высокочастотных составляющих, воздействующих на датчик, можно использовать механические фильтры между датчиком и контролируемым объектом. Однако коэффициент подавления таких фильтров может быть недостаточным, а само их применение зачастую невозможно, например, если датчик установлен в области высокой температуры [Там же, стр.267].

Известны схемы зарядовых усилителей, в которых для подавления высокочастотных составляющих между датчиком и инвертирующим входом операционного усилителя, который соединен с выходом операционного усилителя через конденсатор обратной связи и через резистор обратной связи, включен дополнительный резистор [Holterman J. and J. van Amerongen, “Analog Controller Design for an Active Damping Element”, in: Proceedings of the 3rd IFAC Symposium on Mechatronic Systems, in: 3rd IFAC Symposium on Mechatronic Systems, September 6-8, 2004, Sydney, Australia, pp 313-318, 2004. Стр.316, Fig.3 и 4].

Недостатком данного технического решения является необходимость использования резисторов очень большой величины, подключенных к входу усилителя. Действительно, для обеспечения большого коэффициента передачи емкость конденсатора в цепи обратной связи должна быть сравнительно маленькой, что определяет большую величину резистора в цепи обратной связи, который определяет нижнюю граничную частоту пропускания. Для эффективного подавления высокочастотных составляющих величина входного резистора должна быть большой, причем для обеспечения интегрирующей передаточной функции - больше, чем величина резистора в цепи обратной связи. При такой величине резисторов не только возрастают шумы усилителя, но сам усилитель практически перестает быть усилителем заряда, утрачивая присущие ему преимущества (низкую зависимость от характеристик кабеля связи датчика и усилителя, пониженный уровень шумов и т.д.). Следует отметить, что включение резистора большой величины между пьезодатчиком и входом усилителя особенно сильно сказывается при повышении температуры пьезодатчика, поскольку его сопротивление утечки и сопротивление утечки соединительного кабеля быстро уменьшаются с ростом температуры и формируемые датчиком заряды стекают через эти резисторы, а не через указанный высокоомный резистор, что снижает коэффициент преобразования с ростом температуры.

Представленные ниже варианты изобретения объединены общим изобретательским замыслом, а именно реализация во входном каскаде усилителя заряда для пьезоакселерометра перехода от виброускорения к виброскорости, что подразумевает обеспечение высокого коэффициента преобразования для низкочастотных составляющих и низкого для высокочастотных составляющих. При этом, поскольку операционный усилитель такого каскада имеет спадающую амплитудно-частотную характеристику, на низких частотах можно обеспечить высокое усиление, следовательно, обеспечивается хорошее соотношение сигнал/шум и снимаются ограничения, связанные с присущим операционным усилителем спадом коэффициента передачи с повышением рабочей частоты. В указанных технических решениях такие характеристики достигаются за счет подключения резистора и конденсатора обратной связи с выходу частотно-зависимого делителя, коэффициент деления которого уменьшается с ростом частоты для частот выше нижней граничной частоты пропускания усилителя заряда. Таким образом, в качестве выходного сигнала у предлагаемого усилителя на выходе первого каскада сразу формируется сигнал, пропорциональный виброскорости, которая в соответствии с действующим ГОСТом является величиной, определяющей допустимость эксплуатации оборудования. В соответствии с требованиями нормативных документов измерению подлежит величина виброскорости [ГОСТ 26044-83. Вибрация. Аппаратура для эксплуатационного контроля вибрационного состояния энергетических гидротурбинных агрегатов. Общие технические требования. М., Издательство стандартов, 6 стр., а также ГОСТ Р ИСО 10816-1-97. Контроль состояния машин по результатам измерения вибрации на невращающихся частях. Часть 1. Общие требования. Госстандарт, Минск, 1998 г.. 12 стр. ГОСТ Р ИСО 8579-2-99. Контроль вибрационного состояния зубчатых механизмов при приемке. М., 2000, 14 с.].

Известен усилитель заряда для пьезоакселерометра, содержащий операционный усилитель, выход которого является выходом усилителя заряда и соединен с первым выводом резистора, второй вывод которого соединен с входом резисторного узла, входы операционного усилителя соединены с общей шиной и через соответственно конденсатор обратной связи и резистор обратной связи с вторым выходом резистора [Патент US №6407631, Н.кл. 330/69, МКИ H03F 3/45, 2002 г.].

Недостатками данного усилителя заряда является сравнительно низкая достоверность функционирования и малый динамический диапазон измеряемой виброскорости.

Известен усилитель заряда для пьезоакселерометра, содержащий операционный усилитель, выход которого является выходом усилителя заряда и соединен через первый резистор с первыми выводами второго и третьего резисторов, второй вывод второго резистора соединен с инвертирующим входом операционного усилителя, который через первый конденсатору соединен с первым выводом третьего резистора, второй вывод которого через второй конденсатор соединен с общей шиной [Datasheet Ultralow Noise, High speed BiFET Op Amp AD745. Analog Devices. стp.10, рис.16. 2002 г.].

Недостатком такого устройства является его сравнительно низкая помехоустойчивость, а также сравнительно низкий динамический диапазон измерения виброскорости и относительно низкая достоверность функционирования, поскольку высокочастотные сигналы и ударные воздействия могут перегружать усилитель и искажать сигнал на его выходе.

Наиболее близким к предложенному и выбранным в качестве прототипа является дифференциальный усилитель заряда, содержащий первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора [Патент США №4085349, МКИ H01L 41/04, Н.кл. 310/319, 18.04.1978 г.].

Недостатками данного устройства является относительно высокий уровень собственных шумов, что связано с использованием во входных цепях высоомных резисторов, что при большом коэффициенте преобразования на низких частотах приводит к большой низкочастотной составляющей, снижающей достоверность функционирования. Это связано также и с отсутствием привязки к уровню общей шины по постоянному току входных каскадов, что еще более увеличивает низкочастотный дрейф сигналов и помехи.

Целью изобретения является повышение достоверности функционирования и расширение динамического диапазона измеряемых виброскоростей.

Поставленная цель в первом варианте исполнения достигается тем, что в дифференциальном усилителе заряда, содержащем первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора, выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с общей шиной, которая через четвертый дополнительный резистор соединена с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, вторая обкладка вспомогательного конденсатора соединена с общей шиной, которая соединена с первой обкладкой третьего дополнительного конденсатора, вторая обкладка которого соединена через пятый дополнительный резистор с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора, величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора, величины емкости вспомогательного конденсатора на величину сопротивления вспомогательного резистора и величины емкости третьего дополнительного конденсатора на величину сопротивления пятого дополнительного резистора больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Другое отличие состоит в том, что ограничительный узел содержит первый и второй ограничительные резисторы, первый и второй ограничительные конденсаторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также через соответственно первый и второй ограничительные конденсаторы с первым и вторым выходами ограничительного узла.

Другое отличие состоит в том, что ограничительный узел содержит первый и второй ограничительные резисторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

Другое отличие состоит в том, что в ограничительном узле первый и второй входы обратной связи соединены соответственно с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

Другое отличие состоит в том, что ограничительный элемент содержит двуханодный стабилитрон, первый анод которого является первым входом ограничительного элемента, второй анод двуханоного стабилитрона соединен с анодом первого и катодом второго диодов, катод и анод которых объединены и являются вторым входом ограничительного элемента.

Поставленная цель в втором варианте исполнения достигается тем, что в дифференциальном усилителе заряда, содержащем первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с общей шиной, которая через четвертый дополнительный резистор соединена с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, второй вывод вспомогательного резистора соединен с общей шиной, которая соединена через пятый дополнительный резистор с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора и величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора и величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Поставленная цель в третьем варианте исполнения достигается тем, что в дифференциальном усилителе заряда, содержащем первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора, выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, вторая обкладка вспомогательного конденсатора соединена с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора, величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора и величины емкости вспомогательного конденсатора на величину сопротивления вспомогательного резистора больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Поставленная цель в четвертом варианте исполнения достигается тем, что в дифференциальном усилителе заряда, содержащем первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, второй вывод вспомогательного резистора соединен с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора, величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Предлагаемое техническое решение иллюстрируется представленными ниже чертежами и графиками.

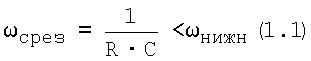

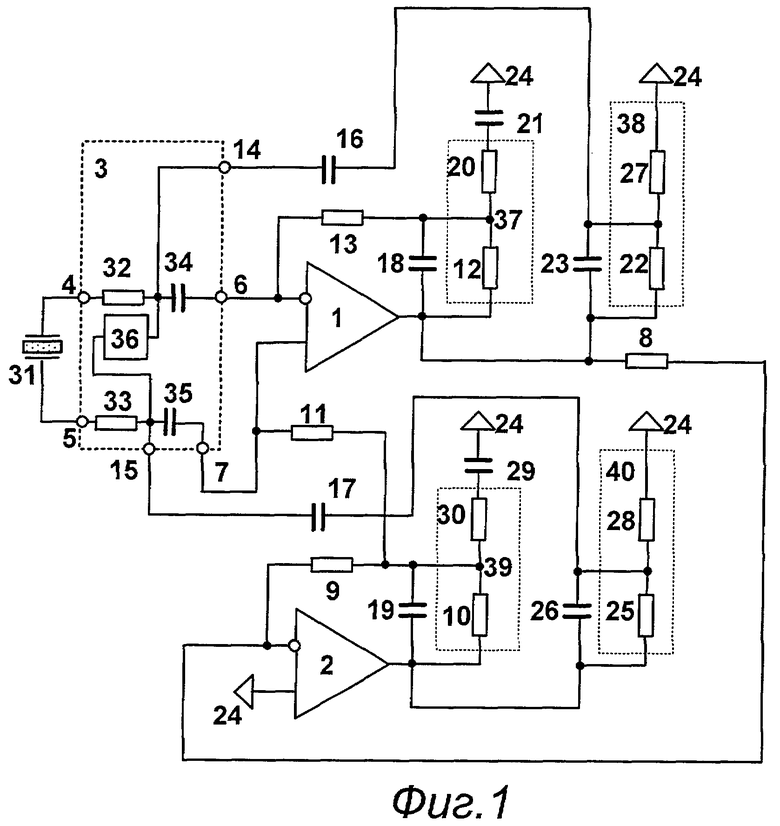

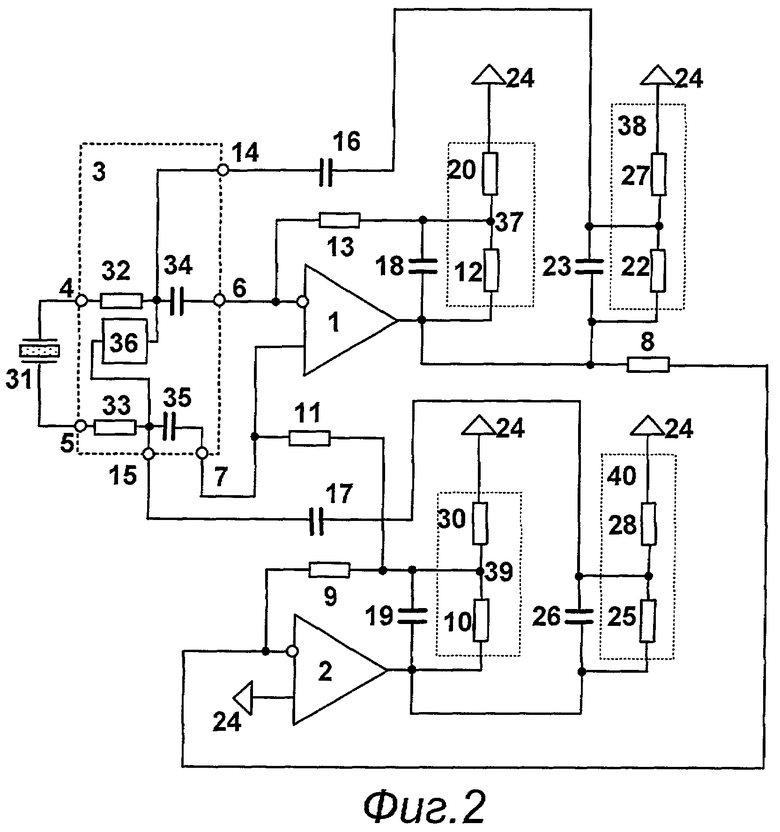

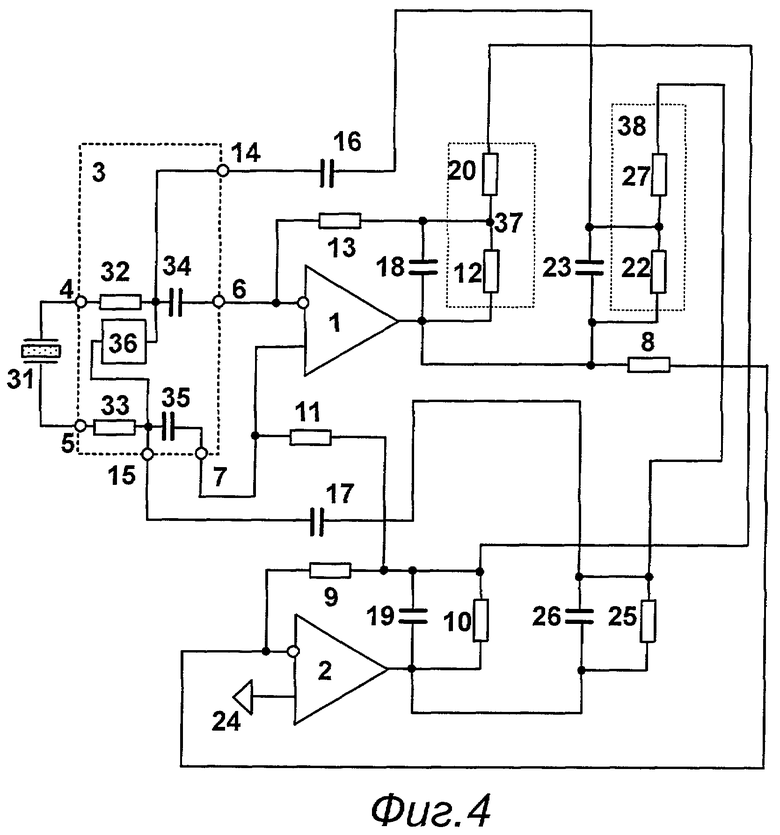

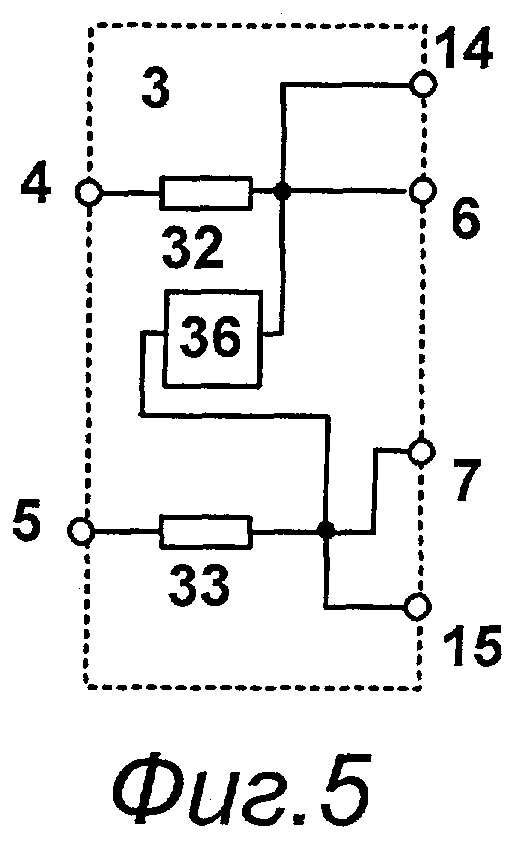

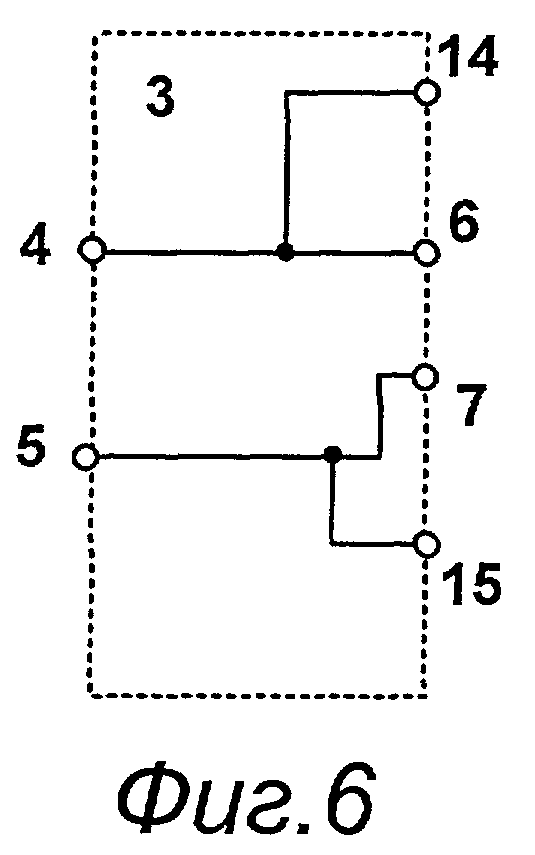

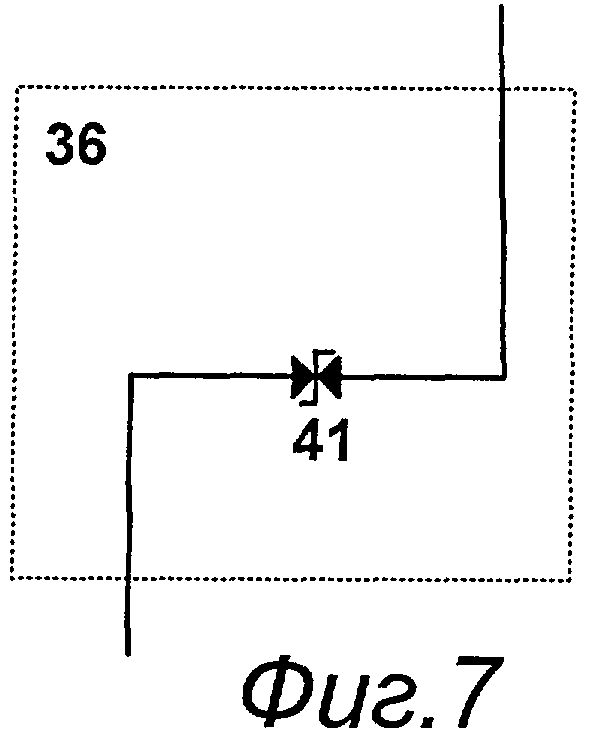

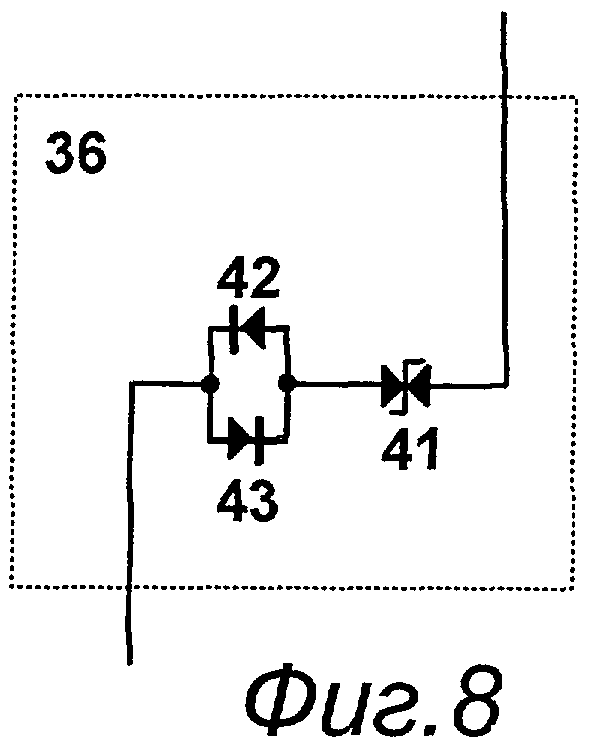

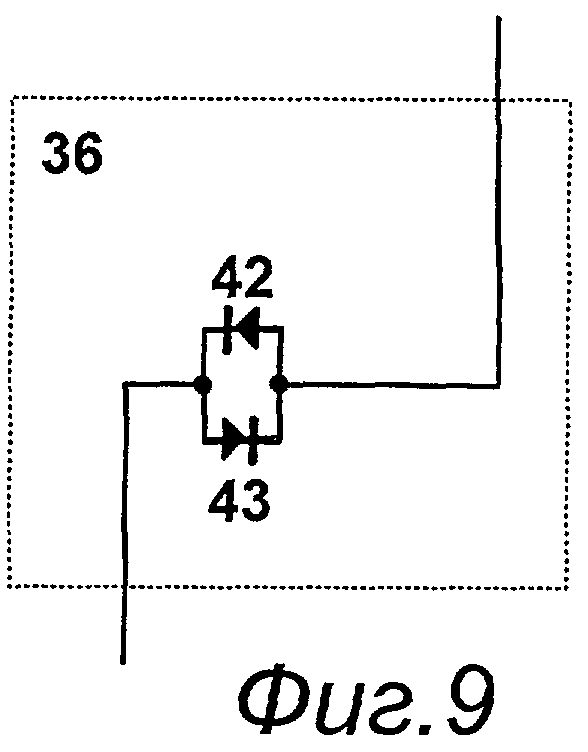

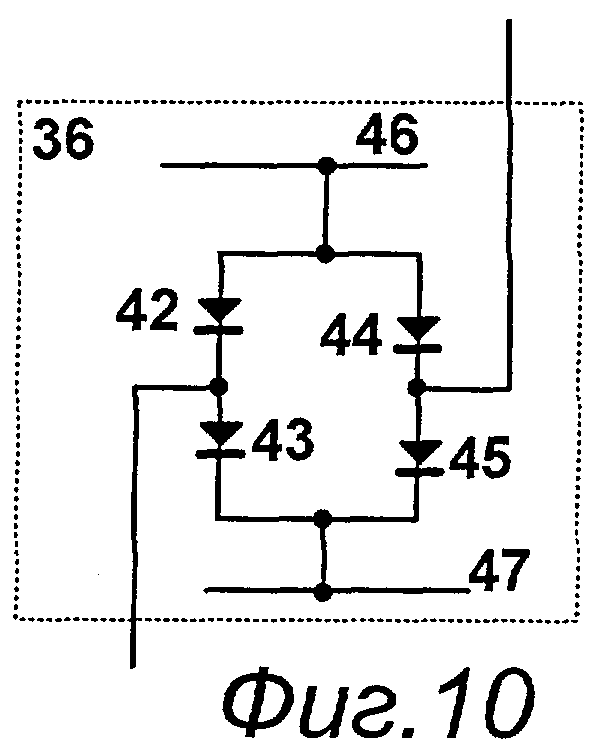

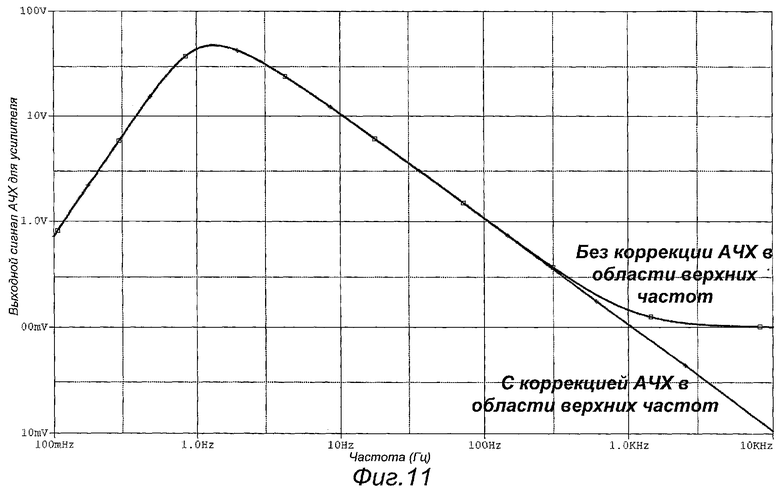

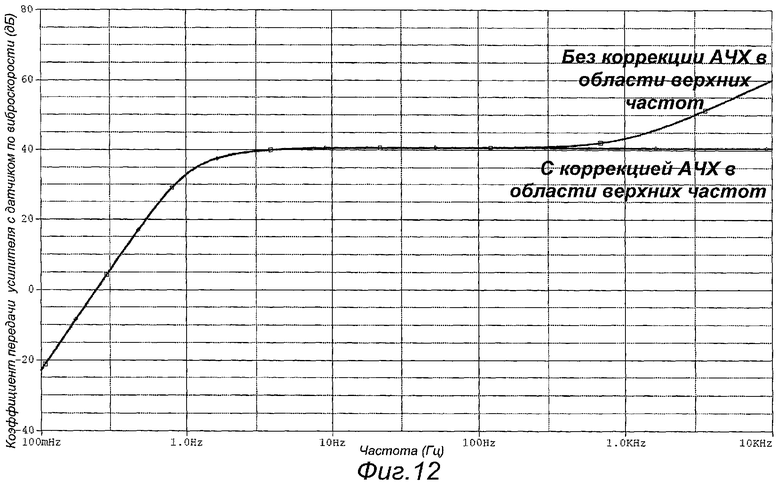

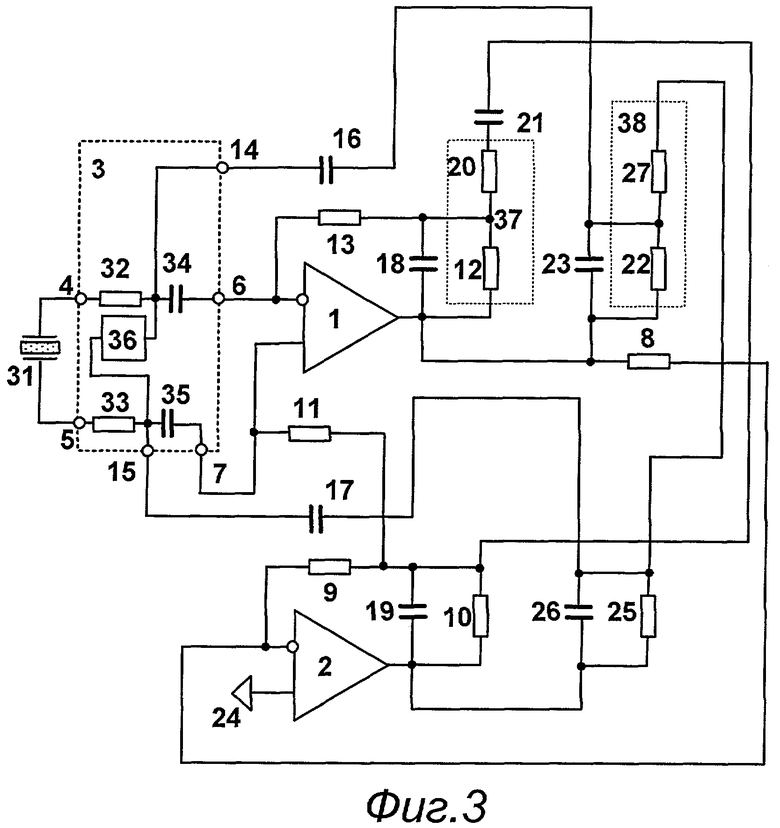

На фиг.1-4 показаны структурные схемы дифференциальных усилителей заряда для пьезодатчиков по соответственно первому, второму, третьему и четвертому вариантам исполнения. На фиг.5-6 приведены варианты структурных схем ограничительного узла, а на фиг.7-10 показаны варианты возможных реализаций ограничительного элемента. Фиг.11 и 12 показывают амплитудно-частотные характеристики, поясняющие работу предлагаемого устройства.

Дифференциальный усилитель заряда, как показано на фиг.1, содержит первый 1 и второй 2 операционные усилители, ограничительный узел 3, первый 4 и второй 5 входы которого являются входами дифференциального усилителя заряда, первый 6 и второй 7 выходы ограничительного узла 3 соединены с инверсным и прямым входами первого операционного усилителя 1, выход которого соединен через первый резистор 8 с инверсным входом второго операционного усилителя 2, который через второй резистор 9 соединен с его выходом, который соединен с первым выводом первого резистора 10 обратной связи, второй вывод которого соединен с первым выводом второго резистора 11 обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя 1, выход которого соединен с первым выводом третьего резистора 12 обратной связи, второй вывод которого соединен с первым выводом четвертого резистора 13 обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя 1, первый и второй входы обратной связи ограничительного узла 3 соединены с первыми обкладками соответственно первого 16 и второго 17 конденсаторов обратной связи, а выходы первого 1 и второго 2 операционного усилителей соединены с первыми обкладками соответственно третьего 18 и четвертого 19 конденсаторов обратной связи, второй вывод третьего резистора 12 обратной связи соединен с первым выводом вспомогательного резистора 20, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора 21, выход первого операционного усилителя 1 соединен с первым выводом первого дополнительного резистора 22 и первой обкладкой первого дополнительного конденсатора 23, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора 22, прямой вход второго операционного усилителя 2 соединен с общей шиной 24, выход второго операционного усилителя 2 соединен с первым выводом второго дополнительного резистора 25 и первой обкладкой второго дополнительного конденсатора 26, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора 25, который соединен со второй обкладкой второго конденсатора 17 обратной связи, вторая обкладка первого конденсатора 16 обратной связи соединена с вторым выводом первого дополнительного резистора 22, который соединен через третий дополнительный резистор 27 с общей шиной 24, которая через четвертый дополнительный резистор 28 соединена с вторым выводом второго дополнительного резистора 25, вторые обкладки третьего 18 и четвертого 19 конденсаторов обратной связи соединены соответственно с вторыми выводами третьего 12 и первого 10 резисторов обратной связи, вторая обкладка вспомогательного конденсатора 21 соединена с общей шиной 24, которая соединена с первой обкладкой третьего дополнительного конденсатора 29, вторая обкладка которого соединена через пятый дополнительный резистор 30 с вторым выводом первого резистора 10 обратной связи, причем произведения величины емкости третьего конденсатора 18 обратной связи на величину сопротивления третьего резистора 12 обратной связи, величины емкости четвертого конденсатора 19 обратной связи на величину сопротивления первого резистора 10 обратной связи, величины емкости первого дополнительного конденсатора 23 на величину сопротивления первого дополнительного резистора 22, величины емкости второго дополнительного конденсатора 26 на величину сопротивления второго дополнительного резистора 25, величины емкости вспомогательного конденсатора 21 на величину сопротивления вспомогательного резистора 20 и величины емкости третьего дополнительного конденсатора 29 на величину сопротивления пятого дополнительного резистора 30 больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Пьезодатчик 31 может быть подключен к входам 4 и 5 устройства непосредственно или через дифференциальную линию связи.

Ограничительный узел, как показано на фиг.1, может содержать первый 32 и второй 33 ограничительные резисторы, первый 34 и второй 35 ограничительные конденсаторы и ограничительный элемент 36, который включен между первым 14 и вторым 15 входами обратной связи, которые соединены через соответственно первый 32 и второй 33 резисторы обратной связи с первым 4 и вторым 5 входами ограничительного узла, а также через соответственно первый 34 и второй 35 ограничительные конденсаторы с первым 6 и вторым 7 выходами ограничительного узла 3.

Резисторы 12 и 20 образуют первый делитель 37, резисторы 22 и 27 образуют второй делитель 38, резисторы 10 и 30 образуют третий делитель 39, а резисторы 25 и 28 образуют четвертый делитель 40.

Дифференциальный усилитель заряда, как показано на фиг.2, содержит первый 1 и второй 2 операционные усилители, ограничительный узел 3, первый 4 и второй 5 входы которого являются входами дифференциального усилителя заряда, первый 6 и второй 7 выходы ограничительного узла 3 соединены с инверсным и прямым входами первого операционного усилителя 1, выход которого соединен через первый резистор 8 с инверсным входом второго операционного усилителя 2, который через второй резистор 9 соединен с его выходом, который соединен с первым выводом первого резистора 10 обратной связи, второй вывод которого соединен с первым выводом второго резистора 11 обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя 1, выход которого соединен с первым выводом третьего резистора 12 обратной связи, второй вывод которого соединен с первым выводом четвертого резистора 13 обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя 1, первый и второй входы обратной связи ограничительного узла 3 соединены с первыми обкладками соответственно первого 16 и второго 17 конденсаторов обратной связи, а выходы первого 1 и второго 2 операционного усилителей соединены с первыми обкладками соответственно третьего 18 и четвертого 19 конденсаторов обратной связи, второй вывод третьего резистора 12 обратной связи соединен с первым выводом вспомогательного резистора 20, выход первого операционного усилителя 1 соединен с первым выводом первого дополнительного резистора 22 и первой обкладкой первого дополнительного конденсатора 23, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора 22, прямой вход второго операционного усилителя 2 соединен с общей шиной 24, выход второго операционного усилителя 2 соединен с первым выводом второго дополнительного резистора 25 и первой обкладкой второго дополнительного конденсатора 26, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора 25, который соединен со второй обкладкой второго конденсатора 17 обратной связи, вторая обкладка первого конденсатора 16 обратной связи соединена с вторым выводом первого дополнительного резистора 22, который соединен через третий дополнительный резистор 27 с общей шиной 24, которая через четвертый дополнительный резистор 28 соединена с вторым выводом второго дополнительного резистора 25, вторые обкладки третьего 18 и четвертого 19 конденсаторов обратной связи соединены соответственно с вторыми выводами третьего 12 и первого 10 резисторов обратной связи, второй вывод вспомогательного резистора 20 соединен с общей шиной 24, которая соединена через пятый дополнительный резистор 30 с вторым выводом первого резистора 10 обратной связи, причем произведения величины емкости третьего конденсатора 18 обратной связи на величину сопротивления третьего резистора 12 обратной связи, величины емкости четвертого конденсатора 19 обратной связи на величину сопротивления первого резистора 10 обратной связи, величины емкости первого дополнительного конденсатора 23 на величину сопротивления первого дополнительного резистора 22, величины емкости второго дополнительного конденсатора 26 на величину сопротивления второго дополнительного резистора 25 и величины емкости третьего дополнительного конденсатора 29 на величину сопротивления пятого дополнительного резистора 30 больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Дифференциальный усилитель заряда, как показано на фиг.3, содержит первый 1 и второй 2 операционные усилители, ограничительный узел 3, первый 4 и второй 5 входы которого являются входами дифференциального усилителя заряда, первый 6 и второй 7 выходы ограничительного узла 3 соединены с инверсным и прямым входами первого операционного усилителя 1, выход которого соединен через первый резистор 8 с инверсным входом второго операционного усилителя 2, который через второй резистор 9 соединен с его выходом, который соединен с первым выводом первого резистора 10 обратной связи, второй вывод которого соединен с первым выводом второго резистора 11 обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя 1, выход которого соединен с первым выводом третьего резистора 12 обратной связи, второй вывод которого соединен с первым выводом четвертого резистора 13 обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя 1, первый и второй входы обратной связи ограничительного узла 3 соединены с первыми обкладками соответственно первого 16 и второго 17 конденсаторов обратной связи, а выходы первого 1 и второго 2 операционного усилителей соединены с первыми обкладками соответственно третьего 18 и четвертого 19 конденсаторов обратной связи, второй вывод третьего резистора 12 обратной связи соединен с первым выводом вспомогательного резистора 20, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора 21, выход первого операционного усилителя 1 соединен с первым выводом первого дополнительного резистора 22 и первой обкладкой первого дополнительного конденсатора 23, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора 22, прямой вход второго операционного усилителя 2 соединен с общей шиной 24, выход второго операционного усилителя 2 соединен с первым выводом второго дополнительного резистора 25 и первой обкладкой второго дополнительного конденсатора 26, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора 25, который соединен со второй обкладкой второго конденсатора 17 обратной связи, вторая обкладка первого конденсатора 16 обратной связи соединена с вторым выводом первого дополнительного резистора 22, который соединен через третий дополнительный резистор 27 с вторым выводом второго дополнительного резистора 25, вторые обкладки третьего 18 и четвертого 19 конденсаторов обратной связи соединены соответственно с вторыми выводами третьего 12 и первого 10 резисторов обратной связи, вторая обкладка вспомогательного конденсатора 21 соединена с вторым выводом первого резистора 10 обратной связи, причем произведения величины емкости третьего конденсатора 18 обратной связи на величину сопротивления третьего резистора 12 обратной связи, величины емкости четвертого конденсатора 19 обратной связи на величину сопротивления первого резистора 10 обратной связи, величины емкости первого дополнительного конденсатора 23 на величину сопротивления первого дополнительного резистора 22, величины емкости второго дополнительного конденсатора 26 на величину сопротивления второго дополнительного резистора 25, величины емкости вспомогательного конденсатора 21 на величину сопротивления вспомогательного резистора 20 больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Дифференциальный усилитель заряда, как показано на фиг.4, содержит первый 1 и второй 2 операционные усилители, ограничительный узел 3, первый 4 и второй 5 входы которого являются входами дифференциального усилителя заряда, первый 6 и второй 7 выходы ограничительного узла 3 соединены с инверсным и прямым входами первого операционного усилителя 1, выход которого соединен через первый резистор 8 с инверсным входом второго операционного усилителя 2, который через второй резистор 9 соединен с его выходом, который соединен с первым выводом первого резистора 10 обратной связи, второй вывод которого соединен с первым выводом второго резистора 11 обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя 1, выход которого соединен с первым выводом третьего резистора 12 обратной связи, второй вывод которого соединен с первым выводом четвертого резистора 13 обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя 1, первый и второй входы обратной связи ограничительного узла 3 соединены с первыми обкладками соответственно первого 16 и второго 17 конденсаторов обратной связи, а выходы первого 1 и второго 2 операционного усилителей соединены с первыми обкладками соответственно третьего 18 и четвертого 19 конденсаторов обратной связи, второй вывод третьего резистора 12 обратной связи соединен с первым выводом вспомогательного резистора 20, выход первого операционного усилителя 1 соединен с первым выводом первого дополнительного резистора 22 и первой обкладкой первого дополнительного конденсатора 23, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора 22, прямой вход второго операционного усилителя 2 соединен с общей шиной 24, выход второго операционного усилителя 2 соединен с первым выводом второго дополнительного резистора 25 и первой обкладкой второго дополнительного конденсатора 26, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора 25, который соединен со второй обкладкой второго конденсатора 17 обратной связи, вторая обкладка первого конденсатора 16 обратной связи соединена с вторым выводом первого дополнительного резистора 22, который соединен через третий дополнительный резистор 27 с общей шиной 24, которая через четвертый дополнительный резистор 28 соединена с вторым выводом второго дополнительного резистора 25, вторые обкладки третьего 18 и четвертого 19 конденсаторов обратной связи соединены соответственно с вторыми выводами третьего 12 и первого 10 резисторов обратной связи, второй вывод вспомогательного резистора 20 соединен с вторым выводом первого резистора 10 обратной связи, причем произведения величины емкости третьего конденсатора 18 обратной связи на величину сопротивления третьего резистора 12 обратной связи, величины емкости четвертого конденсатора 19 обратной связи на величину сопротивления первого резистора 10 обратной связи, величины емкости первого дополнительного конденсатора 23 на величину сопротивления первого дополнительного резистора 22, величины емкости второго дополнительного конденсатора 26 на величину сопротивления второго дополнительного резистора 25 больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

Ограничительный узел 3, как показано на фиг.5, содержит первый 32 и второй 33 ограничительные резисторы и ограничительный элемент 36, который включен между первым 14 и вторым 15 входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым 4 и вторым 5 входами ограничительного узла 3, а также непосредственно с соответственно первым 6 и вторым 7 выходами ограничительного узла 3.

В ограничительном узле, как показано на фиг.6, первый 14 и второй 15 входы обратной связи соединены соответственно с первым 4 и вторым 5 входами ограничительного узла 3, а также непосредственно с соответственно первым 6 и вторым 7 выходами ограничительного узла.

Как показано на фиг.7, ограничительный элемент 36 может быть выполнен в виде двуханодного стабилитрона 41.

Ограничительный элемент 36, как показано на фиг.8, содержит двуханодный стабилитрон 41, первый анод которого является первым входом ограничительного элемента 36, второй анод двуханоного стабилитрона 41 соединен с анодом первого 42 и катодом второго 43 диодов, катод и анод которых объединены и являются вторым входом ограничительного элемента 36.

Ограничительный элемент 36, как показано на фиг.9, содержит первый 42 и второй 43 диоды, первый вход ограничительного элемента 36 соединен с анодом первого 42 и катодом второго 43 диодов, катод и анод которых объединены и являются вторым входом ограничительного элемента 36.

Ограничительный элемент 36, как показано на фиг.10, содержит первый 42, второй 43, третий 44 и четвертый 45 диоды, первый вход ограничительного элемента соединен с катодом первого 42 и анодом второго 43 диодов, второй вход ограничительного элемента соединен с катодом третьего 44 и анодом четвертого 45 диодов, аноды первого 42 и третьего 44 диодов соединены с шиной 46 отрицательного питания устройства, шина 47 положительного питания которого соединена с катодами второго 43 и четвертого 45 диодов.

Устройство работает следующим образом.

Зарядовый сигнал от пьезодатчика 31 поступает на входы 4 и 5 и проходит через ограничительный узел 3 на вход операционного усилителя 1. Данный усилитель охвачен отрицательной обратной связью через конденсаторы обратной связи 16 и 17 и резисторы обратной связи 11 и 13. Напряжение с выхода операционного усилителя 1 поступает на цепи обратной связи с делителя 37, образованного параллельно соединенными резистором 12 и конденсатором 18, и резистором 20. Поскольку в делителе имеется конденсатор 18, коэффициент передачи зависит от частоты. На прямой вход операционного усилителя через аналогичные цепи сигнал подается с выхода операционного усилителя 3, который инвертирует выходной сигнал операционного усилителя 1.

Если постоянные времени RC цепочек C18R12, C19R10, C23R22, C26R25, где индекс соответствует номеру элемента на чертеже, удовлетворяют условию:

В рабочей области частот выше ωнижн - нижней границы рабочей частоты, обеспечивается коэффициент передачи со спадом амплитудно-частотной характеристики с крутизной 6 дБ/октаву, что соответствует интегрированию виброускорения, воздействующего на датчик 31, и формированию на выходе операционного усилителя 1 сигнала, пропорционального виброскорости.

На верхних частотах, когда реактивное сопротивление конденсаторов 18, 19 и 23, 26 много меньше сопротивления резисторов 12,10 и резисторов 22, 25, коэффициент деления выходного напряжения операционного усилителя 1 близок к единице и коэффициент преобразования определяется только величиной конденсаторов 16 и 17, а на частотах, близких к нижней граничной частоте, коэффициент передачи увеличивается пропорционально увеличению коэффициента деления.

Таким образов в рабочем диапазоне частот усилитель обеспечивает реализацию частотной зависимости коэффициента передачи, соответствующей интегрированию входного сигнала ускорения, причем это выполняется непосредственно во входном каскаде - усилителе заряда. Поясняющие это АЧХ показаны на фиг.11 и 12. АЧХ по виброскорости показана на фиг.12. Как видно на этих характеристиках, АЧХ имеет подъем на частотах выше 1 кГц. Для дальнейшего расширения области рабочих частот в сторону ее увеличения в ограничительном узле можно использовать один или два ограничительных резистора сравнительно малой величины, обеспечивающих спад АЧХ в области частот выше 1 кГц. Обеспечить линейность АЧХ на таких частотах можно за счет использования в ограничительном узле резисторов 32 и 33 относительно небольшой величины. Эти резисторы не только могут ограничивать входные токи и напряжения для операционного усилителя 2, но и расширить равномерную АЧХ по виброскорости в область более высоких частот. Соответствующие скорректированные АЧХ также показаны на фиг.11 и 12 как продолжение линейных участков. Это позволяет получить результирующие АЧХ по скорости и ускорению с широким частотным диапазоном.

Даже значительный всплеск на АЧХ датчика, из-за интегрирующей характеристики во входном каскаде усилителя заряда обеспечивает отсутствие перегрузки при воздействии на датчик высокочастотных вибраций и ударов, что обеспечивает повышение достоверности функционирования усилителя заряда.

Для обеспечения требуемой АЧХ в зависимости от заданного диапазона частот необходимо обеспечить ряд соотношений между величинами емкостей и резисторов. Использование независимых цепей для организации цепей обратной связи по постоянному и по переменному току позволяет легко реализовать выбор номиналов резисторов и конденсаторов приемлемой величины.

Использование в устройствах, показанных на фиг.1 и фиг.3, конденсаторов 21 и 29 позволяет уменьшить коэффициент передачи цепей обратной связи по постоянному току на частотах ниже нижней рабочей частоты, что снижает низкочастотный шум и смещение нулевого уровня на выходе операционного усилителя 1. При этом постоянные времени RC цепочек C21R20, C29R30, где индекс соответствует номеру элемента на чертеже, удовлетворяют условию (1.1).

В зависимости от используемого ограничительного узла 4 можно обеспечить не только расширение рабочего диапазона частот в сторону верхних частот, но и обеспечить защиту входных цепей операционного усилителя и снизить влияние пироэффекта. При использовании ограничительных узлов, схема которого показана на фиг.5, обеспечивается ограничение входных токов и напряжений, но нет подавления влияния пироэффекта, а схема, показанная на фиг.6, требует минимальных затрат элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИММЕТРИЧНЫЙ УСИЛИТЕЛЬ ЗАРЯДА ДЛЯ ПЬЕЗОДАТЧИКА (ВАРИАНТЫ) | 2008 |

|

RU2370881C1 |

| УСИЛИТЕЛЬ ЗАРЯДА ДЛЯ ПЬЕЗОДАТЧИКА (ВАРИАНТЫ) | 2008 |

|

RU2370882C1 |

| УСИЛИТЕЛЬ ЗАРЯДА ДЛЯ ПЬЕЗОЭЛЕКТРИЧЕСКОГО ДАТЧИКА ВИБРАЦИИ (ВАРИАНТЫ) | 2008 |

|

RU2391770C2 |

| УСТРОЙСТВО ВИБРАЦИОННОГО КОНТРОЛЯ (ВАРИАНТЫ) | 2008 |

|

RU2375692C1 |

| УСТРОЙСТВО ДЛЯ ВИБРАЦИОННОГО КОНТРОЛЯ (ВАРИАНТЫ) | 2008 |

|

RU2376564C1 |

| СОГЛАСУЮЩЕЕ УСТРОЙСТВО С ДВУХПРОВОДНЫМ ИНТЕРФЕЙСОМ ДЛЯ ПЬЕЗОДАТЧИКА | 2009 |

|

RU2399916C1 |

| Устройство для управления электродвигателем | 1984 |

|

SU1252895A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Преобразователь перемещения в частоту | 1985 |

|

SU1317283A1 |

| ПЕРЕКЛЮЧАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 1996 |

|

RU2127479C1 |

Использование: для согласования высокоомного выхода пьезодатчика и измерительной аппаратуры. Технический результат заключается в расширении динамического диапазона измеряемых виброскоростей и повышении достоверности функционирования при сравнительно низком уровне собственных шумов. Дифференциальный усилитель заряда содержит первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй резисторы, четыре резистора обратной связи, четыре конденсатора обратной связи, пять дополнительных резисторов и три дополнительных конденсатора, вспомогательный резистор и вспомогательный конденсатор. Причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора, величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора, величины емкости вспомогательного конденсатора на величину сопротивления вспомогательного резистора больше величины, обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда. 4 н. и 16 з.п. ф-лы, 12 ил.

1. Дифференциальный усилитель заряда, содержащий первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора, отличающийся тем, что выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с общей шиной, которая через четвертый дополнительный резистор соединена с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, вторая обкладка вспомогательного конденсатора соединена с общей шиной, которая соединена с первой обкладкой третьего дополнительного конденсатора, вторая обкладка которого соединена через пятый дополнительный резистор с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора, величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора, величины емкости вспомогательного конденсатора на величину сопротивления вспомогательного резистора и величины емкости третьего дополнительного конденсатора на величину сопротивления пятого дополнительного резистора больше величины обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

2. Дифференциальный усилитель заряда по п.1, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы, первый и второй ограничительные конденсаторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также через соответственно первый и второй ограничительные конденсаторы с первым и вторым выходами ограничительного узла.

3. Дифференциальный усилитель заряда по п.1, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

4. Дифференциальный усилитель заряда по п.1, отличающийся тем, что в ограничительном узле первый и второй входы обратной связи соединены через соответственно с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

5. Дифференциальный усилитель заряда по п.2, отличающийся тем, что ограничительный элемент содержит двуханодный стабилитрон, первый анод которого является первым входом ограничительного элемента, второй анод двуханоного стабилитрона соединен с анодом первого и катодом второго диодов, катод и анод которых объединены и являются вторым входом ограничительного элемента.

6. Дифференциальный усилитель заряда, содержащий первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, отличающийся тем, что выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с общей шиной, которая через четвертый дополнительный резистор соединена с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, второй вывод вспомогательного резистора соединен с общей шиной, которая соединена через пятый дополнительный резистор с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора и величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора больше величины обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

7. Дифференциальный усилитель заряда по п.6, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы, первый и второй ограничительные конденсаторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также через соответственно первый и второй ограничительные конденсаторы с первым и вторым выходами ограничительного узла.

8. Дифференциальный усилитель заряда по п.6, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

9. Дифференциальный усилитель заряда по п.6, отличающийся тем, что в ограничительном узле первый и второй входы обратной связи соединены соответственно с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

10. Дифференциальный усилитель заряда по п.7, отличающийся тем, что ограничительный элемент содержит двуханодный стабилитрон, первый анод которого является первым входом ограничительного элемента, второй анод двуханоного стабилитрона соединен с анодом первого и катодом второго диодов, катод и анод которых объединены и являются вторым входом ограничительного элемента.

11. Дифференциальный усилитель заряда, содержащий первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, второй вывод которого соединен с первой обкладкой вспомогательного конденсатора, отличающийся тем, что выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, вторая обкладка вспомогательного конденсатора соединена с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора, величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора, величины емкости вспомогательного конденсатора на величину сопротивления вспомогательного резистора больше величины обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

12. Дифференциальный усилитель заряда по п.11, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы, первый и второй ограничительные конденсаторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также через соответственно первый и второй ограничительные конденсаторы с первым и вторым выходами ограничительного узла.

13. Дифференциальный усилитель заряда по п.11, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы, и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

14. Дифференциальный усилитель заряда по п.11, отличающийся тем, что в ограничительном узле первый и второй входы обратной связи соединены через соответственно с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

15. Дифференциальный усилитель заряда по п.12, отличающийся тем, что ограничительный элемент содержит двуханодный стабилитрон, первый анод которого является первым входом ограничительного элемента, второй анод двуханоного стабилитрона соединен с анодом первого и катодом второго диодов, катод и анод которых объедиены и являются вторым входом ограничительного элемента.

16. Дифференциальный усилитель заряда, содержащий первый и второй операционные усилители, ограничительный узел, первый и второй входы которого являются входами дифференциального усилителя заряда, первый и второй выходы ограничительного узла соединены с инверсным и прямым входами первого операционного усилителя, выход которого соединен через первый резистор с инверсным входом второго операционного усилителя, который через второй резистор соединен с его выходом, который соединен с первым выводом первого резистора обратной связи, второй вывод которого соединен с первым выводом второго резистора обратной связи, второй вывод которого соединен с прямым входом первого операционного усилителя, выход которого соединен с первым выводом третьего резистора обратной связи, второй вывод которого соединен с первым выводом четвертого резистора обратной связи, второй вывод которого соединен с инверсным входом первого операционного усилителя, первый и второй входы обратной связи ограничительного узла соединены с первыми обкладками соответственно первого и второго конденсаторов обратной связи, а выходы первого и второго операционного усилителя соединены с первыми обкладками соответственно третьего и четвертого конденсаторов обратной связи, второй вывод третьего резистора обратной связи соединен с первым выводом вспомогательного резистора, отличающийся тем, что выход первого операционного усилителя соединен с первым выводом первого дополнительного резистора и первой обкладкой первого дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом первого дополнительного резистора, прямой вход второго операционного усилителя соединен с общей шиной, выход второго операционного усилителя соединен с первым выводом второго дополнительного резистора и первой обкладкой второго дополнительного конденсатора, вторая обкладка которого соединена с вторым выводом второго дополнительного резистора, который соединен со второй обкладкой второго конденсатора обратной связи, вторая обкладка первого конденсатора обратной связи соединена с вторым выводом первого дополнительного резистора, который соединен через третий дополнительный резистор с вторым выводом второго дополнительного резистора, вторые обкладки третьего и четвертого конденсаторов обратной связи соединены соответственно с вторыми выводами третьего и первого резисторов обратной связи, второй вывод вспомогательного резистора соединен с вторым выводом первого резистора обратной связи, причем произведения величины емкости третьего конденсатора обратной связи на величину сопротивления третьего резистора обратной связи, величины емкости четвертого конденсатора обратной связи на величину сопротивления первого резистора обратной связи, величины емкости первого дополнительного конденсатора на величину сопротивления первого дополнительного резистора и величины емкости второго дополнительного конденсатора на величину сопротивления второго дополнительного резистора больше величины обратной величине нижней рабочей граничной частоты дифференциального усилителя заряда.

17. Дифференциальный усилитель заряда по п.16, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы, первый и второй ограничительные конденсаторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также через соответственно первый и второй ограничительные конденсаторы с первым и вторым выходами ограничительного узла.

18. Дифференциальный усилитель заряда по п.16, отличающийся тем, что ограничительный узел содержит первый и второй ограничительные резисторы и ограничительный элемент, который включен между первым и вторым входами обратной связи, которые соединены через соответственно первый и второй ограничительные резисторы с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

19. Дифференциальный усилитель заряда по п.16, отличающийся тем, что в ограничительном узле первый и второй входы обратной связи соединены через соответственно с первым и вторым входами ограничительного узла, а также непосредственно с соответственно первым и вторым выходами ограничительного узла.

20. Дифференциальный усилитель заряда по п.17, отличающийся тем, что ограничительный элемент содержит двуханодный стабилитрон, первый анод которого является первым входом ограничительного элемента, второй анод двуханоного стабилитрона соединен с анодом первого и катодом второго диодов, катод и анод которых объединены и являются вторым входом ограничительного элемента.

| US 4085349 A, 18.04.1978 | |||

| ЗАРЯДОЧУВСТВИТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2002 |

|

RU2219651C2 |

| Фрикционный амортизатор | 1943 |

|

SU65694A1 |

| Дифференциальный усилитель заряда | 1989 |

|

SU1670770A1 |

| Зарядочувствительный усилитель | 1990 |

|

SU1806442A3 |

| US 5371472 A, 06.12.1994. | |||

Авторы

Даты

2009-10-20—Публикация

2008-07-31—Подача