Область техники

Настоящее изобретение относится к беспроводным системам связи, более конкретно к эффективному обратному перемежению многосимвольных потоков.

Уровень техники

Беспроводные системы связи получили широкое распространение и обеспечивают связь различных типов, таких как голосовая связь и передача данных. Типичная беспроводная система передачи данных или сеть обеспечивает для множества пользователей доступ к одному или больше совместно используемым ресурсам. В системе могут использоваться самые разные методы множественного доступа, такие как мультиплексирование с частотным разделением (FDM, МЧР), мультиплексирование с временным разделением (TDM, МВР), мультиплексирование с кодовым разделением (CDM, МКР) и другие.

Примеры беспроводных сетей включают в себя системы передачи данных на основе сотовой связи. Ниже приведены несколько таких примеров: (1) "TIA/EIA-95-B Mobile Station-Base Station Compatibility Standard for Dual-Mode Wideband Spread Spectrum Cellular System" (стандарт IS-95), (2) стандарт, предложенный консорциумом "3rd Generation Partnership Project" (3GPP) и реализованный в наборе документов, включая № 3G TS 25.211, 3G TS 25.212, 3G TS 25.213 и 3G TS 25.214 (стандарт W-CDMA), (3) стандарт, предложенный консорциумом "3rd Generation Partnership Project 2" (3GPP2) и реализованный в документе "TR-45.5 Physical Layer Standard for cdma2000 Spread Spectrum Systems" (стандарт IS-2000), и (4) система с высокой скоростью передачи данных (HDR, ВСД), которая соответствует стандарту TIA/EIA/IS-856 (стандарт IS-856).

По мере продолжения повышения скорости передачи данных, поддерживаемой беспроводными системами передачи данных, соответственно, увеличиваются требования к вычислительным возможностям. Например, для увеличения скорости передачи данных можно использовать модуляцию более высокого порядка, а также можно повысить эффективность кодирования. Расчеты могут потребовать повышения тактовой частоты в мобильной станции или использования более эффективной архитектуры для снижения требований к вычислительным возможностям при обеспечении тех же рабочих характеристик системы. Например, стандарт HDR Release А устанавливает в качестве целевого значения скорость передачи данных 3,1 Мбит/с. Для поддержания такой скорости передачи данных требуется на 50 процентов увеличить сложность вычислений для обеспечения аналогичных рабочих характеристик, которые ранее достигались при наибольшей скорости передачи данных HDR 2,4 Мбит/с.

Одно из решений, направленных на увеличение вычислительных возможностей, состоит в повышении рабочей частоты схемы. Однако при повышении частоты повышается потребление энергии, что является нежелательным во многих случаях, например в мобильных станциях, работающих от батарей. Кроме того, некоторые схемы имеют ограничения, не позволяющие обеспечить их надежную работу за пределами некоторых значений тактовой частоты.

В системе, которая соответствует стандарту IS-856, турбодекодер может представлять собой единственный блок, для которого требуется наибольшая интенсивность вычислений. Количество времени, выделяемое для обратного перемежения и кодирования в системе HDR, должны быть меньше, чем временной интервал HDR, то есть 1,66 мс, для удовлетворения требования квитирования. Для выполнения этих требований, при поддержании тактовой частоты на приемлемом уровне, с точки зрения потребления энергии, необходимо уменьшить объем вычислений для обратного перемежения и декодирования.

Обычно символы требуется передавать в установленном порядке следования в декодер, такой как турбодекодер. В реализации согласно предшествующему уровню техники, для упрощения подачи демодулированных символов в декодер, символ может демодулироваться более чем один раз. Демодуляция символа может привести к получению более чем одного демодулированного символа на цикл (то есть 4 демодулированных символа из одного символа КАМ-16 (16 QAM, квадратурная амплитудная модуляция)). Таким образом, одновременно генерируются потоки данных из множества символов. Один результат каждой демодуляции сохраняется в запоминающем устройстве в каждый момент времени. При использовании одного запоминающего устройства и при сохранении демодулированных символов в порядке следования, может обеспечиваться возможность упрощения конструкции и/или конфигурации интерфейса данных, но при более высоких скоростях передачи данных такая архитектура может не обеспечить ширину полосы, требуемую для вычислений при декодировании с приемлемой тактовой частотой. Поэтому в известном уровне техники существует потребность в создании эффективного многосимвольного обратного перемежителя.

Сущность изобретения

Описанные варианты выполнения направлены на решение существующей в предшествующем уровне техники потребности в эффективном многосимвольном обратном перемежителе. В одном аспекте используется множество банков запоминающих устройств для приема и одновременного сохранения множества значений, таких, как значения мягкого решения, определенные из совокупности модуляций, в соответствии со структурой сохранения. В другом аспекте структура сохранения содержит множество циклов, выбранный поднабор множества банков запоминающих устройств и смещение адреса для использования при определении адреса для сохранения в соответствующих банках запоминающих устройств, обозначенных для каждого цикла. В еще одном аспекте доступ к сохраненным значениям может быть выполнен в порядке с последовательно увеличивающимся индексом, таким как адрес. Также присутствуют различные другие аспекты. Эти аспекты имеют преимущества, обеспечивающие возможность обратного перемежения множества значений символов эффективным образом, удовлетворяя, таким образом, ограничения по времени вычислений и требование сохранения энергии.

Краткое описание чертежей

На фиг. 1 показана общая блок-схема беспроводной системы связи, позволяющая поддерживать множество пользователей.

На фиг. 2 показана блок-схема беспроводного устройства связи, такого как мобильная станция или базовая станция.

На фиг. 3 представлен примерный вариант выполнения передатчика.

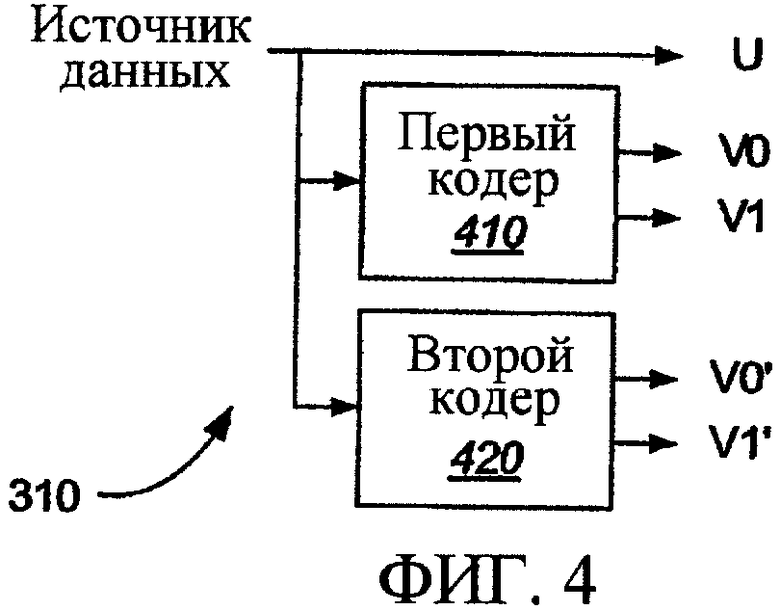

На фиг. 4 представлен примерный вариант выполнения кодера.

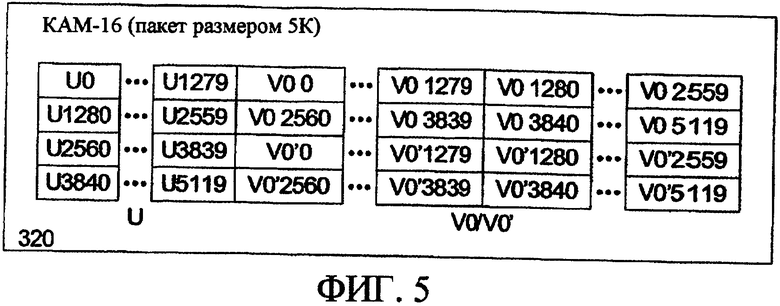

На фиг. 5 показан пример матрицы результатов перемежителя для пакета размером 5К, модулированного с использованием КАМ-16 и кодирования со скоростью 1/3.

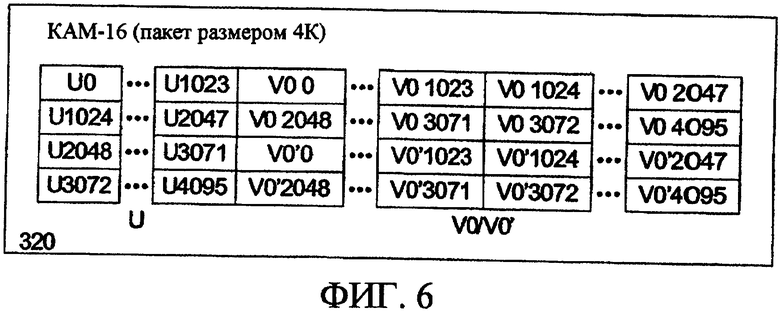

На фиг. 6 показан пример матрицы результатов перемежителя для пакета размером 4К, модулированного с использованием КАМ-16 и кодирования со скоростью 1/3.

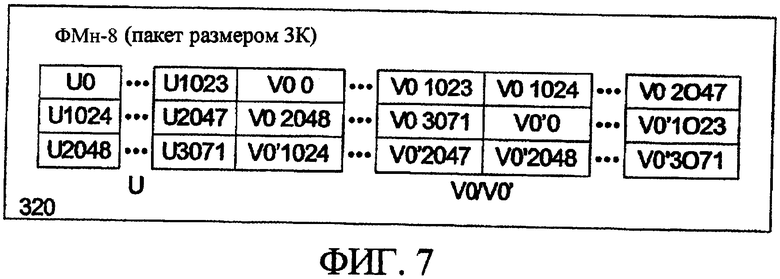

На фиг. 7 показан пример матрицы результатов перемежителя для пакета объемом 3К, модулированного с использованием ФМн-8 (8 PSK, фазовая манипуляция) и кодирования со скоростью 1/3.

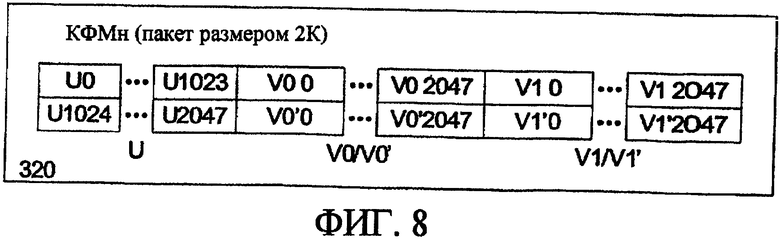

На фиг. 8 показан пример матрицы результатов перемежителя для пакета размером 2К, модулированного с использованием КФМн (КФМн, квадратурная фазовая манипуляция) и кодирования со скоростью 1/3.

На фиг. 9 представлен пример приемника.

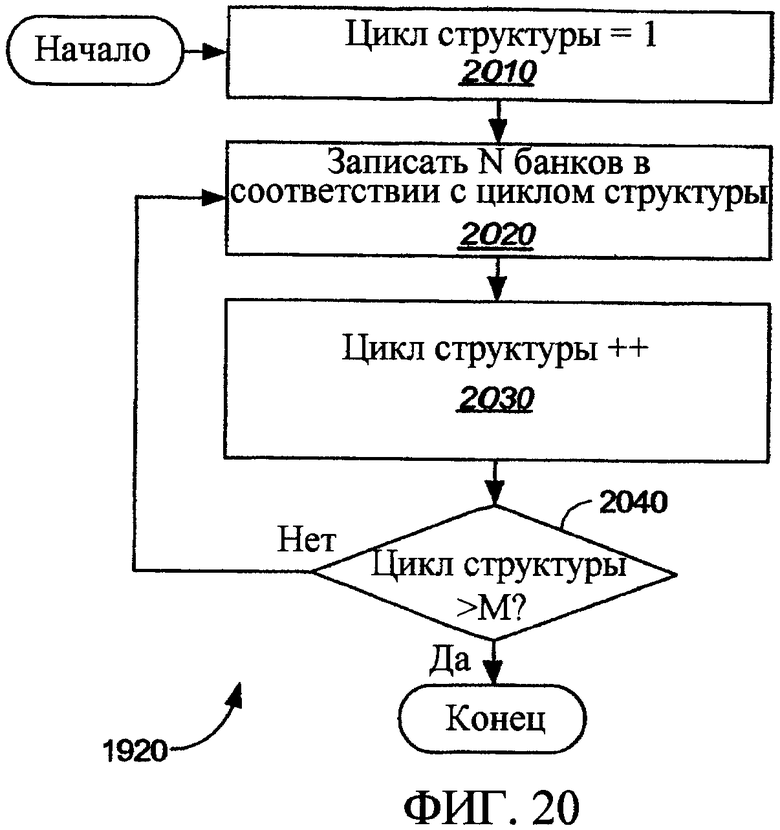

На фиг. 10 представлен пример обратного перемежителя.

На фиг. 11 представлена примерная структура сохранения для КАМ-16.

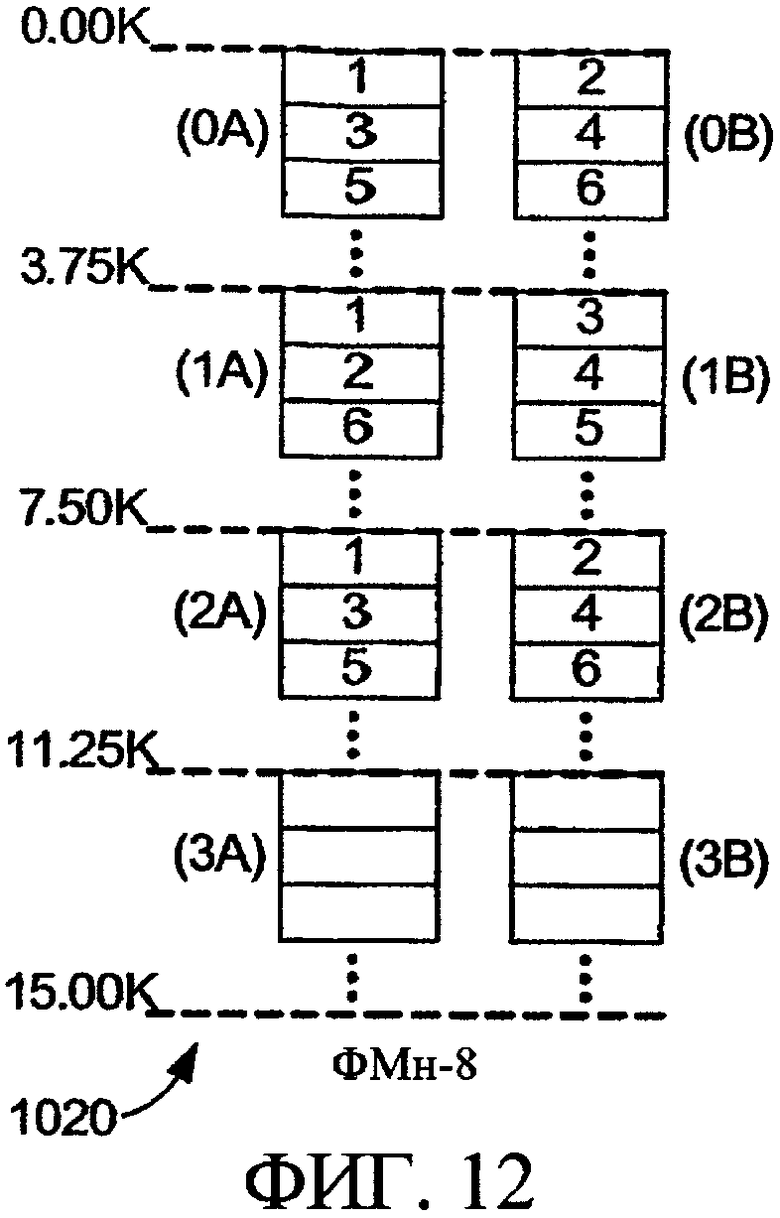

На фиг. 12 представлена примерная структура сохранения для ФМн-8.

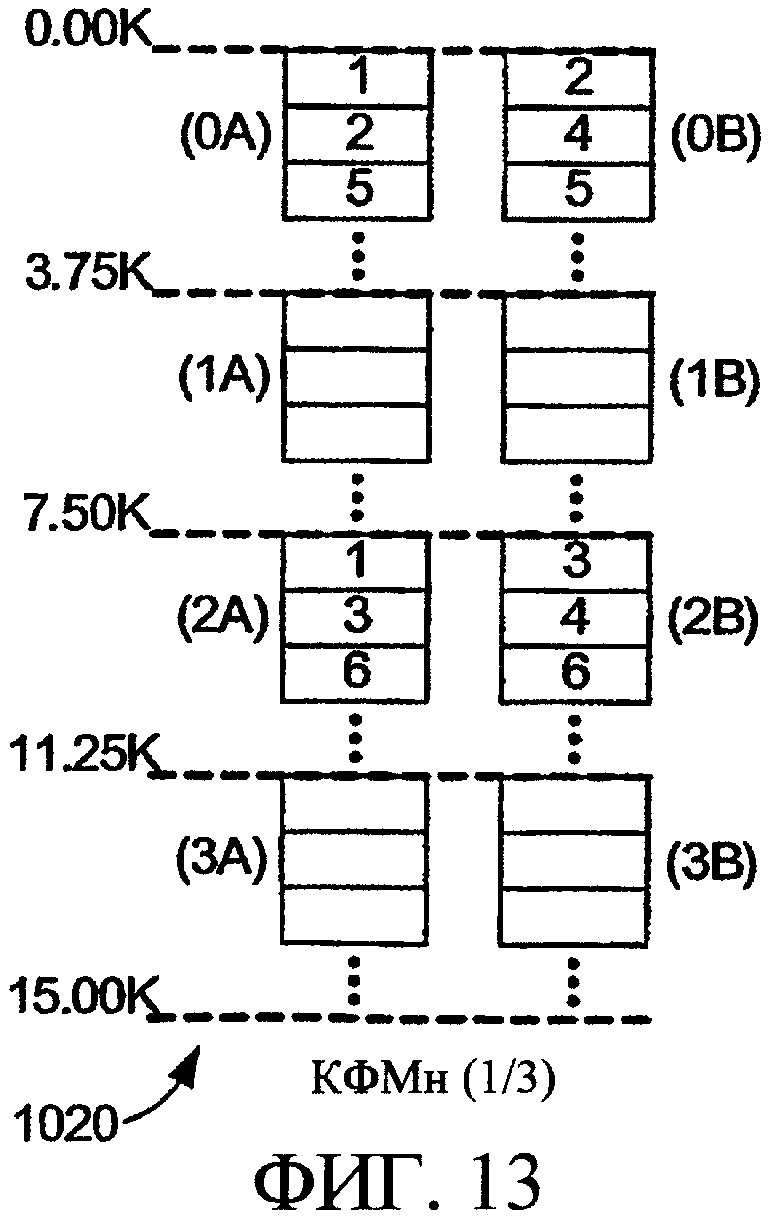

На фиг. 13 представлена примерная структура сохранения для КФМн со скоростью 1/3.

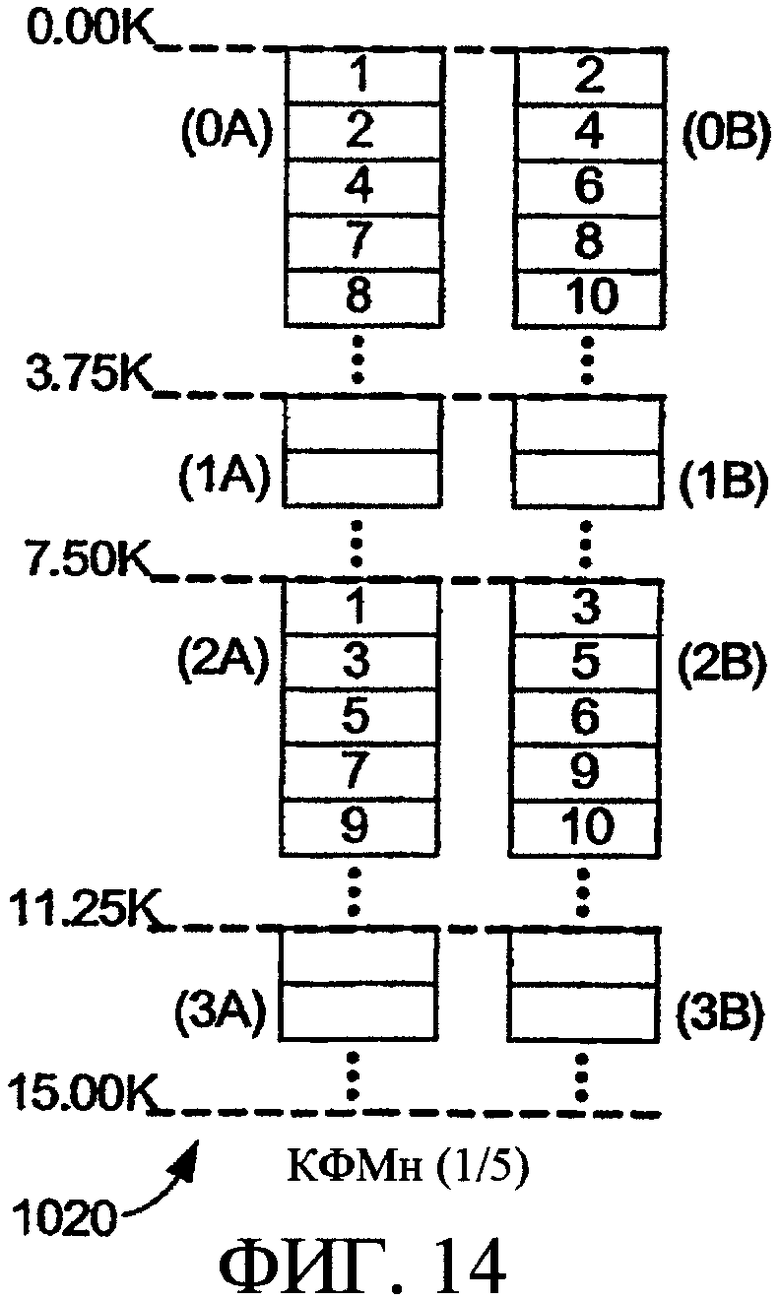

На фиг. 14 представлена примерная структура сохранения для КФМн со скоростью 1/5.

На фиг. 15 представлен пример конфигурации буфера символов для КАМ-16.

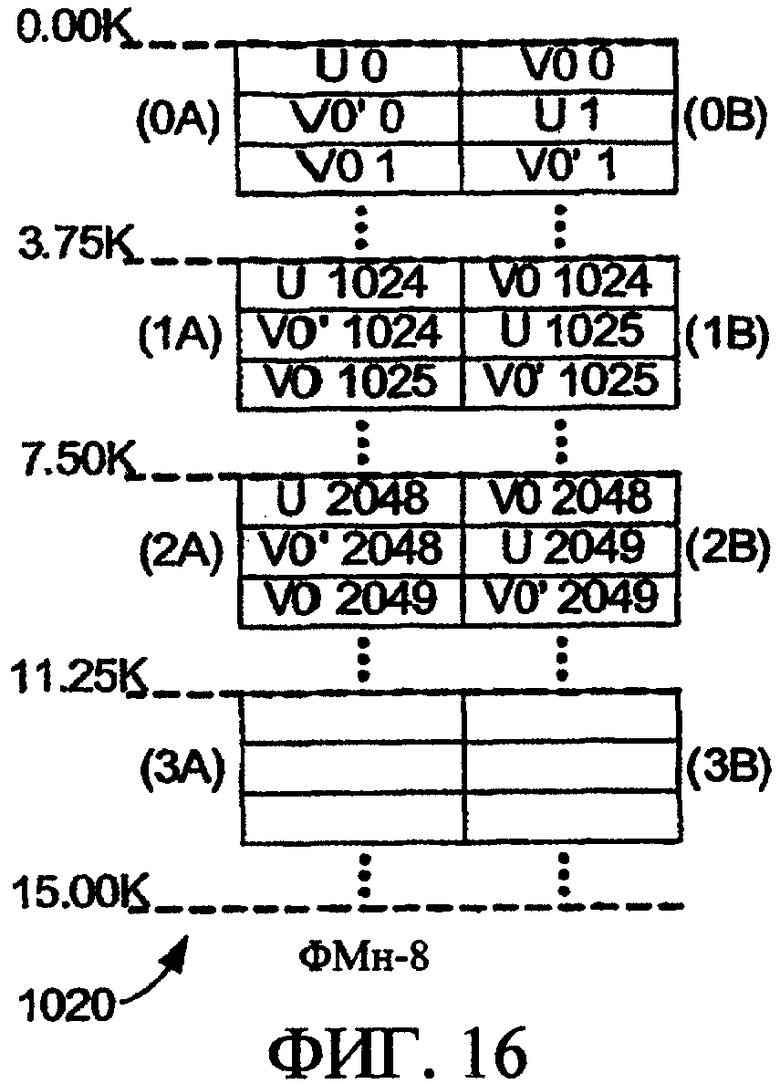

На фиг. 16 представлен пример конфигурации буфера символов для ФМн-8.

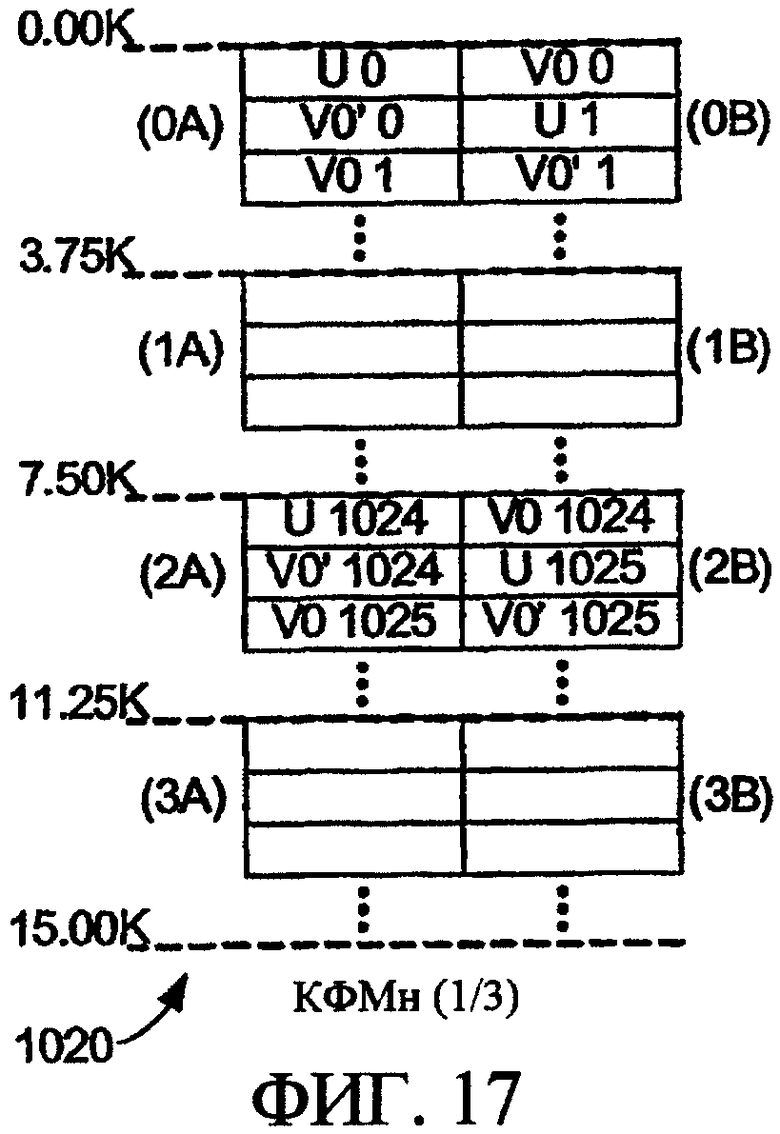

На фиг. 17 показан пример конфигурации буфера символов для КФМн со скоростью 1/3.

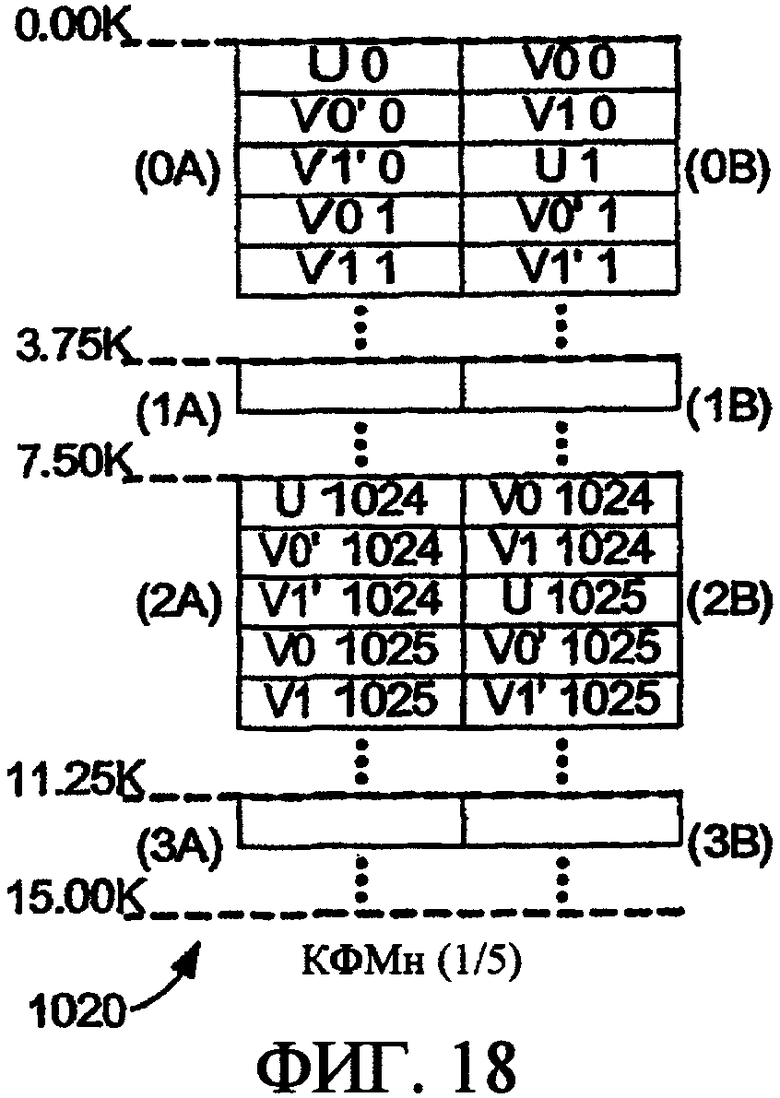

На фиг. 18 показан пример конфигурации буфера символов для КФМн со скоростью 1/5.

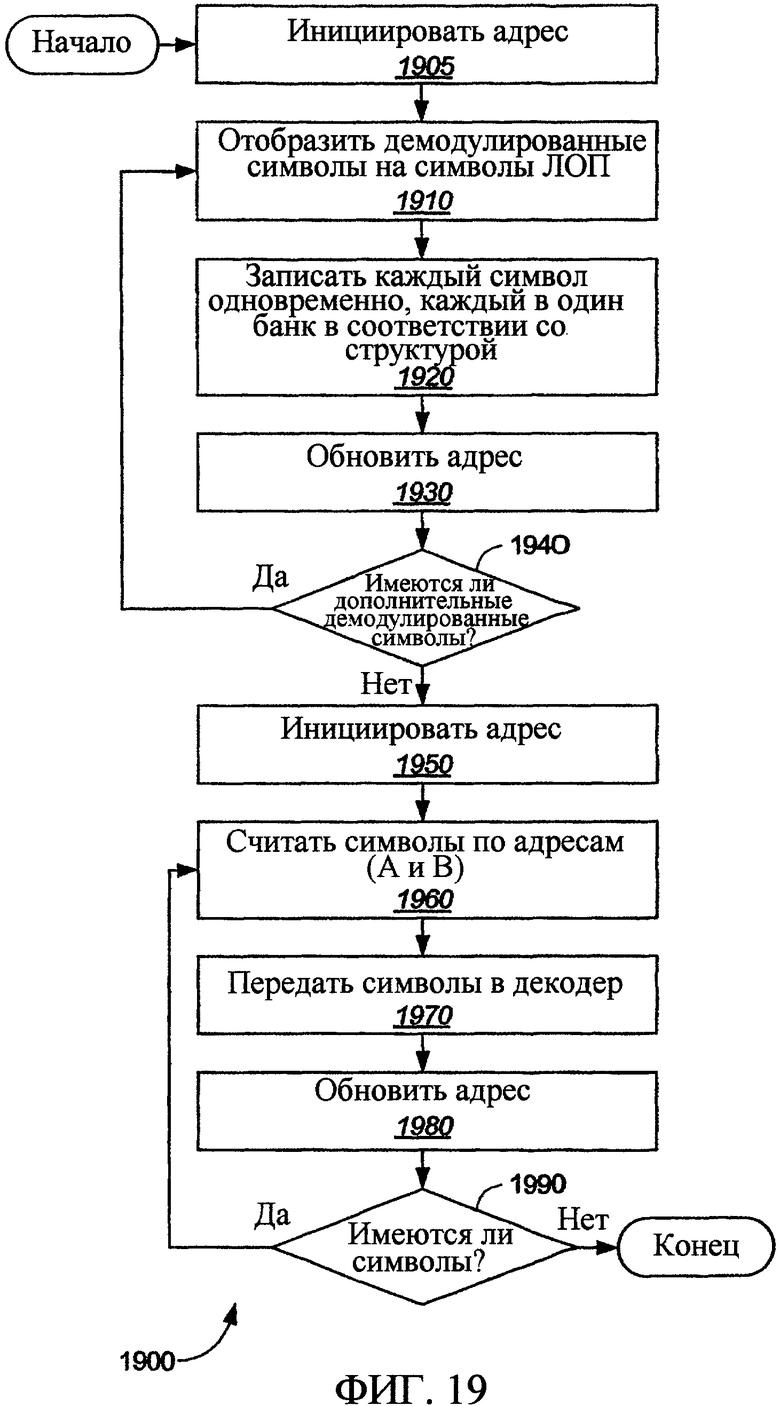

На фиг. 19 показана блок-схема последовательности выполнения примерного варианта способа обратного перемежения.

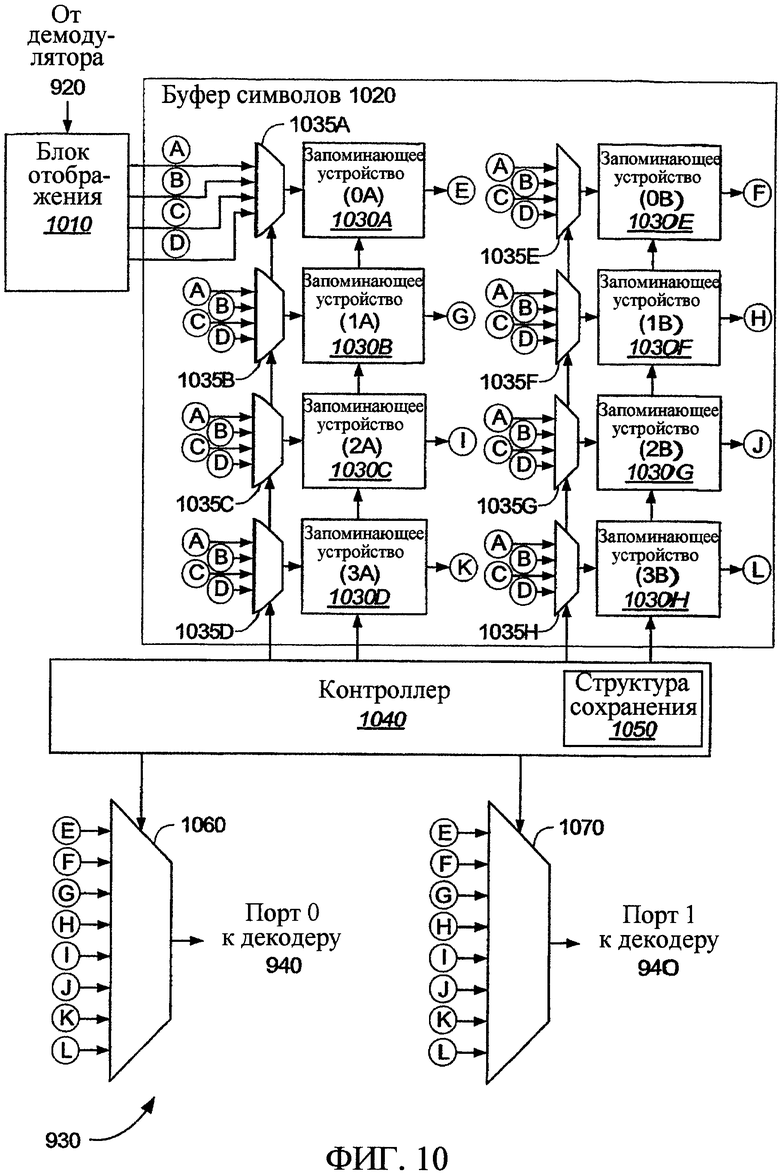

На фиг. 20 показана блок-схема последовательности выполнения примерного варианта способа, предназначенного для записи в банки запоминающих устройств в соответствии со структурой сохранения.

Подробное описание изобретения

На фиг. 1 показана схема беспроводной системы 100 связи, которая может быть предназначена для поддержки одного или более стандартов и/или проектов систем беспроводной связи (например, стандарта W-CDMA, стандарта IS-95, стандарта cdma2000, спецификации HDR, предложения 1xEV-DV, стандарта GSM). В примерном варианте выполнения система 100 поддерживает стандарт IS-856 (HDR).

Для простоты показана система 100, включающая в себя три базовые станции 104, осуществляющие связь с двумя мобильными станциями 106. Базовую станцию и зону ее обслуживания часто совместно называют "ячейкой". В системе IS- 95 ячейка может включать в себя один или более секторов. В спецификации W-CDMA каждый сектор базовой станции и зона обслуживания сектора называются ячейкой. Используемый здесь термин «базовая станция» может применяться взаимозаменяемым образом с терминами «пункт доступа» или «узел B». Термин «мобильная станция» может использоваться взаимозаменяемым образом с терминами «пользовательское устройство» (UE, ОП), «абонентский блок», «абонентская станция», «терминал доступа», «удаленный терминал» или с другими соответствующими терминами, известными в данной области техники. Термин «мобильная станция» охватывает стационарные беспроводные устройства. Мобильная станция представляет собой пример беспроводного устройства связи.

В зависимости от варианта воплощения системы, каждая мобильная станция 106 может осуществлять связь с одной (или, возможно, более) базовыми станциями 104 по прямой линии связи в любой заданный момент времени и может осуществлять связь с одной или более базовыми станциями по обратной линии связи в зависимости от того, находится ли мобильная станция в состоянии гибкой передачи обслуживания. Прямая линия связи (то есть нисходящая линия связи) относится к передаче от базовой станции к мобильной станции, и обратная линия связи (то есть восходящая линия связи) относится к передаче от мобильной станции к базовой станции.

Для ясности, в примерах, используемых в описании настоящего изобретения, базовые станции могут рассматриваться как источник сигналов, и мобильные станции - в качестве приемников и получателей этих сигналов, то есть сигналов прямой линии связи. Для специалистов в данной области техники будет понятно, что мобильные станции так же, как и базовые станции, могут быть оборудованы так, чтобы передавать данные, как описано здесь, и аспекты настоящего изобретения применимы для этих ситуаций. Слово "примерный" используется здесь исключительно для обозначения "служащий в качестве примера, случая или иллюстрации". Любой вариант выполнения, описанный здесь как "примерный", не обязательно следует рассматривать как предпочтительный или преимущественный по сравнению с другими вариантами выполнения.

На фиг. 2 показана блок-схема устройства беспроводной связи, такого как мобильная станция 106 или базовая станция 104. Блоки, изображенные в этом примерном варианте выполнения, обычно представляют собой поднабор компонентов, включенных в состав мобильной станции 106 или базовой станции 104. Для специалистов в данной области техники будет понятна возможность адаптации варианта выполнения, показанного на фиг. 2, для использования в любом количестве конфигураций.

Сигналы принимаются с помощью антенны 210 и передаются в приемник 220. Приемник 220 выполняет обработку в соответствии с одним или больше стандартами беспроводной системы связи, такими как стандарты, представленные выше. Приемник 220 выполняет различную обработку, такую как преобразование сигнала радиочастоты (RF, РЧ) в сигнал огибающей, усиление, аналогово-цифровое преобразование, фильтрация и т.п. Различные технологии приема известны в данной области техники. Приемник 220 может принимать сигналы на различных частотах, в соответствии с тем, как он запрограммирован с помощью процессора 250. Приемник 220 может также включать в себя другие компоненты, описанные более подробно ниже, такие как демодуляторы, обратные перемежители, декодеры и т.п.

В примерном варианте выполнения используется приемник, предназначенный для приема сигналов IS-856. В альтернативных вариантах выполнения могут поддерживаться альтернативные стандарты, и варианты выполнения могут поддерживать или могут не поддерживать множество форматов связи. Прием может включать в себя прием RAKE (многолучевой когерентный прием), коррекцию, комбинирование, обратное перемежение, декодирование и различные другие функции, которые требуются в соответствии с форматом принимаемых сигналов. Различные методы демодуляции известны в данной области техники. Каналы передачи данных и каналы управления представляют собой примеры каналов, принимаемых и демодулируемых в приемнике 220. Демодулированные, обратно перемеженные и декодированные данные могут быть переданы в приемник данных, который может быть приложением любого типа, различные примеры которых известны в данной области техники.

Декодер 230 сообщений принимает демодулированные данные и выделяет сигналы или сообщения, направленные в мобильную станцию 106 по прямой линии связи или в базовую станцию по обратной линии связи. Декодер 230 сообщений декодирует различные сообщения, используемые при установке, поддержании и разъединении вызова (включая голосовые сеансы или сеансы передачи данных) в системе. Различные типы сообщений известны в данной области техники и могут быть определены в различных поддерживаемых стандартах связи. Сообщения передаются в процессор 250 для использования при последующей обработке. Некоторые или все функции декодера 230 сообщений могут быть выполнены в процессоре 250, хотя отдельный блок показан для ясности описания. В качестве альтернативы, приемник 220 может декодировать определенную информацию и может передавать ее непосредственно в процессор 250 (например, однобитовое сообщение, такое как ACK/NAK (подтверждение/не подтверждение приема) или команда управления для повышения/снижения мощности).

Сигналы передаются через антенну 210. Передаваемые сигналы форматируются в передатчике 270 в соответствии с одним или более стандартами беспроводной системы связи, такими как представлены выше. Источник данных предоставляет данные для передачи. Источник данных может представлять собой любой тип источника данных или приложение, примеры которых хорошо известны в данной области техники. Примеры компонентов, которые могут быть включены в передатчик 270, представляют собой усилители, фильтры, цифро-аналоговые (D/A, Ц/А) преобразователи, радиочастотные (РЧ) преобразователи и т.п. Передатчик 270, подробно описанный ниже, также может содержать модуляторы, расширители, кодеры, перемежители и другие функции. Каналы передачи данных и каналы управления могут форматироваться для передачи в соответствии с различными форматами.

Генератор 260 сообщений может использоваться для подготовки сообщений различных типов, которые требуются для установки, поддержания и/или разъединения голосового вызова или сеанса передачи данных. Различные типы сообщений управления могут генерироваться в мобильной станции 106 для передачи по обратной линии связи или в базовую станцию 104 для передачи по прямой линии связи.

Данные, принимаемые и демодулируемые в приемнике 220, могут передаваться в процессор 250 для использования при голосовых сеансах связи или при передаче данных, а также в различные другие компоненты. Аналогично, данные для передачи могут направляться в передатчик 270 из процессора 250. Например, различные приложения обработки данных могут присутствовать в процессоре 250 или в другом процессоре, включенном в устройство 104 или 106 беспроводной связи (не показано). Устройство 104 или 106 беспроводной связи может включать в себя связь с внешним устройством, таким как переносной компьютер (не показан) или может быть встроено в него.

Процессор 250 может представлять собой микропроцессор общего назначения, цифровой процессор сигналов (DSP, ЦПС) или процессор специального назначения. Процессор 250 может выполнять некоторые или все функции приемника 220, декодера 230 сообщений, генератора 260 сообщений или передатчика 270, а также любую другую обработку, требуемую в устройстве беспроводной связи. Процессор 250 может быть соединен со специализированными аппаратными средствами, которые способствуют выполнению этих задач (подробно не показаны). Прикладные программы обработки данных или голоса могут быть внешними, такими как реализуемые внешним подключенным переносным компьютером или соединением с сетью, могут исполняться на дополнительном процессоре в устройстве 104 или 106 беспроводной связи (не показано) или могут исполняться в самом процессоре 250. Процессор 250 соединен с запоминающим устройством 255, которое можно использовать для сохранения данных, а также инструкций для выполнения различных описанных процедур и способов. Для специалистов в данной области техники будет понятно, что запоминающее устройство 255 может состоять из одного или более компонентов памяти различных типов, которые могут быть внедрены полностью или частично в процессор 250.

На фиг. 3 показан примерный вариант выполнения передатчика 270, пригодного для использования в мобильной станции 106 или в базовой станции 104. Кодер 310 принимает данные от источника данных и кодирует эти данные в соответствии с процедурой кодирования, такой как подробно описана в стандарте передачи данных, то есть в одном из стандартов, аналогичных описанным выше. В примерном варианте выполнения кодер 310 представляет собой турбокодер, соответствующий спецификации IS-856. Кодер 310 может передавать кодируемые данные с различной скоростью. В примерном варианте выполнения поддерживаются скорости кодирования 1/3 и 1/5. Выходной сигнал кодера 310 обрабатывается с помощью матрицы 320 перемежения, которая передает поток перемеженных кодированных данных в блок 330 прокалывания кода. Прокалывание кода представляет собой необязательную функцию. Данные прокалывания могут быть вставлены в поток кодированных перемеженных данных, и выходные данные затем передаются в модулятор 340. Модулятор 340 используют для форматирования данных для передачи в соответствии с одним из множества форматов передачи. Можно использовать любое количество форматов модуляции, включая модуляцию более высокого порядка. В примерном варианте выполнения модулятор может быть конфигурирован для выполнения модуляции КАМ-16, ФМн-8 или КФМн. Выходной сигнал модулятора 340 передается в РЧ блок 350 преобразования с повышением частоты, где он форматируется для передачи в антенну 210. Различные методы передачи РЧ сигнала хорошо известны в данной области техники и могут включать в себя усиление, фильтрацию, смешивание для преобразования с повышением частоты, дуплексирование и т.д.

На фиг. 4 показан примерный вариант выполнения кодера 310, который описан выше со ссылкой на фиг. 3. В этом примере данные от источника данных подаются в первый кодер 410 и второй кодер 420. В примерном варианте выполнения используется метод турбокодирования. Подробно кодер 410 и второй кодер 420 описаны в спецификации IS-856, указанной выше. Любые другие методы кодирования могут быть использованы в пределах объема настоящего изобретения. Некодированные биты данных пропускаются через кодер 310 и обозначаются буквой U. Для каждого некодированного бита данных также могут генерироваться один или больше битов проверки на четность от каждого кодера 410 или 420. Два бита проверки на четность, V0 и V1, могут быть выведены из первого кодера 410. Два бита проверки на четность, V0' и V1' генерируются во втором кодере 420. В различных альтернативных вариантах выполнения любое количество битов проверки на четность может генерироваться каждым из кодеров 410 и 420. Если используется скорость кодирования 1/3, то используются некодированные биты U и биты V0 и V0' проверки на четность. Если используется скорость кодирования 1/5, то применяются некодированные биты U, первые биты V0 и V1 проверки на четность и вторые биты V0' и V1' проверки на четность.

В примерном варианте выполнения матрица 320 перемежения выполняет перемежение, как подробно описано в спецификации IS-856. Схема перемежения основана на структуре строк/столбцов. Для кодов со скоростью 1/3 используется кодовое слово, содержащее UV0V0'. Для кодов со скоростью 1/5 используется кодовое слово UV0V1V0'V1'. V0 и V1 поступают из первого компонентного турбокодера, и V0' и V1' поступают от второго компонентного турбокодера. Перемежение выполняется, как описано ниже.

Символы кодового слова переупорядочиваются в пять последовательностей: U, V0, V0', V1 и VI', где U содержит все информационные биты, V0 содержит все первые биты проверки на четность первого компонентного кодера, V0' содержит все первые биты проверки на четность второго компонентного кодера, V1 содержит все вторые биты проверки на четность первого компонентного кодера и V1' содержит все вторые биты проверки на четность второго компонентного кодера. Последовательность U записывается в матрицу размером К строк и M столбцов, по строкам. Столбцы затем переставляются в обратном порядке следования битов, и в каждом столбце выполняется циклический сдвиг.

Последовательность V0 и последовательность V0' конкатенируются, и V0V0' записываются в K строк и М столбцов (с тем же числом K, что и в последовательности U, и с числом М, которое в два раза больше этого числа для последовательности U). Затем столбцы переставляются в обратном порядке следования битов, и в каждом столбце выполняется циклический сдвиг.

Последовательность V1 и последовательность V1' конкатенируются, и V1VI' записываются в K строк и М столбцов (при этом используется то же число K, что и для последовательности U, а число М в два раза больше, чем в последовательности U). Затем столбцы переставляются в обратном порядке следования битов, и в каждом столбце выполняется циклический сдвиг.

На фиг. 5-8 представлен пример результатов матрицы перемежителя для нескольких примерных форматов модуляции. На фиг. 5 показан выходной результат для пакета размером 5К, модулированного с использованием КАМ-16, и при скорости кодирования 1/3. На фиг. 6 показан выходной результат матрицы 320 перемежения для пакета размером 4К, модулированного с использованием КАМ-16, при скорости кодирования 1/3. На фиг. 7 показан выходной результат матрицы 320 перемежения для пакета размером 3К, модулированного с использованием ФМн-8, и при скорости кодирования 1/3. На фиг. 8 показан выходной результат матрицы 320 перемежения для пакетов 2К, модулированных с использованием КФМн, и при скорости кодирования 1/3. Различные свойства этих форматов перемежения можно использовать в описанных ниже примерах выполнения обратного перемежителя. Следует отметить, что для модуляции КФМн количество строк матрицы равно двум. Для модуляции ФМн-8 количество строк матрицы равно трем. Для модуляции КАМ-16 количество строк матрицы составляет четыре. Модуляция выполняется путем обработки одного столбца одновременно. Таким образом, два бита в одном столбце используется для формирования одного символа модуляции КФМн, столбец из трех битов используется для формирования одного символа модуляции ФМн-8, и столбец из четырех битов используется для формирования одного символа модуляции КАМ-16. В примерах матриц перемежения, представленных на фиг. 5-8, иллюстрируется, каким образом символы кодового слова организуются перед перестановкой столбцов с обратной последовательностью битов и циклическим сдвигом для различных типов модуляции. В матрицах затем выполняется перестановка на основе обратного порядка следования битов в столбце, после чего выполняется циклический сдвиг в каждом столбце. Следует отметить, что символы в одном столбце также могут оставаться вместе после этих манипуляций. Каждый столбец обрабатывается модулятором как группа, для формирования одного символа модуляции. Таким образом, перестановки любого типа для описанной матрицы перемежения могут использоваться в пределах объема настоящего изобретения.

Модулятор 340 принимает символ, как описано выше, и форматирует этот символ для передачи в соответствии с требуемым форматом модуляции. Например, символ модулятора отображается на сигнальную совокупность для генерирования синфазного (I) и квадратурного (Q) значения для подачи в РЧ преобразователь 350 с повышением частоты, для передачи через антенну 210.

На фиг. 9 представлен пример приемника 220, пригодного для использования в базовой станции 104 или мобильной станции 106, как подробно описано выше со ссылкой на фиг. 2. Сигналы принимаются от антенны 210 и передаются в РЧ блок 910 преобразования с понижением частоты, где РЧ сигнал преобразуется в базовую полосу. Сигналы базовой полосы передаются в демодулятор 920 для демодуляции. Выходной сигнал демодулятора передается в обратный перемежитель 930 для обратного перемежения, как дополнительно подробно описано ниже. Выходной сигнал обратного перемежителя передается в декодер 940 для декодирования. Декодированные данные могут передаваться в приемник данных. В примерном варианте выполнения декодер 940 представляет собой турбодекодер, и обратный перемежитель 930 выполняет обратное перемежение в соответствии со стандартом IS-856.

Различные методы демодуляции хорошо известны в данной области техники. В примерном варианте выполнения демодулятор 920 генерирует для каждого символа демодулятора значения I и Q. Пара I и Q соответствует точке в сигнальной совокупности, соответствующей выбранному в данный момент времени формату модуляции.

Примерный обратный перемежитель 930 показан на фиг. 10. Обратный перемежитель 930 принимает символы демодулятора от демодулятора 920. Эти символы передаются в блок 1010 отображения. Блок 1010 отображения используется для вычисления значений мягкого решения для определения принятого символа модуляции. В примерном варианте выполнения могут генерироваться символы логарифмического отношения правдоподобия (LLR, ЛОП). Значения мягкого решения могут использоваться после перемежения в декодере для окончательного определения наиболее вероятных декодированных данных, как более подробно описано ниже. В примерном варианте выполнения символы ЛОП представляют собой шестибитовые значения. Для специалистов в данной области техники будет понятно, что значения ЛОП могут иметь любую длину и что другие критерии мягкого решения могут использоваться для декодирования. Блок 1010 отображения может использоваться для генерирования любого типа значения мягкого решения. Обратный перемежитель 930 может иметь два назначения. Во-первых, он будет обращаться к символам модуляции таким образом, что будет выполняться обратный процесс перемежения, вычисляя символы ЛОП на основе совокупности символов в блоке 1010 отображения. Хотя любое количество выходных данных может генерироваться в блоке 1010 отображения, в примерном варианте выполнения максимальное количество символов ЛОП составляет четыре, которые обозначены на фиг. 10 как A, B, C и D. В альтернативном варианте выполнения, могут использоваться форматы модуляции более высокого порядка, что позволяет получить большее количество выходных данных (то есть при КАМ-32 генерируется пять выходных сигналов, при КАМ-64 генерируется шесть выходных сигналов и т.д.). Блок 1010 отображения ассоциирует символы ЛОП для каждого выхода A-D в соответствии с используемой схемой кодирования, то есть перестановкой, перемежением и т.д. Для специалистов в данной области техники будет понятно, что любую схему кодирования можно использовать в пределах объема настоящего изобретения.

Второе назначение состоит в сохранении вычисленных символов ЛОП в буфере, что позволяет декодеру выполнять операции в отношении выходных данных буфера наиболее эффективным возможным способом. В подробно описанных ниже вариантах выполнения символы ЛОП, генерируемые для каждого выходного сигнала демодулятора, сохраняются одновременно, что позволяет исключить необходимость вычисления ЛОП более чем один раз. Символы ЛОП сохраняются таким образом, что буфер можно считывать последовательно для получения линейного потока данных из декодера 940.

Например, если используется КАМ-16, четыре символа ЛОП будут генерироваться из каждой отображенной пары I, Q. Если используется ФМн-8, то будут генерироваться 3 символа ЛОП. При использовании КФМн в каждом цикле тактовой частоты генерируются два символа ЛОП. Как подробно описано ниже, количество требуемых циклов вычисления можно уменьшить путем сохранения всех вычисленных символов ЛОП одновременно, по порядку.

В предшествующем уровне техники примерный обратный перемежитель для минимизации требований к ширине полосы между демодулятором и обратным перемежителем, выбирал один из символов ЛОП, вычисленных из столбца, и сохранял его в буфере символа. Другие три символа ЛОП (в примере КАМ-16), хотя и вычисленные, отбрасывались. Каждый символ ЛОП в действительности вычисляется четыре раза во время всего процесса обратного перемежения. Такое избыточное вычисление использует часть ограниченного времени декодирования, что является нежелательным. Кроме того, оно потребляет избыточную энергию, что также является нежелательным в конструкции мобильного процессора. Те же аргументы справедливы для модуляции ФМн-8 и КФМн, хотя избыточное время и потребляемая энергия могут быть меньше, чем в случае КАМ-16.

Обратный перемежитель 930 разработан так, что все вычисленные символы ЛОП выбираются и сохраняются так, что ни один символ ЛОП не вычисляется более чем один раз. Это сокращает время, требуемое для обратного перемежения на 75 процентов для случаев КАМ-16, на 66 процентов для случаев ФМн-8 и на 50 процентов для случаев КФМн. Эти процентные соотношения также относятся к экономии энергии, обеспечиваемой по сравнению с описанным выше примером предшествующего уровня техники.

Для показанного на фиг. 5 примера КАМ-16 очевидно, что символы кода в каждом столбце расположены на равных расстояниях. Например, четыре символа в первом столбце последовательности U для КАМ-16 (5 К) представляют собой (U0, U1280, U2560, U3840). Четыре символа кода последовательности V0/V0' для того же случая составляют (V00, V02560, V0'0, V0'2560). И снова, они расположены на равном расстоянии в последовательностях V0, V0'. Тщательный анализ всех столбцов для всех совокупностей модуляции показывает то же свойство равного расстояния. Такое свойство обеспечивает возможность реализации эффективного способа сохранения, примерные варианты выполнения которого описаны. Согласно фиг. 10, буфер 1020 символов содержит множество банков 1030A-H запоминающих устройств. Каждый из символов A-D ЛОП может быть выбран в качестве входных данных для любого из показанных восьми банков. Банки 1030A-1030D называются четными банками и обозначены как 0A-3A. Банки 1030E-H запоминающих устройств называются нечетными банками и обозначены как 0B-3B. Как показано на фиг. 10, мультиплексоры 1035A-H используются для выбора одного из символов для сохранения в соответствующем банке запоминающих устройств. Банки запоминающих устройств выполнены с возможностью одновременной записи. Таким образом, каждый из четырех символов ЛОП может быть записан в банк запоминающих устройств во время каждого цикла тактовой частоты. Ниже подробно описано, какие из банков запоминающих устройств выбираются для сохранения этих символов. Следует отметить, что мультиплексоры 1035A-H представлены только в качестве иллюстрации. Различные другие методы мультиплексирования множества входных данных в множество данных назначения хорошо известны в данной области техники. Например, шину с тремя состояниями можно использовать для каждого банка запоминающих устройств с буферами трех состояний, входные данные которых соответствуют символам A-D ЛОП. Шину выборки можно использовать для обеспечения сохранения выходных данных ЛОП в поднаборе банков запоминающих устройств в любой момент времени.

Контроллер 1040 соединен с каждым из банков 1030A-H запоминающих устройств и мультиплексорами 1035A-H. Контроллер 1040 может использоваться для выбора банков запоминающих устройств для приема соответствующих символов ЛОП. Следует отметить, что при описании четырех символов ЛОП в качестве примера используется случай КАМ-16. Вариант выполнения, показанный на фиг. 10, также пригоден для использования с модуляцией ФМн-8 и КФМн, с различными размерами буфера и скоростями кодирования. Вариант выполнения, представленный на фиг. 10, соответствует примерам форматов передачи, изображенным на фиг. 5-8. Однако для специалистов в данной области техники будет понятно, что эти общие принципы также можно применять для множества других комбинаций. Количество банков запоминающих устройств, используемых в буфере 1020 символов, соответствует количеству символов мягкого решения, которые выводятся из блока 1010 отображения. Как описано выше, в данном варианте выполнения с выхода блока 1010 отображения могут поступать четыре, три или два символа, в зависимости от выбранного формата передачи данных. В альтернативном варианте выполнения может использоваться дополнительная модуляция более высокого порядка. Например, если используется КАМ-32, то блок 1010 отображения может формировать пять символов. При использовании модуляции КАМ-64 блок 1010 отображения будет формировать шесть символов и так далее. Количество используемых элементов 1030 запоминающих устройств в два раза больше максимального количества символов, которые могут генерироваться одновременно. Как подробно описано ниже, восемь банков запоминающих устройств в данном примерном варианте выполнения достаточны для примеров КАМ-16 и могут использоваться для модуляции более низкого порядка. Другие используемые в случае необходимости методы с применением дополнительных банков для обеспечения модуляции более низкого порядка, описаны ниже.

Банки 1030 запоминающих устройств, используемые в буфере 1020 символов, имеют размер, обеспечивающий возможность размещения пакета кодера с максимальным размером. В примерах, описанных со ссылками на фиг. 5-8, представлен пакет размером 4К и пакет размером 5К для модуляции КАМ-16. Выделение ресурсов банков запоминающих устройств и планирование сохранения символов ЛОП в них подробно описано ниже. Выходные данные банков 1030 запоминающих устройств обозначены как E-L. В этом примере два банка запоминающих устройств могут считываться одновременно для подачи двух символов одновременно в декодер 940. Мультиплексор 1060 принимает E-L и по выбору обеспечивает передачу одного выходного сигнала по линии, обозначенной как порт 0, в декодер 940. Мультиплексор 1070 принимает выходные данные E-L для передачи их в порт 1 декодера 940. В примерном варианте выполнения такое мультиплексирование может быть упрощено в результате того, что декодер 940 представляет собой турбодекодер, в который подаются последовательные выходные данные буфера. При каждом обращении к запоминающему устройству адресация выполняется к четным и нечетным банкам запоминающих устройств по одному адресу для получения символов, предназначенных для передачи в декодер. Таким образом, поскольку каждый из символов ЛОП сохранен с перемежением в буфере 1020 символов, схема адресации для доступа к сохраненным символам ЛОП существенно упрощается. Это поясняется в примерных вариантах выполнения, подробно описанных ниже.

Контроллер 1040 обеспечивает управление различными компонентами, описанными для обратного перемежителя 930. Например, контроллер 1040 может обеспечивать адреса для каждого банка запоминающих устройств, выбирать линии для каждого банка запоминающих устройств, выбирать входные данные для каждого банка запоминающих устройств для сохранения значений, обеспечивать строб записи для записи, обеспечивать строб доступа для считывания значений из каждого запоминающего устройства, может выбирать два или больше выхода для передачи в выходной декодер и т.д. Контроллер 1040 также можно использовать для определения распределения символов A-D ЛОП из блока 1010 отображения (подробно не показано). Различные методы построения запоминающего устройства, считывания, записи и т.д. хорошо известны в данной области техники. Примеры методов генерирования адресов требуемого обратного перемежения подробно описаны ниже. В различных вариантах выполнения контроллер 1040 формирует адреса для сохранения в поднаборе банков 1030A-H в соответствии со структурой 1050 сохранения.

Структура 1050 сохранения может включать в себя одну или больше структур сохранения, ассоциированных с одним или более форматами передачи. Примеры подробно описаны ниже. В одном варианте выполнения базовый адрес используется для сохранения во всем банке запоминающих устройств со значением смещения для каждого отдельного банка запоминающих устройств, в которых может быть сохранен символ ЛОП. Уникальные смещения и выбранные поднаборы банков запоминающих устройств определяются с использованием структуры 1050 сохранения. Структура сохранения может иметь множество циклов, причем в каждом цикле выбирается разный поднабор банков запоминающих устройств для сохранения и разный набор соответствующих смещений, добавляемых к базовому адресу. Количество циклов в структуре сохранения соответствует скорости кодирования. Например, коды со скоростью 1/3, описанные выше, генерируют три кодируемых символа для каждого информационного символа. Соответствующее количество циклов в структуре сохранения равно удвоенному количеству кодируемых символов. Таким образом, в форматах для передачи со скоростью 1/3 используется структура сохранения из шести циклов. Коды со скоростью 1/5 генерируют пять кодируемых символов для каждого информационного символа. Таким образом, структура сохранения из десяти циклов будет использоваться для такого формата передачи. Примеры структуры сохранения подробно представлены в таблицах 1-4 и подробно описаны ниже.

Структура 1050 сохранения может быть сохранена в запоминающем устройстве, доступ к которому осуществляет контроллер 1040, и может быть выполнена на логических схемах или с использованием любой другой технологии, хорошо известной в данной области техники. Контроллер 1040 может представлять собой ЦПС или другой микроконтроллер, конечный автомат или различные другие средства, хорошо известные в данной области техники. Структура 1050 сохранения также может быть сохранена в запоминающем устройстве 255, подробно описанном выше со ссылкой на фиг. 2. Контроллер 1040 может представлять собой один из множества процессов, исполняемых в процессоре 250, или может быть выполнен как отдельный процессор или контроллер.

На фиг. 11-14 представлены примеры конфигураций буфера 1020 символов для четырех различных форматов передачи данных, КАМ-16, ФМн-8, КФМн (1/3), КФМн (1/5) соответственно. Общий объем буфера равен 15К, как показано на чертеже. Это позволяет размещать максимальное количество символов, требуемых для сохранения кодированного пакета в данном примере (кодирование пакета объемом 5К со скоростью 1/3). И снова, в этом примере каждый банк запоминающих устройств имеет ширину шесть битов. Четные и нечетные банки запоминающих устройств обозначены как A и B соответственно, и используются четыре пары банков запоминающих устройств, обозначенных 0-3 соответственно, как показано на фиг. 10.

КАМ-16 представлена на фиг. 11. Число, показанное в каждой ячейке запоминающего устройства, соответствует сохранению символа ЛОП во время соответствующего цикла структуры сохранения. Можно видеть, что в примере КАМ-16, показанном на фиг. 11, используется каждая из ячеек памяти запоминающего устройства. На фиг. 12, в примере ФМн-8 используются только первые три пары банков запоминающих устройств. В примерах КФМн, показанных на фиг. 13 и 14, используются только две пары банков запоминающих устройств. Выбраны первая и третья пары банков запоминающих устройств, что позволяет присоединить вторую и четвертую пару банков запоминающих устройств к первой и третьей парам для поддержки больших размеров пакета, если необходимо. Следует отметить, что в кодах со скоростью 1/3, показанных на фиг. 11-13, используется структура сохранения с шестью циклами. В примере скорости 1/5, показанном на фиг. 14, используется структура сохранения с десятью циклами. Структура, показанная на каждой из фиг. 11-14, может повторяться до тех пор, пока не будет заполнен буфер. Таким образом, как более подробно описано ниже, для каждого из форматов передачи данных можно использовать общий адрес для индексации начала структуры сохранения.

Когда каждый цикл структуры сохранения будет завершен, общий адрес может получить приращение соответствующим способом. В этом примере, четные и нечетные банки ассоциированы с одним адресом, как очевидно для специалистов в данной области техники. Выбор банка определяется по структуре сохранения. Для специалистов в данной области техники понятно, что могут быть предусмотрены другие схемы адресации структуры сохранения, входящие в объем настоящего изобретения.

В примере по фиг. 11 общий адрес инициализируется как равный 0. Таким образом, в этом примере общий адрес может быть инициирован в адресной позиции 0. Структура сохранения следует соответственно шести последовательным циклам, как показано на чертеже, и затем общий адрес увеличивается на три. Линия выбора банка может использоваться вместе с общим адресом и соответствующими адресами смещения, для обеспечения адресации банков 1, 2 и 3.

Номера циклов, показанные в каждом из примеров на фиг. 11-14, обозначают места, в которых должны быть сохранены символы ЛОП во время соответствующего цикла. Например, на фиг. 11 в течение первого цикла в банки 0A, 1A, 2A и 3A записываются смещения, равные 0. Во втором цикле в банки 0B, 2A и 2B записываются представленные смещения. Цикл структуры для примера КАМ-16, показанного на фиг. 11, подробно представлен в таблице 1. В таблице 1, во время цикла 1, выбираются четыре банка (например, 0-3 в первом цикле), индикатор четный/нечетный для идентификации выбора банка A или B (все четные или A, в этом примере), и смещение указателя (все равны 0 в этом примере). В таблице также показано, какой тип символов записывается в данный момент времени. В цикле 1 каждый символ соответствует символу U. Символы V0 и V0' записываются в последующих циклах, как показано на чертеже. Можно видеть, что если следовать структуре, показанной в таблице 1, в банках запоминающих устройств будет выполнена запись, как показано на фиг. 11. Таблицы 2-4 представляют собой аналогичные структуры сохранения, соответствующие форматам передачи, показанным на фиг. 12-14, ФМн-8, КФМн (скорость 1/3) и КФМн (скорость 1/5) соответственно.

КАМ-16

ФМн-8

КФМн (1/3)

КФМн (1/5)

На фиг. 15-18 показан буфер 1020 символов для каждого из соответствующих форматов передачи, описанных со ссылками на фиг. 11-14. Например, на фиг. 15 показан случай для КАМ-16. Можно видеть, что U0, U1280, U2560 и U3840, которые вычислены из одной пары I, Q, сохранены одновременно во время цикла 1 в банках 0А-3A. По мере продолжения цикла сохранения каждый информационный бит и бит четности будет сохраняться таким образом, что индекс линейно увеличивается от 0 до конца пакета. Таким образом, при передаче значений символа ЛОП в декодер 940 можно использовать простую схему линейной адресации. Запоминающее устройство с двумя портами, представленное на фиг. 10, позволяет обеспечить одновременный доступ к двум банкам, как описано выше. На фиг. 16-18 показаны аналогичные примеры демодулированных символов после обратного перемежения, сохраненных для форматов передачи, соответствующих фиг. 12-14 соответственно.

Следует отметить, что для случая скорости 1/5, показанного на фиг. 18, представлена структура сохранения из десяти циклов, в отличие от структуры сохранения из шести циклов, представленной на фиг. 15-17. Таким образом, для примерного буфера 1020 символов, используемого для поддержания формата перемежения IS-856, перемежитель 930 может быть использован следующим образом: восемь банков запоминающих устройств каждый с 1,875K позициями памяти шириной по шесть битов. (И снова, размер 1,875K определен в соответствии с наибольшим размером пакета 5К и его скоростью передачи данных 1/3, что требует всего 15К ячеек памяти для хранения. Другие размеры могут использоваться в других вариантах выполнения, которые поддерживают другие размеры пакета). Сохранение выполняется таким образом, что любые две последовательные точки адреса для двух разных банков запоминающих устройств и любых двух адресов, которые разнесены на 1/4 общего пространства хранения, указывают на другой физический банк запоминающего устройства. Это соответствует свойству равного расстояния, описанному выше. И снова, следует отметить, что все ячейки памяти в запоминающем устройстве не заполняются до конца обратного перемежения, за исключением случая с наибольшим размером пакета. Тем не менее, даже при меньших размерах пакета, адреса для доступа к заполненным ячейкам памяти в последовательном порядке увеличиваются линейно, что требуется для подачи в турбодекодер в примерном варианте выполнения.

На фиг. 19 представлен способ 1900 обратного перемежения, пригодный для использования в обратном перемежителе 930, как описано выше. Процесс начинается в блоке 1905, в котором инициируется общий адрес. В блоке 1910 символы демодуляции отображаются на символы ЛОП (или другие символы мягкого решения), в соответствии с сигнальной совокупностью, соответствующей выбранному в данное время формату передачи. В блоке 1920 каждый символ ЛОП одновременно записывается в каждый из банков запоминающих устройств в соответствии со структурой сохранения. Пример такого блока подробно описан ниже со ссылкой на фиг. 20.

В блоке 1930 обновляется общий адрес. Для специалистов в данной области техники должно быть понятно, какая величина приращения требуется для обновления адреса в соответствии с количеством циклов в структуре сохранения, как описано выше. Например, при структуре сохранения, равной шести, с использованием четных и нечетных банков, приращение общего адреса составляет три для каждой последующей структуры сохранения. В качестве другого примера, при использовании кодирования со скоростью 1/5, количество циклов в структуре сохранения равно десяти. Таким образом, для варианта выполнения, в котором используются четные и нечетные банки, как описано выше со ссылкой на фиг. 10, общий адрес будет обновляться с приращением, равным пяти, до завершения структуры сохранения.

В блоке 1940 принятия решения, если имеются дополнительные демодулированные символы, предназначенные для обратного перемежения, осуществляется возврат к блоку 1910 и выполняется описанная выше обработка. В противном случае выполняется переход к блоку 1950 для инициирования адреса для считывания буфера символа. В одном примере, при использовании КАМ-16 с размером пакета 5К, все содержание буфера символа может быть последовательно считано, начиная от адреса 0 до адреса 15К. Для специалистов в данной области техники должно быть понятно, что шины выборки для банков 1, 2 и 3 можно использовать вместо дополнительных битов адреса, соответствующих адресам вплоть до 15К. В примере ФМн-8, представленном на фиг. 12 и 16, первые три пары буферов могут считываться последовательно. В примерах КФМн, первый и третий буферы могут считываться последовательно и т.д.

В блоке 1960 символы считываются по инициированному адресу. В примерном варианте выполнения используется запоминающее устройство с двумя портами, что позволяет обеспечить одновременный доступ как к четным, так и нечетным банкам запоминающих устройств. В альтернативных вариантах выполнения может быть обеспечен одновременный доступ к любому количеству банков запоминающих устройств, как должно быть понятно для специалиста в данной области техники. В блоке 1970 символы доступа передаются в декодер для декодирования. В блоке 1980 обновляется адрес. В этом примере адрес обновляется просто путем приращения на единицу. В некоторых вариантах выполнения, после того как доступ к сохраненным значениям в банке запоминающего устройства или в паре банков запоминающих устройств будет исчерпан, может быть выбрана новая пара банков.

В блоке 1990 принятия решения, если имеются дополнительные символы для считывания из буфера символов, осуществляется возврат к блоку 1960 и повторяется описанная выше обработка. В противном случае процесс может быть остановлен. Следует отметить, что процесс обратного перемежения и передачи символов после обратного перемежения в декодер может повторяться бесконечно, если это необходимо.

На фиг. 20 представлен пример варианта выполнения блока 1920, описанного выше. Процесс начинается в блоке 2010, где цикл структуры инициализируется со значением, равным единице. В блоке 2020 выполняется запись в банк в соответствии с циклом структуры. Это может определяться по структуре сохранения, то есть по структуре 1050 сохранения, описанной выше. N определяется в соответствии с форматом передачи. Например, для КАМ-16 N равняется четырем, для ФМн-8 N равняется трем и для КФМн N равняется двум. В блоке 2030 выполняется приращение номера цикла структуры на единицу для выполнения следующего цикла в структуре сохранения. В блоке 2040 принятия решения, если структура цикла больше чем М, процесс завершается для этой структуры и может останавливаться. В противном случае, осуществляется возврат к блоку 2020 для продолжения обработки со следующим циклом структуры. М определяется в соответствии с количеством кодируемых символов, то есть скоростью кодирования. Например, коды со скоростью 1/3, описанные выше, соответствуют циклу структуры, в котором М равно шести. Коды со скоростью 1/5, описанные выше, соответствуют значению М, равному десяти.

Следует отметить, что во всех вариантах выполнения, описанных выше, порядок выполнения этапов способа может быть изменен, без отхода от объема изобретения. В представленном описании, во многих случаях даются ссылки на сигналы, параметры и процедуры, ассоциированные с системой IS-856, но объем настоящего изобретения не ограничивается этим. Для специалистов в данной области техники должно быть понятно, как применить описанные здесь принципы к различным другим системам связи. Эти и другие модификации очевидны для специалистов в данной области техники.

Для специалистов в данной области техники понятно, что информация и сигналы могут быть представлены с использованием любых из множества различных технологий и методов. Например, данные, инструкции, команды, информация, сигналы, биты, символы и элементарные посылки, ссылки на которые могут приводиться в приведенном выше описании, могут быть представлены напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами или любой их комбинацией.

Для специалистов в данной области техники также должно быть понятно, что различные приведенные для иллюстрации логические блоки, модули, схемы и этапы алгоритмов, описанные в связи с раскрытыми вариантами выполнения, могут быть воплощены как электронные аппаратные средства, компьютерное программное обеспечение или их комбинации. Для ясной иллюстрации возможности такой взаимной замены аппаратных и программных средств, различные представленные для иллюстрации компоненты, блоки, модули, схемы и этапы описаны выше, в общем, через выполняемые ими функции. Форма реализации таких функций аппаратными или программными средствами, зависит от конкретного варианта применения и конструктивных ограничений, накладываемых на всю систему. Специалисты в данной области техники могут реализовать требуемые функции различными способами для каждого конкретного варианта применения, и такие решения не следует интерпретировать как обуславливающие отход от объема настоящего изобретения.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми вариантами выполнения, могут быть воплощены или выполнены с использованием процессора общего назначения, цифрового процессора сигналов (ЦПС), специализированной интегральной микросхемы (ASIC, СИМС), программируемой вентильной матрицы (FPGA, ПВМ) или другого программируемого логического устройства, логических элементов на дискретных компонентах или транзисторных логических схем, дискретных аппаратных компонентов или любой их комбинации, разработанной для выполнения описанных функций. Процессор общего назначения может представлять собой микропроцессор, но в качестве альтернативы, процессор может представлять собой любой обычный процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть выполнен как комбинация вычислительных устройств, например комбинация ЦПС и микропроцессора, как множество микропроцессоров, один или более микропроцессоров во взаимосвязи с основным ЦПС, или с использованием любой другой такой конфигурации.

Этапы способа или алгоритма, описанного в связи с раскрытыми вариантами выполнения, могут быть реализованы непосредственно в виде аппаратных средств, в виде программного модуля, выполняемого микропроцессором, или с использованием комбинации этих двух подходов. Программный модуль может быть сохранен в ОЗУ, флэш-памяти, ПЗУ, стираемом программируемом постоянном запоминающем устройстве (EPROM, СППЗУ), электрически стираемом программируемом постоянном запоминающем устройстве (EEPROM, ЭСППЗУ), в регистрах, на жестком диске, на съемном диске, на CD-ROM или на носителе информации, выполненном в любой другой форме, известном в данной области техники. Примерный носитель информации связывается с процессором так, чтобы процессор мог считывать информацию с него и записывать информацию на носитель информации. В качестве альтернативы, носитель информации может быть встроен в процессор. Процессор и носитель информации могут находиться в ASIC. ASIC может находиться в пользовательском терминале. В качестве альтернативы, процессор и носитель информации могут быть установлены как дискретные компоненты в пользовательском терминале.

Приведенное выше описание раскрытых вариантов выполнения представлено для обеспечения возможности для любого специалиста в данной области техники реализовать и использовать настоящее изобретение. Различные модификации этих вариантов выполнения должны быть очевидны для специалистов в данной области техники, и общие определенные здесь принципы могут применяться в других вариантах выполнения без отхода от сущности или объема изобретения. Таким образом, настоящее изобретение не предназначено для ограничения представленными вариантами выполнения, но должно соответствовать самому широкому объему, совместимому с раскрытыми принципами и новыми признаками.

Изобретение относится к беспроводным системам связи, в частности к обратному перемежению многосимвольных потоков. Достигаемый технический результат - эффективное многосимвольное обратное перемежение, удовлетворяющее требованиям: ограничению во времени вычислений и сохранению энергии. Система беспроводной связи содержит обратный перемежитель, содержащий блок отображения, принимающий, по меньшей мере, пару принятых значений символов, множество банков запоминающих устройств, контроллер, множество мультиплексоров. По одному из вариантов приемник содержит блок отображения, множество банков запоминающих устройств, контроллер, при этом принятые значения символов в одном из множества банков запоминающих устройств сохраняются в соответствии с структурой сохранения, которая определена так, что содержит множество циклов и обеспечивает обратное перемежение. 10 н. и 44 з.п. ф-лы, 20 ил., 4 табл.

1. Приемник, содержащий: блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; и контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; при этом структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно; при этом количество циклов равно шести, при этом первый цикл указывает, что выбраны первый, третий, пятый и седьмой банки запоминающих устройств, со смещением, равным нулю; второй цикл указывает, что выбраны первый, второй, пятый и шестой банки запоминающих устройств, с соответствующими смещениями, равными один, ноль, один и ноль; третий цикл указывает, что выбраны второй, третий, седьмой и восьмой банки запоминающих устройств, с соответствующими смещениями, равными один, ноль, один и ноль; четвертый цикл указывает, что выбраны второй, четвертый, шестой и восьмой банки запоминающих устройств, со смещением, равным единице; пятый цикл указывает, что выбраны первый, второй, пятый и шестой банки запоминающих устройств, со смещением, равным двум; и шестой цикл указывает, что выбраны второй, третий, седьмой и восьмой банки запоминающих устройств, со смещением, равным двум.

2. Приемник, содержащий: блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; и контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; при этом структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно; при этом количество циклов равно шести, при этом первый цикл указывает, что выбраны первый, третий и пятый банки запоминающих устройств, со смещением, равным нулю; второй цикл указывает, что выбраны второй, третий и шестой банки запоминающих устройств, с соответствующими смещениями, равными ноль, один и ноль; третий цикл указывает, что выбраны первый, четвертый и пятый банки запоминающих устройств, с соответствующими смещениями, равными один, ноль и один; четвертый цикл указывает, что выбраны второй, четвертый, и шестой банки запоминающих устройств, со смещением, равным единице; пятый цикл указывает, что выбраны первый, четвертый и пятый банки запоминающих устройств, со смещением, равным двум; и шестой цикл указывает, что выбраны второй, третий и шестой банки запоминающих устройств, со смещением, равным двум.

3. Приемник, содержащий: блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; и контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; при этом структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно; при этом количество циклов равно шести, при этом первый цикл указывает, что выбраны первый и третий банки запоминающих устройств, со смещением, равным нулю; второй цикл указывает, что выбраны второй и первый банки запоминающих устройств, с соответствующими смещениями, равными нулю и единице; третий цикл указывает, что выбраны четвертый и третий банки запоминающих устройств, с соответствующими смещениями, равными нулю и единице; четвертый цикл указывает, что выбраны второй и четвертый банки запоминающих устройств, со смещением, равным единице; пятый цикл указывает, что выбраны первый и второй банки запоминающих устройств, со смещением, равным двум; и шестой цикл указывает, что выбраны третий и четвертый банки запоминающих устройств, со смещением, равным двум.

4. Приемник, содержащий: блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; и контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; при этом структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно; при этом количество циклов равно десяти, при этом первый цикл указывает, что выбраны первый и третий банки запоминающих устройств, со смещением, равным нулю; второй цикл указывает, что выбраны второй и первый банки запоминающих устройств, с соответствующими смещениями, равными нулю и единице; третий цикл указывает, что выбраны четвертый и третий банки запоминающих устройств, с соответствующими смещениями, равными нулю и единице; четвертый цикл указывает, что выбраны второй и первый банки запоминающих устройств, с соответствующими смещениями, равными единице и двум; пятый цикл указывает, что выбраны четвертый и третий банки запоминающих устройств, с соответствующими смещениями, равными единице и двум; шестой цикл указывает, что выбраны второй и четвертый банки запоминающих устройств, со смещением, равным двум; седьмой цикл указывает, что выбраны первый и третий банки запоминающих устройств, со смещением, равным трем; восьмой цикл указывает, что выбраны второй и первый банки запоминающих устройств, с соответствующими смещениями, равными трем и четырем; девятый цикл указывает, что выбраны четвертый и третий банки запоминающих устройств, с соответствующими смещениями, равными трем и четырем; и десятый цикл указывает, что выбраны второй и четвертый банки запоминающих устройств, со смещением, равным четырем.

5. Приемник, содержащий: блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; и множество мультиплексоров, предназначенных для приема множества третьих значений и передачи выбранных третьих значений в каждый из соответствующего множества банков запоминающих устройств, причем третьи значения выбираются контроллером.

6. Приемник по п.5, в котором первое и второе значения являются синфазным (I) и квадратурным (Q) значением.

7. Приемник по п.5, в котором третьи значения являются значениями мягкого решения.

8. Приемник по п.5, в котором третьи значения представляют собой значения логарифмического отношения правдоподобия.

9. Приемник по п.5, в котором количество банков запоминающих устройств равно удвоенному количеству третьих значений.

10. Приемник по п.5, в котором два или более сохраненных третьих значений могут быть извлечены из двух или более из множества банков запоминающих устройств одновременно.

11. Приемник по п.5, в котором структура сохранения может быть выбрана из множества структур сохранения, причем структура сохранения выбрана в соответствии с одним из множества форматов передачи.

12. Приемник по п.11, в котором множество форматов передачи содержит 16-позиционную квадратурную амплитудную модуляцию (КАМ).

13. Приемник по п.11, в котором множество форматов передачи содержит кодирование со скоростью 1/3.

14. Приемник по п.5, в котором множество банков запоминающих устройств имеет размер, соответствующий размерам одного или более пакетов кодера.

15. Приемник по п.5, в котором структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно.

16. Приемник по п.15, в котором выбор банка, выбор смещения и выбор третьего значения установлены в соответствии со структурой последовательности кодирования.

17. Приемник по п.15, в котором количество циклов в структуре сохранения в два раза больше, чем количество кодированных символов в ассоциированной структуре последовательности кодирования.

18. Приемник по п.5, в котором контроллер формирует адрес сохранения для одного или более банков запоминающих устройств в соответствии со структурой сохранения, причем каждый адрес сохранения вычисляется с использованием базового адреса, добавляемого к смещению, указанному структурой сохранения, причем базовый адрес получает приращение на фиксированную величину, после окончания каждой последовательной итерации структуры сохранения.

19. Приемник по п.18, в котором базовый адрес установлен в исходное значение и повторно устанавливается в исходное значение после сохранения заданного количества третьих значений.

20. Приемник по п.5, в котором контроллер выбирает два или более банков запоминающих устройств для одновременного извлечения сохраненных третьих значений, в соответствии с адресом, причем после каждого одновременного извлечения данных выполняется приращение адреса.

21. Приемник по п.5, дополнительно содержащий декодер для приема последовательности из двух или более третьих значений и декодирования из них множества пятых значений.

22. Приемник по п.21, в котором декодер представляет собой турбодекодер.

23. Приемник по п.5, дополнительно содержащий демодулятор для демодуляции принятого сигнала для получения демодулированных символов.

24. Приемник, содержащий: блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; и множество шин с тремя состояниями, соединенных с множеством банков запоминающих устройств, причем каждая шина с тремя состояниями предназначена для приема третьего значения, выбираемого контроллером, и каждый банк запоминающих устройств предназначен для сохранения значения соответствующей шины с тремя состояниями под управлением контроллера.

25. Система беспроводной связи, содержащая обратный перемежитель, содержащий блок отображения, принимающий, по меньшей мере, одну пару принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, и генерирующий множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; множество банков запоминающих устройств, причем каждый банк запоминающих устройств конфигурирован для хранения одного из третьих значений; контроллер, направляющий каждое из множества третьих значений в выбранный один из множества банков запоминающих устройств для одновременного сохранения в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств; и множество мультиплексоров, предназначенных для приема множества третьих значений и передачи выбранных третьих значений в каждый из соответствующего множества банков запоминающих устройств, причем третьи значения выбираются контроллером.

26. Способ обратного перемежения, содержащий: прием, по меньшей мере, одной пары принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение; отображение, по меньшей мере, первого и второго значения на множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; прием множества третьих значений и передачи выбранных третьих значений в каждый из соответствующего множества банков запоминающих устройств, причем третьи значения выбираются контроллером; и одновременного сохранения множества третьих значений во множестве банков запоминающих устройств в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств.

27. Способ по п.26, дополнительно содержащий: формирование адреса сохранения для одного или более банков запоминающих устройств в соответствии со структурой сохранения, причем каждый адрес сохранения вычисляют с использованием базового адреса, добавляемого к смещению, указанному структурой сохранения; и приращение базового адреса на фиксированную величину после окончания каждой последовательной итерации структуры сохранения.

28. Способ по п.26, в котором структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно.

29. Способ по п.26, дополнительно содержащий: одновременное извлечение двух или более сохраненных третьих значений из двух или более банков запоминающих устройств в соответствии с адресом извлечения; и приращение адреса извлечения последовательно после одновременного извлечения.

30. Способ по п.29, дополнительно содержащий передачу извлеченных сохраненных третьих значений в декодер для последующего их декодирования.

31. Способ по п.26, в котором каждое первое значение является синфазным (I) значением, и каждое второе значение является квадратурным (Q) значением, при этом способ дополнительно содержит демодуляцию принятых символов для получения, по меньшей мере, одной пары принятых значений символов.

32. Способ по п.26, в котором этап отображения выполняется так, что каждое из третьих значений является значением мягкого решения.

33. Способ по п.26, в котором этап отображения выполняется так, что каждое из третьих значений является значением логарифмического отношения правдоподобия.

34. Способ по п.26, в котором этап сохранения выполняется так, что количество банков запоминающих устройств равно удвоенному количеству третьих значений.

35. Способ по п.26, дополнительно содержащий одновременное извлечение двух или более сохраненных третьих значений из двух или более из множества банков запоминающих устройств.

36. Способ по п.26, дополнительно содержащий демодуляцию принятых символов для получения, по меньшей мере, одной пары принятых значений символов и определение структуры сохранения в соответствии с форматом передачи принятых символов.

37. Способ по п.36, в котором формат передачи выбран из группы, состоящей из кодирования со скоростью 1/3 и кодирования со скоростью 1/5.

38. Способ по п.36, в котором формат передачи выбран из группы, состоящей из 16-позиционной квадратурной амплитудной модуляции (КАМ), 8-позиционной фазовой манипуляции (8PSK) и квадратурной фазовой манипуляции (QPSK).

39. Способ по п.26, в котором структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно.

40. Способ по п.26, дополнительно содержащий формирование адреса сохранения для одного или более банков запоминающих устройств в соответствии со структурой сохранения, причем каждый адрес сохранения вычисляется с использованием базового адреса, добавляемого к смещению, указанному структурой сохранения, причем базовый адрес получает приращение на фиксированную величину, после окончания каждой последовательной итерации структуры сохранения.

41. Способ по п.26, дополнительно содержащий выбор двух или более банков запоминающих устройств и одновременное извлечение сохраненных третьих значений в соответствии с адресом, и выполнение приращения адреса после этапа одновременного извлечения.

42. Приемник, содержащий: средство для приема, по меньшей мере, одной пары принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение, средство для отображения, по меньшей мере, первого и второго значения на множество третьих значений в ответ на, по меньшей мере, одну пару принятых значений символов; средство для приема множества третьих значений и передачи выбранных третьих значений на каждый из соответствующего множества банков запоминающих устройств, причем третьи значения выбираются контроллером; и средство для одновременного сохранения множества третьих значений во множестве банков запоминающих устройств в соответствии со структурой сохранения, при этом структура сохранения определена для обеспечения обратного перемежения путем извлечения значений из множества банков запоминающих устройств.

43. Машиночитаемый носитель, содержащий код для обеспечения компьютером приема, по меньшей мере, одной пары принятых значений символов, причем каждая пара принятых значений символов содержит первое значение и второе значение; код для обеспечения компьютером отображения, по меньшей мере, первого и второго значения на множество третьих значений, в ответ на, по меньшей мере, одну пару принятых значений символов; код для обеспечения компьютером приема множества третьих значений и передачи выбранных третьих значений в каждый из соответствующего множества банков запоминающих устройств, причем третьи значения выбираются контроллером; и код для обеспечения компьютером одновременного сохранения множества третьих значений во множестве банков запоминающих устройств в соответствии со структурой сохранения, причем структура сохранения определена так, чтобы обеспечивать обратное перемежение путем извлечения значений из множества банков запоминающих устройств.

44. Машиночитаемый носитель по п.43, в котором каждое первое значение является синфазным (I) значением, и каждое второе значение является квадратурным (Q) значением, дополнительно содержащий код для обеспечения компьютером демодуляции принятых символов для получения, по меньшей мере, одной пары принятых значений символов.

45. Машиночитаемый носитель по п.43, в котором отображение выполняется так, что каждое из третьих значений является значением мягкого решения.

46. Машиночитаемый носитель по п.43, в котором отображение выполняется так, что каждое из третьих значений является значением логарифмического отношения правдоподобия.

47. Машиночитаемый носитель по п.43, в котором сохранение выполняется так, что количество банков запоминающих устройств равно удвоенному количеству третьих значений.

48. Машиночитаемый носитель по п.43, дополнительно содержащий одновременное извлечение двух или более сохраненных третьих значений из двух или более из множества банков запоминающих устройств.

49. Машиночитаемый носитель по п.43, дополнительно содержащий код для обеспечения компьютером демодуляции принятых символов для получения, по меньшей мере, одной пары принятых значений символов и код для обеспечения компьютером определения структуры сохранения в соответствии с форматом передачи принятых символов.

50. Машиночитаемый носитель по п.49, в котором формат передачи выбран из группы, состоящей из кодирования со скоростью 1/3 и кодирования со скоростью 1/5.

51. Машиночитаемый носитель по п.49, в котором формат передачи выбран из группы, состоящей из 16-позиционной квадратурной амплитудной модуляции (КАМ), 8-позиционной фазовой манипуляции (8PSK) и квадратурной фазовой манипуляции (QPSK).

52. Машиночитаемый носитель по п.43, в котором структура сохранения содержит множество циклов, причем каждый цикл указывает выбранный поднабор из множества банков запоминающих устройств и значение смещения адреса для каждого банка запоминающих устройств в выбранном поднаборе, причем каждый из банков запоминающих устройств в выбранном поднаборе предназначен для сохранения одного из множества третьих значений, соответственно.

53. Машиночитаемый носитель по п.43, дополнительно содержащий код для обеспечения компьютером формирования адреса сохранения для одного или более банков запоминающих устройств в соответствии со структурой сохранения, причем каждый адрес сохранения вычисляется с использованием базового адреса, добавляемого к смещению, указанному структурой сохранения, причем базовый адрес получает приращение на фиксированную величину, после окончания каждой последовательной итерации структуры сохранения.