Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), непрерывных стабилизаторах напряжения и т.п.).

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах с так называемой «архитектурой входного каскада операционного усилителя µА741» [1-28] или комплементарных каскодных дифференциальных усилителей (ККДУ). На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом, стали основным усилительным элементом многих аналоговых интерфейсов. Предполагаемое изобретение относится к данному подклассу устройств.

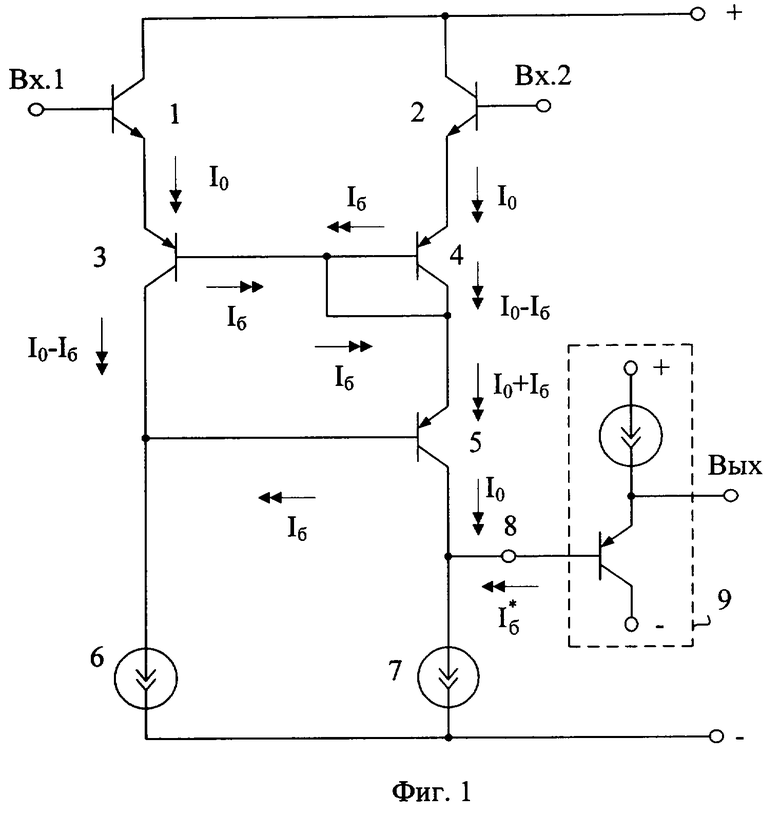

Прототипом (фиг.1) заявляемого устройства является комплементарный каскодный дифференциальный усилитель, описанный в патенте фирмы Texas Instruments (США) № 3.649.926, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с эмиттерами первого 3 и второго 4 выходных транзисторов, третий выходной транзистор 5, эмиттер которого соединен с коллектором и базой второго 4 выходного транзистора и базой первого 3 выходного транзистора, база подключена к первому 6 токостабилизирующему двухполюснику и связана с коллектором первого 3 выходного транзистора, а коллектор подключен ко второму 17 токостабилизирующему двухполюснику 7 и входу 8 выходного каскада 9.

Существенный недостаток известного ККДУ состоит в том, что он имеет сравнительно большое напряжение смещения нуля (Uсм), а также невысокий коэффициент усиления по напряжению (Ky=uвых/uвх).

Основная цель предлагаемого изобретения состоит в повышении статической точности ККДУ. Дополнительная цель - повышение коэффициента усиления дифференциального сигнала.

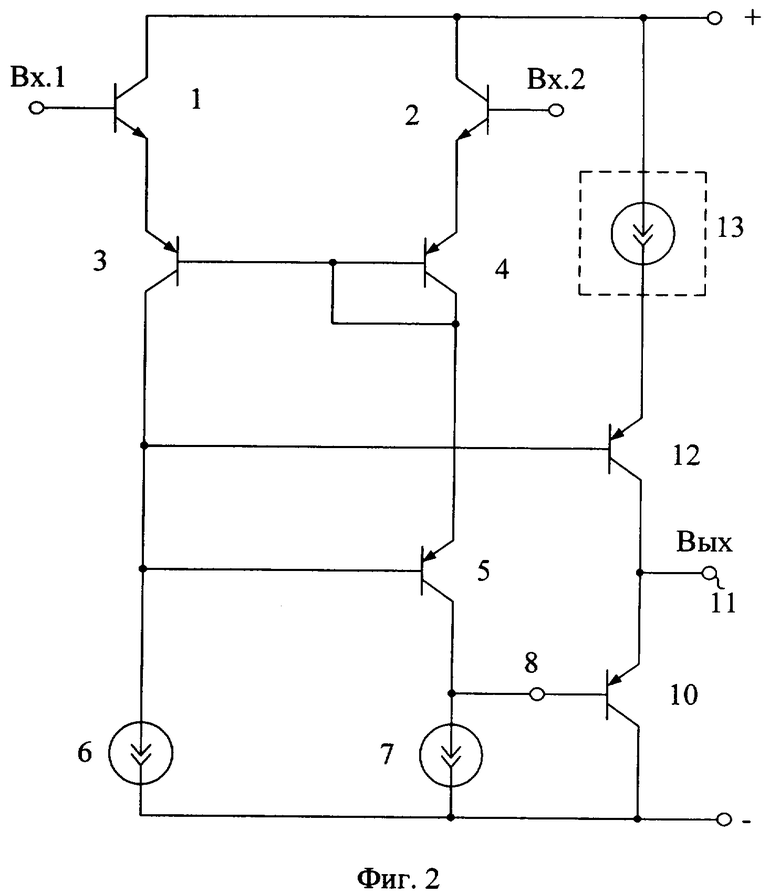

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с эмиттерами первого 3 и второго 4 выходных транзисторов, третий выходной транзистор 5, эмиттер которого соединен с коллектором и базой второго 4 выходного транзистора и базой первого 3 выходного транзистора, база подключена к первому 6 токостабилизирующему двухполюснику и связана с коллектором первого 3 выходного транзистора, а коллектор подключен ко второму 17 токостабилизирующему двухполюснику 7 и входу 8 выходного каскада 9, предусмотрены новые элементы и связи - выходной каскад 9 выполнен в виде эмиттерного повторителя на первом вспомогательном транзисторе 10, эмиттер которого соединен с выходом 11 комплементарного каскодного дифференциального усилителя и коллектором дополнительного транзистора 12, база которого соединена с коллектором первого 3 выходного транзистора, а эмиттер соединен с цепью установления статического режима 3 дополнительного транзистора 12.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения.

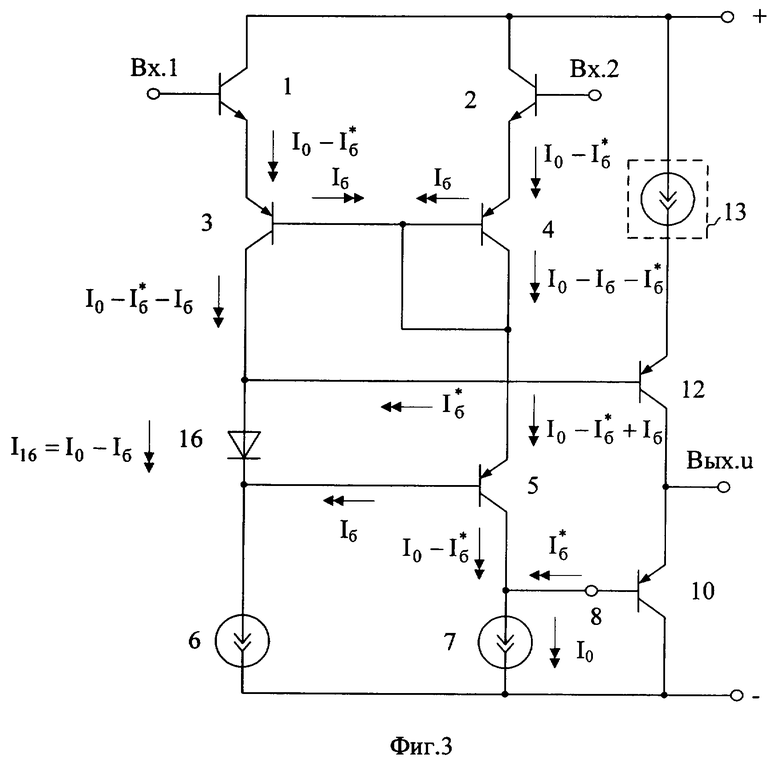

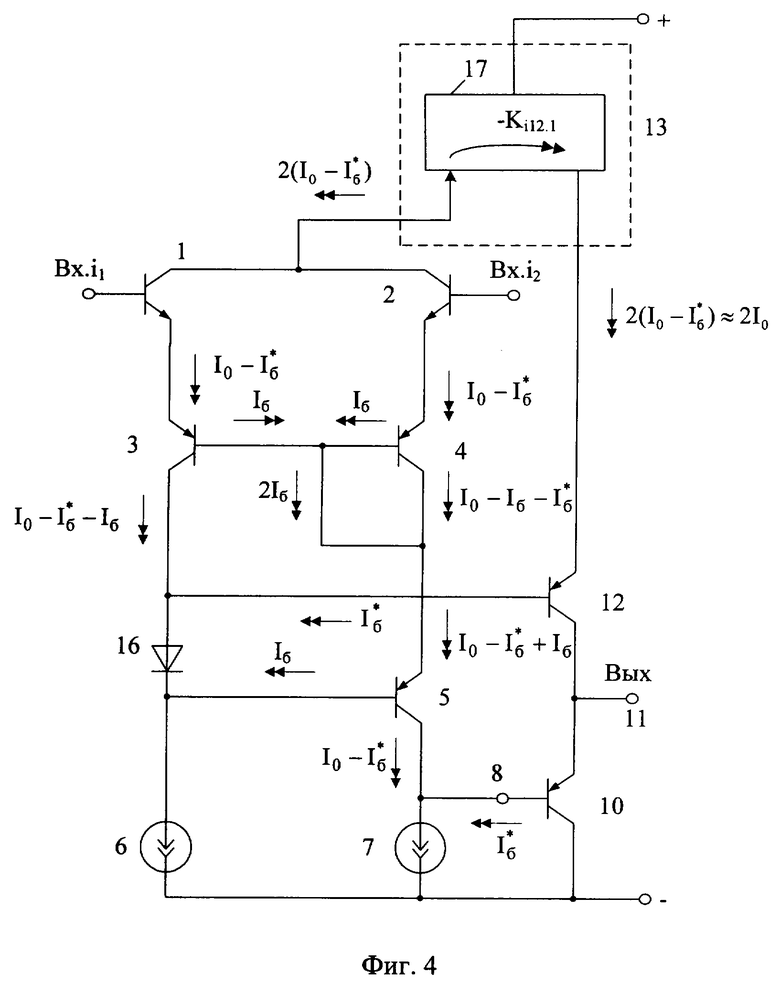

На фиг.3 приведена схема ККДУ, соответствующего п.2, а на фиг.4 - п.3 формулы изобретения.

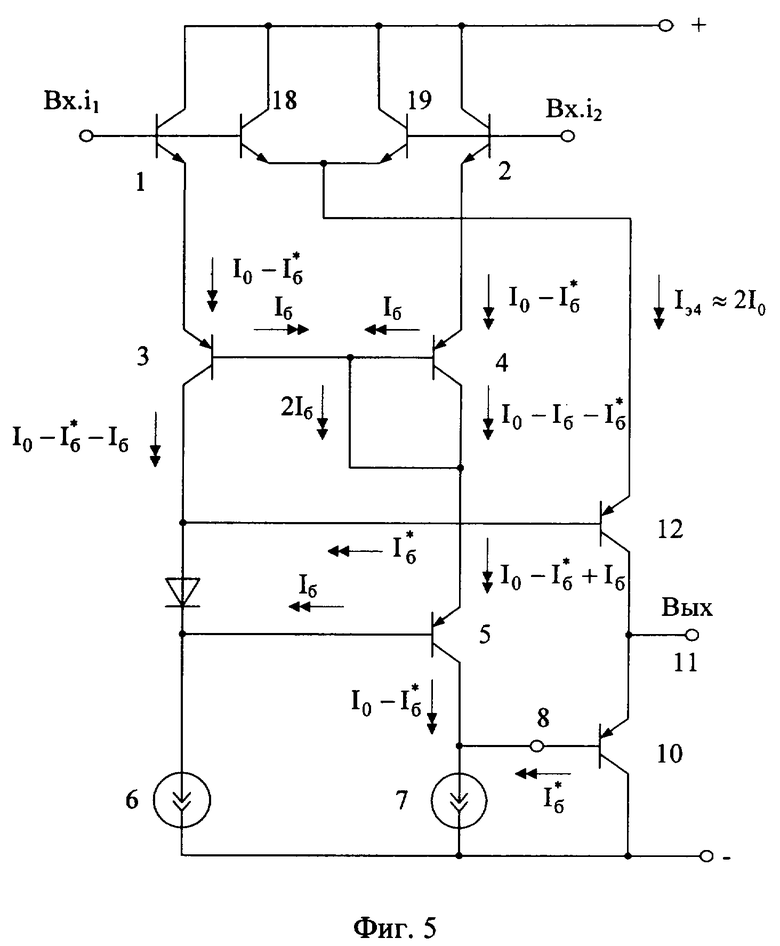

На фиг.5 - схема, соответствующая п.4 формулы изобретения.

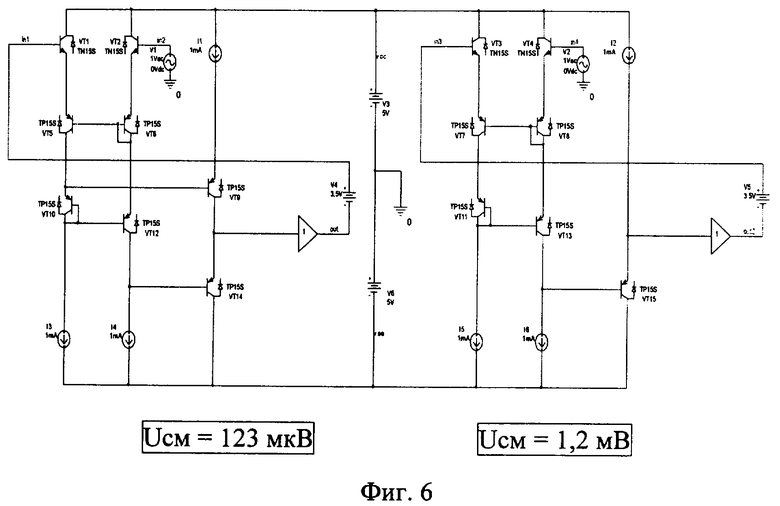

На фиг.6 - схема заявляемого и известного устройств в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

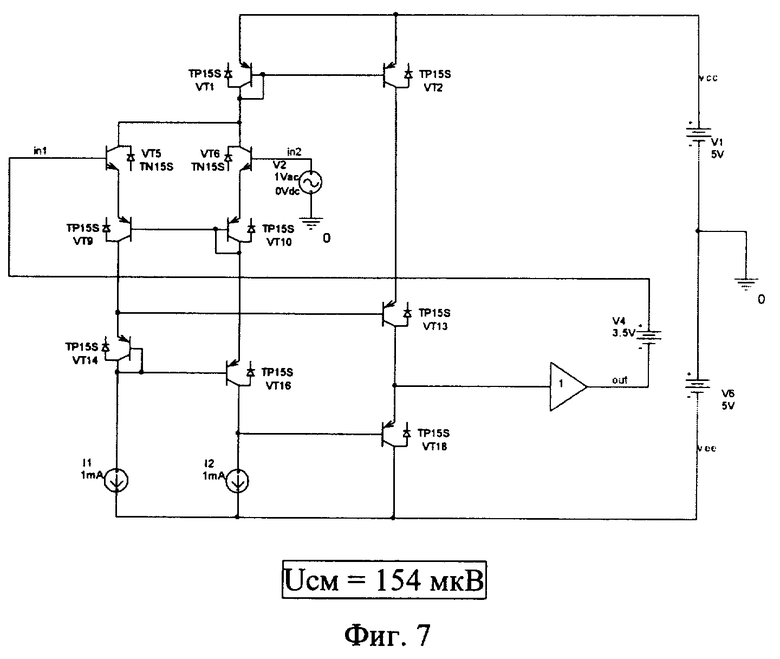

На фиг.7 - схема фиг.4 в среде PSpice.

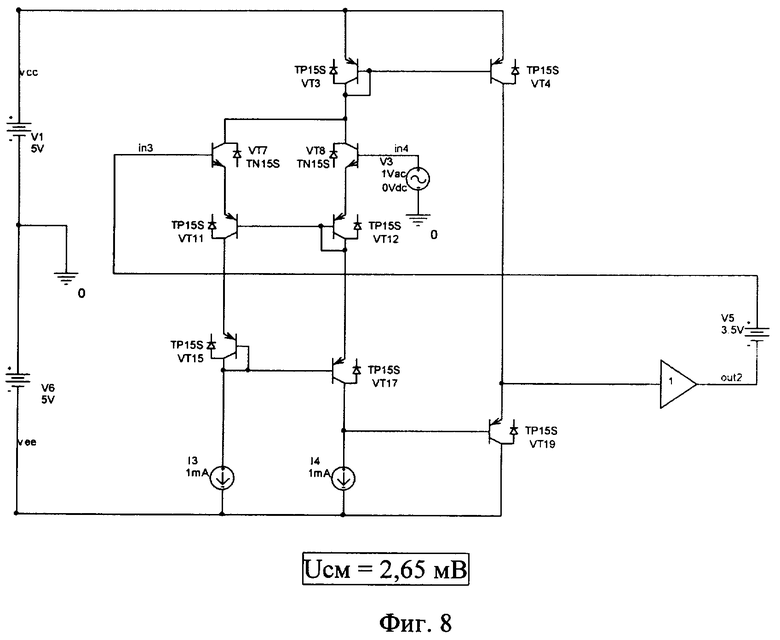

На фиг.8 - результаты компьютерного моделирования Uсм схемы-прототипа для его сравнения с ККДУ фиг.7.

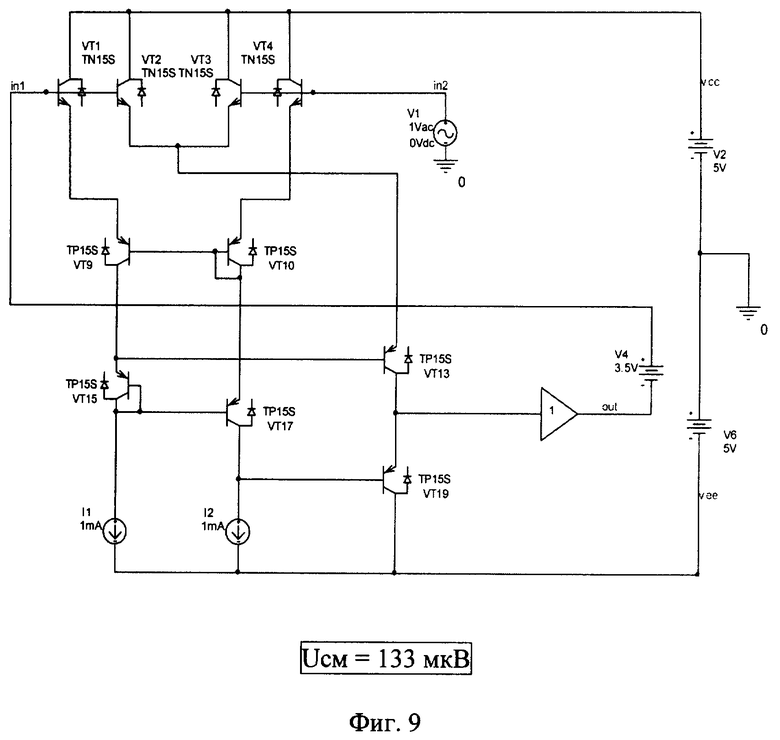

На фиг.9 - схема фиг.5 в среде PSpice.

Сопоставление результатов моделирования фиг.6-9 позволяет определить выигрыш по систематической составляющей Uсм (без учета разброса параметров элементов схемы), который дает предлагаемое техническое решение.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с эмиттерами первого 3 и второго 4 выходных транзисторов, третий выходной транзистор 5, эмиттер которого соединен с коллектором и базой второго 4 выходного транзистора и базой первого 3 выходного транзистора, база подключена к первому 6 токостабилизирующему двухполюснику и связана с коллектором первого 3 выходного транзистора, а коллектор подключен ко второму 17 токостабилизирующему двухполюснику 7 и входу 8 выходного каскада 9. Выходной каскад 9 выполнен в виде эмиттерного повторителя на первом вспомогательном транзисторе 10, эмиттер которого соединен с выходом 11 комплементарного каскодного дифференциального усилителя и коллектором дополнительного транзистора 12, база которого соединена с коллектором первого 3 выходного транзистора, а эмиттер соединен с цепью установления статического режима 3 дополнительного транзистора 12.

В устройстве фиг.3 в соответствии с п.2 формулы изобретения база третьего выходного транзистора 5 соединена с коллектором первого выходного транзистора 3 через дополнительный p-n переход 16.

В устройстве фиг.4 в соответствии с п.3 формулы изобретения цепь установления статического режима 13 дополнительного транзистора 12 выполнена в виде дополнительного токового зеркала 17, выход которого соединен с эмиттером дополнительного транзистора 12, а вход соединен с коллекторами первого 1 и второго 2 входных транзисторов.

В устройстве фиг.5 в соответствии с п.4 формулы изобретения цепь установления статического режима 13 дополнительного транзистора 12 выполнена на основе второго 18 и третьего 19 вспомогательных транзисторов, эмиттеры которых соединены с эмиттерами дополнительного транзистора 12, а базы соединены с соответствующими базами первого 1 и второго 2 входных транзисторов.

Описание фиг.6-9 дано выше.

Рассмотрим работу заявляемого ДУ фиг.3.

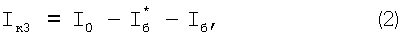

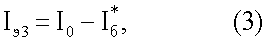

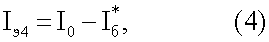

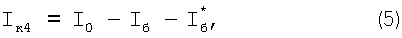

В статическом режиме в схеме фиг.3 устанавливаются следующие токи:

где Iб - ток базы транзисторов 3, 4, 5;

- ток базы транзисторов 10 и 12;

- ток базы транзисторов 10 и 12;

Iэi, Iкi - ток эмиттера (коллектора) транзисторов схемы.

Если выбрать токи I6=I7=I0 двухполюсников 6 и 7 одинаковыми, то во входной цепи 8 выходного каскада 9 обеспечивается полная взаимная компенсация статических токов, что является необходимым условием уменьшения Uсм:

В схеме ККДУ фиг.1

Это существенно ухудшает Uсм.

Аналогичные эффекты компенсации присутствуют в схемах фиг.4 и 5. Их отличие от схемы фиг.2 - другие способы организации статического режима транзистора 12.

Таким образом, заявляемое устройство характеризуется существенным преимуществом по Uсм в сравнении с ДУ-прототипом. Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.786.362.

2. Патент США №4.030.044.

3. Патент США №4.059.808, фиг.5.

4. Патент США №4.286.227.

5. Авт.свид. СССР №375754, H03f 3/38.

6. Авт.свид. СССР №843164, H03f 3/30.

7. Патент США №3.660.773.

8. Патент США №4.560.948.

9. Патент РФ №2930041, H03f 1/32.

10. Патент Японии №57-5364, H03f 3/343.

11. Патент ЧССР №134845, кл. 21а2 18/08.

12. Патент ЧССР №134849, кл. 21а2 18/08.

13. Патент ЧССР №135326, кл. 21а2 18/08.

14. Патент США №4.389.579.

15. Патент Англии №1543361, Н3Т.

16. Патент США №5.521.552 (фиг.3а).

17. Патент США №4.059.808.

18. Патент США №5.789.949.

19. Патент США №4.453.134.

20. Патент США №4.760.286.

21. Авт.свид. СССР №1283946.

22. Патент РФ №2019019.

23. Патент США №4.389.579.

24. Патент США №4.453.092.

25. Патент США №3.566.289.

26. Патент США №4.059.808 (фиг.2).

27. Патент США №3.649.926.

28. Патент США №4.714.894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412536C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2374755C2 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388137C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| КОМПЛЕМЕНТАРНЫЙ ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2370879C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412540C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), непрерывных стабилизаторах напряжения и т.п.). Технический результат - повышение статической точности и коэффициента усиления. Комплементарный каскодный дифференциальный усилитель (ККДУ) содержит первый (1) и второй (2) входные транзисторы (Т), эмиттеры которых соединены с эмиттерами первого (3) и второго (4) выходных Т, третий выходной Т (5), эмиттер которого соединен с коллектором и базой второго выходного Т (4) и базой первого (3) выходного Т, база подключена к первому (6) токостабилизирующему двухполюснику и связана с коллектором первого (3) выходного Т, а коллектор подключен ко второму (7) токостабилизирующему двухполюснику и входу (8) выходного каскада (9). Выходной каскад (9) выполнен в виде эмиттерного повторителя на первом вспомогательном Т (10), эмиттер которого соединен с выходом (11) ККДУ и коллектором дополнительного Т (12), база которого соединена с коллектором первого (3) выходного Т, а эмиттер соединен с цепью установления статического режима (13) дополнительного транзистора (12). 3 з.п. ф-лы, 9 ил.

1. Комплементарный каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых соединены с эмиттерами первого (3) и второго (4) выходных транзисторов, третий выходной транзистор (5), эмиттер которого соединен с коллектором и базой второго выходного (4) транзистора и базой первого (3) выходного транзистора, база подключена к первому (6) токостабилизирующему двухполюснику и связана с коллектором первого (3) выходного транзистора, а коллектор подключен ко второму (17) токостабилизирующему двухполюснику (7) и входу (8) выходного каскада (9), отличающийся тем, что выходной каскад (9) выполнен в виде эмиттерного повторителя на первом вспомогательном транзисторе (10), эмиттер которого соединен с выходом (11) комплементарного каскодного дифференциального усилителя и коллектором дополнительного транзистора (12), база которого соединена с коллектором первого (3) выходного транзистора, а эмиттер соединен с цепью установления статического режима (13) дополнительного транзистора (12).

2. Устройство по п.1, отличающееся тем, что база третьего выходного транзистора (5) соединена с коллектором первого выходного транзистора (3) через дополнительный p-n-переход (16).

3. Устройство по п.1, отличающееся тем, что цепь установления статического режима (13) дополнительного транзистора (12) выполнена в виде дополнительного токового зеркала (17), выход которого соединен с эмиттером дополнительного транзистора (12), а вход соединен с коллекторами первого (1) и второго (2) входных транзисторов.

4. Устройство по п.1, отличающееся тем, что цепь установления статического режима (13) дополнительного транзистора (12) выполнена на основе второго (18) и третьего (19) вспомогательных транзисторов, эмиттеры которых соединены с эмиттерами дополнительного транзистора (12), а базы соединены с соответствующими базами первого (1) и второго (2) входных транзисторов.

| US 3649926 А, 14.03.1972 | |||

| Дифференциальный усилитель | 1988 |

|

SU1608784A2 |

| US 4030044 A, 14.06.1977 | |||

| US 4059808 A, 22.11.1977. | |||

Авторы

Даты

2009-11-27—Публикация

2008-04-03—Подача