Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage» или «комплементарных дифференциальных усилителей (КДУ)») [1-20]. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Однако в практических схемах известных ДУ напряжение смещения нуля (Uсм) (эдс смещения нуля) даже при совершенно идентичных транзисторах измеряется единицами милливольт, что обусловлено свойствами их архитектуры - повышенным влиянием коэффициентов передачи по току используемых токовых зеркал на Uсм.

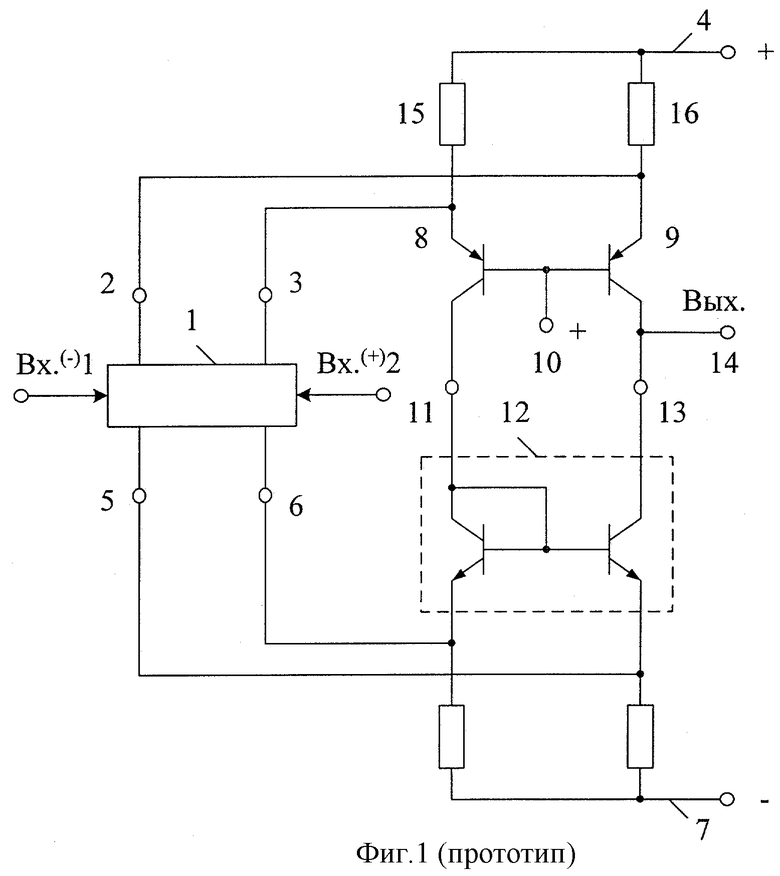

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4649352, содержащий комплементарный входной дифференциальный каскад 1, имеющий первый 2 и второй 3 противофазные токовые выходы, согласованные с шиной положительного источника питания 4, третий 5 и четвертый 6 противофазные токовые выходы, согласованные с шиной отрицательного источника питания 7, первый 8 и второй 9 выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 10, коллектор первого выходного транзистора 8 соединен со входом 11 первого токового зеркала 12, выход которого 13 связан с коллектором второго выходного транзистора 9 и выходом дифференциального усилителя 14, причем первый 2 и второй 3 токовые выходы комплементарного входного дифференциального каскада 1 соединены с эмиттерами первого 8 и второго 9 выходных транзисторов и соответствующими токостабилизирующими двухполюсниками 15 и 16.

Существенный недостаток известного ДУ состоит в том, что он имеет повышенные значения напряжения смещения нуля.

Отличие от единицы коэффициента передачи по току токовых зеркал данных ДУ не позволяет получить малые значения Uсм даже при совершенно идентичных транзисторах, что отрицательно сказывается на погрешностях аналоговых интерфейсов на их основе.

Основная цель предлагаемого изобретения состоит в уменьшении напряжения смещения нуля дифференциального усилителя в широком диапазоне изменения коэффициентов передачи по току его токовых зеркал.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем комплементарный входной дифференциальный каскад 1, имеющий первый 2 и второй 3 противофазные токовые выходы, согласованные с шиной положительного источника питания 4, третий 5 и четвертый 6 противофазные токовые выходы, согласованные с шиной отрицательного источника питания 7, первый 8 и второй 9 выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 10, коллектор первого выходного транзистора 8 соединен со входом 11 первого токового зеркала 12, выход которого 13 связан с коллектором второго выходного транзистора 9 и выходом дифференциального усилителя 14, причем первый 2 и второй 3 токовые выходы комплементарного входного дифференциального каскада 1 соединены с эмиттерами первого 8 и второго 9 выходных транзисторов и соответствующими токостабилизирующими двухполюсниками 15 и 16, предусмотрены новые элементы и связи - в схему введено дополнительное токовое зеркало 17, вход которого соединен с третьим токовым выходом 5 комплементарного входного дифференциального каскада 1, а выход связан с четвертым токовым выходом 6 комплементарного входного дифференциального каскада 1 и входом 11 первого токового зеркала 12.

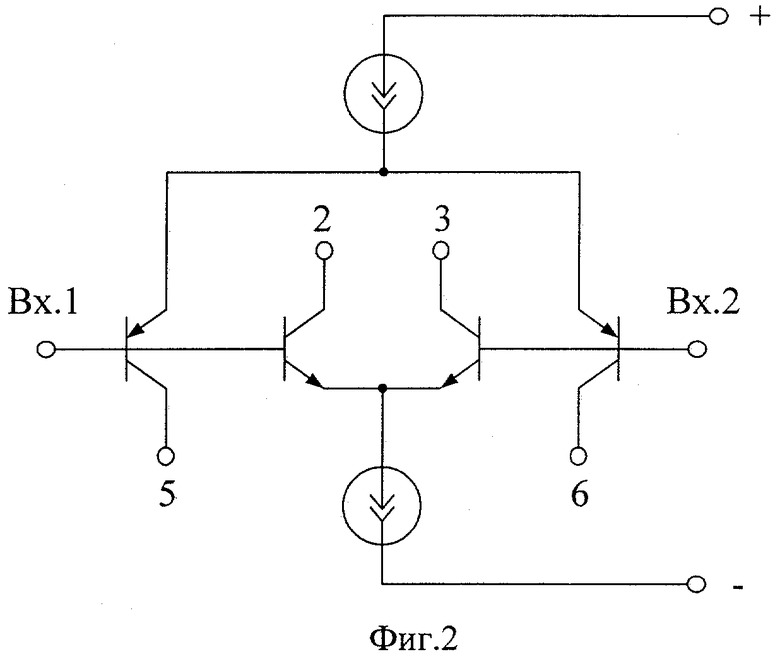

На фиг.2 представлена структура типового комплементарного дифференциального усилителя 1, реализованного на n-р-n и р-n-р транзисторах с источниками тока в их общей эмиттерной цепи.

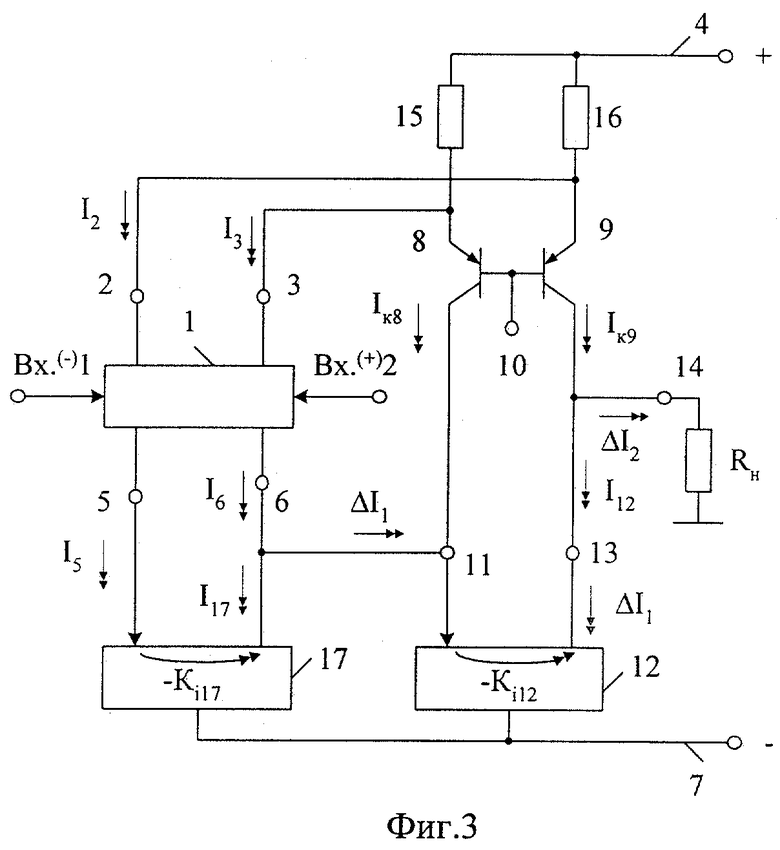

Схема заявляемого устройства в соответствии с формулой изобретения показана на фиг.3.

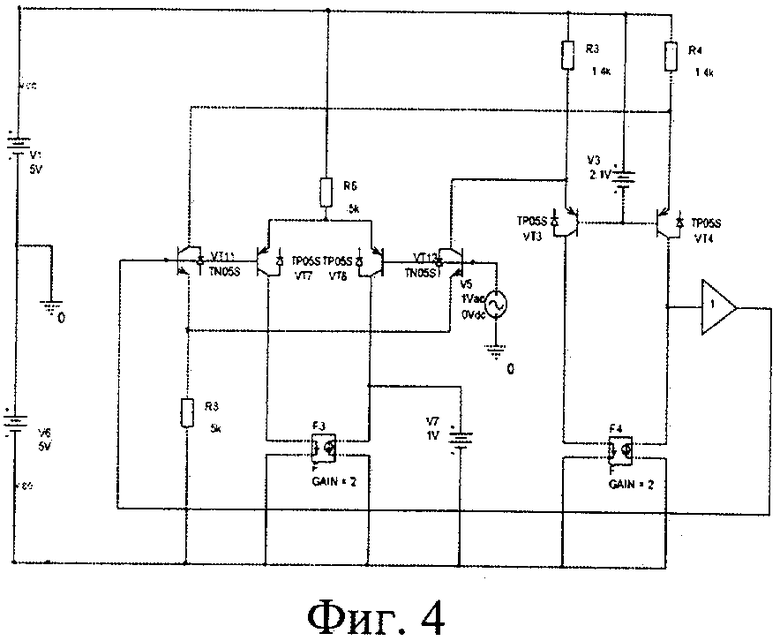

На фиг.4 показана компьютерная модель известного усилителя в среде компьютерного моделирования PSpice с использованием транзисторов ФГУП НПП «Пульсар».

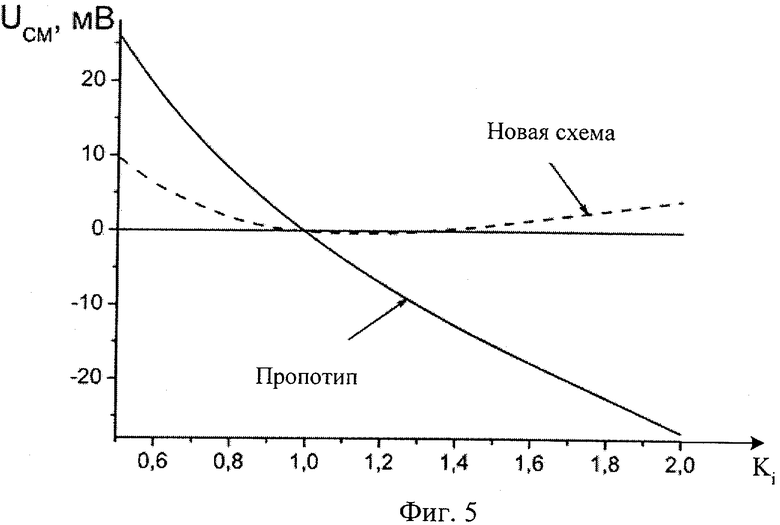

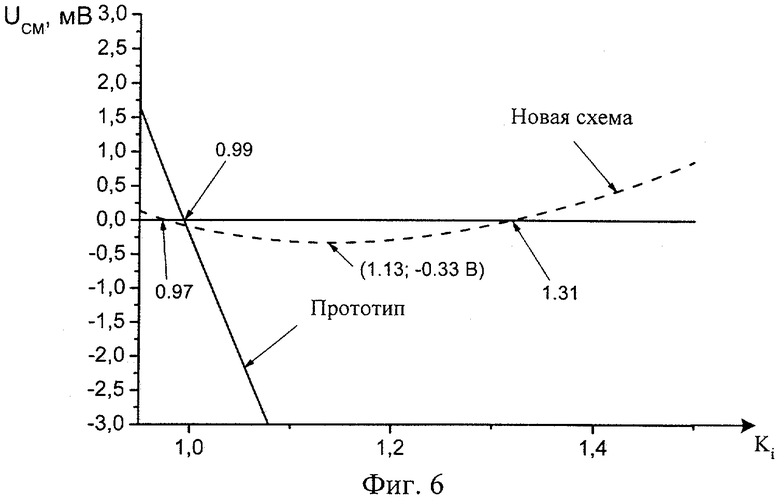

На фиг.5 и 6 представлены графики зависимости напряжения смещения нуля от коэффициентов передачи по току токовых зеркал (Кi).

Дифференциальный усилитель фиг.3 содержит комплементарный входной дифференциальный каскад 1, имеющий первый 2 и второй 3 противофазные токовые выходы, согласованные с шиной положительного источника питания 4, третий 5 и четвертый 6 противофазные токовые выходы, согласованные с шиной отрицательного источника питания 7, первый 8 и второй 9 выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 10, коллектор первого выходного транзистора 8 соединен со входом 11 первого токового зеркала 12, выход которого 13 связан с коллектором второго выходного транзистора 9 и выходом дифференциального усилителя 14, причем первый 2 и второй 3 токовые выходы комплементарного входного дифференциального каскада 1 соединены с эмиттерами первого 8 и второго 9 выходных транзисторов и соответствующими токостабилизирующими двухполюсниками 15 и 16. В схему введено дополнительное токовое зеркало 17, вход которого соединен с третьим токовым выходом 5 комплементарного входного дифференциального каскада 1, а выход связан с четвертым токовым выходом 6 комплементарного входного дифференциального каскада 1 и входом 11 первого токового зеркала 12.

Рассмотрим работу заявляемого ДУ.

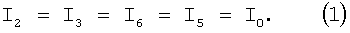

В статическом режиме выходные токи входного комплементарного каскада 1 равны

При идентичных сопротивлениях токостабилизирующих двухполюсников 15 и 16 коллекторные токи транзисторов 8 и 9 также могут быть равны друг

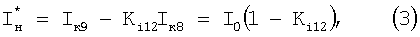

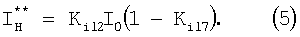

При этом в цепи нагрузки Rн создается первая составляющая статического тока ошибки  , обусловленная разностью

, обусловленная разностью

где Кi12≤1 - коэффициент усиления по току токового зеркала 12.

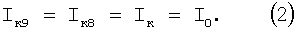

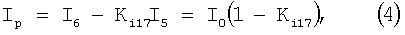

Аналогичное уравнение можно записать для входной цепи повторителя тока 17, который идентичен токовому зеркалу 12:

где Ki17 - коэффициент усиления по току токового зеркала 17.

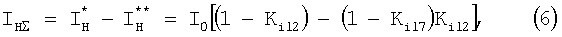

Разностный ток Iр поступает на вход 1 токового зеркала 12 и создает в нагрузке Rн вторую составляющую статической ошибки  , которая противоположна по знаку первой составляющей

, которая противоположна по знаку первой составляющей

В результате суммарный статический ток ошибки в нагрузке Rн уменьшается

где Кi=Kil2=Ki17≤1.

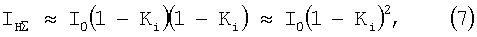

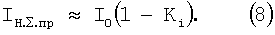

В схеме ДУ-прототипа при идентичных статических режимах

Поэтому напряжение смещения нуля заявляемой и известной схем

где Sду - крутизна усиления дифференциального сигнала ДУ.

Таким образом, в предлагаемом устройстве составляющая напряжения смещения нуля, обусловленная влиянием токовых зеркал, в Nc-раз меньше, чем в ДУ-прототипе, где

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice - напряжение смещения нуля в зависимости от численных значений Ki уменьшается в 5-10 раз.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №2193273, H03F 3/45.

2. Патент Японии №53-25232, H03F 3/26, 98(5) А332.

3. Патент US 2001/0052818 А1, H03F, 3/45.

4. Патент Японии № JP 8222972.

5. Авт. свид. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М. Радио и связь, 1989. - стр.103, Рис.6.11.

7. Патент США №6366170, B1 H03F/45.

8. Патент США №6268769, H03F/45.

9. Патент США №3974455, H03F/45.

10. Патент США №3968451, H03F/45.

11. Патент США №4837523, H03F/45.

12. Патент США №5291149, H03F/45.

13. Патент США №4636743, H03F/45.

14. Патент США №4783637, H03F/45.

15. Патент США №5515005, H03F/45.

16. Патент США №5291149, H03F/45.

17. Патент США №5140280, H03F/45.

18. Патент США №5455535, H03F/45.

19. Патент США №5523718, H03F/45.

20. Патент США №4600893, H03F/45.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2320078C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412536C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

Изобретение относится к радиотехнике и связи для использования в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в уменьшении напряжения смещения нуля в широком диапазоне изменения коэффициентов передачи по току токовых зеркал (ТЗ). Дифференциальный усилитель с малым напряжением смещения нуля (ДУ) содержит комплементарный входной дифференциальный каскад (ДК) (1), имеющий первый (2) и второй (3) противофазные токовые выходы, согласованные с положительной шиной источника питания (ИП) (4), третий (5) и четвертый (6) противофазные токовые выходы, согласованные с шиной отрицательного ИП (7), первый (8) и второй (9) выходные транзисторы (Т), объединенные базы которых подключены к источнику напряжения смещения (10), коллектор Т (8) соединен со входом (11) первого ТЗ (12), выход которого (13) связан с коллектором Т (9) и выходом ДУ (14), причем первый (2) и второй (3) токовые выходы ДК (1) соединены с эмиттерами первого (8) и второго (9) выходных Т и соответствующими токостабилизирующими двухполюсниками (15) и (16). В схему введено дополнительное ТЗ (17), вход которого соединен с третьим токовым выходом (5) ДК (1), а выход связан с четвертым токовым выходом (6) ДК (1) и входом (11) первого ТЗ (12). 6 ил.

Дифференциальный усилитель с малым напряжением смещения нуля, содержащий комплементарный входной дифференциальный каскад (1), имеющий первый (2) и второй (3) противофазные токовые выходы, согласованные с положительной шиной источника питания (4), третий (5) и четвертый (6) противофазные токовые выходы, согласованные с шиной отрицательного источника питания (7), первый (8) и второй (9) выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения (10), коллектор первого выходного транзистора (8) соединен со входом (11) первого токового зеркала (12), выход (13) которого связан с коллектором второго выходного транзистора (9) и выходом дифференциального усилителя (14), причем первый (2) и второй (3) токовые выходы комплементарного входного дифференциального каскада (1) соединены с эмиттерами первого (8) и второго (9) выходных транзисторов и соответствующими токостабилизирующими двухполюсниками (15) и (16), отличающийся тем, что в схему введено дополнительное токовое зеркало (17), вход которого соединен с третьим токовым выходом (5) комплементарного входного дифференциального каскада (1), а выход связан с четвертым токовым выходом (6) комплементарного входного дифференциального каскада (1) и входом (11) первого токового зеркала (12).

| US 4649352, 10.03.1987 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| US 5455535 A, 03.10.1995 | |||

| US 5153529 A, 06.10.1992 | |||

| US 4636743, 13.01.1987. | |||

Авторы

Даты

2008-08-20—Публикация

2007-04-25—Подача