Изобретение относится к области электросвязи и может быть использовано для определения состояния сети связи и оперативной идентификации стека коммуникационных протоколов ТСР/IP, применяемого в цифровых системах связи, в частности в сети передачи данных типа "Internet".

Известно устройство поиска информации по патенту РФ №2219577, класс G06F 17/40, заявленному 24.04.2002, содержащее делитель частоты, два блока памяти, вычитающий счетчик, четыре блока дешифрации, четыре счетчика, четыре блока приема адреса, два блока сравнения, два дешифратора и блок индикации.

Данное устройство имеет недостаток - узкую область применения, поэтому предназначено только для анализа сравнительно небольшого количества параметров проходящих через него потоков, что приводит к неустойчивому функционированию автоматизированных систем в условиях несанкционированного информационного воздействия и ограничивает область его применения в сетях передачи данных типа "Internet" в условиях несанкционированного воздействия (информационных атак).

Наиболее близким по технической сущности (прототипом) является устройство поиска информации, содержащее два блока памяти, девять счетчиков, одиннадцать блоков дешифрации, функционально объединенные в блок выделения параметров, блок сравнения, блок управления и блок индикации, по патенту №2301443, приоритет изобретения 04 июля 2005 г. Вход первого блока памяти является входом устройства поиска информации, а его выход подключен к информационному входу первого блока дешифрации, второй вход которого подключен к первому счетчику, а выход дешифратора - к входу второго счетчика, первый выход которого соединен с вторым входом второго блока дешифрации, первый вход которого подключен к выходу первого блока памяти. Выход второго блока дешифрации соединен с входом второго блока памяти, а выход второго счетчика соединен с входом третьего счетчика, выход которого соединен с первым входом третьего блока дешифрации, второй вход которого подключен к выходу первого блока памяти. Первый и второй выходы третьего блока дешифрации подключены к входам четвертого и пятого счетчиков. Выход счетчика подключен к первому входу пятого блока дешифрации, второй вход которого соединен с выходом первого блока памяти, выход пятого блока дешифрации соединен с вторым входом блока сравнения, первый вход которого подключен через четвертый блок дешифрации к выходу четвертого счетчика, причем второй вход четвертого блока дешифрации соединен с выходом первого блока памяти. Входы блока управления подключены к второму выходу первого блока дешифрации, к третьему выходу третьего блока дешифрации, к второму выходу блока сравнения, к второму выходу шестого блока дешифрации, к первому выходу седьмого блока дешифрации, к выходу восьмого блока дешифрации, к выходу девятого блока дешифрации, к первому выходу десятого блока дешифрации, к двум выходам одиннадцатого блока дешифрации. Одиннадцатый выход блока управления подключен к входу первого счетчика и к первому блоку памяти, двенадцатый выход блока управления к первому блоку памяти, тринадцатый выход к входу блока индикации. Выход второго блока памяти соединен с первым входом шестого счетчика, второй вход которого подключен к выходу первого блока сравнения, а выход счетчика соединен с входом шестого блока дешифрации, первый выход которого соединен с входом седьмого счетчика, выход которого подключен к входу седьмого блока дешифрации, второй выход которого соединен с входом восьмого счетчика, выход, которого подключен к первым входам десятого, восьмого и девятого блоков дешифрации, вторые входы каждого из которых соединены с выходом первого блока памяти. Вторые входы шестого, седьмого и одиннадцатого блоков дешифрации соединены с выходом первого блока памяти, а второй выход десятого блока дешифрации соединен с входом девятого счетчика, выход которого подключен к первому входу одиннадцатого блока дешифрации. Блок индикации является выходом устройства.

Данное устройство по сравнению с аналогом позволяет расширить область своего применения, в частности, для получения однозначного решения об использовании протокола TCP и о наличии неоднократно повторяющихся запросов на создание сколь угодно большого количества логических каналов связи путем сравнения последующего блока данных с предыдущим по девяти параметрам, что необходимо для обеспечения устойчивого функционирования автоматизированных систем в условиях несанкционированного воздействия), описанного, например, в книге Медведовский И.Д. и др. Атака на Internet. - М.: ДМК, 1999, стр.120-128.

К недостаткам устройства-прототипа относится анализ сравнительно небольшого количества параметров проходящих через него потоков, основанный на сигнатурном методе, что приводит к неустойчивому функционированию автоматизированных систем в условиях несанкционированного информационного воздействия, а также низкая достоверность принятия решения.

Технической задачей предлагаемого изобретения является разработка устройства определения состояния сети связи, обеспечивающего расширенную область применения и повышения достоверности принятия решения за счет расширения набора характеристических параметров, анализа протокола TCP, учета правил установления и ведения сеанса связи, выявления случаев аномального увеличения интенсивности информационного обмена, аномального увеличения нагрузки входящего трафика, изменения соотношения числа пакетов на установление и разъединение соединения, аномального увеличения числа пакетов, получивших отказ, определения достоверности используемого источником IP адреса, выявления случаев установки запрещенных комбинаций флагов и неправильной установки IP адресов получателя и отправителя пакета.

Поставленная цель достигается тем, что в известное устройство поиска информации, содержащее блок индикации, блок управления, блок сравнения IP адресов, блок SYN/FIN и блок выделения параметров, вход которого является информационным входом устройства, а третий и четвертый выходы подключены соответственно к первому и второму входам блока SYN/FIN, первый и второй выходы подключены соответственно к первому и второму входам блока сравнения IP адресов, первый и второй выходы блока управления подключены к первому и второму входам блока выделения параметров, дополнительно введены блок интенсивности, блок нагрузки, блок потерь, блок достоверности, блок нормировки, первые и вторые входы блоков интенсивности, нагрузки подключены соответственно к пятому, шестому и седьмому, восьмому выходам блока выделения параметров, а первый, второй, третий входы блока достоверности подключены соответственно к девятому, десятому и одиннадцатому выходам блока выделения параметров, двенадцатый выход блока выделения параметров подключен к девятнадцатому входу блока индикации, входом блока потерь является статистическая информация о соотношении числа пакетов, получивших отказ, к общему числу пришедших пакетов, первый выход блока SYN/FIN, выходы блока интенсивности, блока нагрузки и блока потерь подключены соответственно к первому, второму, третьему и четвертому входам блока нормировки, первый, второй, третий и четвертый выходы которого подключены соответственно к первому, второму, третьему и четвертому входам блока управления, выход блока достоверности подключен к восемнадцатому входу блока индикации, а выходы блока управления с третьего по восемнадцатый включительно подключены соответственно ко входам блока индикации со второго по семнадцатый включительно, выход блока сравнения IP адресов подключен к первому входу блока индикации.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «Новизна». Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из современного уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «Изобретательский уровень».

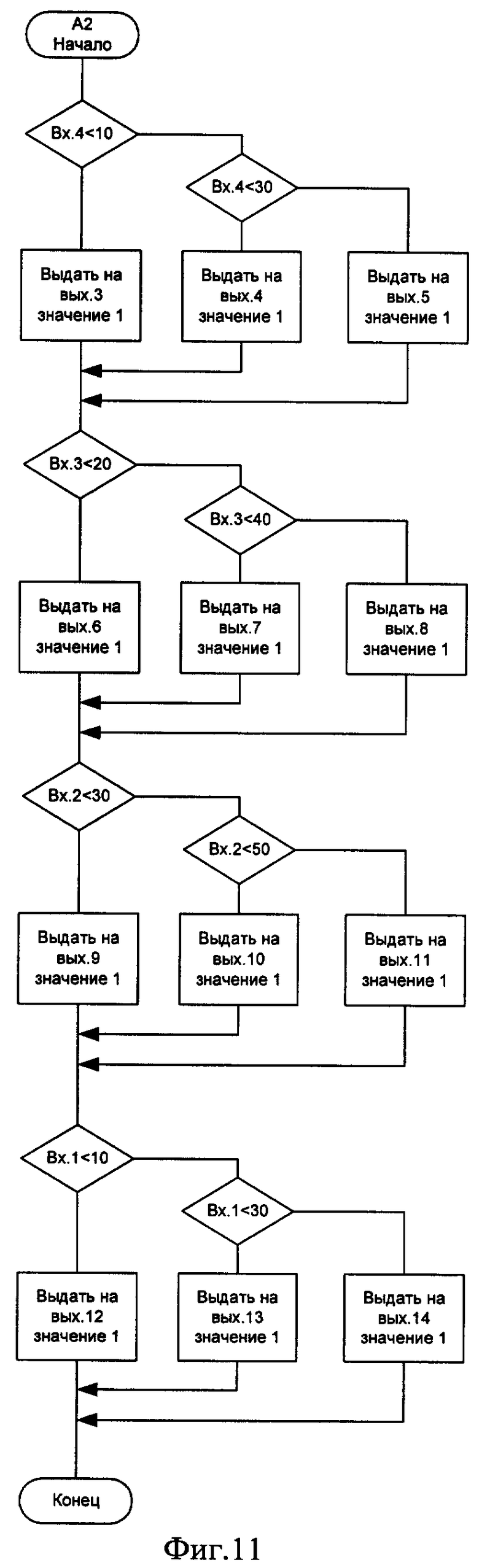

Заявленное устройство поясняется следующими чертежами:

фиг.1 - устройство определения состояния сети связи;

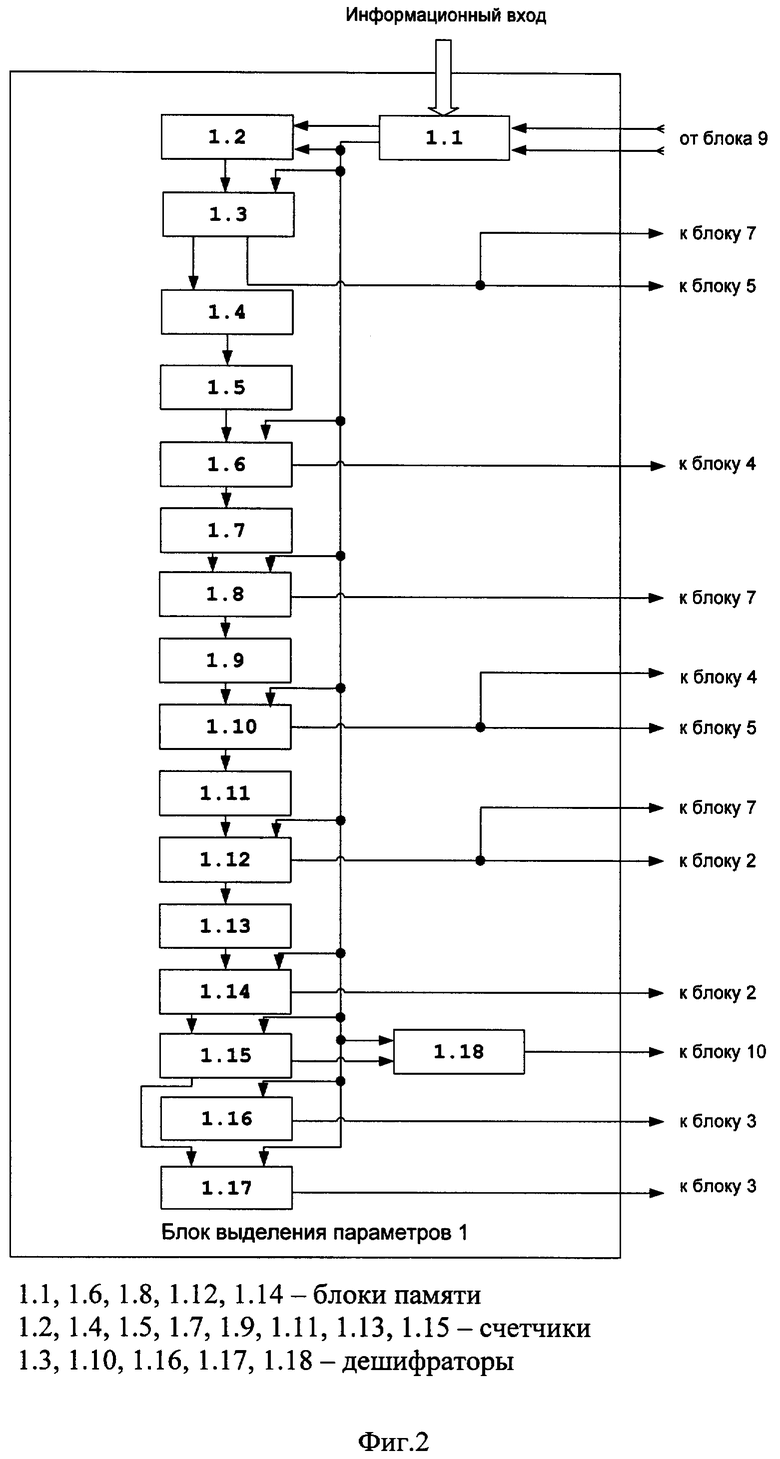

фиг.2 - структурная схема блока выделения параметров;

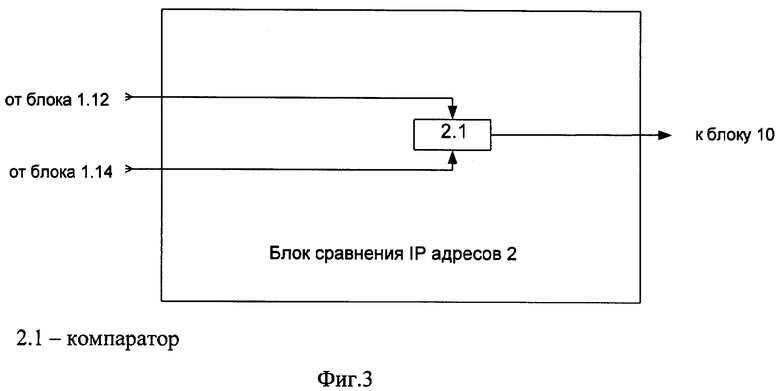

фиг.3 - структурная схема блока сравнения IP адресов;

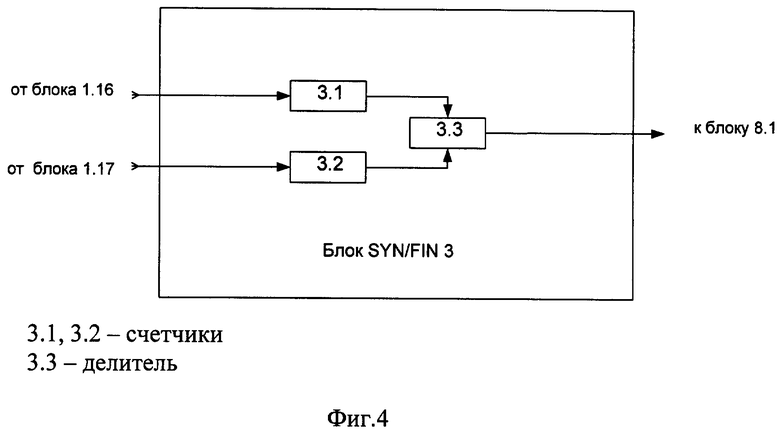

фиг.4 - структурная схема блока SYN/FIN;

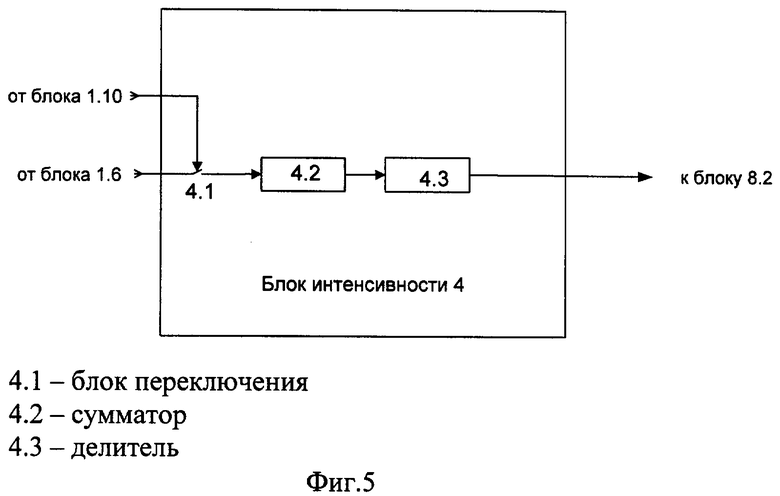

фиг.5 - структурная схема блока интенсивности;

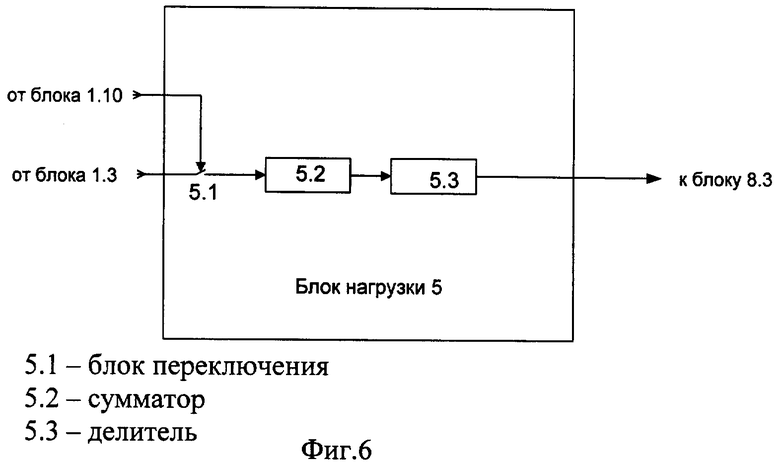

фиг.6 - структурная схема блока нагрузки;

фиг.7 - структурная схема блока достоверности;

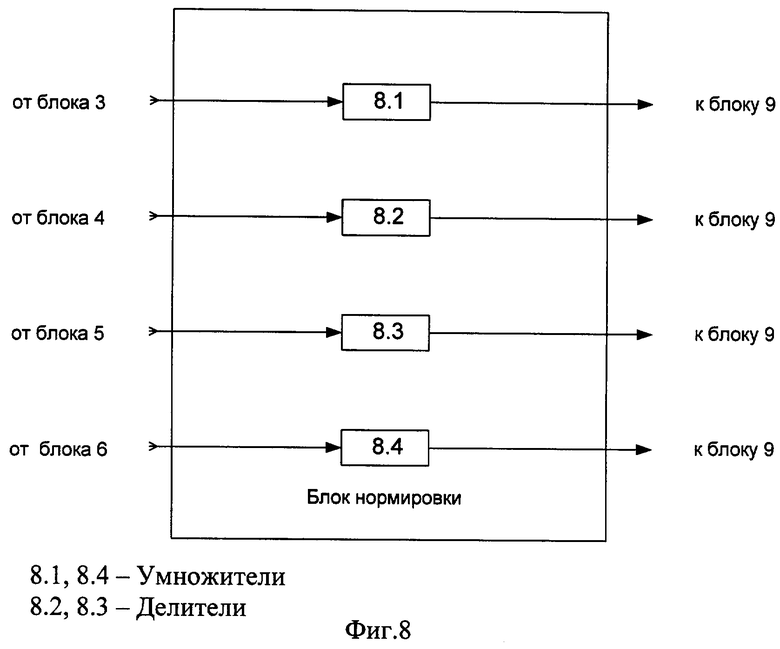

фиг.8 - структурная схема блока нормировки;

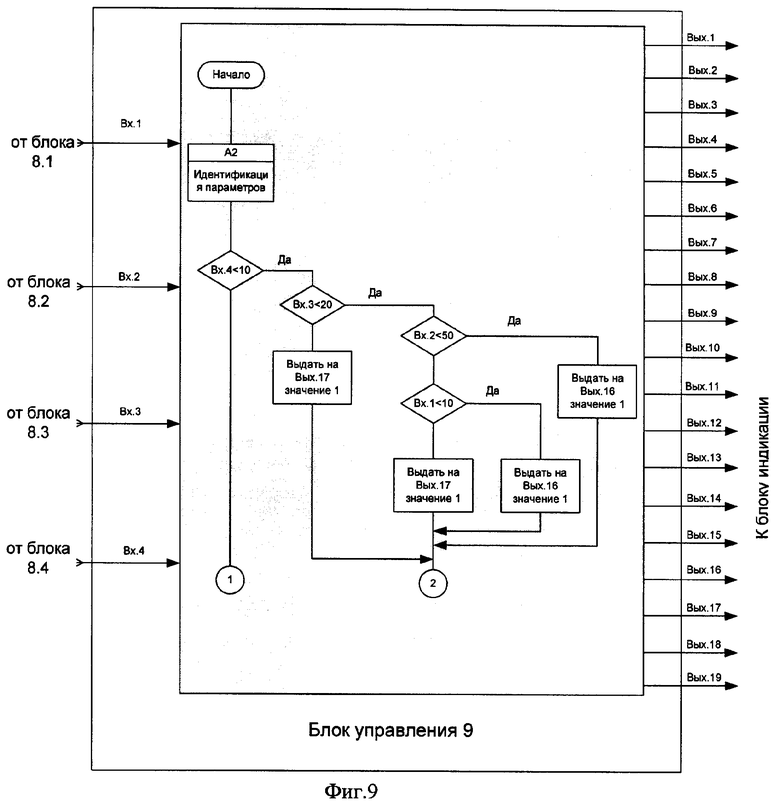

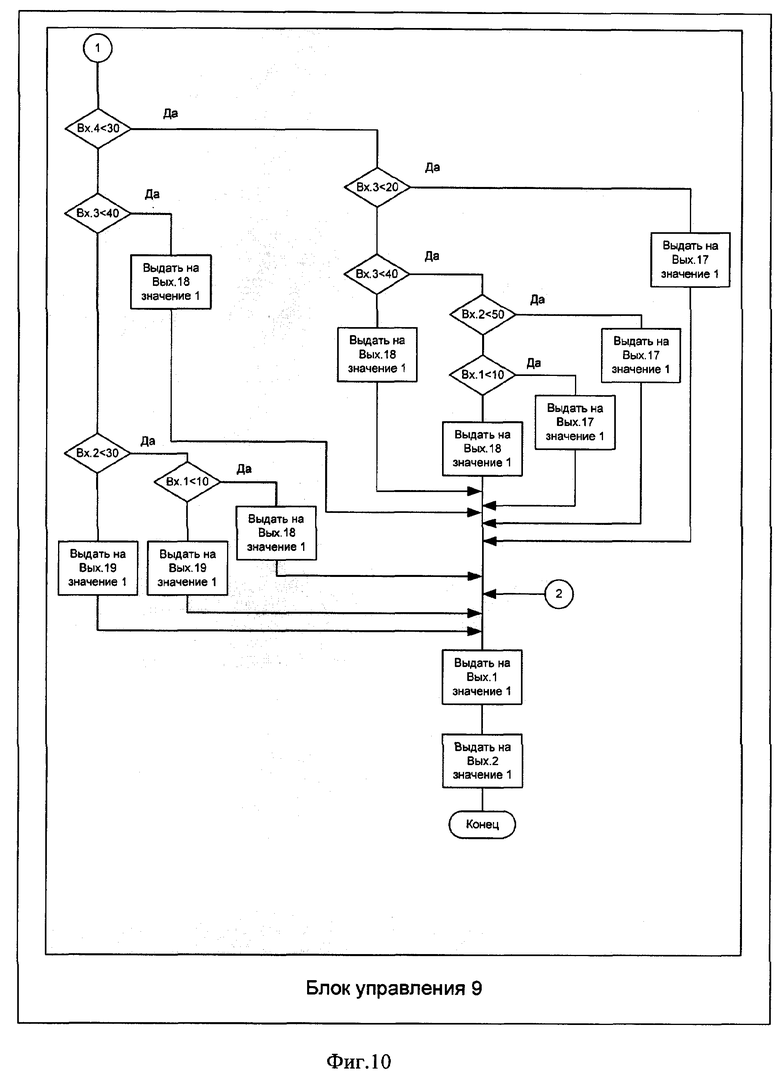

фиг.9-10 - структурная схема блока управления;

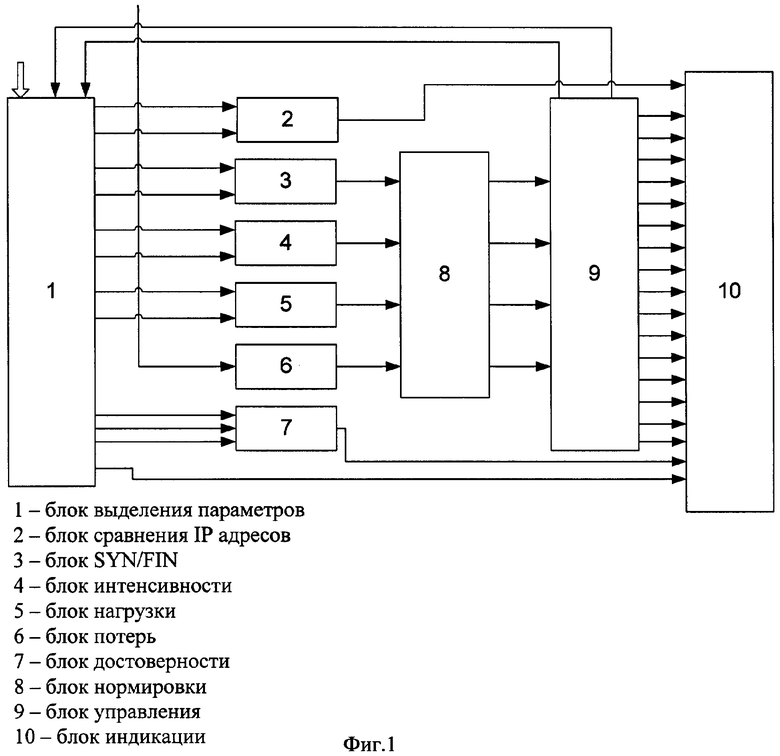

фиг.11 - схема алгоритма индикации.

Устройство определения состояния сети связи, показанное на фиг.1, содержит блок выделения параметров 1, блок сравнения адресов IP 2, блок SYN/FIN 3, блок интенсивности 4, блок нагрузки 5, блок потерь 6, блок достоверности 7, блок нормировки 8, блок управления 9, блок индикации 10.

Вход блока выделения параметров 1 является информационным входом устройства, а третий и четвертый выходы подключены соответственно к первому и второму входам блока SYN/FIN 3. Первый и второй выходы подключены соответственно к первому и второму входам блока сравнения IP адресов 2. Первый и второй выходы блока управления 9 подключены к первому и второму входам блока выделения параметров 1. Первые и вторые входы блоков интенсивности 4, нагрузки 5 подключены соответственно к пятому, шестому и седьмому, восьмому выходам блока выделения параметров 1, а первый, второй, третий входы блока достоверности 7 подключены соответственно к девятому, десятому и одиннадцатому выходам блока выделения параметров 1. Двенадцатый выход блока выделения параметров 1 подключен к девятнадцатому входу блока индикации 10. Входом блока потерь 6 является статистическая информация о соотношении числа пакетов, получивших отказ, к общему числу пришедших пакетов. Первый выход блока SYN/FIN 3, выходы блока интенсивности 4, блока нагрузки 5 и блока потерь 6 подключены соответственно к первому, второму, третьему и четвертому входам блока нормировки 8, первый, второй, третий и четвертый выходы которого подключены соответственно к первому, второму, третьему и четвертому входам блока управления 9. Выход блока достоверности 7 подключен к восемнадцатому входу блока индикации 10, а выходы блока управления с третьего по восемнадцатый включительно подключены соответственно к входам блока индикации 10 со второго по семнадцатый включительно. Выход блока сравнения IP адресов 2 подключен к первому входу блока индикации.

Блок выделения параметров предназначен, для определения наличия протокола TCP в информационном потоке, его анализа и подачи извлеченных характеристических параметров (IP адресов отправителя и получателя, значения поля TTL, установления флагов в заголовке пакета TCP, общего размера пакета) на вход остальных блоков. Его структурная схема представлена на фиг.2

Первый блок памяти 1.1 предназначен для хранения и последующего считывания с него на первый 1.2, восьмой 1.15 счетчики, второй 1.6, третий 1.8, четвертый 1.12, пятый 1.14 блоки памяти, второй 1.10, третий 1.16, четвертый 1.17, пятый 1.18 блоки дешифрации байтов данных пакетов, поступающих с демодулирующего устройства (канального контроллера) и подачи команды об окончании записи пришедших данных пакета на первый счетчик 1.2.

Первый счетчик 1.2 отсчитывает 14 байт в цифровой последовательности для определения пакета IP.

Первый блок дешифрации 1.3 предназначен для определения в последовательности поступающих данных протокола IP и подачи управляющего сигнала на блок достоверности.

Второй счетчик 1.4 предназначен для отсчета 4 бит для обнаружения поля длины заголовка пакета.

Третий счетчик 1.5 предназначен для отсчета 12 бит для нахождения общего размера IP пакета и подачи управляющего сигнала разрешения записи этого значения во второй блок памяти 1.6.

Второй блок памяти 1.6 предназначен для записи в него и хранения общего размера пакета IP и выдачи этого значения на блок интенсивности.

Четвертый счетчик 1.7 предназначен для отсчета 6 байт для нахождения значения поля TTL пакета и подачи управляющего сигнала о разрешении его записи в третий блок памяти 1.8.

Третий блок памяти 1.8 предназначен для записи в него и хранения значения поля TTL пакета IP и выдачи этого значения на блок достоверности 7.

Пятый счетчик 1.9 предназначен для отсчета 1 байта для нахождения значения поля, обозначающего протокол вышестоящего уровня, пакета и подачи управляющего сигнала о разрешении его записи во второй блок дешифрации 1.10.

Второй блок дешифрации 1.10 служит для определения числового значения «шесть» в десятичном виде, т.е. определения протокола TCP и подачи управляющего сигнала «1» на шестой счетчик 1.11, на блоки нагрузки и интенсивности.

Шестой счетчик 1.11 предназначен для отсчета 5 байт для нахождения двух последних байт адреса отправителя IP пакета и подачи управляющего сигнала разрешения записи этого значения в четвертый блок памяти 1.12.

Четвертый блок памяти 1.12 предназначен для записи в него и хранения значения двух последних байт адреса отправителя пакета IP и выдачи этого значения на блоки достоверности 7 и сравнения IP адресов 2.

Седьмой счетчик 1.13 предназначен для отсчета 4 байт для нахождения двух последних байт адреса получателя IP пакета и подачи управляющего сигнала разрешения записи этого значения в пятый блок памяти 1.14.

Пятый блок памяти 1.14 предназначен для записи в него и хранения значения двух последних байт адреса получателя пакета I и выдачи этого значения на блок сравнения IP адресов 2.

Восьмой счетчик 1.15 предназначен для нахождения байта флагов заголовка TCP и выдачи этого байта в третий 1.16, четвертый 1.17 и пятый 1.18 блоки дешифрации.

Третий блок дешифрации 1.16 предназначен для определения случая установки флага SYN в заголовке TCP и подачи управляющего сигнала на блок SYN/FIN 3.

Четвертый блок дешифрации 1.17 предназначен для определения случая установки флага FIN в заголовке TCP и подачи управляющего сигнала на блок SYN/FIN 3.

Пятый блок дешифрации 1.18 предназначен для определения случая аномальной совместной установки флагов SYN и FIN в заголовке TCP и подачи управляющего сигнала на блок управления 9.

Блок сравнения IP адресов 2 предназначен для выявления аномального выставления IP адресов в пакетах TCP и подачи сигнала об этом в блок индикации 10. Вариант схемы блока сравнения IP адресов 2 представлен на фиг.3.

Блок SYN/FIN 3 предназначен для расчета соотношения числа пакетов TCP с установленными флагами SYN и FIN и выдачи этого значения на блок нормировки. Вариант схемы блока SYN/FIN представлен на фиг.4.

Блок интенсивности 4 предназначен для расчета интенсивности информационного обмена пакетов TCP и выдачи этого значения на блок нормировки 8. Вариант схемы данного блока представлен на фиг.5.

Блок нагрузки 5 предназначен для расчета количества приходящих в единицу времени пакетов TCP и выдачи этого значения на блок нормировки 8. Вариант схемы данного блока представлен на фиг.6.

Блок потерь 6 предназначен для хранения поступающей на него статистической информации о соотношении числа пакетов, получивших отказ, к общему числу пришедших пакетов и выдачи этого значения на блок нормировки.

Блок достоверности 7 предназначен для выработки сигнала об обнаружении недостоверного IP адреса полученного пакета и подачи этого сигнала на блок индикации 10. Вариант схемы блока достоверности 7 представлен на фиг.7.

Блок нормировки 8 предназначен для нормирования входных величин для равноценного учета их в процессе принятия решения и выдачи полученных значений на блок управления 9. Вариант схемы блока нормировки представлен на фиг.8.

Блок управления 9 предназначен для принятия решения о состоянии сети в данный момент времени на основе анализа поступающих на него нормированных числовых значений характеристических параметров, определения состояния каждого из характеристических параметров, выдачи этих результатов на блок индикации 10 и подачи управляющих сигналов «стирание» и «запись» на первый блок памяти 1.1 для разрешения считывания следующего пакета информации. Вариант схемы блока управления представлен на фиг.9.

Блок индикации 10 предназначен для визуального отображения принятого решения о состоянии сети в конкретный момент времени, состоянии каждого из исследуемых характеристических параметров, отклонения параметра достоверности, аномальности выставления флагов SYN и FIN, IP адресов отправителя. Схемы индикаторов известны и описаны, например, в книге Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1989, стр.197, рис.7.1.

Первый 1.1, второй 1.6, третий 1.8, четвертый 1.12, пятый 1.14 блоки памяти могут быть реализованы на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В.Тарабрин, С.В.Якубовский, Н.А.Баранов и др. Под ред. Б.В.Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215).

Схемы первого 1.2, второго 1.4, третьего 1.5, четвертого 1.7, пятого 1.9, шестого 1.11, седьмого 1.13, восьмого 1.15 счетчиков известны и описаны, например, на фиг.6, 7, 8 патента РФ №2219577, МПК G06F 17/40 и могут быть реализованы на элементах И, счетчиках и дешифраторах. Схемы элементов И известны и описаны, например, в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.40, рис.1.23. В частности, такая схема может быть реализована на микросхеме К555ЛИ2. Счетчики могут быть реализованы на микросхемах серии К555, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.90, рис.1.66. Дешифратор может быть реализован на микросхемах дешифраторов, имеющих четыре разряда, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.133, рис.1.95. В частности, такая схема может быть реализована на микросхеме К555ИДЗ.

Схемы первого 1.3, второго 1.10, третьего 1.16, четвертого 1.17, пятого 1.18 блоков дешифрации известны (см., например, фиг.2 и фиг.3 патента РФ №2219577, МПК G06F 17/40) и могут быть реализованы на элементах И, дешифраторах и элементах И-НЕ. Схемы элементов И известны и описаны, например, в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.40, рис.1.23. В частности, такая схема может быть реализована на микросхеме К555ЛР12. В качестве дешифраторов могут быть использованы микросхемы серии 555, например К555ИД10 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.137, рис.1.98). В качестве элемента И-НЕ может быть использована, например, микросхема К155ЛАЗ (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.41, рис.1.24).

Блок сравнения IP адресов содержит компаратор 2.1. Схема компараторов для сравнения двух N-разрядных слов известна и описана в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. М.: Радио и связь, 1987, стр.183-184, 187, рис.1.135. Он может быть реализован на микросхемах К555СП1.

Блок SYN/FIN содержит делитель 3.1, который может быть реализован на микросхеме КР1802ВР2 (например, см. Н.Н.Аверьянов, А.И.Березенко, Ю.И.Борщенко и др. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник: в 2 т.; под ред. В.А.Шахнова. - М.: Радио и связь, 1988. - Т.2, стр.61-70).

Блок интенсивности содержит сумматор 4.2 со временем суммирования ДТ, делитель на AT 4.3, блок переключения 4.1. Сумматор 4.2 может быть построен на программируемых интервальных таймерах и накапливающих сумматорах типа аккумуляторов. Схемы программируемых интервальных таймеров известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника. Справочное пособие. - СПб.: БХВ-Петербург, 2004, стр 348-355, рис.6.29. В частности, такая схема может быть реализована на микросхеме ВИ54 серии К1821 и К1860. Сумматоры могут быть реализованы на микросхемах К555ИМЗ, например см. Угрюмов Е.П. Цифровая схемотехника. Справочное пособие. - СПб.: БХВ-Петербург, 2004,

стр.77-85, рис.2.24, 2.28. Схемы элементов ИЛИ известны, например описаны в книге Якубовский С.В. Цифровые и аналоговые интегральные микросхемы: Справочник. - М.: Радио и связь, 1990, стр.78, рис.167. В частности, такая схема может быть реализована на микросхеме К555ЛП2. Блок переключения 4.1 может быть реализован на мультиплексорах и демультиплексорах, схемы которых известны, например см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие.- СПб.: БХВ-Петербург, 2004, стр.54-56, рис.2.9(б). В частности, он строится на элементах И-НЕ.

Блок нагрузки содержит сумматор 5.2 со временем суммирования ΔТ, делитель на ДТ 5.3, блок переключения 5.1. Сумматор 5.2 может быть построен на программируемых интервальных таймерах и накапливающих сумматорах типа аккумуляторов. Схемы программируемых интервальных таймеров известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие - СПб.: БХВ-Петербург, 2004, стр 348-355, рис.6.29. В частности, такая схема может быть реализована на микросхеме ВИ54 серии К1821 и К1860. Сумматоры могут быть реализованы на микросхемах К555ИМЗ, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие. - СПб.: БХВ-Петербург, 2004,

стр.77-85, рис.2.24, 2.28. Схемы элементов ИЛИ известны, например описаны в книге Якубовский С.В. Цифровые и аналоговые интегральные микросхемы: Справочник. - М.: Радио и связь, 1990, стр.78, рис.167. В частности, такая схема может быть реализована на микросхеме К555ЛП2. Блок переключения 5.1 может быть реализован на мультиплексорах и демультиплексорах, схемы которых известны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие.- СПб.: БХВ-Петербург, 2004, стр.54-56, рис.2.9(б). В частности, он строится на элементах И-НЕ.

Блок достоверности содержит блок памяти 29.1, блок вычисления среднего значения 29.2, делитель на четыре 29.3, сумматор 29.4, вычитатель 29.5, компараторы 29.6 и 29.7, элемент ИЛИ 29.8. Схемы блоков памяти известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие. - СПб.: БХВ-Петербург, 2004, стр.175-190. В частности, такая схема может быть реализована на микросхемах КН531РУ9. Блок вычисления среднего значения 29.2 может быть построен на арифметико-логических устройствах, схемы которых известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие. - СПб.: БХВ-Петербург, 2004, стр.90-92. В частности, такая схема может быть реализована на микросхемах К555ИПЗ. Схема делителя может быть реализована на регистре сдвига. Схемы регистров сдвига известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие. - СПб.: БХВ-Петербург, 2004, стр.148-150, стр.143-146, в частности, могут быть реализованы на микросхеме ИР13 серии КР1533. Схемы сумматоров и вычитателей известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие. - СПб.: БХВ-Петербург, 2004,

стр.77-85, рис.2.24, 2.28. В частности, они строятся на микросхемах КМ155ИМЗ. Схемы компараторов известны и описаны, например, см. Угрюмов Е.П. Цифровая схемотехника: Справочное пособие. - СПб.: БХВ-Петербург, 2004, стр 64-66. В частности, они строятся на микросхемах КР1533СП1. Схемы элементов ИЛИ известны, например описаны в книге Якубовский С.В. Цифровые и аналоговые интегральные микросхемы: Справочник. - М.: Радио и связь, 1990, стр.78, рис.167. В частности, такая схема может быть реализована на микросхеме К555ЛП2.

Блок нормировки содержит умножители на десять 8.1 и 8.4, делитель на десять 8.2, делитель на тысячу 8.3. Данные элементы могут быть реализованы на микросхемах КР1802 ВР2 (например, см. Н.Н.Аверьянов, А.И.Березенко, Ю.И.Борщенко и др. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: в 2 т.; под ред. В.А.Шахнова. - М.: Радио и связь, 1988. - Т.2., стр.61-70).

Блок управления предназначен для выработки управляющих сигналов с целью реализации требуемого алгоритма принятия решения и может быть реализован на микропроцессоре TMS32010 (Ланне А.А. Цифровой процессор TMS32010 и его применение - Л.: ВАС, 1990. - 296 с). Обычно блок управления представляет собой последовательностные логические схемы и может быть синтезирован по известным правилам (Гутников B.C., Лопатин В.В. и др. Электронные устройства информационно-измерительной техники: Учебное пособие. - Л.: ЛПИ им. Калинина, 1980, стр.73-76, рис 42; Гутников B.C. Интегральная электроника в измерительных устройствах - Л.: Энергия, 1980. - 248 с).

Устройство работает следующим образом. Первый блок памяти 1.1 блока выделения параметров предназначен для хранения и последующего считывания с него байтов данных пакета. При получении с выхода блока управления 8 управляющих сигналов «стирание» и «запись» (логическая «1») производится заполнение ячеек ОЗУ первого блока памяти 1.1 байтами пакета, поступившими с демодулирующего устройства (канального контроллера). После того как записаны все байты очередного пакета анализируемого протокола, на втором выходе блока памяти 1.1 формируется разрешение на побайтное считывание информации (логическая «1»). С первого выхода первого блока памяти 1.1 байты пакетов последовательно поступают на первые входы первого 1.3, второго 1.10, третьего 1.16, четвертого 1.17 и пятого 1.18 блоков дешифрации, а также на первые входы второго 1.6, третьего 1.8, четвертого 1.12, пятого 1.14 блоков памяти, а также на первые входы первого 1.2 и восьмого счетчиков.

При поступлении на вход первого счетчика 1.2 сигнала с блока памяти 1.1 (логическая «1») считывается 14 байт для определения в сигнальной цифровой последовательности значения «шесть» (06) в десятичном виде, соответствующего наличию в пакете протокола IP.

В данном описании рассматривается формат кадра Ethernet 802.3/LLC. В случае других типов кадров, например Ethernet DIX (Ethernet II), длина этого поля составляет 2 байта и его значение равно в десятичном виде числу «восемь» (0800).

Если значение «шесть» найдено, на втором выходе первого блока дешифрации 1.3 формируется сигнал логической «1», поступающий на блоки достоверности 7 и нагрузки 5.

На первом выходе первого дешифратора 1.3 формируется управляющий сигнал, поступающий на второй счетчик 1.4, который отсчитывает 4 бита для обнаружения поля длины заголовка и вырабатывает управляющий сигнал, поступающий на третий счетчик 1.5, служащий для отсчета 12 бит для нахождения общего размера IP пакета в сигнально-цифровой последовательности и подачи управляющего сигнала разрешения записи этого значения во второй блок памяти 1.6.

Второй блок памяти 1.6 хранит значение общего размера пакета и по первому выходу передает его на блок интенсивности 4, при этом на втором выходе вырабатывает сигнал для запуска четвертого счетчика 1.7, который отсчитывает 6 байт для нахождения значения поля TTL пакета TCP и подает управляющий сигнал о разрешении его записи в третий блок памяти 1.8.

Третий блок памяти 1.8 хранит значение поля TTL пакета и по первому выходу передает его на блок достоверности 7, при этом на втором выходе вырабатывает сигнал для запуска пятого счетчика 1.9, который отсчитывает 1 байт для нахождения значения поля, обозначающего протокол вышестоящего уровня пакета, и подачи управляющего сигнала о разрешении его записи во второй блок дешифрации 1.10.

Второй блок дешифрации 1.10 предназначен для определения в этом байте числового значения «шесть» (06) в десятичном виде. В случае (06) используемым протоколом является TCP и на его выходе формируется сигнал на запуск шестого счетчика 1.11, а также на вход блоков нагрузки 5 и интенсивности 4.

Шестой счетчик 1.11 отсчитывает 5 байт для нахождения двух последних байт адреса отправителя IP пакета и подает управляющий сигнал разрешения записи этого значения в четвертый блок памяти 1.12.

Четвертый блок памяти 1.12 хранит значение двух последних байт адреса отправителя IP пакета и по первому выходу передает его на блок достоверности 7 и к блоку сравнения IP адресов 2, при этом на втором выходе вырабатывает сигнал для запуска седьмого счетчика 1.13, который отсчитывает 4 байта для нахождения двух последних байт адреса получателя IP пакета и подачи этого значения на блок сравнения IP адресов 2, а также управляющего сигнала разрешения записи этого значения в пятый блок памяти 1.14.

Пятый блок памяти 1.14 хранит значение двух последних байт адреса получателя IP пакета и по первому выходу передает его на блок сравнения IP, при этом на втором выходе вырабатывает сигнал для запуска восьмого счетчика 1.15, который отыскивает байт флагов заголовка TCP пакета и подает управляющий сигнал разрешения записи этого байта в третий 1.16, четвертый 1.17, пятый 1.18 блоки дешифрации.

Третий блок дешифрации 1.16 определяет случай установки флага SYN в заголовке TCP пакета и подает управляющий сигнал в виде логической «1» о его установке на блок SYN/FIN 3.

Четвертый блок дешифрации 1.17 определяет случай установки флага FIN в заголовке TCP пакета и подает управляющий сигнал в виде логической «1» о его установке на блок SYN/FIN 3.

Пятый блок дешифрации 1.18 определяет случай совместной установки флагов SYN и FIN в заголовке TCP пакета и подает управляющий сигнал в виде логической «1» об их установке на блок индикации 10.

При получении с первого выхода второго блока дешифрации 1.10 на первый вход блока нагрузки 5 сигнала о наличии протокола TCP в пакете IP происходит включение ключа 5.1 и значение «1», поступающее с первого выхода первого дешифратора 1.3 на второй вход блока нагрузки 5, проходит на сумматор 5.2. Блок ведет подсчет в течение времени ΔT. По истечении установленного времени ΔТ сумматор 5.2 выдает свое значение на делитель 5.3, который делит подсчитанное за ΔТ количество пакетов TCP на значение интервала ΔТ, тем самым получая среднее значение количества приходящих пакетов TCP за промежуток времени ΔТ. Далее это значение передается на блок нормировки 8.

При получении с первого выхода второго блока дешифрации 1.10 на первый вход блока интенсивности 4 сигнала о наличии протокола TCP в пакете IP происходит включение ключа 4.1 и значение размера пакета TCP, поступающее с первого выхода второго дешифратора 1.10 на второй вход блока интенсивности 4, проходит на сумматор 4.2. Блок ведет подсчет в течении времени ΔТ. По истечении установленного времени ΔТ сумматор 4.2 выдает свое значение на делитель 4.3, который делит подсчитанный за ΔТ объем трафика TCP на значение интервала ΔТ, тем самым получая среднее значение объема трафика TCP за промежуток времени ΔТ. Далее это значение передается на блок нормировки 8.

Сигналы об установлении флагов SYN и FIN от третьего 1.16 и четвертого 1.17 блоков дешифрации приходят на первые два входа блока SYN/FIN 3 и поступают на счетчики 3.1 и 3.2, которые ведут подсчет в течении времени ΔТ. По истечении этого времени они выдают подсчитанные значения на первый и второй входы делителя 3.3, который делит значение, поступающее от счетчика 3.1, на значение, поступающее от счетчика 3.2, и передает полученное значение на блок нормировки 8.

Сигнал наличия протокола IP в кадре Ethernet, пришедший с первого блока дешифрации 1.3 и поступивший на первый вход блока достоверности 7, формирует команду разрешения считывания (R) из блока памяти 7.1 по адресу соответствующему числу, пришедшему от пятого блока памяти 1.12 и поступившему на второй вход блока достоверности 7. Число, считанное из блока памяти 7.1, поступает на первый вход блока 7.2, на второй вход которого приходит значение, полученное с третьего входа блока достоверности 7, куда оно поступило с третьего блока памяти 1.8. Блок 7.2 вычисляет среднее между двумя числами, при этом если одно из чисел равно нулю, то результатом оставляет не нулевое число. Рассчитав среднее значение, блок 7.2 выдает на управляющие входы блока памяти 7.1 команду на разрешение записи (W), а на вход данных полученный результат, который записывается по тому же адресу, с которого производилось считывание. Одновременно рассчитанное в блоке 7.2 среднее значение передается на вход делителя 7.3, который на выходе выдает устанавливаемую часть пришедшего значения (например, четверть) на сумматоры 7.4 и 7.5. Пришедшие на входы сумматоров 7.4 и 7.5 значения с блока 7.2 и делителя 7.3 суммируются и вычитаются соответственно, а полученные значения с выходов сумматоров 7.4 и 7.5 поступают на вторые входы компараторов 7.6 и 7.7. Компараторы 7.6 и 7.7 сравнивают пришедшие на первые входы числа с сумматоров 7.4 и 7.5 с величиной числа, пришедшего на вторые входы от третьего входа блока достоверности. Компаратор 7.6 настроен на превышение величины от первого входа над вторым, а компаратор 7.7 настроен на меньшее значение с первого входа по сравнению со вторым. Выходы компараторов 7.6 и 7.7 идут на входы элемента ИЛИ 7.8, который выдает на выходе сигнал логической «1» при срабатывании хотя бы одного из компараторов, который говорит об аномальном значении поля TTL для заданного IP адреса.

Значения последних двух байт IP адресов отправителя и получателя с четвертого 1.12 и пятого 1.13 блоков памяти приходят на первые два входа блока сравнения IP 2 адресов и поступают на входы компаратора, который при их совпадении выдает значение логической «1» на первый вход блока индикации.

С выходов блоков SYN/FIN 3, интенсивности 4, нагрузки 5 и блока потерь 6 и блока значения поступают соответственно на входы первого умножителя 8.1, первого делителя 8.2, второго умножителя 8.3 и второго делителя 8.4. Данные элементы производят умножение или деления этих значений для выполнения их нормировки. С выходов этих элементов значения передаются на блок управления 9.

При поступлении сигналов на входы блока управления 9 начинает работу алгоритм принятия решения. Сначала работает алгоритм индикации характеристических параметров.

Если значение на четвертом входе меньше 10, то на третий выход блока управления выдается значение логической «1». Далее проверяется условие «значение на четвертом входе меньше 30», при выполнении этого условия значение логической «1» выдается на четвертый выход блока управления, а при невыполнении - на пятый.

Если значение на третьем входе меньше 20, то на шестой выход блока управления выдается значение логической «1». Далее проверяется условие «значение на третьем входе меньше 40», при выполнении этого условия значение логической «1» выдается на седьмой выход блока управления, а при невыполнении - на восьмой.

Если значение на втором входе меньше 30, то на девятый выход блока управления выдается значение логической «1». Далее проверяется условие «значение на втором входе меньше 50», при выполнении этого условия значение логической «1» выдается на десятый выход блока управления, а при невыполнении - на одиннадцатый.

Если значение на первом входе меньше 10, то на двенадцатый выход блока управления выдается значение логической «1». Далее проверяется условие «значение на первом входе меньше 30», при выполнении этого условия значение логической «1» выдается на тринадцатый выход блока управления, а при невыполнении - на четырнадцатый.

Далее проверяется одновременное выполнение условий.

После проверки выполнения данных условий по алгоритму блок управления по первому и второму выходу последовательно выдает логические «1» (сигналы «стирание» и «запись»), которые поступают на блок выделения параметров.

Устройство готово к ведению анализа вновь поступающей входной цифровой последовательности.

Таким образом, из рассмотренного принципа действия устройства видно, что оно обеспечивает возможность анализа протоколов, определения использования протокола TCP и его анализ, учет правил установления и ведения сеанса связи, выявление случаев аномального увеличения интенсивности информационного обмена, аномальное увеличение нагрузки входящего трафика, изменение соотношения числа пакетов на установление и разъединение соединения, аномальное увеличение числа пакетов, получивших отказ, определение достоверности используемого источником IP адреса и выявление случаев установки запрещенных комбинаций флагов, что необходимо для обеспечения устойчивого функционирования автоматизированных систем в условиях несанкционированного воздействия (информационных атак). Этим достигается сформулированная цель - повышение достоверности принятия решения, расширение области применения заявленного устройства, которое позволяет не только определять тип протокола, учитывать правила установления и ведения сеанса связи, но и производить анализ проходящих через него потоков для выявления аномалий сетевого трафика.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АНАЛИЗА ИНФОРМАЦИОННОГО ПОТОКА И ОПРЕДЕЛЕНИЯ СОСТОЯНИЯ ЗАЩИЩЕННОСТИ СЕТИ НА ОСНОВЕ АДАПТИВНОГО ПРОГНОЗИРОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2546236C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2009 |

|

RU2417537C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ АТАК В БЕСПРОВОДНЫХ СЕТЯХ СТАНДАРТА 802.11G | 2013 |

|

RU2545516C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ УДАЛЕННЫХ КОМПЬЮТЕРНЫХ АТАК | 2014 |

|

RU2540838C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2301443C2 |

| УСТРОЙСТВО МОНИТОРИНГА БЕЗОПАСНОСТИ АВТОМАТИЗИРОВАННЫХ СИСТЕМ | 2004 |

|

RU2270478C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ КОМПЬЮТЕРНЫХ АТАК В МАРШРУТАХ | 2014 |

|

RU2566331C1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ИСКАЖЕНИЯ ИНФОРМАЦИОННОГО ЦИФРОВОГО ПОТОКА | 2004 |

|

RU2273045C1 |

| Способ фильтрации части пакетов в сетевой сессии | 2022 |

|

RU2790635C1 |

| СПОСОБ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНЫХ СЕТЕЙ | 2018 |

|

RU2696330C1 |

Изобретение относится к области сетей передачи данных. Технический результат заключается в увеличении устойчивости функционирования системы в условиях несанкционированного воздействия. Сущность изобретения заключается в том, что устройство содержит блок выделения параметров (1), блок сравнения IP адресов (2), блок SYN/FIN (3), блок интенсивности (4), блок нагрузки (5), блок потерь (6), блок достоверности (7), блок нормировки (8), блок управления (9), блок индикации (10). Указанный технический результат достигается за счет введения дополнительных блоков интенсивности (4), блока нагрузки (5), блока потерь (6), блока достоверности (7), блока нормировки (8) и введения новых связей между блоками. 11 ил.

Устройство определения состояния сети связи, содержащее блок индикации, блок управления, блок сравнения IP адресов, блок SYN/FIN и блок выделения параметров, вход которого является информационным входом устройства, а третий и четвертый выходы подключены соответственно к первому и второму входам блока SYN/FIN, первый и второй выходы подключены соответственно к первому и второму входам блока сравнения IP адресов, первый и второй выходы блока управления подключены к первому и второму входам блока выделения параметров, отличающееся тем, что в него дополнительно введены блок интенсивности, блок нагрузки, блок потерь, блок достоверности, блок нормировки, первые и вторые входы блоков интенсивности, нагрузки подключены соответственно к пятому, шестому и седьмому, восьмому выходам блока выделения параметров, а первый, второй, третий входы блока достоверности подключены соответственно к девятому, десятому и одиннадцатому выходам блока выделения параметров, двенадцатый выход блока выделения параметров подключен к девятнадцатому входу блока индикации, входом блока потерь является статистическая информация о соотношении числа пакетов, получивших отказ к общему числу пришедших пакетов, первый выход блока SYN/FIN, выходы блока интенсивности, блока нагрузки и блока потерь подключены соответственно к первому, второму, третьему и четвертому входам блока нормировки, первый, второй, третий и четвертый выходы которого подключены соответственно к первому, второму, третьему и четвертому входам блока управления, выход блока достоверности подключен к восемнадцатому входу блока индикации, а выходы блока управления с третьего по восемнадцатый включительно подключены соответственно ко входам блока индикации со второго по семнадцатый включительно, выход блока сравнения IP адресов подключен к первому входу блока индикации.

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2301443C2 |

| US 6816973, 09.11.2004 | |||

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2002 |

|

RU2219577C1 |

| СПОСОБ ОБНАРУЖЕНИЯ УДАЛЕННЫХ АТАК В КОМПЬЮТЕРНОЙ СЕТИ | 2000 |

|

RU2179738C2 |

Авторы

Даты

2010-02-27—Публикация

2008-06-30—Подача