Изобретение относится к области электросвязи и предназначено для использования в технических средствах защиты с целью оперативного выявления компьютерных атак в доверенных маршрутах передачи пакетов сообщений.

Известно устройство защиты информационных ресурсов вычислительной сети по патенту РФ №2313127, опубл. 20.12.2007. Устройство-аналог состоит из серверов с блоками памяти, промежуточной памяти, коммутатора, коннекторов, линий обмена данными и блока управления.

Недостатком указанного способа является отсутствие возможности выявления компьютерных атак, направленных на ввод ложной информации в пакеты сообщений.

Известно устройство защиты информации от несанкционированного доступа для компьютеров информационно-вычислительных систем по патенту РФ №2321055, опубл. 27.03.2008. Устройство-аналог состоит из контроллера обмена информацией с внешним носителем информации, контроллера обмена информацией с компьютером, процессора идентификации и аутентификации пользователей, блока энергонезависимой памяти, модуля блокировки общей шины управления и обмена данными компьютера, устройства контроля питания, блока интерфейсов внешних устройств, модуля блокирования внешних устройств, аппаратного датчика случайных чисел, микроконтроллера датчиков вскрытия и извлечения компонентов компьютера с собственным независимым источником питания, оперативного запоминающего устройства, модуля постоянной аутентификации пользователя, модуля проверки целостности и состояния аппаратных компонентов устройства защиты, модуля управления загрузкой ключей аппаратного шифратора, модуля управления сетевыми адаптерами, модуля взаимодействия с системой разграничения доступа и модуля взаимодействия с серверами информационно-вычислительной системы.

Недостатком указанного способа является узкая область применения, обусловленная тем, что несмотря на возможность обнаружения несанкционированного доступа к компьютерам в нем не предусмотрена возможность предотвращения удаленных компьютерных атак.

Наиболее близким аналогом (прототипом) по своей технической сущности к заявленному устройству обнаружения удаленных компьютерных атак является устройство поиска информации по патенту РФ №2301443, опубл. 20.06.2007.

Устройство-прототип состоит из блока памяти, вход которого является входом устройства, а выход подключен к информационному входу первого блока дешифрации, второй вход которого подключен к первому счетчику, а выход - к входу второго счетчика, первый выход которого соединен с вторым входом второго блока дешифрации, первый вход которого подключен к выходу первого блока памяти, выход второго блока дешифрации соединен с входом второго блока памяти, а выход второго счетчика через третий счетчик соединен с первым входом третьего блока дешифрации, второй вход которого подключен к выходу первого блока памяти, первый и второй выходы третьего блока дешифрации подключены через четвертый и пятый счетчики соответственно к первым входам четвертого и пятого блоков дешифрации, вторые входы которых соединены с выходом первого блока памяти, а выходы четвертого и пятого блоков дешифрации подключены соответственно к первому и второму входам первого блока сравнения, входы блока управления подключены к второму выходу первого блока дешифрации, к третьему выходу третьего блока дешифрации, к второму выходу первого блока сравнения, к второму выходу шестого блока дешифрации, к первому выходу седьмого блока дешифрации, к выходу восьмого блока дешифрации, к выходу девятого блока дешифрации, к первому выходу десятого блока дешифрации, к двум выходам одиннадцатого блока дешифрации, а одиннадцатый выход блока управления подключен к входу первого счетчика и к первому блоку памяти, причем выход второго блока памяти соединен с первым входом шестого счетчика, второй вход которого подключен к выходу первого блока сравнения, а его выход - к входу шестого блока дешифрации, первый выход которого соединен с входом седьмого счетчика, выход которого подключен к входу седьмого блока дешифрации, второй выход которого соединен с входом восьмого счетчика, а выход восьмого счетчика подключен к первому входу восьмого, девятого и десятого блоков дешифрации, вторые входы каждого из которых соединены с выходом первого блока памяти, к которому также подключены вторые входы седьмого, шестого и одиннадцатого блоков дешифрации, причем второй выход десятого блока дешифрации соединен с входом девятого счетчика, выход которого подключен к первому входу одиннадцатого блока дешифрации.

Недостатком прототипа является относительно низкая достоверность обнаружения компьютерных атак из-за отсутствия возможности заблаговременно выявлять удаленные компьютерные атаки, направленные на ввод ложной информации в пакеты сообщений.

Целью изобретения является разработка устройства обнаружения в резервных доверенных маршрутах компьютерных атак, компьютерных атак, направленных на хищение, искажение и ввод ложной информации, а также перенаправление графика, обеспечивающего повышение достоверности обнаружения компьютерных атак за счет возможности заблаговременного их выявления.

Поставленная цель достигается тем, что в известном устройстве обнаружения компьютерных атак в маршрутах, содержащем первый блок памяти, снабженный входной шиной сообщений, а его информационный выход подключен к первым информационным входам первого, третьего, четвертого, пятого, шестого, седьмого, восьмого блоков дешифрации, первый управляющий вход первого блока памяти подключен к управляющему входу первого счетчика, информационный выход которого подключен к второму информационному входу первого блока дешифрации, управляющий и информационный выходы которого подключены соответственно к первому управляющему входу блока управления и информационному входу второго счетчика, первый информационный выход которого подключен к информационному входу второго блока дешифрации, информационный выход которого подключен к информационному входу второго блока памяти, информационный выход которого подключен к первому информационному входу шестого счетчика, второй информационный вход которого подключен к второму информационному выходу первого блока сравнения, информационный выход шестого счетчика подключен к второму информационному входу шестого блока дешифрации, первый управляющий выход которого подключен к четвертому управляющему входу блока управления, пятый управляющий вход которого подключен к первому управляющему выходу седьмого блока дешифрации, второй информационный выход которого подключен к информационному входу восьмого счетчика, выход которого подключен к второму информационному входу восьмого блока дешифрации, первый управляющий выход которого подключен к шестому управляющему входу блока управления, второй и третий управляющие входы блока управления подключены соответственно к первому управляющему выходу третьего блока дешифрации и первому управляющему выходу первого блока сравнения, второй информационный вход которого подключен к выходу пятого блока дешифрации, второй информационный вход которого подключен к выходу пятого счетчика, информационный вход которого подключен к второму информационному выходу третьего блока дешифрации, третий информационный выход которого подключен к входу четвертого счетчика, выход которого подключен к второму информационному входу четвертого блока дешифрации, выход которого подключен к третьему информационному входу первого блока сравнения, второй информационный выход второго счетчика подключен к информационному входу третьего счетчика, информационный выход которого подключен к второму информационному входу третьего блока дешифрации, второй информационный выход шестого блока дешифрации подключен к входу седьмого счетчика, выход которого подключен к второму информационному входу седьмого блока дешифрации, первый, второй и третий управляющие выходы блока управления подключены соответственно к первому, второму управляющим входам первого блока памяти и к управляющему входу блока индикации, отличающееся тем, что дополнительно введены второй блок сравнения, блок центрального управления передающим устройством, третий, пятый и четвертый блоки памяти. Выход четвертого блока памяти подключен к второму информационному входу второго блока сравнения, первый информационный вход и первый управляющий выход которого подключены соответственно к второму информационному выходу восьмого блока дешифрации и седьмому управляющему входу блока управления. Четвертый управляющий выход блока управления подключен к первому управляющему входу блока центрального управления передающим устройством, второй информационный вход которого подключен к информационному выходу пятого блока памяти. Второй информационный вход пятого блока памяти подключен к второму информационному выходу второго блока сравнения. Информационный выход третьего блока памяти подключен к первому информационному входу первого блока сравнения. Причем управляющие входы третьего блока памяти, четвертого блока памяти и пятого блока памяти объединены и являются управляющим входом устройства.

Благодаря новой совокупности существенных признаков в заявленном устройстве за счет постоянного мониторинга доверенных маршрутов передачи пакетов сообщений на наличие компьютерных атак, направленных на хищение, искажение и ввод ложной информации, а также перенаправление трафика, представляется возможным более оперативно прогнозировать факт воздействия компьютерных атак (КА), что указывает на возможность повышения достоверности обнаружения компьютерных атак.

Заявленное устройство поясняется чертежами, на которых показаны:

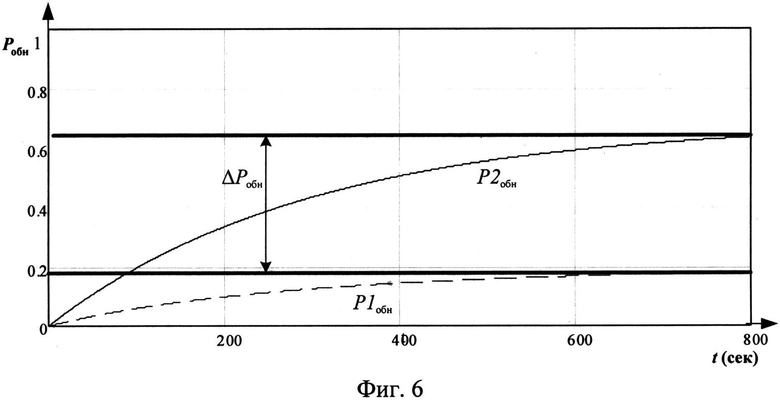

на фиг. 1 - структурная схема устройства обнаружения компьютерных атак в маршрутах;

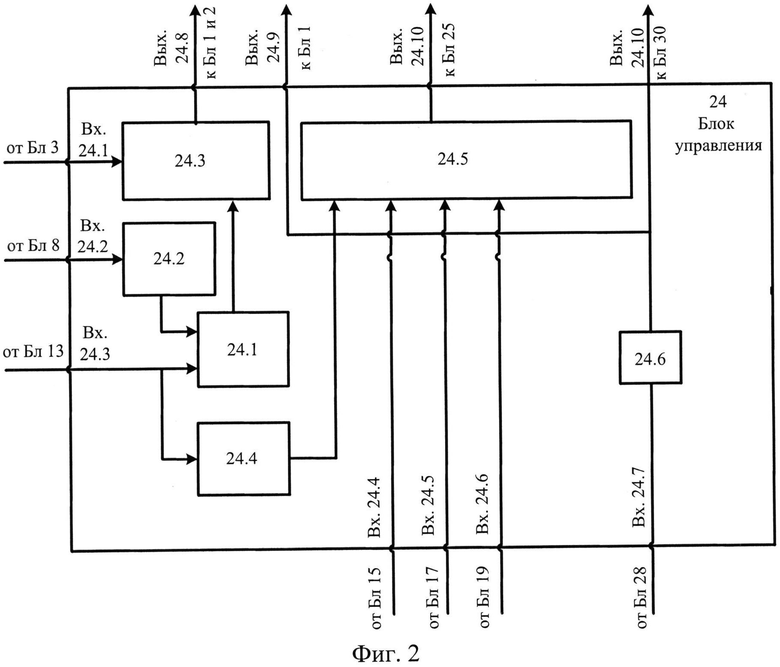

на фиг. 2 - структурная схема блока управления;

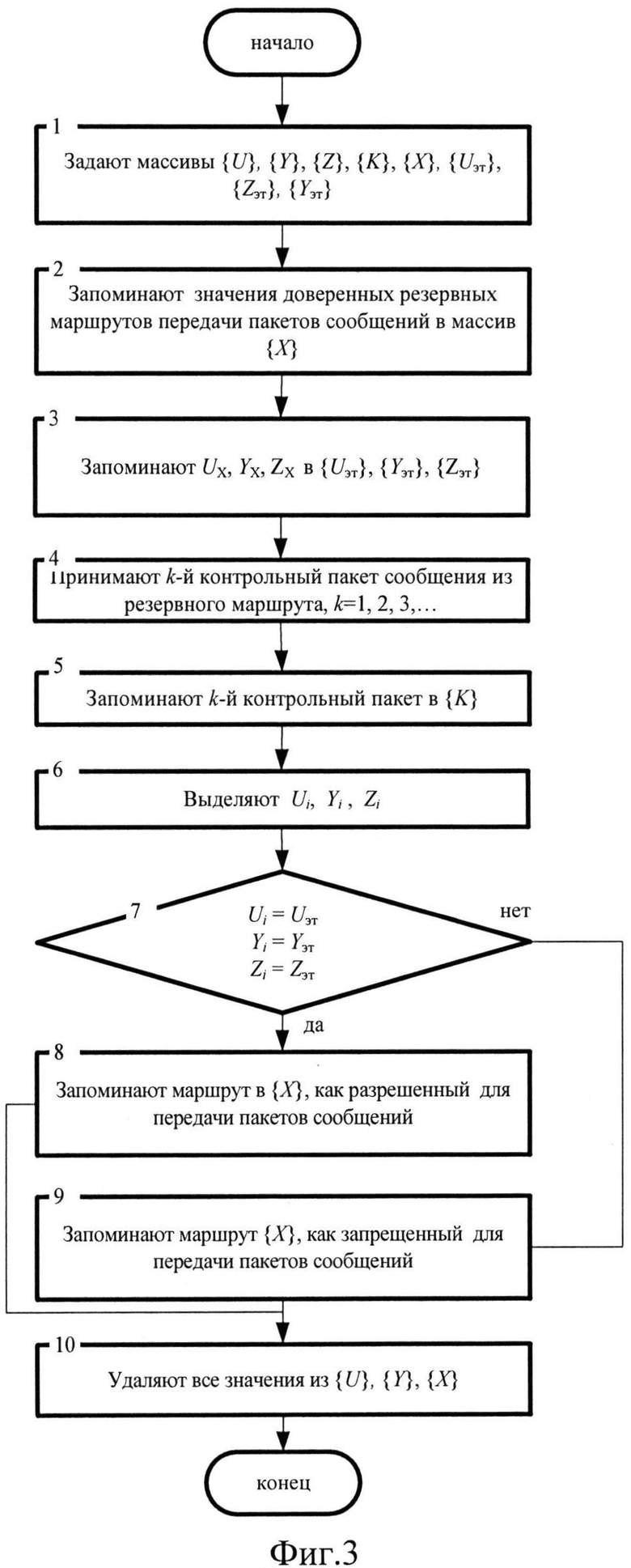

на фиг 3 - блок-схема алгоритма работы устройства;

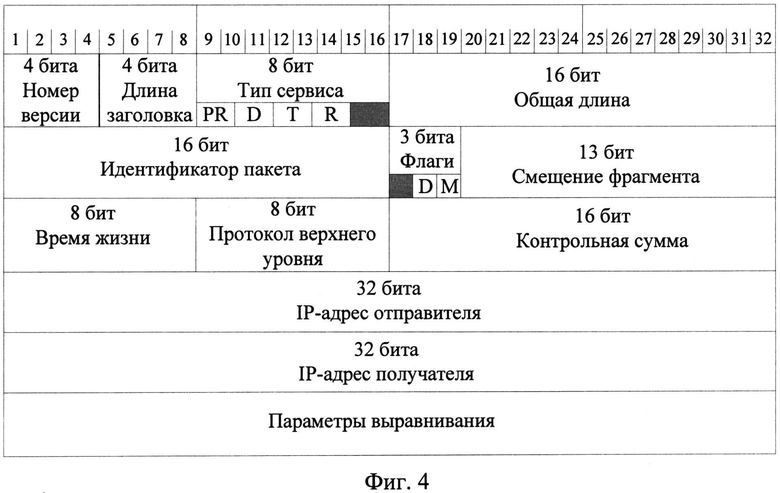

на фиг. 4 - структура заголовка IP-пакета;

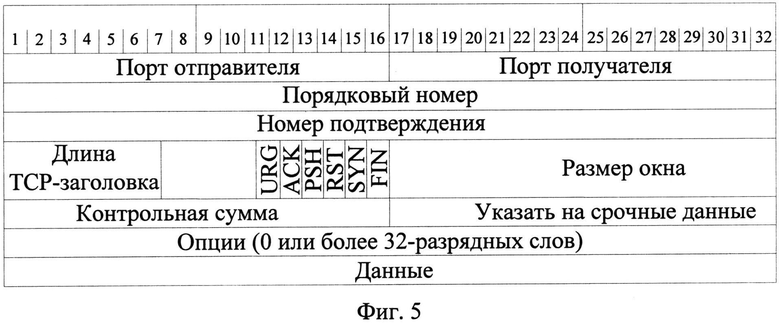

на фиг. 5 - структура заголовка TCP-пакета;

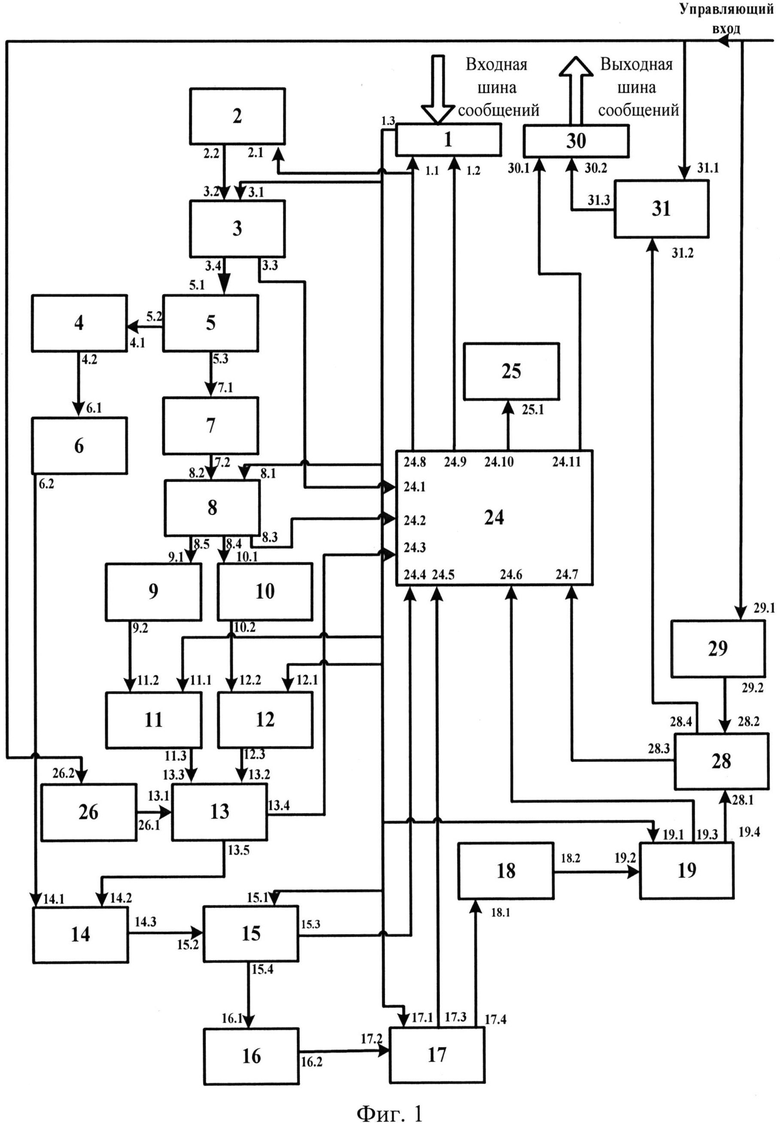

на фиг. 6 - зависимость вероятности передачи пакетов сообщений от объема передаваемых пакетов сообщений.

Заявленное устройство обнаружения компьютерных атак в маршрутах, показанное на фиг. 1, состоит из первого (1), второго (6), третьего (26), четвертого (29) и пятого (31) блоков памяти, первого (2), второго (5), третьего (7), четвертого (9), пятого (10), шестого (14), седьмого (16) и восьмого (18) счетчиков, первого (3), второго (4), третьего (8), четвертого (11), пятого (12), шестого (15), седьмого (17) и восьмого (19) блоков дешифрации, первого (13) и второго (28) блоков сравнения, центрального блока управления (30), блока управления (24) и блока индикации (25). Первый блок памяти 1 снабжен входной шиной сообщений, а его информационный выход 1.3 подключен к первым информационным входам первого 3, третьего 8, четвертого 11, пятого 12, шестого 15, седьмого 17, восьмого 19 блоков дешифрации. Первый управляющий вход 1.1 первого блока памяти 1 подключен к управляющему входу 2.1 первого счетчика 2, информационный выход 2.2 которого подключен к второму информационному входу 3.2 первого блока дешифрации 3, управляющий 3.3 и информационный 3.4 выходы которого подключены соответственно к первому управляющему входу 24.1 блока управления 24 и информационному входу 5.1 второго счетчика 5. Первый информационный выход 5.2 второго счетчика 5 подключен к информационному входу 4.1 второго блока дешифрации 4, информационный выход 4.2 которого подключен к информационному входу 6.1 второго блока памяти 6, информационный выход 6.2 которого подключен к первому информационному входу 14.1 шестого счетчика 14. Второй информационный вход 14.2 шестого счетчика 14 подключен к второму информационному выходу 13.5 первого блока сравнения 13, информационный выход 14.3 шестого счетчика 14 подключен к второму информационному входу 15.2 шестого блока дешифрации 15, первый управляющий выход 15.3 которого подключен к четвертому управляющему входу 24.4 блока управления 24, пятый управляющий вход 24.5 которого подключен к первому управляющему выходу 17.3 седьмого блока дешифрации 17. Второй информационный выход 17.4 блока дешифрации 17 подключен к информационному входу 18.1 восьмого счетчика 18, выход 18.2 которого подключен к второму информационному входу 19.2 восьмого блока дешифрации 19, первый управляющий выход 19.3 которого подключен к шестому 24.6 управляющему входу блока управления 24, второй 24.2 и третий 24.3 управляющие входы которого подключены соответственно к первому управляющему выходу 8.3 третьего блока дешифрации 8 и первому управляющему выходу 13.4 первого блока сравнения 13. Второй информационный вход 13.2 первого блока сравнения 13 подключен к выходу 12.3 пятого блока дешифрации 12, второй информационный вход 12.2 которого подключен к выходу 10.2 пятого счетчика 10, информационный вход 10.1 которого подключен к второму информационному выходу 8.4 третьего блока дешифрации 8, третий информационный выход 8.5 которого подключен к входу 9.1 четвертого счетчика 9, выход 9.2 которого подключен к второму информационному входу 11.2 четвертого блока дешифрации 11, выход 11.3 которого подключен к третьему информационному входу 13.3 первого блока сравнения 13. Второй информационный выход 5.3 второго счетчика 5 подключен к информационному входу 7.1 третьего счетчика 7, информационный выход 7.2 которого подключен к второму информационному входу 8.2 третьего блока дешифрации 8. Второй информационный выход 15.4 шестого блока дешифрации 15 подключен к входу 16.1 седьмого счетчика 16, выход 16.2 которого подключен к второму информационному входу 17.2 седьмого блока дешифрации 17. Первый 24.8, второй 24.9 и третий 24.10 управляющие выходы блока управления 24 подключены соответственно к первому 1.1 и второму 1.2 управляющим входам первого блока памяти 1 и к управляющему входу 25.1 блока индикации 25. Выход 29.2 четвертого блока памяти 29 подключен к второму информационному входу 28.2 второго блока сравнения 28, первый информационный вход 28.1 и первый управляющий выход 28.3 которого подключены соответственно к второму информационному выходу 19.4 восьмого блока дешифрации 19 и седьмому управляющему входу 24.7 блока управления 24. Четвертый управляющий выход 24.11 блока управления 24 подключен к первому управляющему входу 30.1 блока центрального управления передающим устройством 30, второй информационный вход 30.2 которого подключен к информационному выходу 31.3 пятого блока памяти 31. Второй информационный вход 31.2 пятого блока памяти 31 подключен к второму информационному выходу 28.4 второго блока сравнения 28. Информационный выход 26.1 третьего блока памяти 26 подключен к первому информационному входу 13.1 первого блока сравнения 13. Причем управляющие входы 26.2 третьего блока памяти 26, 29.1 четвертого блока памяти 29 и 31.1 пятого блока памяти 31 объединены и являются управляющим входом устройства.

Входящие в устройство обнаружения компьютерных атак в маршрутах (УОКАМ) блоки имеют следующее назначение:

Первый 1 и второй 6 блоки памяти предназначены соответственно для хранения и последующего считывания с них байтов (битов) пакетов сообщений, поступающих с демодулирующего устройства и блока дешифрации.

Третий 26, четвертый 29 и пятый 31 блоки памяти предназначены для записи и хранения соответствующих эталонных значений параметров IP-адресов (отправителей и получателей) и поля «Опции», а также доверенных маршрутов.

Схемы их известны и описаны в патенте РФ №2115952 (фиг. 2).

Первый счетчик 2 предназначен для отсчета 14 байтов в цифровой последовательности для определения IP-пакета (фиг. 3) и выработки управляющего сигнала для первого блока дешифрации 3.

Второй счетчик 5 предназначен для отсчета 4 бит для обнаружения поля «Длина заголовка» пакета сообщения.

Третий счетчик 7 предназначен для отсчета 8 байт с целью обнаружения 24-го байта пакета и выработки управляющего сигнала для третьего блока дешифрации 8.

Четвертый счетчик 9 предназначен для отсчета 3 байт до первого байта поля адреса отправителя в заголовке IP-дейтаграммы и выработки управляющего сигнала для четвертого блока дешифрации 11.

Пятый счетчик 10 предназначен для отсчета 4 байт до первого байта поля адреса получателя в заголовке IP-дейтаграммы и выработки управляющего сигнала для пятого блока дешифрации 12.

Шестой счетчик 14 предназначен для определения поля, содержащего номер порта отправителя пакета сообщения в заголовке TCP-пакета (фиг. 4).

Седьмой счетчик 16 предназначен для определения поля, содержащего значение резервных битов заголовка TCP-пакета.

Восьмой счетчик 18 предназначен для определения поля «Опции» заголовка TCP-пакета и выработки управляющих сигналов для восьмого 20 блока дешифрации.

Схема счетчиков известны и описаны в патенте РФ №2219577 (фиг. 6).

Первый блок дешифрации 3 предназначен для определения в последовательности поступающих данных протокола IP.

Второй блок дешифрации 4 предназначен для определения значения «Длина заголовка».

Третий блок дешифрации 8 предназначен для определения протокола TCP за счет выявления в 24-ом байте числового значения «шесть» в десятичном виде.

Четвертый 11 и пятый 12 блоки дешифрации предназначены для записи в них по четыре байта 27-30 и 31-34 полей адреса отправителя и адреса получателя соответственно.

Шестой блок дешифрации 15 предназначен для определения записи 35 и 36 байтов и определяет числовое значение «ноль» (00) в десятичном виде.

Седьмой блок дешифрации 17 предназначен для определения значения поля резервных бит.

Восьмой блок дешифрации 19 предназначен для определения значения «Опции».

Схема блоков дешифрации известны и описаны в патенте РФ №2219577 (фиг. 2).

Первый блок сравнения 13 предназначен для сравнения значений IP-адресов отправителя и получателя с соответствующими эталонными значениями и выработки управляющих сигналов на блок управления 24.

Второй блок сравнения 28 предназначен для сравнения значений поля «Опции» с соответствующими эталонными значениями и выработки управляющих сигналов на блок управления 24.

Схема компараторов известна и описана на рис. 1.134 стр. 185 в книге Шило В.Л. «Популярные цифровые микросхемы»: Справочник - М.: Радио и связь, 1987.

Блок центрального управления передающим устройством (30) предназначен для формирования, накопления и хранения контрольных пакетов сообщений передаваемых по доверенным маршрутам.

Центральный блок управления 30 может быть реализован, например, на микропроцессоре (К580ИК80), РICконтроллере (PIC16C5X) или микроЭВМ (СОР800).

Блок управления 24 предназначен для выработки управляющих сигналов при реализации требуемого алгоритма работы устройством обнаружения удаленных компьютерных атак. Схема блока управления 24 может быть реализована различным образом, в частности, как показано на фиг. 2.

Блок управления 24 содержит элементы ИЛИ 24.1 и 24.3, устройство задержки 24.2 и шифраторы 24.4-24.7. Схемы элементов ИЛИ известны и показаны на рис. 167 стр. 78 в книге Якубовский С. В. «Цифровые и аналоговые интегральные микросхемы»: Справочник. - М.: Радио и связь, 1990.

В качестве устройства задержки 24.2 может быть использована одна из известных микросхем, например, показанная на рис. 1.78 стр. 111 в книге Шило В.Л. «Популярные цифровые микросхемы»: Справочник - М: Радио и связь, 1987.

В качестве шифраторов 24.4-24.7 может быть использована одна из известных микросхем, например, показанная на рис. 1.101 стр. 141 в книге Шило В.Л. «Популярные цифровые микросхемы»: Справочник - М.: Радио и связь, 1987.

Блок индикации 25 предназначен для визуального отображения принятого решения. Схемы индикаторов известны и описаны на рис. 7.1 на стр. 197 в книге Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. «Микросхемы и их применение»: Справочное пособие. - М.: Радио и связь, 1989.

Разрядность шины «Входная шина сообщений» и «Выходная шина сообщений» определяется разрядностью анализируемых пакетов сообщений, в связи с тем, что устройство обрабатывает байты, шина является восьмиразрядной.

Заявленное УОКАМ работает следующим образом.

В исходном состоянии в оперативном запоминающем устройстве блока центрального управления передающим устройством сформирован необходимый для передачи контрольный пакет сообщения, а первый блок памяти в исходном состоянии готов к приему контрольных сообщений от других устройств обнаружения компьютерных атак в маршрутах. Каждые 6 минут соответствующие устройства, расположенные в информационно-телекоммуникационной сети, автоматически передают контрольные сообщения по всем доверенным маршрутам.

При получении с выхода блока управления 24 разрешения на запись (логическая «1») производится заполнение ячеек оперативного запоминающего устройства первого блока памяти 1 байтами контрольного пакета сообщений (КПС), поступившего с демодулирующего устройства (канального контроллера). После того как записаны все байты очередного КПС анализируемого протокола, на выходе блока управления 24 формируется разрешение на побайтное считывание информации (логический «0»).

С выхода первого блока памяти 1 байты КПС последовательно поступают на информационные входы первого 3, второго 4, третьего 8, четвертого 11, пятого 12, шестого 15, седьмого 17, восьмого 19 блоков дешифрации.

При поступлении на вход 2.1 первого счетчика 2 сигнала с блока управления 24 (логический «0») считывается 14 байт для определения в сигнальной цифровой последовательности значения «шесть» (06) в десятичном виде, соответствующего наличию в КПС протокола IP. Необходимо отметить, что в заявке рассматривается формат КПС Ethernet 802.3 // LLC. (Кульгин М. Технологии корпоративных сетей. Энциклопедия. - СПб.: Издательство «Питер», 1999. - 704 с.).

Если значение «шесть» не найдено, на первом выходе 3.3 первого блока дешифрации 3 формируется сигнал, поступающий на первый вход 24.1 блока управления 24.

На втором выходе 3.4 первого дешифратора 3 формируется управляющий сигнал, поступающий на второй счетчик 5, который отсчитывает 4 бита для обнаружения значения поля «Длина заголовка» и вырабатывает на первом выходе 5.2 управляющий сигнал разрешения записи этих бит во второй блок дешифрации 4, который служит для определения значения поля «Длина заголовка». На выходе второго блока дешифрации 4 формируется сигнал для записи значения поля «Длина заголовка» во второй блок памяти 6.

На втором выходе 5.3 второго счетчика 5 формируется управляющий сигнал, поступающий на третий счетчик 7, который отсчитывает 8 байт для обнаружения 24-го байта пакета и вырабатывает управляющий сигнал разрешения записи этого байта в третий блок дешифрации 8. Блок дешифрации 8 предназначен для определения в этом байте числового значения «шесть» (06) в десятичном виде. В этом случае используемым протоколом является TCP (Кульгин М. Технологии корпоративных сетей. Энциклопедия. - СПб.: Издательство «Питер», 1999. - 704 с.).

Если значение «шесть» не найдено, то на первом выходе 8.3 третьего блока дешифрации 8 формируется сигнал, поступающий на второй вход блока управления 24.

На третьем выходе 8.5 третьего блока дешифрации 8 формируется сигнал, поступающий на четвертый счетчик 9, который отсчитывает 3 байта до появления первого байта поля адреса отправителя в заголовке IP-дейтаграммы и вырабатывает на выходе 9.2 управляющий сигнал разрешения записи следующих четырех байтов сигнальных цифровых последовательностей (27-30) в четвертый блок дешифрации 11. На втором выходе 8.4 третьего блока дешифрации 8 формируется сигнал, поступающий на пятый счетчик 10, который отсчитывает 4 байта до первого поля адреса получателя в заголовке IP-дейтаграммы и вырабатывает на выходе 10.2 управляющий сигнал разрешения записи следующих четырех байтов сигнальных цифровых последовательностей (31-34) в пятый блок дешифрации 12.

В первом блоке сравнения 13 выделенные значения параметров адресов сравниваются с соответствующими эталонными значениями, хранящимися в третьем блоке памяти 26, и в случае их совпадения на втором выходе блока 13 вырабатывается управляющий сигнал в виде логической «1», поступающей на третий вход блока управления 24. Если адреса не совпали, вырабатывается управляющий сигнал - логический «0».

На втором выходе 13.5 первого блока сравнения 13 вырабатывается управляющий сигнал, поступающий на второй вход 14.2 шестого счетчика 14, который отыскивает поле, содержащее номер порта источника в заголовке TCP. На выходе 14.3 шестого счетчика 14 вырабатывается управляющий сигнал разрешения записи следующих двух байтов сигнальных цифровых последовательностей в шестой блок дешифрации 15. Шестой блок дешифрации 15 предназначен для определения в этом байте числового значения «ноль» (00) в десятичном виде. В этом случае на втором выходе блока 15 вырабатывается управляющий сигнал, поступающий на четвертый вход блока управления 24.

С первого выхода шестого блока дешифрации 15 поступает управляющий сигнал на седьмой счетчик 16, который отыскивает поле, содержащее значение резервных битов заголовка TCP-пакета. Седьмой счетчик 16 вырабатывает управляющие сигналы для записи в седьмой блок дешифрации 17 следующих 6 бит. Седьмой блок дешифрации 17 предназначен для определения значения поля резервных бит. Если это значение отлично от «нуля» (00) в десятичном виде, на первом выходе дешифратора 17 формируется управляющий сигнал, поступающий на пятый вход блока управления 24.

Со второго выхода 17.4 седьмого блока дешифрации 17 формируется управляющий сигнал, поступающий на восьмой счетчик 18, который отыскивает поле «Опции».

Восьмой счетчик 18, который отчитывает 4 байта для определения значения поля «Опции» и вырабатывает на первом выходе управляющий сигнал разрешения сохранения этих байт в восьмой блок дешифрации 19, который служит для определения параметров поля «Опции».

Поле «Опции» является необязательным и имеет переменную длину. Поддержка опций должна реализоваться во всех модулях IP (узлах и маршрутизаторах). Стандартом определены 8 опций. В предлагаемом устройстве используется опция - «запись маршрута» и/или «безопасности» [RFC 791, Internet Protocol, 1981, сентябрь, стр. 14-22].

Во втором блоке сравнения 28 выделенные параметры поля «Опции» сравниваются с эталонными значениями, хранящимися в четвертом блоке памяти 29, и в случае их совпадения на первом выходе блока сравнения 28 вырабатывается управляющий сигнал в виде логической «1», поступающей на седьмой вход блока управления 24. Если значения поля «Опции» не совпали, на первом выходе вырабатывается управляющий сигнал - логический «0», поступающий на двенадцатый вход блока управления 24.

После выделения всех параметров КПС информация о наличии или отсутствии воздействия на КПС в каждом доверенном маршруте сохраняется в пятом блоке памяти 31 и обновляется каждые 7 минут.

При поступлении управляющего сигнала на первый вход блока управления 24 формируется управляющий сигнал на его первом выходе.

При поступлении управляющего сигнала на второй вход блока управления 24 включается линия задержки до момента поступления сигнала на его третий вход, после чего формируется управляющий сигнал на первом выходе блока управления 24.

При поступлении управляющего сигнала на входы с третьего по шестой блока управления 24 подключается соответствующий шифратор. Шифратор необходим для преобразования сигналов, поступающих на его информационный вход в кодовую комбинацию, соответствующую сообщению, которое передается на второй выход блока управления 24.

При получении на седьмой вход блока управления 24 управляющего сигнала на его втором и четвертом выходе формируется управляющий сигнал, поступающий на первый блок памяти 1, по которому происходит обнуление ячеек памяти и блок центрального управления передающим устройством, по которому происходит запись информации о состоянии доверенного маршрута. Устройство готово к ведению анализа вновь поступающих КПС.

Через управляющий вход устройства администратор обновляет эталонные значения параметров КПС. Для этого администратор в тестовом режиме функционирования ИТКС измеряет реальные значения полей данных КПС для маршрута между каждой парой доверенных адресов получателя и отправителя. После передачи КПС по ИТКС от отправителя к получателю сообщения по определенному маршруту адреса отправителя и получателя (поля «IP адрес отправителя», «IP адрес получателя») и маршрут прохождения КПС (поле «опции») будут иметь одинаковые значение для всех КПС, проходящих по этому маршруту. Эти значения запоминают в соответствующие блоки памяти. После того как все эталонные значения проверяемых параметров собраны и записаны в соответствующие блоки памяти, осуществляется перевод ИТКС в режим реальной работы.

Таким образом, благодаря постоянному мониторингу резервных доверенных маршрутов передачи пакетов сообщений на наличие компьютерных атак, направленных на хищение, искажение и ввод ложной информации, а также перенаправление трафика повысилась достоверность их обнаружения, характеризуемая вероятностью обнаружения (Робн). С помощью моделирования получена взаимосвязь значений вероятности обнаружении компьютерных атак от времени диагностики маршрутов КПС.

Для этого была построена профильная модель устройства обнаружения компьютерных атак в маршрутах и метод топологического преобразования стохастических сетей [Привалов А.А. Метод топологического преобразования стохастических сетей и его использование для анализа систем связи ВМФ. - СПб: ВМА, 2000 г.].

Достижение технического результата поясняется следующим образом. Для устройства-прототипа из-за отсутствия возможности периодической диагностики резервных доверенных маршрутов на наличие в них воздействия компьютерных атак вероятность обнаружения компьютерных атак (Р1обн) ниже, чем у прототипа (Р2обн) в 3,5 раза.

При этом разница в вероятности обнаружения компьютерных атак тем больше, чем больше время диагностики резервных доверенных маршрутов, чем и достигается сформулированный технический результат, т.е. повышение достоверности обнаружения компьютерных атак.

Полученные результаты расчетов подтверждают возможность достижения указанного технического результата при использовании заявленного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБНАРУЖЕНИЯ УДАЛЕННЫХ КОМПЬЮТЕРНЫХ АТАК | 2014 |

|

RU2540838C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2301443C2 |

| УСТРОЙСТВО МОНИТОРИНГА БЕЗОПАСНОСТИ АВТОМАТИЗИРОВАННЫХ СИСТЕМ | 2004 |

|

RU2270478C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2009 |

|

RU2417537C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ СОСТОЯНИЯ СЕТИ СВЯЗИ | 2008 |

|

RU2383105C1 |

| СПОСОБ ОБНАРУЖЕНИЯ КОМПЬЮТЕРНЫХ АТАК В ИНФОРМАЦИОННО-ТЕЛЕКОММУНИКАЦИОННОЙ СЕТИ | 2013 |

|

RU2531878C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ АТАК В БЕСПРОВОДНЫХ СЕТЯХ СТАНДАРТА 802.11G | 2013 |

|

RU2545516C2 |

| СПОСОБ АНАЛИЗА ИНФОРМАЦИОННОГО ПОТОКА И ОПРЕДЕЛЕНИЯ СОСТОЯНИЯ ЗАЩИЩЕННОСТИ СЕТИ НА ОСНОВЕ АДАПТИВНОГО ПРОГНОЗИРОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2546236C2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

Изобретение относится к области электросвязи и предназначено для использования в технических средствах защиты с целью оперативного выявления компьютерных атак в доверенных маршрутах информационно-телекоммуникационной сети (ИТКС). Техническим результатом является повышение достоверности обнаружения компьютерных атак в маршрутах ИТКС. Устройство обнаружения компьютерных атак в маршрутах содержит счетчики (2, 5, 7, 9, 10, 14, 16, 18), блоки дешифрации (3, 4, 8, 11, 12, 15, 17, 19), блоки сравнения (13, 28), центральный блок управления (30), блок управления (24), блок индикации (25) и блоки памяти (1, 6, 26, 29, 31). Первый блок памяти (1) снабжен входной шиной сообщений, а его информационный выход подключен к первым информационным входам первого (3), третьего (8), четвертого (11), пятого (12), шестого (15), седьмого (17) и восьмого (19) блоков дешифрации, управляющие выходы которых подключены к соответствующим управляющим входам блока управления, управляющие выходы которого подключены к блоку индикации и первому блоку памяти. Управляющие выходы счетчиков подключены к управляющим входам соответствующих блоков дешифрации. Информационные выходы четвертого (11) и пятого (12) блоков дешифрации подключены к первому блоку сравнения (13), информационный выход которого подключен к третьему блоку памяти (26). Информационный вход пятого блока памяти (31) подключен к информационному выходу второго блока сравнения (28). Управляющий вход блока центрального управления передающим устройством (30) подключен к информационному выходу пятого блока памяти (31). Причем управляющие входы третьего блока памяти (26), четвертого блока памяти (29) и пятого блока памяти (31) объединены и являются управляющим входом устройства. 6 ил.

Устройство обнаружения компьютерных атак в маршрутах, содержащее первый блок памяти, снабженный входной шиной сообщений, а его информационный выход подключен к первым информационным входам первого, третьего, четвертого, пятого, шестого, седьмого, восьмого блоков дешифрации, первый управляющий вход первого блока памяти подключен к управляющему входу первого счетчика, информационный выход которого подключен к второму информационному входу первого блока дешифрации, управляющий и информационный выходы которого подключены соответственно к первому управляющему входу блока управления и информационному входу второго счетчика, первый информационный выход которого подключен к информационному входу второго блока дешифрации, информационный выход которого подключен к информационному входу второго блока памяти, информационный выход которого подключен к первому информационному входу шестого счетчика, второй информационный вход которого подключен к второму информационному выходу первого блока сравнения, информационный выход шестого счетчика подключен к второму информационному входу шестого блока дешифрации, первый управляющий выход которого подключен к четвертому управляющему входу блока управления, пятый управляющий вход которого подключен к первому управляющему выходу седьмого блока дешифрации, второй информационный выход которого подключен к информационному входу восьмого счетчика, выход которого подключен к второму информационному входу восьмого блока дешифрации, первый управляющий выход которого подключен к шестому управляющему входу блока управления, второй и третий управляющие входы блока управления подключены соответственно к первому управляющему выходу третьего блока дешифрации и первому управляющему выходу первого блока сравнения, второй информационный вход которого подключен к выходу пятого блока дешифрации, второй информационный вход которого подключен к выходу пятого счетчика, информационный вход которого подключен к второму информационному выходу третьего блока дешифрации, третий информационный выход которого подключен к входу четвертого счетчика, выход которого подключен к второму информационному входу четвертого блока дешифрации, выход которого подключен к третьему информационному входу первого блока сравнения, второй информационный выход второго счетчика подключен к информационному входу третьего счетчика, информационный выход которого подключен к второму информационному входу третьего блока дешифрации, второй информационный выход шестого блока дешифрации подключен к входу седьмого счетчика, выход которого подключен к второму информационному входу седьмого блока дешифрации, первый, второй и третий управляющие выходы блока управления подключены соответственно к первому, второму управляющим входам первого блока памяти и к управляющему входу блока индикации, отличающееся тем, что дополнительно введены второй блок сравнения, блок центрального управления передающим устройством, третий, пятый блоки памяти и четвертый блок памяти, выход которого подключен к второму информационному входу второго блока сравнения, первый информационный вход и первый управляющий выход которого подключены соответственно к второму информационному выходу восьмого блока дешифрации и седьмому управляющему входу блока управления, четвертый управляющий выход которого подключен к первому управляющему входу блока центрального управления передающим устройством, второй информационный вход которого подключен к информационному выходу пятого блока памяти, второй информационный вход которого подключен к второму информационному выходу второго блока сравнения, информационный выход третьего блока памяти подключен к первому информационному входу первого блока сравнения, причем управляющие входы третьего блока памяти, четвертого блока памяти и пятого блока памяти объединены и являются управляющим входом устройства.

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2301443C2 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИОННЫХ РЕСУРСОВ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 2005 |

|

RU2313127C2 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

| US 6816973 B1, 09.11.2004 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2015-10-20—Публикация

2014-07-01—Подача