Устройство относится к области кодирования информации и может быть использовано в вычислительной технике и в системах защиты информации от несанкционированного доступа.

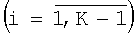

Известно устройство линейного дешифратора (см. патент РФ № 2032937, МПК G06F 11/00), содержащее К уровней узлов дешифрации (К - разрядность информационного входа дешифратора). В устройство введено К элементов НЕ, а каждый узел дешифрации выполнен в виде мажоритарного элемента. Каждый уровень дешифрации содержит 2i мажоритарных элементов  . Вход выборки дешифратора соединен с первыми входами первого и второго мажоритарных элементов первого уровня. Выход каждого мажоритарного элемента i-го уровня соединен с первыми входами пары мажоритарных элементов (i+1)-го уровня, выходы мажоритарных элементов k-го уровня являются выходами дешифратора, информационные входы которого соединены с входами элементов НЕ и соответственно с вторыми входами четных мажоритарных элементов уровней с первого по k-й. Вторые входы нечетных мажоритарных элементов которых соединены соответственно с выходами элементов НЕ. Третьи входы нечетных мажоритарных элементов всех уровней соединены с первым управляющим входом дешифратора, второй управляющий вход которого соединен с третьими входами четных мажоритарных элементов всех уровней.

. Вход выборки дешифратора соединен с первыми входами первого и второго мажоритарных элементов первого уровня. Выход каждого мажоритарного элемента i-го уровня соединен с первыми входами пары мажоритарных элементов (i+1)-го уровня, выходы мажоритарных элементов k-го уровня являются выходами дешифратора, информационные входы которого соединены с входами элементов НЕ и соответственно с вторыми входами четных мажоритарных элементов уровней с первого по k-й. Вторые входы нечетных мажоритарных элементов которых соединены соответственно с выходами элементов НЕ. Третьи входы нечетных мажоритарных элементов всех уровней соединены с первым управляющим входом дешифратора, второй управляющий вход которого соединен с третьими входами четных мажоритарных элементов всех уровней.

Однако это устройство функционально не решает задачу управляемой транспозиции данных.

Известен коммутатор на базе коммутационной матрицы, основанной на комбинационной схеме, аналогичной предлагаемой (http://www.unix.com.ua/lsok/glava_7.htm). Коммутационная матрица состоит из уровней двоичных переключателей, которые соединяют свой вход с одним из двух выходов в зависимости от значения бита тэга. Переключатели первого уровня управляются первым битом тэга, второго - вторым и т.д.

Недостатком использования такой матрицы в качестве дешифратора управляемой транспозиции является невозможность параллельной обработки всего входного блока данных. Если составной канал передачи данных невозможно построить из-за занятости выходного порта или промежуточного коммутационного элемента, то данные должны накапливаться в их источнике, в данном случае - во входном блоке порта, принявшего эти данные. Таким образом, скорость преобразования входных данных существенно уменьшается.

Наиболее близким к предлагаемому решению является дешифратор управляемой побитовой транспозиции информации, хранимой в персональной ЭВМ (см. патент РФ № 2320000, МПК G06F 7/76). Дешифратор содержит К уровней узлов дешифрации, каждый уровень дешифрации содержит 2i элементов  , регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов. Вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня. Элемент первого уровня реализует логическую функцию Y1=X,

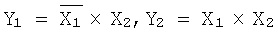

, регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов. Вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня. Элемент первого уровня реализует логическую функцию Y1=X,  остальные элементы реализуют логическую функцию

остальные элементы реализуют логическую функцию  . Вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов, входы X1 остальных элементов i-го уровня соединены с выходом i-го бита регистра управляющих кодов, входы X2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных, а входы разрешения записи этого регистра соединены с выходами последнего уровня дешифрации. Генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов.

. Вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов, входы X1 остальных элементов i-го уровня соединены с выходом i-го бита регистра управляющих кодов, входы X2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных, а входы разрешения записи этого регистра соединены с выходами последнего уровня дешифрации. Генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов.

Недостатком данного дешифратора является последовательное преобразование данных, которое происходит за N тактовых импульсов генератора, что при больших значениях N значительно снижает быстродействие.

Задачей настоящего решения является ускорение процесса форматирующего преобразования произвольной транспозиции информации за счет одновременной (параллельной) перестановки входного вектора данных (α1, α2, …, αN), при минимизации логических вентилей матрицы дешифратора.

Техническим результатом является возможность высокоскоростного параллельного преобразования форматов блоков данных методом транспозиции с использованием управляющих кодов.

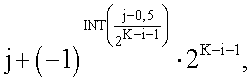

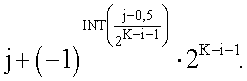

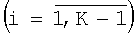

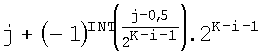

Поставленная задача достигается тем, что дешифратор управляемой транспозиции информации, хранимой в персональной ЭВМ, содержащий K уровней узлов дешифрации, регистр управляющих кодов, содержащий биты управляющих кодов, согласно решению содержит N=2K входов данных и выполнен с возможностью перестановки вектора входных данных длиной N параллельно. Для этого узлы дешифрации выполнены на одинаковых логических элементах, имеющих первый и второй входы данных X1, X2, первый и второй выходы данных Y1, Y2 и вход управляющего кода COD, причем каждый логический элемент электрически соединен входом COD с соответствующим битовым выходом регистра управляющих кодов, каждый логический элемент i-го уровня дешифрации  с номером j электрически соединен первым выходом данных Y1 с первым входом данных X1 элемента i+1 уровня дешифрации с номером j, а вторым выходом данных Y2 со вторым входом данных Х2 элемента i+1 уровня дешифрации с номером

с номером j электрически соединен первым выходом данных Y1 с первым входом данных X1 элемента i+1 уровня дешифрации с номером j, а вторым выходом данных Y2 со вторым входом данных Х2 элемента i+1 уровня дешифрации с номером  входы данных элементов первого уровня дешифрации являются входами данных дешифратора, выходы данных элементов К-го уровня дешифрации являются выходами данных дешифратора, где i - номер уровня дешифрации, j - номер уровня логического элемента, INT - функция выделения целой части числа.

входы данных элементов первого уровня дешифрации являются входами данных дешифратора, выходы данных элементов К-го уровня дешифрации являются выходами данных дешифратора, где i - номер уровня дешифрации, j - номер уровня логического элемента, INT - функция выделения целой части числа.

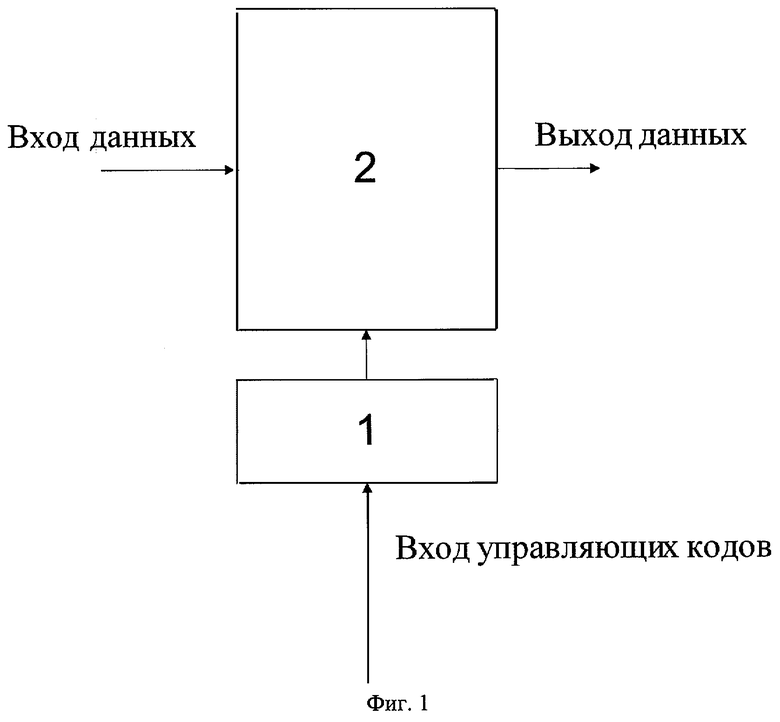

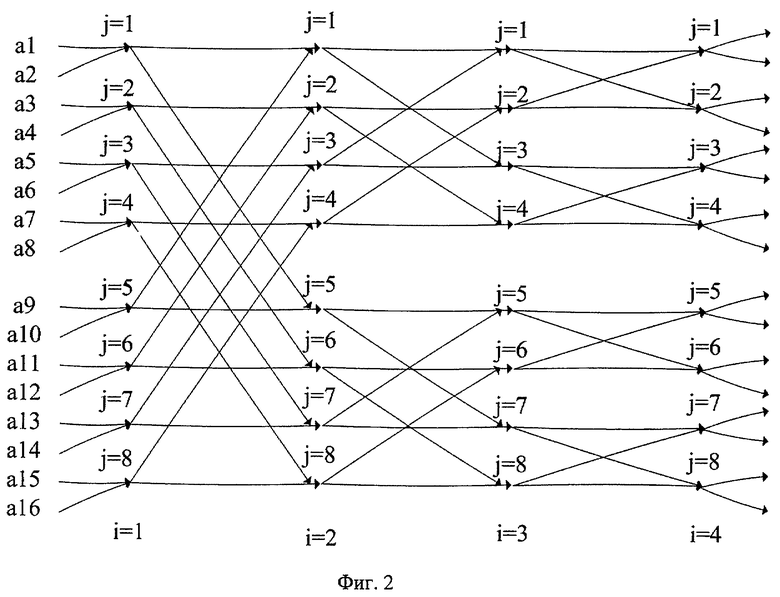

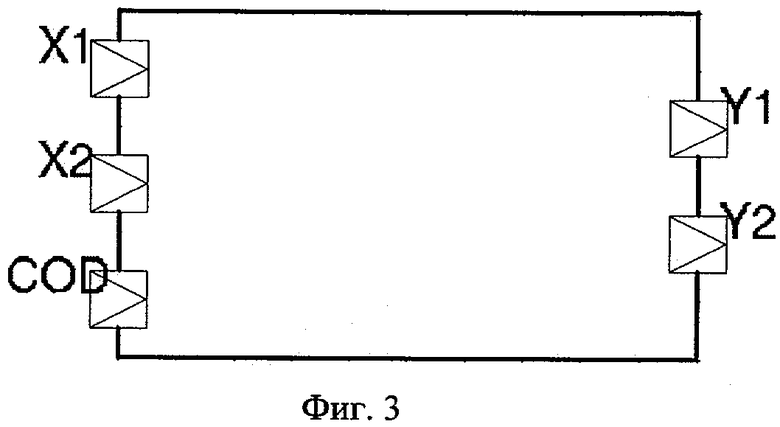

Изобретение поясняется чертежами, где на фиг.1 приведена блок-схема устройства, на фиг.2 - логический элемент узла дешифратора, на фиг.3 - граф, иллюстрирующий работу матрицы дешифратора, где

1) регистр управляющих кодов;

2) матрица дешифратора;

3) X1, Х2 - первый и второй входы данных узла дешифрации;

4) Y1, Y2 - первый и второй выходы данных узла дешифрации;

5) COD - вход управляющего кода.

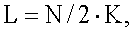

Предлагаемый параллельный дешифратор управляемой транспозиции информации состоит из регистра управляющих кодов 1 и матрицы дешифратора 2 (фиг.1), выполняющей функцию перестановки вектора данных (α1, α2, …, αN). Матрица дешифратора выполнена на одинаковых логических элементах, имеющих два входа данных X1, X2, два выхода данных Y1, Y2 и вход управляющего кода COD (см. фиг.2). Каждый логический элемент осуществляет транспозицию данных Y1=X2, Y2=X1 при высоком логическом уровне на входе COD или передает данные без изменения Y1=X1, Y2=X2 при низком логическом уровне на входе COD. Входы кодов матрицы дешифратора соединены с выходами регистра управляющих кодов. Число логических элементов матрицы дешифратора  где

где  - уровней дешифрации.

- уровней дешифрации.

Работа дешифратора поясняется графом, представленным на фиг.3, выполненным для N=16, К=4. Логические элементы фиг.2 располагаются в вершинах графа. На входы данных элементов первого уровня дешифрации подаются элементы входного вектора данных (α1, α2, …, αN). Каждый элемент i-го уровня дешифрации с номером j электрически соединен первым выходом данных с первым входом данных элемента i+1 уровня дешифрации с номером j, а вторым выходом данных со вторым входом данных элемента i+1 уровня дешифрации с номером  Выходы данных элементов К-го уровня дешифрации являются выходами данных дешифратора.

Выходы данных элементов К-го уровня дешифрации являются выходами данных дешифратора.

Устройство работает следующим образом. Перед началом преобразования в регистр управляющих кодов записывается N/2·log2N бит управляющих кодов, каждый их которых управляет соответствующим логическим элементом узла дешифратора. На входы дешифратора подаются элементы входного вектора данных. Через время задержки преобразования на выходах дешифратора появляется перестановка входного вектора данных. Время задержки выполнения перестановки Т определяется временем задержки на логическом элементе узла матрицы дешифратора τ и числом уровней дешифрации K:T=K·τ.

Таким образом, перестановка входного вектора данных длиной N в соответствии с управляющими кодами в регистре управляющих кодов выполняется параллельно, что обеспечивает высокую скорость преобразования. Число логических элементов дешифратора N/2·log2N растет практически линейно с ростом N, что делает технически возможным перестановку больших блоков данных. Число возможных перестановок, осуществляемых данным дешифратором, 2N/2·log 2 N < N!, т.к. данный дешифратор не реализует полное множество возможных перестановок вектора входных данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КРОСС-КЛАСТЕРНОЙ УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2009 |

|

RU2409842C1 |

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2008 |

|

RU2390052C2 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ЭВМ | 2009 |

|

RU2405187C1 |

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПОБИТОВОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2007 |

|

RU2320000C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК И СОЧЕТАНИЙ | 2010 |

|

RU2427885C1 |

| УСТРОЙСТВО ПЕРЕСТАНОВОК И СДВИГОВ БИТОВ ДАННЫХ В МИКРОПРОЦЕССОРАХ | 2011 |

|

RU2488161C1 |

| КРОСС-КЛАСТЕРНАЯ КОММУТАЦИОННАЯ МАТРИЦА | 2009 |

|

RU2417402C1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК | 2009 |

|

RU2395834C1 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ БИТОВ БИНАРНОЙ СТРОКИ | 2009 |

|

RU2439662C2 |

| СПОСОБ ЗАЩИТЫ ИНФОРМАЦИИ В РАДИОСЕТИ С ПАКЕТНОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2009 |

|

RU2425455C1 |

Изобретение относится к области кодирования информации и может быть использовано в вычислительной технике и в системах защиты информации от несанкционированного доступа. Техническим результатом является возможность высокоскоростного параллельного преобразования форматов блоков данных методом транспозиции с использованием управляющих кодов. Дешифратор управляемой транспозиции информации, хранимой в персональной ЭВМ, содержит К уровней узлов дешифрации, регистр управляющих кодов, содержащий биты управляющих кодов. Узлы дешифрации выполнены на одинаковых логических элементах, имеющих первый и второй входы данных Х1, Х2, первый и второй выходы данных Y1, Y2 и вход управляющего кода COD. 3 ил.

Дешифратор управляемой транспозиции информации, хранимой в персональной ЭВМ, содержащий узлы дешифрации, которые образуют К уровней, регистр управляющих кодов, содержащий биты управляющих кодов, отличающийся тем, что он содержит N=2K входов данных и выполнен с возможностью перестановки вектора входных данных длиной N параллельно, при этом узлы дешифрации выполнены на одинаковых логических элементах, имеющих первый и второй входы данных Х1, Х2, первый и второй выходы данных Y1, Y2 и вход управляющего кода COD и осуществляющих транспозицию данных на входах данных Y1=X2, Y2=X1 при высоком логическом уровне на входе COD или передающих данные на входах данных без изменения Y1=X1, Y2=X2 при низком логическом уровне на входе COD, причем каждый логический элемент электрически соединен входом COD с соответствующим битовым выходом регистра управляющих кодов, каждый логический элемент i-го уровня дешифрации  с номером j электрически соединен первым выходом данных Y1 с первым входом данных X1 элемента i+1 уровня дешифрации с номером j, а вторым выходом данных Y2 со вторым входом данных Х2 элемента i+1 уровня дешифрации с номером

с номером j электрически соединен первым выходом данных Y1 с первым входом данных X1 элемента i+1 уровня дешифрации с номером j, а вторым выходом данных Y2 со вторым входом данных Х2 элемента i+1 уровня дешифрации с номером  , входы данных элементов первого уровня дешифрации являются входами данных дешифратора, выходы данных элементов К-го уровня дешифрации являются выходами данных дешифратора, где i - номер уровня дешифрации, j - номер уровня логического элемента, INT - функция выделения целой части числа.

, входы данных элементов первого уровня дешифрации являются входами данных дешифратора, выходы данных элементов К-го уровня дешифрации являются выходами данных дешифратора, где i - номер уровня дешифрации, j - номер уровня логического элемента, INT - функция выделения целой части числа.

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПОБИТОВОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2007 |

|

RU2320000C1 |

| US 20070277085 А1, 29.11.2007 | |||

| US 6105114, 15.08.2000 | |||

| US 20030145272 A1, 31.07.2003. | |||

Авторы

Даты

2010-05-20—Публикация

2008-10-07—Подача