Изобретение относится к области кодирования информации и может быть использовано в системах защиты информации от несанкционированного доступа.

Известны устройства, обеспечивающие генерацию перестановок (транспозиций) исходных величин (см., например, авт. св. СССР №957215, МПК G06F 7/08, №995093, МПК G06F 7/06, №1124319, G06F 7/06, №1397933, МПК G06F 15/20).

Недостатком этих устройств является невозможность управления перестановками.

Известно устройство, обеспечивающее генерацию управляемых перестановок (см. авторское свидетельство СССР №1513467, МПК G05F 15/20). Данное устройство реализует процедуру преобразования номера перестановки в однозначно соответствующую ему перестановку.

Недостатком устройства является его техническая сложность при больших длинах исходных данных N, т.к. число логических вентилей, принимаемых за минимальную единицу аппаратных структур устройства, растет пропорционально N2. Перестановка выполняется за несколько раундов преобразований, что снижает скорость ее выполнения. Кроме этого устройство предназначено для загрузки исходных данных в параллельном коде, что приводит к дополнительным затратам при его соединении с последовательной шиной передачи данных.

Наиболее близким к заявляемому является дешифратор управляемой побитовой транспозиции информации, хранимой в персональной ЭВМ (см. патент РФ №2320000, МПК G06F 7/76). Дешифратор содержит К уровней узлов дешифрации, каждый уровень дешифрации содержит 2i элементов  . Вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня. Выход каждого элемента i-го уровня соединен с первыми входами пары элементов (i+1)-го уровня. Дешифратор также содержит регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов, причем элемент первого уровня реализует логическую функцию

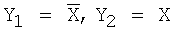

. Вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня. Выход каждого элемента i-го уровня соединен с первыми входами пары элементов (i+1)-го уровня. Дешифратор также содержит регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов, причем элемент первого уровня реализует логическую функцию  , остальные элементы реализуют логическую функцию

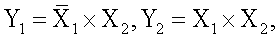

, остальные элементы реализуют логическую функцию  где X, X1, X2 - входы логических элементов, Y1, Y2 - выходы логических элементов. Вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов. Входы X1 остальных элементов i-го уровня соединены с выходом i-го бита регистра управляющих кодов. Входы X2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных. Генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов

где X, X1, X2 - входы логических элементов, Y1, Y2 - выходы логических элементов. Вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов. Входы X1 остальных элементов i-го уровня соединены с выходом i-го бита регистра управляющих кодов. Входы X2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных. Генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов

При большой длине N преобразуемого блока данных число уровней дешифрации K=log2(N) велико, а суммарная задержка установки управляющих кодов τΣ=τ·K, где τ - задержка на одном уровне дешифрации. Это снижает скорость преобразования в K раз, что является недостатком дешифратора.

Задачей настоящего решения является ускорение процесса управляемой перестановки элементов (a 1, a, …, a i, …a N) исходной строки данных длиной N за счет конвейерной обработки, при выполнении преобразования за N тактов генератора тактовых импульсов.

Техническим результатом является возможность высокоскоростной перестановки данных с использованием управляющих кодов.

Поставленная задача решается в заявленном изобретении за счет реализации следующей совокупности признаков, характеризующих его сущность.

Дешифратор содержит K уровней узлов дешифрации, каждый уровень дешифрации содержит 2i-1 элементов  , двойной буферный регистр накопления и хранения форматированных данных.

, двойной буферный регистр накопления и хранения форматированных данных.

Согласно решению узлы дешифрации i-го уровня состоят из элементов, объединяющих D триггер хранения данных и регистр хранения и циклического сдвига бит кодов дешифрации длиной K=i+1. Первый бит Q которого управляет первым r1 и вторым r2 выходами разрешения записи данных rd1=Q,  . Причем выход данных каждого элемента i-го уровня электрически соединен с входами данных двух элементов (i+1)-го уровня. Первый и второй выходы разрешения записи данных каждого элемента i-го уровня электрически соединены с входами разрешения записи данных элементов (i+1)-го уровня. Входы тактовых импульсов электрически соединены между собой, входы разрешения записи управляющих кодов, поступающих на вход управляющих кодов, для всех элементов электрически соединены между собой. Выход данных каждого элемента K-го уровня электрически соединен с двумя входами данных двойного буферного регистра накопления и хранения форматированных данных. Первый и второй выходы разрешения записи данных каждого элемента K-го уровня электрически соединены с двумя входами разрешения записи данных двойного буферного регистра накопления и хранения форматированных данных.

. Причем выход данных каждого элемента i-го уровня электрически соединен с входами данных двух элементов (i+1)-го уровня. Первый и второй выходы разрешения записи данных каждого элемента i-го уровня электрически соединены с входами разрешения записи данных элементов (i+1)-го уровня. Входы тактовых импульсов электрически соединены между собой, входы разрешения записи управляющих кодов, поступающих на вход управляющих кодов, для всех элементов электрически соединены между собой. Выход данных каждого элемента K-го уровня электрически соединен с двумя входами данных двойного буферного регистра накопления и хранения форматированных данных. Первый и второй выходы разрешения записи данных каждого элемента K-го уровня электрически соединены с двумя входами разрешения записи данных двойного буферного регистра накопления и хранения форматированных данных.

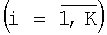

Изобретение поясняется чертежами, где на фиг.1 приведена блок-схема дешифратора для K уровней, на фиг.2 - схема дешифратора для двух уровней, позволяющая выполнять перестановку вектора данных из четырех элементов, где:

0 - двойной буферный регистр накопления и хранения форматированных данных;

1 - логический элемент узла первого уровня дешифратора;

2 - логические элементы узлов второго уровня дешифратора;

3 - логические элементы узлов третьего уровня дешифратора;

4, …K-1 - блок логических элементов узлов от четвертого до K-1 уровня дешифратора;

K - логические элементы узлов К-го уровня дешифратора;

D - вход данных;

RD - вход разрешения записи данных;

CS - вход разрешения записи управляющих кодов;

СР - вход управляющих кодов;

rd1 - первый выход разрешения записи данных;

rd2 - второй выход разрешения записи данных;

D_OUT - выход данных;

clk - вход тактовых импульсов от внешнего генератора;

BZY - выход сигнала переполнения двойного буферного регистра.

Предлагаемый дешифратор состоит из К уровней узлов дешифрации 1-K, выполняющих функцию перестановки вектора данных (a

1, a, …, a

i, … a

N), загружаемого в дешифратор последовательно. Логические элементы узлов дешифратора 1-K имеют одинаковую структуру. Вход данных D узла дешифрации первого уровня является входом данных дешифратора. Узлы дешифрации i-го уровня состоят из элементов, хранения текущих компонент вектора данных (a

1, a, …, a

i, …a

N) и циклического сдвигового регистра длиной K-i+1 бит для хранения кодов дешифрации. Первый бит Q циклического сдвигового регистра управляет первым r1 и вторым r2 выходами разрешения записи данных  ,

,  . Каждый выход данных элемента i-го уровня электрически соединен шиной данных с входами двух элементов i+1 уровня, первый и второй выходы разрешения записи данных каждого элемента i-го уровня электрически соединены с входами разрешения записи данных элементов (i+1)-го уровня. При этом логические элементы узлов дешифратора образуют двоичное дерево (фиг.1). Входы тактовых импульсов и разрешения записи управляющих кодов всех элементов электрически соединены между собой. Выход данных каждого элемента K-го уровня электрически соединен с двумя входами данных двойного буферного регистра накопления и хранения форматированных данных, первый и второй выходы разрешения записи данных каждого элемента К-го уровня электрически соединены с соответствующими входами разрешения записи данных двойного буферного регистра накопления и хранения форматированных данных.

. Каждый выход данных элемента i-го уровня электрически соединен шиной данных с входами двух элементов i+1 уровня, первый и второй выходы разрешения записи данных каждого элемента i-го уровня электрически соединены с входами разрешения записи данных элементов (i+1)-го уровня. При этом логические элементы узлов дешифратора образуют двоичное дерево (фиг.1). Входы тактовых импульсов и разрешения записи управляющих кодов всех элементов электрически соединены между собой. Выход данных каждого элемента K-го уровня электрически соединен с двумя входами данных двойного буферного регистра накопления и хранения форматированных данных, первый и второй выходы разрешения записи данных каждого элемента К-го уровня электрически соединены с соответствующими входами разрешения записи данных двойного буферного регистра накопления и хранения форматированных данных.

Управление перестановкой осуществляется кодами N×K бит, загружаемыми в циклические сдвиговые регистры логических элементов узлов дешифратора. Причем в логический элемент первого уровня 1 загружается N бит управляющих кодов, в логические элементы второго уровня 2 загружается  бит управляющих кодов, в логические элементы K-го уровня загружается

бит управляющих кодов, в логические элементы K-го уровня загружается  бит управляющих кодов.

бит управляющих кодов.

Устройство работает следующим образом. Перед началом преобразования в циклические сдвиговые регистры хранения кодов дешифрации заносятся управляющие коды дешифрации. Для этого управляющая ЭВМ устанавливает вход RD в состояние с логическим уровнем 0, подает на входы СР N×K бит управляющих кодов и записывает их в регистры по очередному импульсу clk, устанавливая для этого на входе CS состояние с логическим уровнем 1. Для перестановки очередного вектора данных (a

1, a, …, a

i, …a

N) вход CS устанавливается в состояние 0. На вход данных D элемента первого уровня дешифрации подается элемент a

1 вектора данных. Вход RD устанавливается в состояние 1 и по очередному импульсу clk a

1 записывается в элемент первого уровня дешифрации. По заднему фронту импульса clk в состоянии RD=1, CS=0 логическая схема этого элемента формирует сигналы на выходах разрешения записи данных rd1=Q,  , где Q - первый бит регистра кодов элемента первого уровня, после чего осуществляется циклический сдвиг битов управляющего кода регистра первого уровня и бит Q заменяется на следующий.

, где Q - первый бит регистра кодов элемента первого уровня, после чего осуществляется циклический сдвиг битов управляющего кода регистра первого уровня и бит Q заменяется на следующий.

По фронту следующего импульса clk данные из логического элемента первого уровня a 1 переписываются в первый элемент второго уровня при rd1=1, rd2=0 или во второй элемент второго уровня при rd1=0, rd2=1, после чего в элемент первого уровня записывается значение α2 вектора данных. Работа всех логических элементов узлов дешифратора осуществляется по одинаковому алгоритму. После загрузки (a 1, a, …, a i, … a N) в дешифратор без остановки загружается следующий вектор данных (a 1, a, …, a i, …a N). В результате, через N тактовых импульсов clk элементы (a 1, a, …, a i, …a N) записываются в двойной буферный регистр накопления и хранения форматированных данных в порядке, определяемом кодами дешифрации. При сигнале двойного буферного регистра RD=0 перестановка вектора (а 1, а, …,a i, …a N) в параллельном коде записывается во второй регистр, и сигнал RD двойного буферного регистра накопления и хранения форматированных данных устанавливается в 1. Если сигнал двойного буферного регистра RD=1, формируется выходной сигнал BZY=1, и процесс преобразования приостанавливается путем прекращения подачи тактовых импульсов clk до момента освобождения второго регистра.

Таким образом, за счет конвейерной обработки данных в узлах дешифрации удается сократить время выполнения перестановки примерно в K раз, так как общее время задержки определяется временем задержки на одном узле дешифратора. Кроме этого число логических элементов узлов дешифрации составляет N-1 и растет линейно с ростом N, что позволяет осуществлять перестановки больших блоков данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КРОСС-КЛАСТЕРНОЙ УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2009 |

|

RU2409842C1 |

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПОБИТОВОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2007 |

|

RU2320000C1 |

| ПАРАЛЛЕЛЬНЫЙ ДЕШИФРАТОР УПРАВЛЯЕМОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2008 |

|

RU2390049C1 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ЭВМ | 2009 |

|

RU2405187C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ОБРАТНЫХ ПЕРЕСТАНОВОК ИНФОРМАЦИИ, ХРАНИМОЙ В ЭВМ | 2010 |

|

RU2446445C1 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ БИТОВ БИНАРНОЙ СТРОКИ | 2009 |

|

RU2439662C2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК И СОЧЕТАНИЙ | 2010 |

|

RU2427885C1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

Изобретение относится к области кодирования информации и может быть использовано в системах защиты информации от несанкционированного доступа. Техническим результатом является ускорение процесса управляемой перестановки элементов (a

1, a,…, a

i, …a

N) исходной строки данных длиной N за счет конвейерной обработки, при выполнении преобразования за N тактов генератора тактовых импульсов. Дешифратор содержит К уровней узлов дешифрации, двойной буферный регистр накопления и хранения форматированных данных. При этом каждый уровень дешифрации содержит 2i-1 элементов  , объединяющих D триггеры хранения данных и регистр хранения и циклического сдвига бит кодов дешифрации длиной K-i+1. 2 ил.

, объединяющих D триггеры хранения данных и регистр хранения и циклического сдвига бит кодов дешифрации длиной K-i+1. 2 ил.

Дешифратор управляемой перестановки информации, хранимой в персональной ЭВМ, содержащий К уровней узлов дешифрации, где каждый уровень дешифрации содержит: 2i-1 элементов  , двойной буферный регистр накопления и хранения форматированных данных, отличающийся тем, что узлы дешифрации i-го уровня состоят из элементов, объединяющих D триггер хранения данных и регистр хранения и циклического сдвига бит кодов дешифрации длиной K-i+1, первый бит Q регистра управляет первым rd1 и вторым rd2 выходами разрешения записи rd1=Q,

, двойной буферный регистр накопления и хранения форматированных данных, отличающийся тем, что узлы дешифрации i-го уровня состоят из элементов, объединяющих D триггер хранения данных и регистр хранения и циклического сдвига бит кодов дешифрации длиной K-i+1, первый бит Q регистра управляет первым rd1 и вторым rd2 выходами разрешения записи rd1=Q,  , причем выход данных каждого элемента 1-го уровня электрически соединен с входами данных двух элементов (i+1)-го уровня, первый и второй выходы разрешения записи данных каждого элемента i-го уровня электрически соединены с входами разрешения записи данных двух элементов (i+1)-го уровня, входы тактовых импульсов электрически соединены между собой, входы разрешения записи управляющих кодов, поступающих на вход управляющих кодов, для всех элементов электрически соединены между собой, выход данных каждого элемента K-го уровня электрически соединен с двумя входами данных двойного буферного регистра накопления и хранения форматированных данных, первый и второй выходы разрешения записи данных каждого элемента K-го уровня электрически соединены с двумя входами разрешения записи данных двойного буферного регистра накопления и хранения форматированных данных.

, причем выход данных каждого элемента 1-го уровня электрически соединен с входами данных двух элементов (i+1)-го уровня, первый и второй выходы разрешения записи данных каждого элемента i-го уровня электрически соединены с входами разрешения записи данных двух элементов (i+1)-го уровня, входы тактовых импульсов электрически соединены между собой, входы разрешения записи управляющих кодов, поступающих на вход управляющих кодов, для всех элементов электрически соединены между собой, выход данных каждого элемента K-го уровня электрически соединен с двумя входами данных двойного буферного регистра накопления и хранения форматированных данных, первый и второй выходы разрешения записи данных каждого элемента K-го уровня электрически соединены с двумя входами разрешения записи данных двойного буферного регистра накопления и хранения форматированных данных.

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПОБИТОВОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2007 |

|

RU2320000C1 |

| ШИФРУЮЩИЙ БЛОК | 1998 |

|

RU2140715C1 |

| JP 55000911 A, 07.01.1980 | |||

| US 6622242 В1, 16.09.2003. | |||

Авторы

Даты

2010-05-20—Публикация

2008-08-06—Подача