Изобретение относится к области преобразования информации и может быть использовано в системах защиты информации от несанкционированного доступа.

Известны средства защиты конфиденциальной информации, базирующиеся на форматирующем преобразовании посимвольной транспозиции информации (Б.Шнайер. Прикладная криптография, 2-е издание: протоколы, алгоритмы, исходные тексты на языке Си. Под редакцией П.В.Семьянова. М., Триумф, 2002), однако с использованием частотного анализа по форматированным данным возможно восстановить исходные (A.Sinkov, Elementary Cryptoanalysis, Mathematical Assotiation of America, 1966).

Известны способ, устройство и носитель для кодирования информации, состоящий из многих слов, включающие в себя устройство пословного перемежения (патент РФ №2273092 МПК Н03М 13/00).

Наиболее близким к предлагаемому решению является устройство линейного дешифратора (патент RU 2032937 МПК G06F 11/00), который содержит K уровней узлов дешифрации (K - разрядность информационного входа дешифратора), K элементов НЕ, а каждый узел дешифрации выполнен в виде мажоритарного элемента, каждый уровень дешифрации содержит 2i мажоритарных элементов  вход выборки дешифратора соединен с первыми входами первого и второго мажоритарных элементов первого уровня, выход каждого мажоритарного элемента i-го уровня соединен с первыми входами пары мажоритарных элементов (i+1)-го уровня, выходы мажоритарных элементов k-го уровня являются выходами дешифратора, информационные входы которого соединены с входами элементов НЕ и соответственно с вторыми входами четных мажоритарных элементов уровней с первого по k-й, вторые входы нечетных мажоритарных элементов которых соединены соответственно с выходами элементов НЕ, третьи входы нечетных мажоритарных элементов всех уровней соединены с первым управляющим входом дешифратора, второй управляющий вход которого соединен с третьими входами четных мажоритарных элементов всех уровней.

вход выборки дешифратора соединен с первыми входами первого и второго мажоритарных элементов первого уровня, выход каждого мажоритарного элемента i-го уровня соединен с первыми входами пары мажоритарных элементов (i+1)-го уровня, выходы мажоритарных элементов k-го уровня являются выходами дешифратора, информационные входы которого соединены с входами элементов НЕ и соответственно с вторыми входами четных мажоритарных элементов уровней с первого по k-й, вторые входы нечетных мажоритарных элементов которых соединены соответственно с выходами элементов НЕ, третьи входы нечетных мажоритарных элементов всех уровней соединены с первым управляющим входом дешифратора, второй управляющий вход которого соединен с третьими входами четных мажоритарных элементов всех уровней.

Однако это устройство функционально не решает задачу управляемой побитовой транспозиции данных.

Задачей настоящего решения является обеспечение процесса произвольной побитовой транспозиции информации (форматирующего преобразования).

Техническим результатом является возможность высокоскоростного преобразования форматов данных методом транспозиции с использованием управляющих кодов.

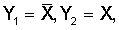

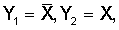

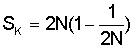

Поставленная задача решается тем, что в дешифратор, содержащий К уровней узлов дешифрации, каждый уровень дешифрации содержит 2i элементов  вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня, выход каждого элемента i-го уровня соединен с первыми входами пары элементов (i+1)-го уровня, согласно решению дополнительно введены регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов, причем элемент первого уровня реализует логическую функцию

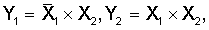

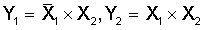

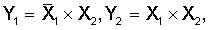

вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня, выход каждого элемента i-го уровня соединен с первыми входами пары элементов (i+1)-го уровня, согласно решению дополнительно введены регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов, причем элемент первого уровня реализует логическую функцию  остальные элементы реализуют логическую функцию

остальные элементы реализуют логическую функцию  вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов, входы Х1 остальных элементов i-ого уровня соединены с выходом i-того бита регистра управляющих кодов, входы Х2 остальных элементов i-того уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных, генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов.

вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов, входы Х1 остальных элементов i-ого уровня соединены с выходом i-того бита регистра управляющих кодов, входы Х2 остальных элементов i-того уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных, генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов.

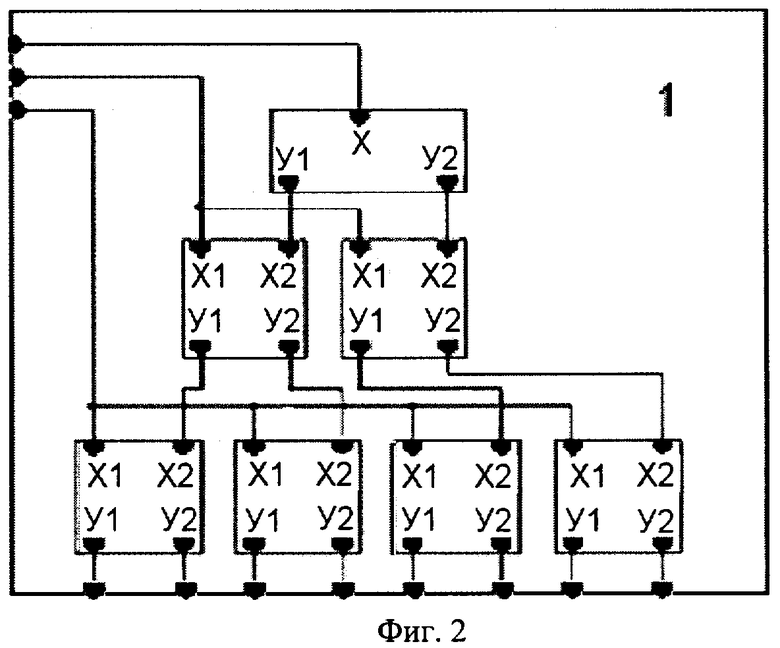

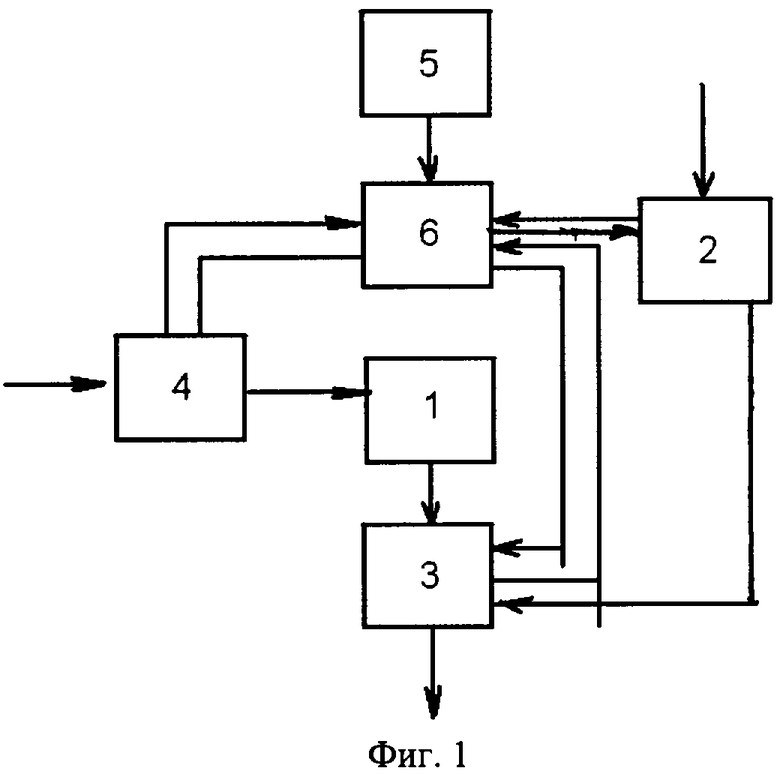

Изобретение поясняется чертежами, где на фиг.1 приведена блок-схема устройства; на фиг.2 - схема устройства для трех уровней, позволяющая выполнять транспозицию бинарного вектора данных из восьми элементов, где

1 - уровни дешифратора;

2 - сдвиговый регистр данных;

3 - двойной буферный регистр накопления и хранения форматированных данных;

4 - регистр управляющих кодов;

5 - генератор тактовых импульсов;

6 - блок управления.

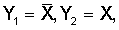

Предлагаемое устройство форматирования состоит из К уровней узлов дешифрации 1, выполняющих функцию транспозиции бинарного вектора данных (а1,а,...,аi,...аN), соединенных входами с регистром управляющих кодов 4, а выходами - с двойным буферным регистром накопления и хранения форматированных данных 3, информационный вход которого соединен с выходом входного сдвигового регистра данных 2. Каждый узел дешифрации 1 выполнен в виде элементов SEL0, SEL. Элемент SEL0 имеет логическую формулу  элементы SEL имеют логическую формулу

элементы SEL имеют логическую формулу  и образуют двоичное дерево (фиг.2). Для выполнения транспозиции вектора из N бит необходимо

и образуют двоичное дерево (фиг.2). Для выполнения транспозиции вектора из N бит необходимо  - элементов.

- элементов.

Вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов 4, входы Х1 остальных элементов i-го уровня соединены с выходом i-го бита регистра управляющих кодов 4, входы Х2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных 3 соединен с выходом сдвигового регистра данных 2. Генератор тактовых импульсов 5 соединен с блоком управления 6, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных 3, входным сдвиговым регистром данных 2, регистром управляющих кодов 4.

Устройство работает следующим образом. По переднему фронту сигнала генератора тактовых импульсов 5 на выход регистра 2 поступает текущий бит данных в формате хранения, текущий управляющий код загружается в регистр 4 и поступает на уровни дешифратора 1, с выходов которых управляющий сигнал поступает на соответствующий вход разрешения записи двойного буферного регистра накопления и хранения форматированных данных 3. По заднему фронту сигнала генератора тактовых импульсов данные со входа регистра 3 записываются в соответствующую ячейку регистра. Процесс повторяется N раз, после чего регистр 3 оказывается полностью заполненным, операция транспозиции блокируется, и выполняется операция записи транспонированных данных во второй регистр хранения 3. Перед записью во второй буферный регистр 3 осуществляется проверка отсутствия в нем данных, в противном случае выполняется необходимое число тактов ожидания. После процедуры записи транспозиции подвергается следующий пакет данных. Условием продолжения процесса транспозиции является наличие данных в регистрах 2, 4 и наличие свободных элементов регистра 3. При своевременном поступлении данных полный цикл транспозиции выполняется за N тактовых импульсов. Предлагаемое выполнение уровней позволяет обеспечить высокоскоростное преобразование форматов данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ ДЕШИФРАТОР УПРАВЛЯЕМОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2008 |

|

RU2390049C1 |

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2008 |

|

RU2390052C2 |

| УСТРОЙСТВО КРОСС-КЛАСТЕРНОЙ УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2009 |

|

RU2409842C1 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ЭВМ | 2009 |

|

RU2405187C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ОБРАТНЫХ ПЕРЕСТАНОВОК ИНФОРМАЦИИ, ХРАНИМОЙ В ЭВМ | 2010 |

|

RU2446445C1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ БИТОВ БИНАРНОЙ СТРОКИ | 2009 |

|

RU2439662C2 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК | 2009 |

|

RU2395834C1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Полевой модуль | 1987 |

|

SU1550451A1 |

Устройство относится к области кодирования информации и может быть использовано в системах защиты информации от несанкционированного доступа. Техническим результатом является ускорение преобразования форматов данных методом транспозиции с использованием управляющих кодов. Устройство содержит дешифратор побитовой транспозиции (1), сдвиговый регистр данных (2), двойной буферный регистр накопления и хранения форматированных данных (3), регистр управляющих кодов (4), генератор тактовых импульсов (5), блок управления (6). 2 ил.

Дешифратор, содержащий К уровней узлов дешифрации, каждый уровень дешифрации содержит 2 элемента  , вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня, отличающийся тем, что в него дополнительно введены регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов, причем элемент первого уровня реализует логическую функцию

, вход выборки дешифратора соединен с первыми входами первого и второго элементов первого уровня, отличающийся тем, что в него дополнительно введены регистр управляющих кодов, сдвиговый регистр данных, двойной буферный регистр накопления и хранения форматированных данных, блок управления, генератор тактовых импульсов, причем элемент первого уровня реализует логическую функцию  остальные элементы реализуют логическую функцию

остальные элементы реализуют логическую функцию  вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов, входы X1 остальных элементов i-того уровня соединены с выходом i-го бита регистра управляющих кодов, входы Х2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных, а входы разрешения записи этого регистра соединены с выходами последнего уровня дешифрации, генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов.

вход Х элемента первого уровня соединен с выходом первого бита регистра управляющих кодов, входы X1 остальных элементов i-того уровня соединены с выходом i-го бита регистра управляющих кодов, входы Х2 остальных элементов i-го уровня соединены с выходами элементов i-1 уровня, причем вход двойного буферного регистра накопления и хранения форматированных данных соединен с выходом сдвигового регистра данных, а входы разрешения записи этого регистра соединены с выходами последнего уровня дешифрации, генератор тактовых импульсов соединен с блоком управления, который своими входами и выходами соединен с буферным регистром накопления и хранения форматированных данных, входным сдвиговым регистром данных, регистром управляющих кодов.

| ЛИНЕЙНЫЙ ДЕШИФРАТОР | 1991 |

|

RU2032937C1 |

| СПОСОБ И УСТРОЙСТВО БЛОКИРОВАНИЯ КОМАНД ДЛЯ ОГРАНИЧЕНИЯ ДОСТУПА К ЗАПИСАННЫМ НА НОСИТЕЛЕ ДАННЫМ | 2005 |

|

RU2280890C1 |

| Устройство для преобразования информации | 1988 |

|

SU1645950A1 |

| US 6205551 B1, 20.03.2001. | |||

Авторы

Даты

2008-03-20—Публикация

2007-02-13—Подача