Изобретение относится к радиоизмерительной технике и может использоваться в стандартах частоты и времени, дисциплинированных стандартах частоты, приемниках-компараторах, системах единого времени и другой время-частотной аппаратуре.

Устройство формирования сигналов времени (УФСВ) решает задачи:

формирования основной шкалы времени (ШВ) 1 Гц, вспомогательной (задержанной) ШВ 1 Гц, автоматической синхронизация ШВ по внешнему импульсу синхронизации, коррекции (сдвига) ШВ, измерения сдвига внешней ШВ по отношению к основной, измерения временного положения импульсов «опрос» по отношению к основной ШВ, выдачи результатов измерения для индикации и обработки.

Известны устройства, выполняющие функции ФШВ, например многоканальный (по входам сигналов «опрос») измеритель интервалов времени (ИИВ) по свидетельству RU на полезную модель №20999, H03D 13/00. Однако данное устройство не формирует задержанную ШВ. Более функциональными возможностями обладает УФСВ по авт. св. SU №1220115, Н03К 3/64, которое за счет исключения механических кодовых переключателей обладает более высокой надежностью. Схема его принята в качестве прототипа заявляемого устройства.

Данная схема содержит формирователь импульсов опорной (высокой) частоты, выполненный на декадах основной делитель частоты, вспомогательный делитель частоты со схемой добавления/вычитания импульсов (СДВИ), коммутатор ШВ, блок управления, блок буферной памяти. Синусоидальный сигнал высокой частоты подается на формирователь, а с него в виде импульсной последовательности - на входы основного делителя частоты до 1 Гц и на вспомогательный делитель частоты со схемой СДВИ. Выходные импульсы частотой 1 Гц основного делителя частоты поступают на счетчик времени. Вспомогательный делитель частоты имеет построение аналогично основному делителю и выдает импульсы 1 Гц задержанной ШВ. Вспомогательный делитель частоты со схемой СДВИ, управляемой блоком 5, позволяет сдвигать вспомогательную шкалу времени относительно основной (в пределах 0-1 c с шагом 0,1 мкс). Последовательность импульсов вспомогательной ШВ используется при сличении и синхронизации часов между собой, например, путем запуска синхронизации осциллографа.

Состояние всех декад основного делителя частоты (10 МГц-1 Гц) изменяется последовательно от 000.000.0 до 999.999.9, причем состояниям 000.000.0 соответствует момент выдачи импульсов шкалы времени.

В одном положении коммутатора, который может быть выполнен на обычном тумблере, импульсы после формирования сдвигаемой шкалы времени через коммутатор поступают на вход блока буферной памяти, фиксируя состояние декад основного делителя частоты. При этом в блок буферной памяти переписывается десятичное число N, которое показывает, сколько импульсов входной частоты поступило на основной делитель с момента выдачи последнего импульса основной шкалы времени. Информация с блока буферной памяти поступает на выход для обработки и цифровой индикации. Таким образом, реализуются функции измерения и индикации временного сдвига вспомогательной ШВ относительно основной. Устройство позволяет также измерять сдвиг между основной и внешней ШВ. Для этого коммутатор ставится в положение, при котором на вход блока буферной памяти через коммутатор подаются импульсы внешней ШВ.

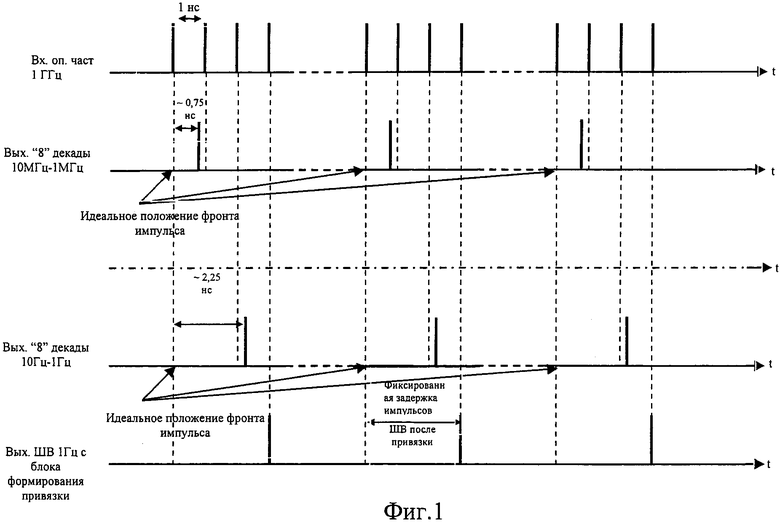

Недостатком прототипа является невозможность достаточно точного определения временного положения переднего фронта импульса внешней ШВ по отношению к основной даже при использовании достаточно быстродействующих триггеров делителей частоты. Из-за накопления задержек при движении рабочего фронта импульсов от младшего разряда к старшему (при делении входной опорной частоты от 1 ГГц до 1 Гц) это накопление составит для декад с проносом фронтов, выполненных по современным нанотехнологиям, (0.18 мкм) ~ 0.25 нс × 9 разрядов = 2.25 нс. Моменты переключения триггеров декад по мере удаления от младшего разряда будут все более отставать от идеальных моментов времени, соответствующих моментам прихода импульсов опорной частоты, например, 1 ГГц. Временные диаграммы процесса "отставания" сигналов основного (и вспомогательного) делителя частоты представлены на фиг.1.

Таким образом, переписываемые в блок буферной памяти состояния триггеров декад основного делителя частоты не будут соответствовать идеальным, что приведет к увеличению погрешности измерений в 2-3 раза, превышающей минимальный временной дискрет даже для очень быстродействующих триггеров. Такое "отставание" сигналов основного делителя частоты сильно зависит от внешней температуры и влияет на стабильность сигналов.

Кроме того, схема прототипа не имеет входа сигналов опроса и не позволяет реализовать быструю оперативную выдачу записываемой в блок буферной памяти информации в последовательном коде после единичного измерения при высокой частоте импульсов внешней ШВ, не позволяет производить коррекцию (сдвиг) и синхронизацию основного делителя частоты по внешней ШВ или импульсу синхронизации.

Технической задачей, на решение которой направленно данное изобретение, является повышение точности определения временного положения импульсов внешней ШВ, импульса опроса, повышение стабильности (температурной) выдаваемых ШВ, расширение функциональных возможностей за счет реализации режимов определения временного положения импульсов опроса, коррекции (сдвига) и синхронизации внешним импульсом синхронизации основного делителя частоты, повышение быстродействия оперативной выдачи информации в последовательном коде после единичного измерения.

Решение задачи достигается тем, что в устройство формирования сигналов времени, содержащее формирователь импульсов, вход которого является входом устройства, основной делитель частоты, включающий счетчик импульсов и блок буферной памяти, блок управления, вспомогательный делитель частоты, включающий счетчик импульсов, коммутатор, первый вход которого соединен с шиной входа внешней шкалы времени, при этом первые входы счетчиков импульсов основного и вспомогательного делителей частоты соединены с выходом формирователя импульсов, дополнительно введены второй и третий коммутаторы, в основной делитель частоты введены второй счетчик импульсов, триггер управления, блок остановки счета и предварительной установки декад основного делителя частоты и блок привязки основной шкалы времени, во вспомогательный делитель частоты введены второй счетчик импульсов, триггер управления, блок остановки счета и предварительной установки декад вспомогательного делителя частоты, блок привязки вспомогательной шкалы времени и блок буферной памяти, первый вход второго коммутатора соединен с шиной входа внешней шкалы времени, вторые входы первого и второго коммутаторов соединены соответственно с выходом блоков привязки шкалы времени вспомогательного и основного делителей частоты, которые соответственно являются выходами вспомогательной и основной шкалы времени устройства, третьи входы коммутаторов объединены и являются входом сигнала «опрос» устройства, четвертые входы коммутаторов соединены с первым выходом блока управления, а выходы коммутаторов соединены соответственно с первыми входами триггеров управления основного и вспомогательного делителей частоты, вторые входы триггеров управления соединены соответственно с выходом блока привязки шкалы времени основного и вспомогательного делителей частоты, выходы триггеров управления соединены соответственно с первыми входами вторых счетчиков импульсов основного и вспомогательного делителей частоты и с первыми входами блоков буферной памяти основного и вспомогательного делителей частоты, вторые входы которых соединены соответственно со вторым и третьим выходами блока управления, выходы вторых счетчиков импульсов основного и вспомогательного делителей частоты соединены соответственно с третьими входами блоков буферной памяти основного и вспомогательного делителей частоты, вторые входы вторых счетчиков импульсов основного и вспомогательного делителей частоты соединены с выходом формирователя импульсов, выход блока буферной памяти вспомогательного делителя частоты соединен с первым входом третьего коммутатора, второй вход которого соединен с выходом блока буферной памяти основного делителя частоты, третий вход которого соединен с четвертым выходом блока управления, а выход третьего коммутатора является выходом информации (для обработки и индикации) устройства, первые входы блоков остановки счета и предварительной установки декад основного и вспомогательного делителей частоты соединены соответственно с пятым и шестым выходом блока управления, вторые входы соединены с входом сигнала синхронизации устройства, третьи входы соединены соответственно с первыми входами блоков привязки шкал времени основного и вспомогательного делителей частоты и с выходом формирователя импульсов, четвертые входы соединены с первым выходом блока управления, а пятые входы соединены соответственно с выходами блоков привязки шкалы времени основного и вспомогательного делителей частоты, вторые входы которых соединены соответственно с выходами первых счетчиков импульсов основного и вспомогательного делителей частоты, вторые и третьи входы которых соединены соответственно с первыми и вторыми выходами блоков остановки счета и предварительной установки декад основного и вспомогательного делителей частоты.

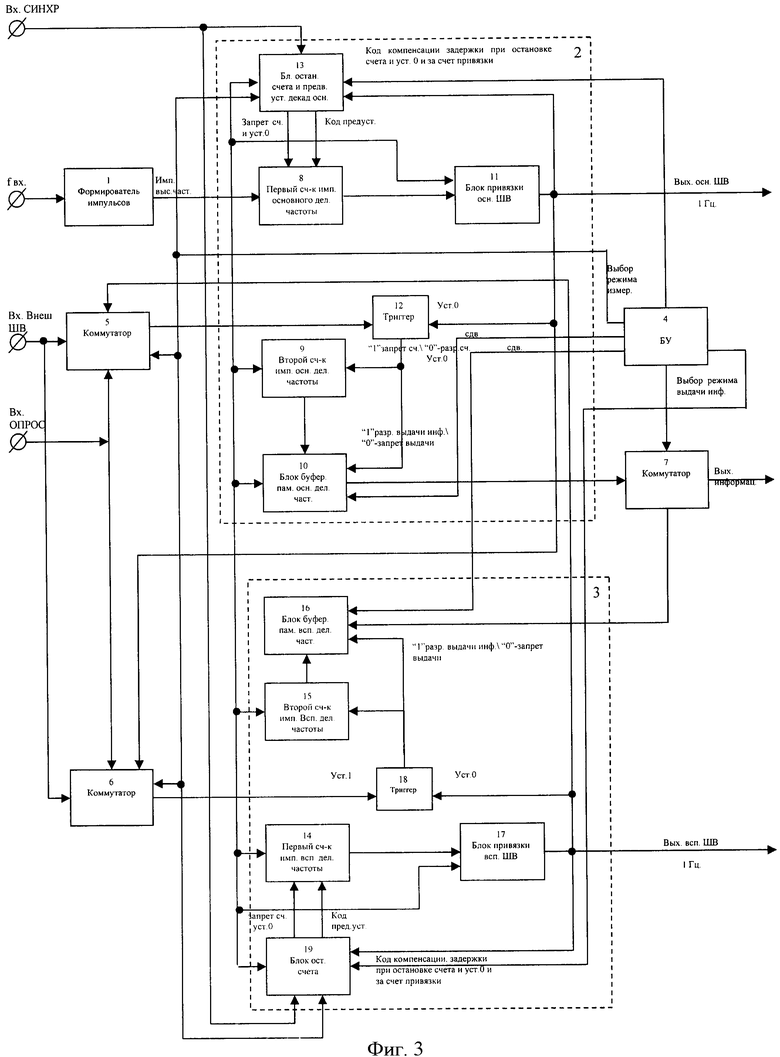

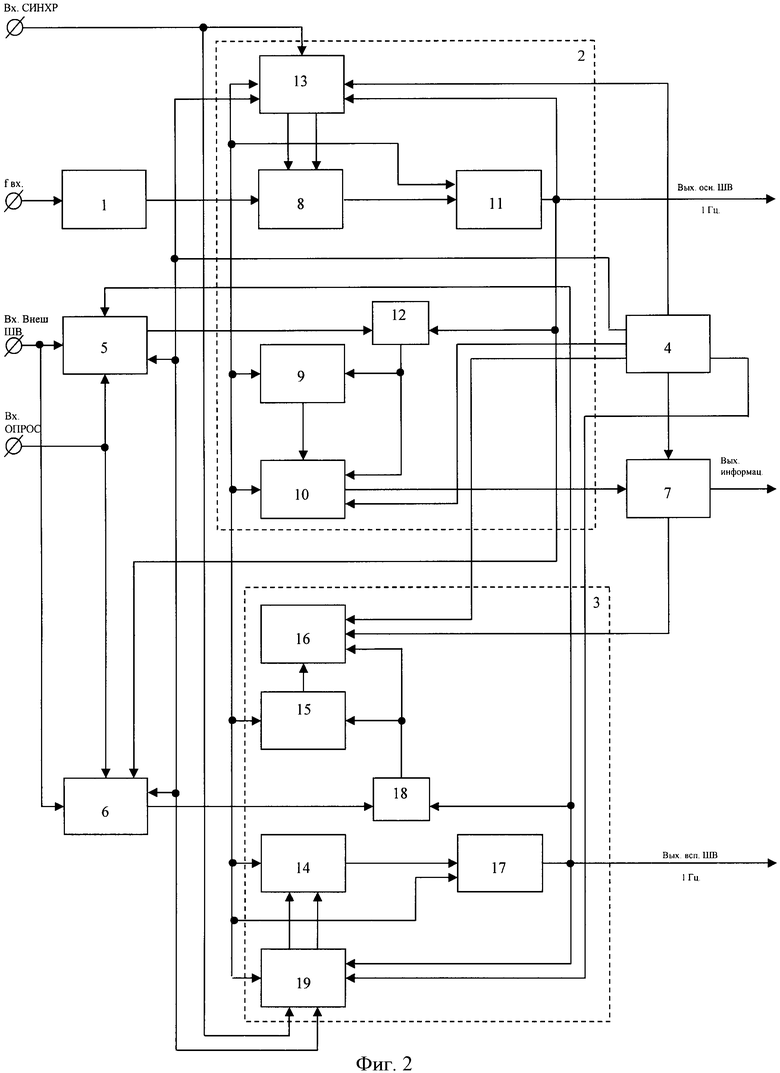

На фиг.2 представлена структурная схема устройства, на фиг.3 - структурная схема устройства с пояснениями.

На схемах обозначено: 1 - формирователь импульсов (ФИ); 2 - основной делитель частоты; 3 - вспомогательный делитель частоты; 4 - блок управления; 5, 6, 7 - коммутаторы; 8 - первый счетчик импульсов основного делителя частоты; 9 - второй счетчик импульсов основного делителя частоты; 10 - блок буферной памяти основного делителя частоты; 11 - блок привязки к опорной частоте основной ШВ; 12 - триггер управления основного делителя частоты; 13 - блок остановки счета и предварительной установки декад основного делителя частоты; 14 - первый счетчик импульсов вспомогательного делителя частоты; 15 - второй счетчик импульсов вспомогательного делителя частоты; 16 - блок буферной памяти вспомогательного делителя частоты; 17 - блок привязки к опорной частоте вспомогательной ШВ; 18 - триггер управления вспомогательного делителя частоты; 19 - блок остановки счета и предварительной установки декад вспомогательного делителя частоты.

Устройство формирования сигналов времени содержит формирователь импульсов 1, вход fВХ которого является входом устройства, основной 2 и вспомогательный 3 делители частоты, блок управления 4 и три коммутатора 5-7. Основной делитель частоты 2 включает в себя первый 8 и второй 9 счетчики импульсов, блок буферной памяти 10, блок привязки основной шкалы времени 11, триггер управления 12, блок остановки счета 13 (и предварительной установки декад первого счетчика импульсов основного делителя частоты). Вспомогательный делитель частоты 3 включает в себя первый 14 и второй 15 счетчики импульсов, блок буферной памяти 16, блок привязки вспомогательной шкалы времени 17, триггер управления 18, блок остановки счета 19 (и предварительной установки декад первого счетчика импульсов вспомогательного делителя частоты). Первый вход коммутатора 1 соединен с шиной входа внешней шкалы времени. Первые входы счетчиков импульсов 8 и 14 соединены с выходом формирователя импульсов 1. Первый вход коммутатора 6 соединен с шиной входа внешней шкалы времени, вторые входы коммутаторов 5 и 6 соединены соответственно с выходом блоков привязки шкалы времени 17 и 11, которые соответственно являются выходами вспомогательной и основной шкалы времени устройства, третьи входы коммутаторов 5 и 6 объединены и являются входом сигнала «опрос» устройства, четвертые входы коммутаторов 5 и 6 соединены с первым выходом блока управления 4, а выходы коммутаторов 5 и 6 соединены соответственно с первыми входами триггеров управления 12 и 18. Вторые входы триггеров управления 12 и 18 соединены соответственно с выходом блока привязки шкалы времени 11 и 17, выходы триггеров управления 12 и 18 соединены соответственно с первыми входами счетчиков импульсов 9 и 15 и с первыми входами блоков буферной памяти 10 и 16, вторые входы которых соединены соответственно со вторым и третьим выходами блока управления 4. Выходы счетчиков импульсов 9 и 15 соединены соответственно с третьими входами блоков буферной памяти 10 и 16, вторые входы счетчиков импульсов 9 и 15 соединены с выходом формирователя импульсов 1. Выход блока буферной памяти 16 соединен с первым входом коммутатора 7, второй вход которого соединен с выходом блока буферной памяти 10, третий вход коммутатора 7 соединен с четвертым выходом блока управления 4, а выход коммутатора 7 является выходом информации (для обработки и индикации) устройства. Первые входы блоков остановки счета и предварительной установки декад 13 и 19 соединены соответственно с пятым и шестым выходом блока управления 4, вторые входы соединены с входом сигнала синхронизации устройства, третьи входы соединены соответственно с первыми входами блоков привязки шкал времени 11 и 17 и с выходом формирователя импульсов 1, четвертые входы соединены с первым выходом блока управления 4, а пятые входы соединены соответственно с выходами блоков привязки шкалы времени 11 и 17, вторые входы которых соединены соответственно с выходами счетчиков импульсов 8 и 14, вторые и третьи входы которых соединены соответственно с первыми и вторыми выходами блоков остановки счета и предварительной установки декад 13 и 19.

Работа устройства происходит следующим образом.

Вышеприведенная структура построения УФСВ делает оба канала формирования ШВ равноправными. Сформированные формирователем импульсов 1 импульсы высокой опорной частоты 1 ГГц поступают одновременно на первый 8 и второй 9 счетчики импульсов основного делителя частоты 2, на первый 14 и второй 15 счетчики импульсов вспомогательного делителя частоты 3, которые работают параллельно при подаче на первые входы вторых счетчиков импульсов основного и вспомогательного делителей частоты разрешающего сигнала логического "0", по переднему фронту которого происходит установка в "0" вторых счетчиков импульсов.

При выборе режима измерения временной задержки импульсов «опрос» или внешней ШВ относительно ШВ любого из каналов формирования, что производится с помощью блока управления 4 и коммутаторов 5 и 6, выбранные сигналы поступают либо на триггер управления 12 основного делителя частоты, либо на триггер управления 18 вспомогательного делителя частоты, которые после переключения своего состояния в лог."1" прекращают поступление импульсов на счетный вход соответствующего второго счетчика импульсов 9 или 15 основного 2 или вспомогательного 3 делителя частоты. Таким образом, спустя небольшой промежуток времени, когда закончатся все переключения триггеров счетчика, в нем будет зафиксировано состояние, которое точно (с погрешностью в одну единицу дискретности счета) соответствует моменту прихода выбранного импульса «опрос» или внешней ШВ относительно выбранной основной или вспомогательной ШВ. Эта информация переписывается в один из блоков буферной памяти 10 и 16 и может быть передана с помощью импульсов сдвига с блока управления 4 последовательным кодом через коммутатор 7 на выход устройства.

Приходящий следом импульс основной или вспомогательной ШВ, относительно которой измеряется временное положение импульса «опрос» или внешней ШВ, переключит триггер управления 12 или 18 в исходное состояние, по переднему фронту соответствующего сигнала произойдет синхронизация второго счетчика импульсов 9 или 15 с предустановкой младших декад в необходимое состояние для компенсации потери времени на действие импульса установки в "0" декад, и счет второму счетчику импульсов будет разрешен. После этого процесс повторится.

За счет многоступенчатой привязки импульсов 1 Гц поделенной частоты к исходной опорной частоте рассогласование выходных импульсов ШВ с импульсами опорной частоты (1 ГГц) сводится к минимуму (см. последнюю диаграмму на фиг.1), но появляется фиксированная задержка импульса ШВ по отношению к его идеальному положению. Указанная задержка может быть измерена в режиме калибровки устройства (при подаче на вход внешней ШВ или «опрос» на какой-либо канал соответствующего импульса выходной ШВ устройства), зафиксирована по индикатору или внешним устройством обработки информации и учтена в блоке управления 4 при формировании кода компенсации задержки при остановке счета и установке "0" и за счет привязки.

При поступлении импульса синхронизации, например, ШВ 1 Гц от внешнего стандарта частоты блоки остановки счета и предварительной установки декад 13 и 19 основного 2 и вспомогательного 3 делителей частоты останавливают работу первых счетчиков импульсов 8 и 14 делителей частоты 2 и 3 и устанавливают их декады в "0". Затем происходит предварительная установка декад в состояние, которое позволяет компенсировать потери времени на "привязку" импульсов ШВ и за счет накопления задержек при движении переключающего триггера рабочего фронта импульсов. Остановка счета нужна также для того, чтобы все триггеры надежно были установлены предварительно в вычисленное заранее и заложенное в блоке управления 4 вручную или программно требуемое состояние.

После того как в блоках 13 и 19 будет отсчитана необходимая задержка счет импульсов опорной частоты первыми счетчиками импульсов основного и вспомогательного делителей частоты возобновляется, при этом выходные импульсы ШВ будут синхронизированы с внешнем импульсом синхронизации с минимальной погрешностью, равной ± единице дискретности счета.

При коррекции (сдвиге) основной или вспомогательной ШВ на заданную величину с шагом, равным одному периоду высокой опорной частоты (1 ГГц) при выборе этого режима, аналогично импульсу синхронизации, при поступлении импульса основной или вспомогательной ШВ на соответствующий вход блока установки счета и предварительной установке декад основного или вспомогательного делителя частоты производится разовая однократная остановка счета первого счетчика импульсов основного или вспомогательного делителя частоты, установка декад счетчика в "0", затем предустановка декад в состояние, заложенное программно или вручную в блоке управления 4, необходимое для требуемого сдвига ШВ с учетом потерь времени на привязку и на накопление задержек при движении переключающего фронта.

Практическая реализация блоков предлагаемого УФСВ может быть выполнена следующим образом: блоки 1, 2, 3, 5 - 19 для обеспечения компактности и технологичности выполнения устройства со сложной радиоэлектронной схемой выполнены в виде единого сложно-функционального узла на большой интегральной схеме (система на кристалле), например, типа К1897АП1Т; блок 4 - на микроконтроллере фирмы «Миландр» Россия, CPU фирмы Fastvel и др.

Таким образом, заявленная структура УФСВ позволяет максимально уменьшить погрешность измерения временного положения импульсов «опрос» и внешней ШВ и сделать ее равной ± 1 счета, улучшить температурную стабильность выдаваемых ШВ, повысить надежность и оперативное быстродействие при выдаче информации на внешнее устройство обработки, а также расширить функциональные возможности УФСВ за счет обеспечения режимов коррекции (сдвига) ШВ основной и вспомогательной и их синхронизации по внешнему импульсу СИНХР. Кроме того данное УФСВ позволяет проводить взаимную перекрестную проверку и калибровку каналов без использования других вспомогательных устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ | 2008 |

|

RU2379824C1 |

| СИНХРОНИЗИРУЕМЫЕ РАДИОЧАСЫ | 2002 |

|

RU2221336C1 |

| ПРИЕМНИК-КОМПАРАТОР СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2002 |

|

RU2236753C2 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1991 |

|

RU2024042C1 |

| Устройство формирования сигналов времени | 1983 |

|

SU1220115A1 |

| ПРИЕМНИК-КОМПАРАТОР СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2008 |

|

RU2379834C2 |

| Устройство для синхронизации часов по радиоканалу | 1983 |

|

SU1230442A2 |

| Регистрирующее устройство | 1988 |

|

SU1509595A1 |

| Устройство для сбора и регистрации данных о работе информационно-вычислительной системы | 1981 |

|

SU978155A1 |

Изобретение относится к радиоизмерительной технике и может использоваться в стандартах частоты и времени, системах единого времени и другой время-частотной аппаратуре. Достигаемый технический результат - повышение точности определения временного положения импульсов опроса, коррекции и синхронизации, повышение стабильности выдаваемых шкал времени и повышение быстродействия оперативной выдачи информации. Устройство содержит формирователь импульсов, основной и вспомогательный делители частоты, блок управления и три коммутатора. 3 ил.

Устройство формирования сигналов времени, содержащее формирователь импульсов, вход которого является входом устройства, основной делитель частоты, включающий счетчик импульсов и блок буферной памяти, блок управления, вспомогательный делитель частоты, включающий счетчик импульсов, и коммутатор, первый вход которого соединен с шиной входа внешней шкалы времени, при этом первые входы счетчиков импульсов основного и вспомогательного делителей частоты соединены с выходом формирователя импульсов, отличающееся тем, что в него дополнительно введены второй и третий коммутаторы, в основной делитель частоты введены второй счетчик импульсов, триггер управления, блок остановки счета и предварительной установки декад основного делителя частоты и блок привязки основной шкалы времени, во вспомогательный делитель частоты введены второй счетчик импульсов, триггер управления, блок остановки счета и предварительной установки декад вспомогательного делителя частоты, блок привязки вспомогательной шкалы времени и блок буферной памяти, первый вход второго коммутатора соединен с шиной входа внешней шкалы времени, вторые входы первого и второго коммутаторов соединены соответственно с выходом блоков привязки шкалы времени вспомогательного и основного делителя частоты, которые соответственно являются выходами вспомогательной и основной шкалы времени устройства, третьи входы коммутаторов объединены и являются входом сигнала «опрос» устройства, четвертые входы коммутаторов соединены с первым выходом блока управления, а выходы коммутаторов соединены соответственно с первыми входами триггеров управления основного и вспомогательного делителей частоты, вторые входы триггеров управления соединены соответственно с выходом блока привязки шкалы времени основного и вспомогательного делителей частоты, выходы триггеров управления соединены соответственно с первыми входами вторых счетчиков импульсов основного и вспомогательного делителей частоты и с первыми входами блоков буферной памяти основного и вспомогательного делителей частоты, вторые входы которых соединены соответственно со вторым и третьим выходами блока управления, выходы вторых счетчиков импульсов основного и вспомогательного делителей частоты соединены соответственно с третьими входами блоков буферной памяти основного и вспомогательного делителей частоты, вторые входы вторых счетчиков импульсов основного и вспомогательного делителей частоты соединены с выходом формирователя импульсов, выход блока буферной памяти вспомогательного делителя частоты соединен с первым входом третьего коммутатора, второй вход которого соединен с выходом блока буферной памяти основного делителя частоты, третий вход которого соединен с четвертым выходом блока управления, а выход третьего коммутатора является выходом информации устройства, первые входы блоков остановки счета и предварительной установки декад основного и вспомогательного делителей частоты соединены соответственно с пятым и шестым выходом блока управления, вторые входы соединены с входом сигнала синхронизации устройства, третьи входы соединены соответственно с первыми входами блоков привязки шкал времени основного и вспомогательного делителей частоты и с выходом формирователя импульсов, четвертые входы соединены с первым выходом блока управления, а пятые входы соединены соответственно с выходами блоков привязки шкалы времени основного и вспомогательного делителей частоты, вторые входы которых соединены соответственно с выходами первых счетчиков импульсов основного и вспомогательного делителей частоты, вторые и третьи входы которых соединены соответственно с первыми и вторыми выходами блоков остановки счета и предварительной установки декад основного и вспомогательного делителей частоты.

| Устройство формирования сигналов времени | 1983 |

|

SU1220115A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Устройство формирования резервированного сигнала времени | 1982 |

|

SU1092459A1 |

| СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1993 |

|

RU2099865C1 |

Авторы

Даты

2010-05-27—Публикация

2008-12-03—Подача