Изобретение относится к радиоизмерительной технике, а именно к устройствам выделения ошибочных символов из информационной последовательности и измерения верности передачи информации в цифровых трактах, и может использоваться в анализаторах ошибок при контроле качества работы каналов связи.

Принцип работы таких устройств основан на том, что тест-последовательность, в качестве которой наиболее часто используется псевдослучайная последовательность (ПСП) максимальной длины (М-последовательность), подается на объект контроля, с которого поступает на анализатор ошибок, для проверки качества работы объекта контроля.

Известны устройства для детектирования ошибок [1-4], в которых используются систематические свойства М-последовательностей, которые позволяют достаточно точно проводить измерение количества ошибок. При входе в режим синхронизации устройство начинает процесс детектирования и анализа потока ошибок. За счет определения факта ложной синхронизации и запрещения счета ошибок на время, необходимое для повторной синхронизации, повышается точность измерений. Затраты времени на проверку отсутствия ложной синхронизации и (в случае необходимости) повторную синхронизацию устройства составляют 3 n тактовых интервалов, где n - число разрядов (длина) регистра сдвига, в который производится запись входной информации.

Недостатком таких устройств является недостаточная помехоустойчивость - невозможность синхронизации при приеме внешней М-последовательности с максимальным средним по времени коэффициентом ошибок  , так как если на этапах записи информации или проверки отсутствия ложной синхронизации во входной внешней М-последовательности будет присутствовать хотя бы одна ошибка (в каком-либо из n битов информации), то такие детекторы ошибок будут возвращаться в исходное начальное состояние, при этом подсчет ошибок производиться не будет.

, так как если на этапах записи информации или проверки отсутствия ложной синхронизации во входной внешней М-последовательности будет присутствовать хотя бы одна ошибка (в каком-либо из n битов информации), то такие детекторы ошибок будут возвращаться в исходное начальное состояние, при этом подсчет ошибок производиться не будет.

Наиболее близкой является более помехоустойчивая и точная схема устройства для детектирования ошибок, описанная в [2], которая содержит первый, второй, третий и четвертый сумматоры по модулю два (СМД), компаратор, первый, второй, третий, четвертый и пятый триггеры, первый, второй, третий и четвертый счетчики, элемент И, регистр сдвига (PC). После включения устройства импульс синхронизации устанавливает триггеры, счетчики в исходное состояние, при котором на выходе счетчиков и прямом выходе триггеров устанавливается уровень лог."0" или лог."1", разрешающие счетчику счет тактов. Компаратор начинает сравнение входной внешней ПСП и формируемой внутренней ПСП. Если в процессе нормального функционирования устройства произойдет сбой в регистре сдвига, появятся импульсы, которые, воздействуя на вход "установки логического нуля", установят лог."0" на его выходе, устройство перейдет ко второму этапу работы при синхронизации - записи информации, затем к третьему этапу и т.д. до тех пор, пока автоматически не произойдет пересинхронизация устройства.

Большая помехоустойчивость данного устройства позволяет использовать его при анализе входной внешней ПСП, прошедшей объект контроля, а также в тех случаях, когда вместо устройства [1] требуются другие методы анализа тестовой ПСП, например измерение времени задержки сигнала в объекте контроля. Но данная схема устройства детектирования ошибок [2] является не универсальной, т.к. предполагает проектирование устройства с жестко заданными обратными связями (ОС) приемного регистра сдвига (PC), такими же как ОС в PC на передающей стороне, отсутствует возможность выбора вида тест-последовательности (ПСП/кодовое слово), режима генерации/приема тест-последовательности, выбора тактовой частоты. Кроме того, за счет наличия промежуточных ОС по длине PC не возможно повысить быстродействие устройства при работе с кодовым словом (КС), где используется лишь одна ОС - с конца PC на его первый разряд.

Технической задачей, на решение которой направлено данное изобретение, является расширение функциональных возможностей устройства за счет возможности выбора конфигурации ОС PC, выбора вида тест-последовательности ПСП/КС, расширение диапазона рабочих частот при использовании КС (повышение быстродействия).

Указанная задача решается тем, что в устройство для детектирования ошибок, содержащее последовательно соединенные компаратор, первый триггер, R-вход которого соединен с корпусом, первый сумматор по модулю два, второй сумматор по модулю два, выход которого является установочным входом устройства, второй триггер, первый счетчик, и третий триггер, R-вход которого соединен с выходом второго триггера, четвертый триггер, S-вход и инверсный выход которого соединены соответственно с выходом и S-входом второго триггера, второй счетчик, элемент И, первый регистр сдвига (псевдослучайной последовательности PC ПСП), третий счетчик, третий сумматор по модулю два (псевдослучайной последовательности СМД ПСП), пятый триггер, четвертый сумматор по модулю два, четвертый счетчик, выход которого подключен к С-входу четвертого триггера, прямой выход которого соединен с первыми входами элемента И и второго счетчика, второй вход которого соединен с выходом компаратора, вторым входом элемента И и первым входом третьего счетчика, второй вход которого соединен с первым входом четвертого счетчика, третьим входом элемента И и инверсным выходом третьего триггера, выход пятого триггера, D-вход которого является информационным входом устройства, соединен со вторым входом первого сумматора по модулю два и первым входом компаратора, второй вход которого подключен ко второму входу второго сумматора по модулю два, первый, второй и третий входы третьего сумматора по модулю два соединены соответственно с первым, вторым и третьим выходами регистра сдвига, С-вход пятого триггера и второй вход четвертого счетчика соединены со вторым входом первого счетчика, выход элемента И соединен с первым входом четвертого сумматора по модулю два, выход третьего счетчика соединен с S-входом четвертого триггера, а выход компаратора является выходом устройства, дополнительно введены последовательно соединенные блок управления, первый коммутатор, второй регистр сдвига (кодового слова PC КС) и пятый сумматор по модулю два (кодового слова СМД КС), блок выбора опорных частот и второй коммутатор, первый вход которого соединен с выходом пятого сумматора по модулю два, второй вход соединен с выходом третьего сумматора по модулю два, третий вход соединен с первым выходом блока управления, а выход соединен со вторым входом четвертого сумматора по модулю два, вторым входом второго сумматор по модулю два, вторым входом компаратора и является выходом псевдослучайной последовательности или кодового слова (ПСП\КС) устройства, второй вход первого коммутатора соединен с выходом четвертого сумматора по модулю два, а второй его выход соединен с входом первого разряда первого регистра сдвига, второй выход блока управления соединен с третьим входом третьего счетчика, третий выход блока управления соединен с четвертым входом третьего сумматора по модулю два, четвертый выход блока управления соединен со вторым входом пятого сумматора по модулю два, пятый выход блока управления соединен с третьим входом четвертого триггера, а шестой выход блока управления соединен с третьим входом первого счетчика, первый выход блока опорных частот соединен со вторым входом первого счетчика, второй выход является выходом тактовой частоты устройства, а вход является тактовым входом устройства.

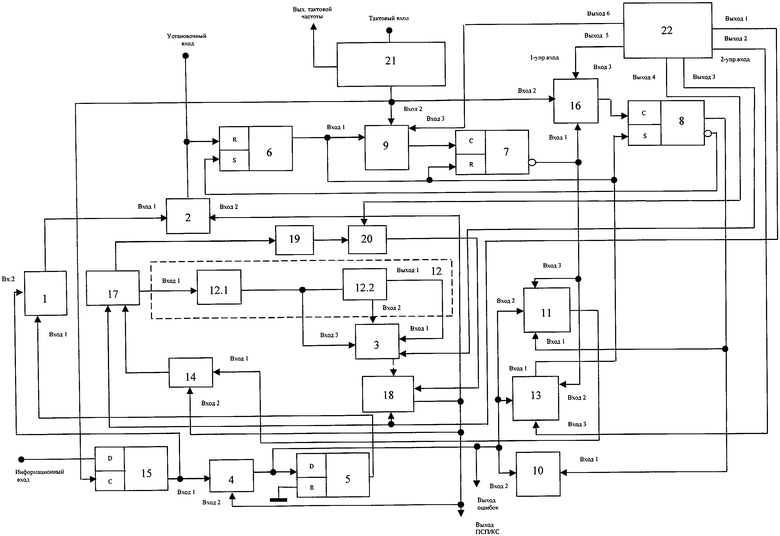

На чертеже приведена структурная электрическая схема заявляемого устройства для детектирования ошибок, где обозначено:

1, 2, 3 - первый, второй и третий сумматоры по модулю два (СМД);

4 - компаратор;

5, 6, 7, 8 - первый, второй, третий и четвертый триггеры;

9, 10 - первый и второй счетчики;

11 - элемент И;

12 - регистр сдвига (PC), включающий первый и остальные разряды 12.1, 12.2;

13 - третий счетчик;

14 - четвертый СМД;

15 - пятый триггер;

16 - четвертый счетчик;

17 и 18 - первый и второй коммутаторы;

19 - регистр сдвига кодового слова (PC КС);

20 - сумматор по модулю два кодового слова (СМД КС);

21 - блок выбора опорных частот;

22 - блок управления.

Обозначения входов триггеров: R - вход установки логического нуля;

С - счетный (тактовый) вход; D - информационный вход.

Устройство содержит последовательно соединенные первый СМД1, второй СМД2, выход которого является установочным входом устройства, а второй вход СМД2 соединен со вторым входом компаратора 4, выход которого через триггер 5, R-вход которого соединен с корпусом, подключен к первому входу СМД1, последовательно соединенные триггер 6, счетчик 9 и триггер 7, R-вход которого соединен с выходом триггера 6; S-вход, С-вход и инверсный выход триггера 8 соединены соответственно с выходом триггера 6, выходом счетчика 16 и S-входом триггера 6, прямой выход триггера 8 соединен с первыми входами элемента И 11 и счетчика 10, второй вход которого соединен с выходом компаратора 4, вторым входом элемента И 11 и первым входом счетчика 13, второй вход которого соединен с первым входом счетчика 16, третьим входом элемента И 11 и инверсным выходом триггера 7; выход триггера 15, D-вход которого является информационным входом устройства, соединен со вторым входом СМД 1 и первым входом компаратора 4; первый, второй и третий входы СМД 3 соединены соответственно с первым, вторым и третьим выходами регистра сдвига 12, С-вход триггера 15 и второй вход счетчика 16 соединены со вторым входом счетчика 9, выход элемента И 11 соединен с первым входом СМД 14, выход счетчика 13 соединен с S-входом триггера 8; последовательно соединенные блок управления 22, коммутатор 17, регистр сдвига 19 и СМД КС 20, первый вход коммутатора 18 соединен с выходом СМД 20, второй вход коммутатора 18 соединен с выходом СМД 3, третий вход коммутатора 18 соединен с первым выходом блока управления 22, выход коммутатора 18 соединен со вторым входом СМД 14, вторым входом СМД 2, вторым входом компаратора 4 и является выходом псевдослучайной последовательности или кодового слова устройства, второй вход коммутатора 17 соединен с выходом СМД 14, а второй его выход соединен со входом первого разряда PC 12, второй, третий, четвертый, пятый и шестой выходы блока управления 22 соединены соответственно с третьим входом счетчика 13, с четвертым входом СМД 3, со вторым входом СМД 20, с третьим входом триггера 16 и с третьим входом счетчика 9, первый выход блока опорных частот 21 соединен со вторым входом счетчика 9, второй выход блока опорных частот 21 является выходом тактовой частоты устройства, а вход является тактовым входом устройства.

В процессе работы устройство для детектирования ошибок формирует внутреннюю тест-последовательность, обеспечивает синхронизацию внутренней тест-последовательности с входной внешней тест-последовательностью, выделяет ошибки из входной тест-последовательности путем сравнения входной внешней и внутренней тест-последовательностей и подсчитывает их количество.

После включения устройства производится выбор режима работы: прием/генерация тест-последовательности, вида тест-последовательности ПСП/КС, выбор опорной частоты, выбор ОС PC ПСП или КС, задание параметров (чисел) счетчиков "n", "m", "1+α", что выполняется вручную или программным образом через блок управления 22, который может быть выполнен на микроконтроллере. Выбор работы с ПСП или КС осуществляется коммутаторами 17 и 18 по управляющим сигналам с блока управления 22. После этого при работе с ПСП импульс синхронизации (начальной установки) устанавливает триггеры 6, 7, 8, счетчики 9, 13 и 16 в исходное состояние, при котором на выходе счетчиков 9 и 16 и прямом выходе триггера 7 устанавливается "0", на прямом выходе триггера 8 - "1", a на выходе триггера 6 и счетчика 13 устанавливается уровень "0", который разрешает счетчику 9 счет тактов. Модуль счета счетчика 16, равный числу m, и модуль счета счетчика 13, равный числу 1+α, устанавливаются предварительно сигналами управления на соответствующих входах устройства. Компаратор 4 начинает сравнение входной внешней ПСП и формируемой на выходе СМД 3 внутренней ПСП. При этом импульсы ошибок с выхода компаратора 4 проходят на счетчик 13 ошибок и на элемент И 11, последний открыт уровнями "1" с инверсного выхода триггера 7 и прямого выхода триггера 8. Поэтому импульсы ошибок воздействуют на PC 12 через СМД 14 до тех пор, пока счетчик 9 не досчитает число тактовых импульсов до n. Если при этом в PC 12 записывается безошибочная информация, т.е. регистр сдвига детектора ошибок входит в синхронизм с регистром сдвига передатчика, то на следующем этапе, когда на инверсном выходе триггера 7 устанавливается "0" и разрешается счет тактов счетчику 16 и счет ошибок счетчику 13, а элемент И 11 закрыт, счетчик 13 за число тактовых периодов m при правильном выборе m и 1+α не досчитает до своего модуля счета 1+α (при ожидаемом распределении ошибок во входной ПСП). На выходе счетчика 16 появится импульс, который устанавливает "0" на прямом выходе триггера 8, который закрывает элемент И 11 и разрешает счет ошибок счетчику 10, т.е. третий этап синхронизации благополучно закончится.

Если на втором этапе синхронизации в PC 12 записана хотя бы одна ошибка, которая принята во входной ПСП, то на третьем этапе синхронизации счетчик 13 за число тактовых периодов m успевает досчитать до своего модуля счета 1+α, и положительный импульс на его выходе устанавливает схему устройства в исходное состояние.

Такой процесс повторяется до тех пор, пока PC 12 не войдет в синхронизм с регистром сдвига передатчика. После этого устройство начинает работать как детектор ошибок входной внешней ПСП.

При нормальном функционировании устройства информация на обоих входах СМД 2 совпадает и поэтому на его выходе формируется "0".

Если в процессе функционирования устройства происходит сбой в PC 12, на выходе СМД 2 появляются импульсы, которые, воздействуя на вход установки "0" второго триггера 6, устанавливают "0" на его выходе, начинает работать первый счетчик 9, и устройство вновь переходит ко второму этапу работы при синхронизации - записи информации, затем к третьему этапу и т.д., до тех пор, пока автоматически не происходит пересинхронизация устройства. При этом процесс измерения прерывается на время, равное времени пересинхронизации устройства (n+m+1 тактовых интервалов), а затем продолжается. Работа в режиме работы с КС осуществляется аналогично и обеспечивается PC КС 19 и СМД КС 20.

Устройство позволяет использовать любые реально применяемые ПСП и КС за счет возможности выбора ОС PC ПСП и PC КС, т.е. становится многофункциональным, кроме того, позволяет увеличить быстродействие устройства за счет возможности использования отдельного канала КС, избежав влияния межэлектродных емкостей при использовании коммутаторов в перестраиваемых СМД ПСП 3.

Такая схема позволяет осуществить практическую реализацию устройства детектирования в виде сложно-функционального блока для СБИС (система на кристалле) типа К1897ДП1Т.

Источники информации

1 Авторское свидетельство СССР №1251335, МПК Н04В 3/46, 1985 г.

2. Авторское свидетельство СССР №1709542 - прототип, МПК Н04В 3/46, 1990 г.

3. Патент РФ №2279184, МПК Н04В 3/46, 2006 г.

4. Патент РФ №2276835, МПК Н04В 3/46, 2006 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

| Устройство для детектирования ошибок | 1985 |

|

SU1251335A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛОВ ВРЕМЕНИ | 2008 |

|

RU2390925C1 |

| Устройство для детектирования ошибок | 1989 |

|

SU1663771A1 |

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

Устройство для детектирования ошибок относится к радиоизмерительной технике и может быть использовано для выделения ошибочных символов из информационной последовательности и измерения верности передачи информации в цифровых трактах, может использоваться в анализаторах ошибок при контроле качества работы каналов связи. Достигаемым техническим результатом является расширение функциональных возможностей устройства для детектирования ошибок, расширение диапазона рабочих частот. Устройство содержит первый (1), второй (2), третий (3) и четвертый (14) сумматоры по модулю два (СМД), компаратор (4), первый (5), второй (6), третий (7), четвертый (8) и пятый (15) триггеры, первый (9), второй (10), третий (13) и четвертый счетчики (16), элемент И (11), регистр сдвига (PC) (12), первый (17) и второй (18) коммутаторы, регистр сдвига кодового слова (19) (PC КС), сумматор по модулю два кодового слова (20) (СМД КС), блок выбора опорных частот (21) и блок управления (22). 1 ил.

Устройство для детектирования ошибок, содержащее последовательно соединенные компаратор, первый триггер, R-вход которого соединен с корпусом, первый сумматор по модулю два, второй сумматор по модулю два, выход которого является установочным входом устройства, второй триггер, первый счетчик и третий триггер, R-вход которого соединен с выходом второго триггера, четвертый триггер, S-вход и инверсный выход которого соединены соответственно с выходом и S-входом второго триггера, второй счетчик, элемент И, первый регистр сдвига псевдослучайной последовательности, третий счетчик, третий сумматор по модулю два псевдослучайной последовательности, пятый триггер, четвертый сумматор по модулю два, четвертый счетчик, выход которого подключен к С-входу четвертого триггера, прямой выход которого соединен с первыми входами элемента И и второго счетчика, второй вход которого соединен с выходом компаратора, вторым входом элемента И и первым входом третьего счетчика, второй вход которого соединен с первым входом четвертого счетчика, третьим входом элемента И и инверсным выходом третьего триггера, выход пятого триггера, D-вход которого является информационным входом устройства, соединен со вторым входом первого сумматора по модулю два и первым входом компаратора, второй вход которого подключен ко второму входу второго сумматора по модулю два, первый, второй и третий входы третьего сумматора по модулю два соединены соответственно с первым, вторым и третьим выходами регистра сдвига, С-вход пятого триггера и второй вход четвертого счетчика соединены со вторым входом первого счетчика, выход элемента И соединен с первым входом четвертого сумматора по модулю два, выход третьего счетчика соединен с S-входом четвертого триггера, а выход компаратора является выходом устройства, отличающееся тем, что в него дополнительно введены последовательно соединенные блок управления, первый коммутатор, второй регистр сдвига кодового слова и пятый сумматор по модулю два кодового слова, блок выбора опорных частот и второй коммутатор, первый вход которого соединен с выходом пятого сумматора по модулю два, второй вход соединен с выходом третьего сумматора по модулю два, третий вход соединен с первым выходом блока управления, а выход соединен со вторым входом четвертого сумматора по модулю два, вторым входом второго сумматора по модулю два, вторым входом компаратора и является выходом псевдослучайной последовательности или кодового слова устройства, второй вход первого коммутатора соединен с выходом четвертого сумматора по модулю два, а второй его выход соединен со входом первого разряда первого регистра сдвига, второй выход блока управления соединен с третьим входом третьего счетчика, третий выход блока управления соединен с четвертым входом третьего сумматора по модулю два, четвертый выход блока управления соединен со вторым входом пятого сумматора по модулю два, пятый выход блока управления соединен с третьим входом четвертого счетчика, а шестой выход блока управления соединен с третьим входом первого счетчика, первый выход блока опорных частот соединен со вторым входом первого счетчика, второй выход является выходом тактовой частоты устройства, а вход является тактовым входом устройства.

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ ДАННЫХ В ПРЯМОМ КАНАЛЕ UMTS-2000 ДЛЯ ВТОРОГО ТИПА ПРЕРЫВИСТОЙ ПЕРЕДАЧИ | 1999 |

|

RU2168858C1 |

| Дешифратор адреса | 1978 |

|

SU741470A1 |

| US 5446370 A, 29.08.1995. | |||

Авторы

Даты

2010-05-27—Публикация

2008-12-03—Подача