Изобретение относится к логическим полупроводниковым К-МОП интегральным схемам.

Известны: Электрические схемы К-МОП логических элементов «ИЛИ-НЕ», в частности:

- электрическая схема «ИЛИ-НЕ» - [1], содержащая два n-МОП и два p-МОП транзистора;

- электрические схемы «ИЛИ-НЕ» логических элементов, содержащие восемь и более МОП транзисторов [2, 3, 4].

Недостатки

- электрическая схема логического элемента «ИЛИ-НЕ» [1] обеспечивает информационную емкость, равную только 1 биту информации (два логических состояния -лог «0» и лог «1»);

- электрические схемы известных троичных инверторов «НЕ» [2, 3, 4] обеспечивают большую информационную емкость 1,5 бита (три логических состояния - лог «0», лог «-1» лог «+1»), однако, сложны, поскольку содержат большее количество МОП транзисторов и их соединений.

Наиболее близкой по технической сущности является электрическая схема «ИЛИ-НЕ» элемента [1], которая выбрана за прототип, содержащая первую и вторую входные и выходную шины, общую шину и шину питания, первый и второй n-МОП транзисторы и первый и второй p-МОП транзисторы, причем затворы первых n-МОП и p-МОП транзисторов подсоединены к первой входной шине, а затворы вторых n-МОП и p-МОП транзисторов подсоединены ко второй входной шине. Исток первого n-МОП транзистора подсоединен к общей шине, его сток - к истоку второго n-МОП транзистора, исток первого p-МОП транзистора подсоединен к шине питания.

Данная электрическая схема не позволяет получить более двух логических уровней сигнала, т.е. более (1 бита информации).

Техническим результатом изобретения является повышение информационной емкости логического элемента - инвертора.

Технический результат достигается за счет:

введения в электрическую схему 2 дополнительных конденсаторов, соединенных, соответственно, первый - со стоком второго n-МОП транзистора и выходной шиной, второй - со стоком второго p-МОП транзистора и выходной шиной инвертора, при этом исток второго p-МОП транзистора соединен со стоком первого p-МОП транзистора.

Изобретение поясняется приведенными чертежами

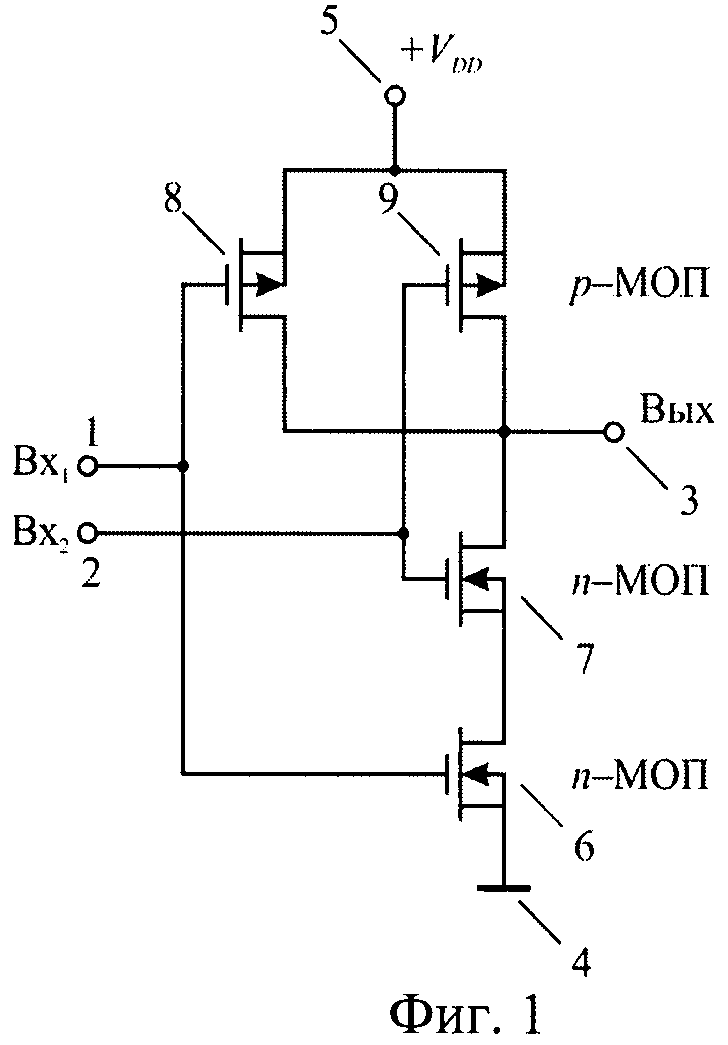

Электрическая схема прототипа приведена на чертеже 1 фиг.1. Она содержит первую 1 и вторую 2 входные и выходную 3 шины, общую шину 4 и шину питания 5, первый 6 и второй 7 n-МОП транзисторы и первый 8 и второй 9 и p-МОП транзисторы, причем затворы первых 6 n-МОП и 8 p-МОП транзисторов подсоединены к первой входной шине, а затворы вторых n-МОП и p-МОП - транзисторов 7, 9 соответственно подсоединены к второй 2 входной шине. Исток первого 6 n-МОП транзистора подсоединен к общей шине 4, его сток - к истоку второго n-МОП транзистора, исток первого p-МОП транзистора 8 подсоединен к шине, питания 5, стоки p-МОП транзисторов 8, 9 подключены к выходной шине 3.

Электрическая схема изобретения

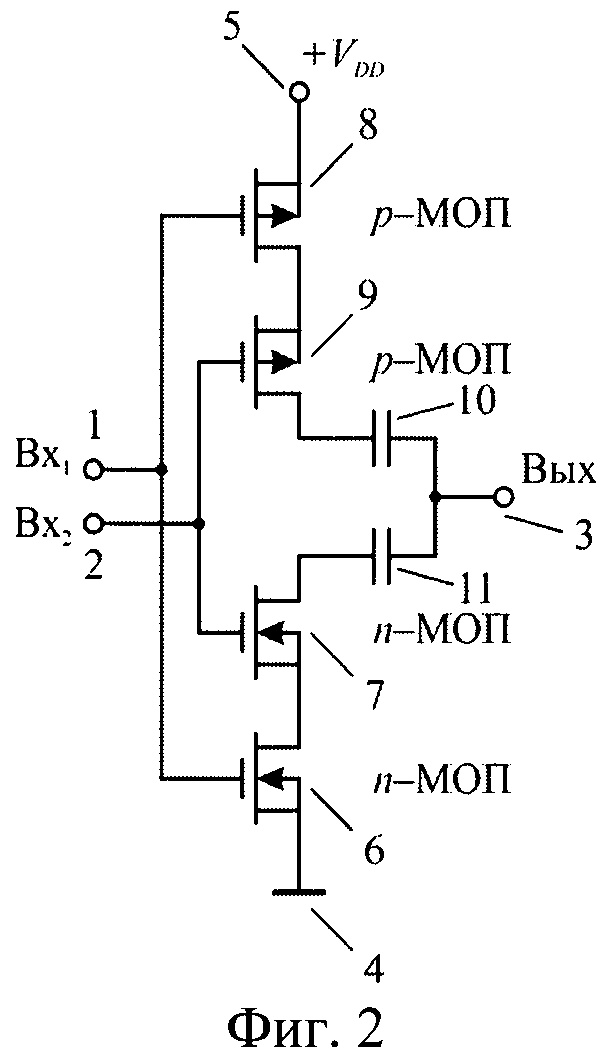

На чертеже 1 (фиг.2) приведена электрическая схема изобретения. Она содержит входную 1 и выходную 2 шины, общую шину 3 и шину питания 4, два первых n-МОП - 6, и p-МОП - 8 транзистора соответственно, затворы которых соединены между собой и подсоединены к первой входной шине 1, исток первого n-МОП транзистора 6 подсоединен к обшей шине 4, а его сток к истоку второго n-МОП транзистора 7, затвор которого соединен с затвором второго p-МОП транзистора 9, исток которого соединен со стоком первого p-МОП транзистора 8, исток которого подсоединен к шине питания, при этом сток второго p-МОП транзистора 9 соединен через первый дополнительный конденсатор 10 с выходной шиной 3, а сток второго n-МОП транзистора 7 соединен через второй дополнительный конденсатор 11 с выходной шиной 3. Подзатворные области n-МОП транзисторов 6, 7 подсоединены к обшей шине 4, а подзатворные области p-МОП транзисторов 8, 9 подсоединены к шине питания 5. Причем подзатворные области n и p-МОП транзисторов могут иметь «плавающий» потенциал, т.е. ни с чем не соединены.

Троичный К-МОП-С Логический элемент «ИЛИ-НЕ» работает следующим образом.

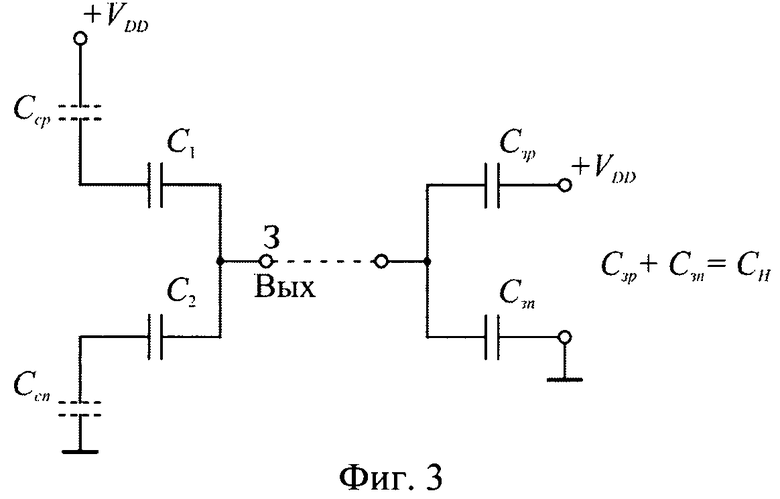

При подаче низкого (нулевого потенциала) соответствующего состоянию логической «лог - 1» на первый вход 1 и второй вход 2 n-МОП транзисторы 6, 7 закрываются, а p-МОП транзисторы 8, 9 открываются, при этом на стоке второго p-МОП транзистора 10 появляется положительный потенциал (+Vdd) шины питания 4, который через емкость первого конденсатора (Cl) 10 поступает на выход схемы 3 и на вход следующего логического элемента, например, аналогичного логического элемента, затворные емкости n и p-МОП транзисторов которого (Сзп и Сзр) см. фиг.3 (образуют емкостную нагрузку логического элемента Сн).

При подаче высокого потенциала (соответствующего состоянию логической «лог+1» на первый и второй входы 1, 2 p-МОП транзисторы 8, 9 закрываются, а n-МОП транзисторы 6, 7 открываются, при этом на его стоке n-МОП транзистора 7 появляется низкий - нулевой потенциал) общей шины, который через емкость второго конденсатора С2 11 поступает на вход следующего логического элемента, образующего емкостную нагрузку Cн.

При этом для получения высоких по абсолютному значению потенциалов (близких соответственно к напряжению питания и нулевому потенциалу) на выходе 3 схемы, необходимых для нормальной работы логических элементов нагрузки, необходимо выполнение условия, такого чтобы:

емкость каждого конденсатора C1 и С2 была больше суммарной емкости p-n перехода сток - подзатворная область, соответственно Сc,n, Сc,p и нагрузочной емкости Cн.

C1>Cн+Cc,p

С2>Cн+Cc,n

где Cн=Cз,п+Cз,p

Cн - емкость нагрузки логического элемента;

Cc,n - емкость конденсатора, образуемого стоком n-МОП транзистора и его подзатворной областью;

Сc,p - емкость конденсатора, образуемого стоком p-МОП транзистора и его подзатворной областью;

Сз,п - емкость конденсатора, образованного затвором и подзатворной областью n-МОП транзистора;

Сз,p - емкость конденсатора, образованного затвором и подзатворной областью p-МОП транзистора.

При наличии на входах 1, 2 логического элемента состояний логического «лог 0», соответствующего потенциалу +Vdd/2, оба транзистора логического элемента будут открыты, поскольку пороговые напряжения (Vт,n, Vт,p) n-МОП и p-МОП транзисторов выбираются меньше по абсолютной величине напряжения питания схем +Vdd/2 т.е. (+Vdd/2>Vт,п).

{+Vdd/2}>{Vt,p}, таким образом потенциал напряжения питания +Vdd поделится равными емкостями, соответственно, пополам, т.е +Vdd/2, что соответствует состоянию «лог 0» на выходе логического элемента.

При наличии на входах 1, 2 логического элемента других сочетаний возможных логических состояний «лог 0» и «лог+1», представленных в таблице 1 «истинности» (он работает аналогичным образом, см. таблицу 1).

Пример конкретной реализации

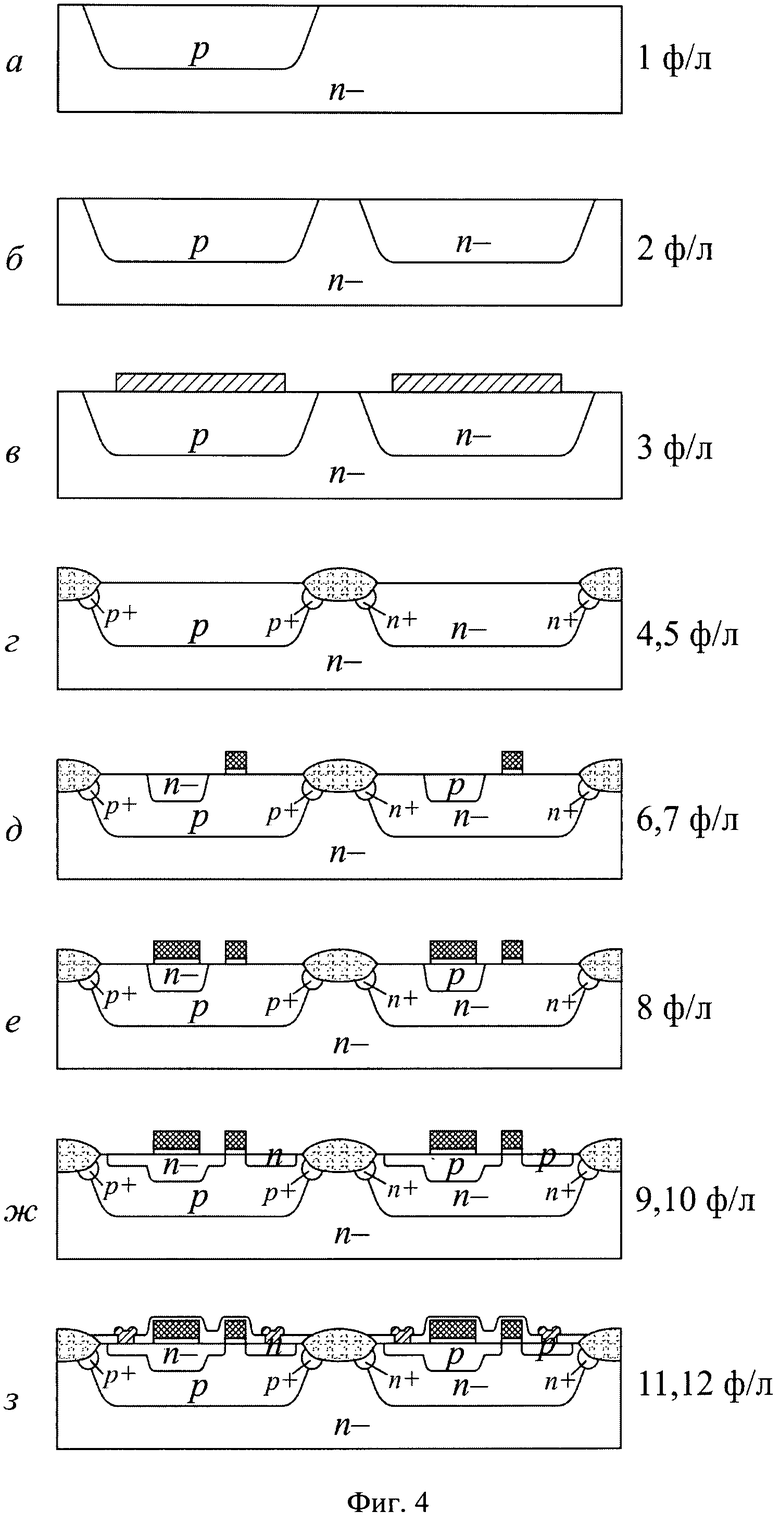

Логический элемент может быть выполнен по технологии, близкой к стандартной для К-МОП микросхем, например: (см. рис.4, чертеж 2):

а) проведение 1-й фотолитографией и формирование ионным легированием бора в подложке-p-кармана, т.е. подлатворной области p-типа, см. рис.4,а;

б) проведение 2-й фотолитографией и формирование ионным легированием фосфора в подложке-p-кармана, т.е. подлатворной области n-типа, см рис.4, 6;

в) формирование 3-й фотолитографией жесткой маски из нитрида кремния, см. рис.4,в;

г) формирование 4-ей и 5-ой фотолитографией и ионным легированием p+ и n+охранных областей;

- локальное окисление (формировании толстого диэлектрика) и удаление нитрида кремния, см. рис.4,г;

д) формирование путем проведения 6 и 7 фотолитографий и ионного легирования фосфора и бора «первоначальных» n+ и p+стоковых областей, см. рис.4,д,

е) формирование затворных областей, т.е. окислении поверхности кремния, т.е. создании тонкого, подзатворного оксида и осаждение поликристаллического слоя кремния на поверхность пластины, и проведение операции 8-й фотолитографии - обтрава - разводки поликремния, см. рис.4,е;

ж) проведение - 9-й и - 10-й фотолитографии с последующей имплантацией бора и фосфор, т.е. формирование «основных» областей стока истока n-типа и p-типа МОП транзисторов, см. рис.4,ж;

з) формирование металлической разводки - соединения стоков - истоков - затворов МОП транзисторов путем осаждения плазмохимического оксида, формирование 11-й фотолитографией контактных окон, осаждение алюминия и его образа с помощью 12-й литографии, см. рис.4,з.

Примечание.

Формировать «первоначальные» n+ и p+стоковые области можно ионным легированием примеси с высокой энергией ионов не до, а после формирования затворных областей.

Литература

1.1. Джонс М.Х. Электроника - практический курс. Москва: Постмаркет, 1999. - 528 с. (с.381), Practical Introduction to Electronic Circuits. By Martin Hartley Jones. Cambridge University Press, 40 West 20th Street, New York, N.Y. 10011-4211. 522 pages.

2. Попов Н.Д. Лукашенко В.А. «Логическое устройство отрицания». Патент PU №238.78.95С2 от 01.11.2004, Заявка №2004.131.582.09.

4. Пат. 2005080257 Япония. Симосу дорайба кайро оеби симосу инба: та кайро (Схема КМОП-драйвера, а также схема КМОП-инвертора) / Хидэки Фукуда. Заявл. 04.09.2003, опубл. 24.03.2005.

4. А.Кушнеров Троичная цифровая техника. Ретроспектива и современность (http://314159.ru/kushnerov/kushnerov1.pdf)

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" | 2011 |

|

RU2481701C2 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ДИНАМИЧЕСКОЕ ПОСЛЕДОВАТЕЛЬНОЕ ФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО | 2005 |

|

RU2392672C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| Ячейка памяти статического оперативного запоминающего устройства с радиоактивным источником питания | 2021 |

|

RU2777553C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении информационной емкости логических элементов. Электрическая схема троичного К-МОП-С логического элемента «ИЛИ-НЕ», содержащая первую и вторую входные и выходную шины, общую шину и шину питания, первый и второй n-МОП транзисторы и первый и второй р-МОП транзисторы, причем затворы первых n-МОП и р-МОП транзисторов подсоединены к первой входной шине, а затворы вторых n-МОП и р-МОП транзисторов подсоединены к второй входной шине, исток первого n-МОП транзистора подсоединен к общей шине, его сток - к истоку второго n-МОП транзистора, исток первого р-МОП транзистора подсоединен к шине питания, при этом электрическая схема содержит два дополнительных конденсатора, соединенных соответственно, первый - со стоком второго n-МОП транзистора и выходной шиной, второй - со стоком второго р-МОП транзистора и выходной шиной, при этом исток второго р-МОП транзистора соединен со стоком первого р-МОП транзистора. 11 ил., 1 табл.

Электрическая схема троичного К-МОП-С логического элемента «ИЛИ-НЕ», содержащая первую и вторую входные и выходную шины, общую шину и шину питания, первый и второй n-МОП транзисторы и первый и второй и р-МОП транзисторы, причем затворы первых n-МОП и р-МОП транзисторов подсоединены к первой входной шине, а затворы вторых n-МОП и р-МОП транзисторов подсоединены к второй входной шине, исток первого n-МОП транзистора подсоединен к общей шине, его сток - к истоку второго n-МОП транзистора, исток первого р-МОП транзистора подсоединен к шине питания, отличающаяся тем, что, с целью повышения информационной емкости, электрическая схема содержит два дополнительных конденсатора, соединенных соответственно: первый со стоком второго n-МОП транзистора и выходной шиной, второй - со стоком второго р-МОП транзистора и выходной шиной, при этом исток второго р-МОП транзистора соединен со стоком первого р-МОП транзистора.

| RU 2003123617 А, 27.01.2005 | |||

| Способ изготовления прокаткойпОлыХ издЕлий CO СпиРАльНыМиРЕбРАМи | 1978 |

|

SU833343A2 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| JP 8139591 А, 31.05.1996 | |||

| JP 4044018 B2, 06.02.2008 | |||

| RU 2001129132 А, 20.08.2003. | |||

Авторы

Даты

2012-11-27—Публикация

2011-09-16—Подача