Предлагаемое изобретение относится к микроэлектронике и может быть использовано при создании запоминающих и логических устройств компьютеров.

Известна электрическая схема динамической ячейки памяти, содержащая МДП транзистор, исток которого подключен соответственно к входной разрядной шине и запоминающему конденсатору, подключенному к общей шине.

Такая ячейка памяти не позволяет достичь максимального быстродействия в широко применяемых в настоящее время динамических запоминающих устройствах (ДОЗУ), которое ограничивается временем выборки информации ~20•109 с, вследствие малой крутизны МДП транзисторы по сравнению с биополярным и малой удельной емкостью МДП конденсатора.

Данный недостаток частично устраняется в схеме динамической ячейкой памяти, содержащей биополярный двухэмиттерный транзистор, находящейся в состоянии насыщения или отсечки, коллектор которого через резистор подключен к шине питания, база к входной шине, а эмиттеры к входной и тактовой шинам соответственно.

Указанная схема имеет ограниченное быстродействие ~3•10-9 с и надежность работы требует синхронного тактового сигнала по тактовой шине и совпадения по времени релаксации заряда в базе с длительностью тактового импульса.

Техническим эффектом данного изобретения является повышение надежности работы и быстродействия динамической памяти до уровня ~10-10 с.

Указанный эффект достигается тем, что в схеме динамической ячейки памяти, содержащей биополярный транзистор, коллектор которого подключен к выходной шине, эмиттер к общей шине, а база через конденсатор к входной шине и через дополнительный резистор к общей шине.

Для дальнейшего повышения быстродействия эмиттер подсоединен к общей шине через второй дополнительный резистор.

Для повышения быстродействия эмиттер подсоединен к общей шине через дополнительный источник питания.

Для повышения быстродействия база транзистора подсоединена к конденсатору и дополнительному резистору через третий дополнительный резистор.

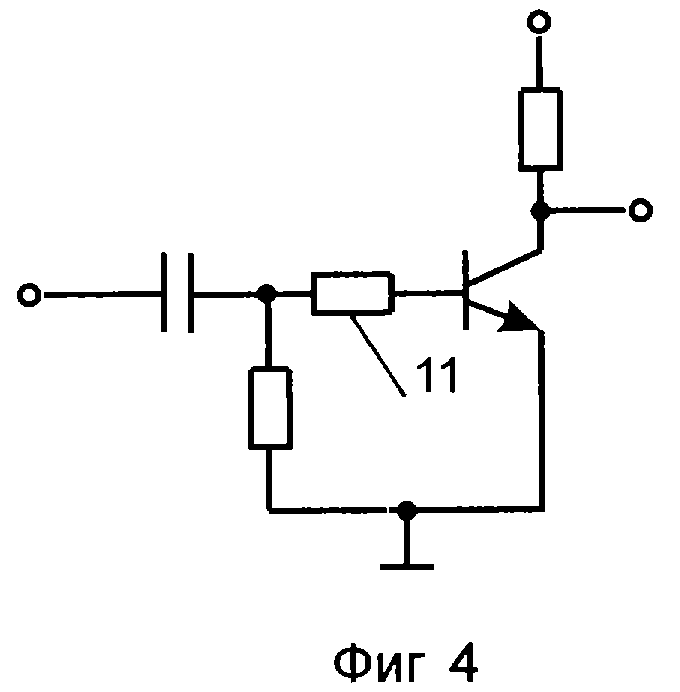

Для повышения технологичности конденсатор представляет собой диод, анод которого соединен с базой транзистора, а катод с входной шиной.

Ниже приводится описание настоящего изобретения со ссылками на чертеж, на котором:

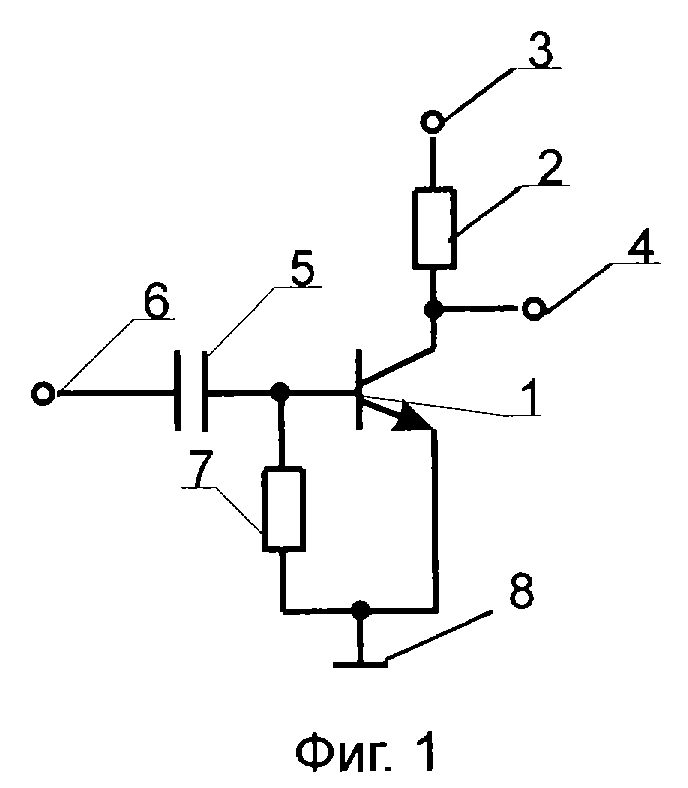

на фиг. 1 показана схема динамической ячейки памяти (ДЯП);

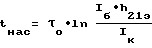

на фиг. 2 показана схема динамической ячейки памяти со вторым дополнительным резистором в эмиттере;

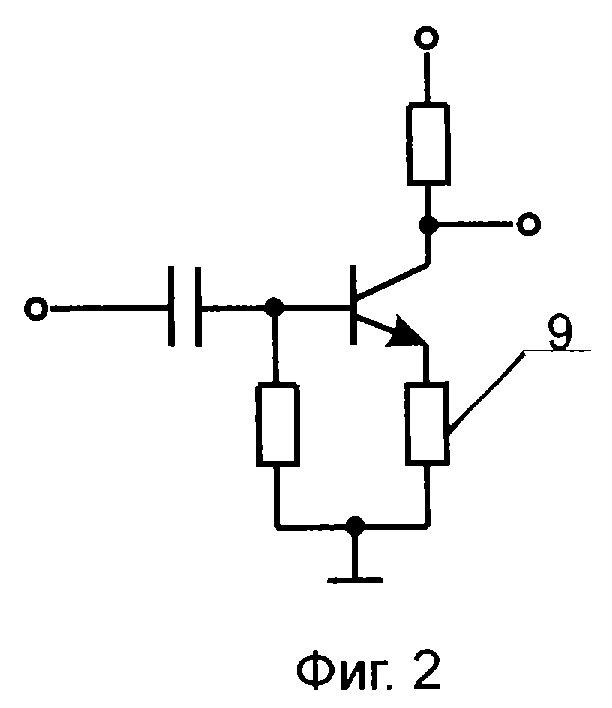

на фиг. 3 показана схема ДЯП с дополнительным источником питания;

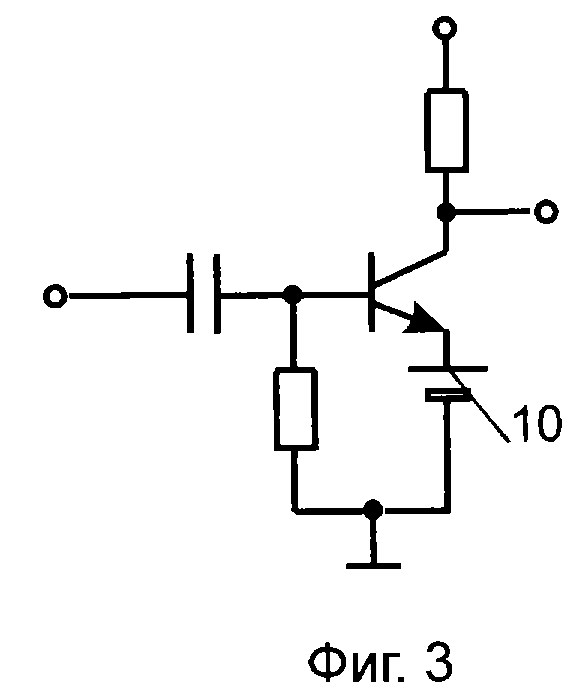

на фиг. 4 показана схема ДЯП с третьим дополнительным резистором на базе;

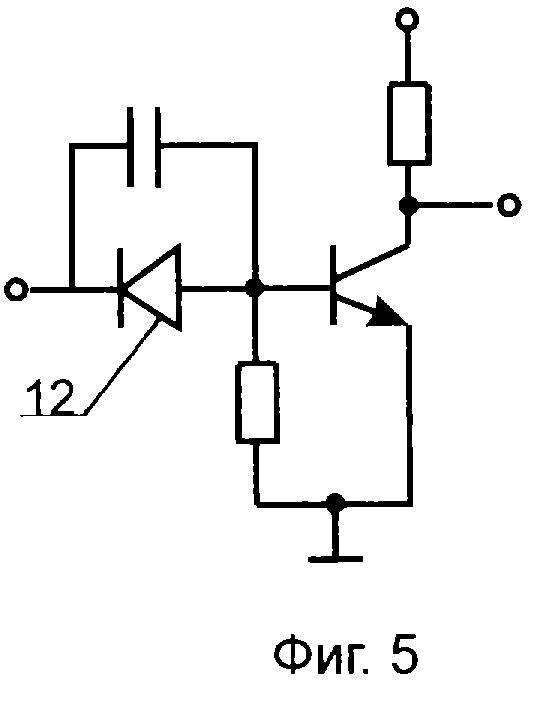

на фиг. 5 показана схема ДЯП с диодом в качестве конденсатора.

Схема ДЯП показана на фигуре 1, она содержит биополярный транзистор-1, коллектор которого подключен через резистор-2 к шине питания-3, подсоединен и к выходной шине-4, база через конденсатор-5 к входной шине-6 и через дополнительный резистор-7 к общей шине-8.

На фиг. 2 показана схема ДЯП со вторым дополнительным резистором-9 в эмиттере.

На фиг. 3 показана схема ДЯП с дополнительным источником питания-10.

На фиг. 4 показана схема ДЯП с дополнительным резистором в базе-11.

На фиг. 5 показана схема ДЯП с диодом-12 в качестве конденсатора.

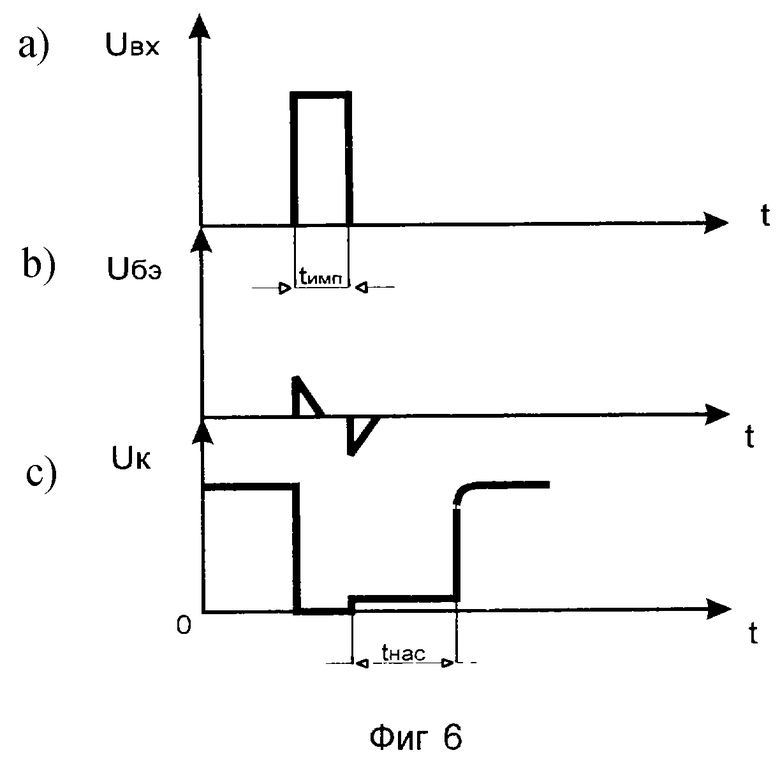

Динамическая ячейка памяти (см. фиг. 1) работает следующим образом. При поступлении положительного входного импульса (Uвх) на входную шину-6, как это показано на фиг. 6a, происходит его дифференциация с помощью R-C-цепочки, образованной элементами 5 и 7 соответственно. В результате получаются два коротких импульса на базе транзистора (Uбэ) (см. фиг. 6b).

При этом положительный импульс открывает биполярный транзистор-1, находящейся до этого в закрытом состоянии, причем время открытого состояния превышает время действия входного импульса (tим ) на величину времени насыщения (tнас), как это видно из фиг. 6c.

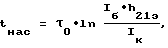

Как известно, tнас примерно определяется соотношением

где τo - время жизни неосновных носителей заряда в транзисторе;

Iб,Iк - токи базы и коллектора соответственно;

h21э - коэффициент усиления тока в схеме в общим эмиттером.

Таким образом, длинная динамическая ячейка памяти будет "помнить" входной импульс в течение времени tнас, после чего требуется его повторение (регенерация). Время хранения информация в данном случае, как и в прототипе [2] , определяется временем рекомбинации неосновных носителей заряда, а не временем релаксации, как МДП-конденсаторной динамической ячейки [1].

Более высокое быстродействие предлагаемой ДЯП по сравнению с аналогами [1,2] очевидно и следует из того, что:

в первом случае используется МОП транзистор, имеющий высокое внутренне сопротивление по сравнению с биполярным, что дает большую постоянную времени с емкостью разрядной шины при малой величине заряда в информационном конденсаторе;

во втором случае быстродействие ДЯП определяется в основном "раскачкой" шины, которая представляет собой значительную емкость, вследствие чего в реальных СБИС ОЗУ тактовая частота обычно не превосходит 200 МГц.

Однако более важным является большая надежность работы в предлагаемой изобретении, т. к. существенное несовпадение тактовой частоты с величиной Tнас в ДЯП может привести к потери ее работоспособности.

Схемы, показанные на фиг. 2, 3, 4, имеют целью дальнейшее повышение быстродействие ДЯП за счет уменьшения глубины насыщения транзистора в схеме на фиг. 3 за счет использования сопротивления отрицательной обратной связи-9, в схеме на фиг. 3 за счет дополнительного источника питания-10, в схеме на фиг. 4 за счет базового сопротивления-11.

Схема, показанная на фиг. 5, показывает, что ДЯП способна функционировать при конструктивной реализации конденсатора дифференцирующей цепочке на основе p-n перехода, что значительно упрощает технологию изготовления ДЯП, которая в этом случае является стандартной.

Автором был изготовлен опытный макет динамического запоминающего устройства (ДОЗУ) состоящего из 12 ячеек ДЯП. Каждая ячейка содержала дискретные элементы схемы: транзистор - КТ-315, резисторы ОМЛТ-l кОм±10%, конденсатор K4D9-100пФ.

Устройство показало свою работоспособность в необычайно широком диапазоне изменения параметров элементов схемы:

- сопротивления-7- в базе транзистора в диапазоне 1 кОм - 10 МОм

- емкости-5- в диапазоне 10 пФ - 200 пФ при значениях емкости эмитерного и коллекторного переходов транзистора КТ-315-6 пФ и 8 пФ соответственно.

- резисторе-2- в коллекторе в диапазоне от 1 кОм до 10 МОм

- температурном диапазоне от -90oC до +250oC

- изменении времени жизни неосновных носителей заряда от ~0,5 нс - 10 мкс

- коэффициента усиления R21э=10 - 300

- питающего напряжения от 3,5 - 10 В.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКОЕ ПОСЛЕДОВАТЕЛЬНОЕ ФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО | 2005 |

|

RU2392672C2 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| КООРДИНАТНО-ЧУВСТВИТЕЛЬНЫЙ ДЕТЕКТОР (ВАРИАНТЫ) | 1998 |

|

RU2133524C1 |

| Долговременный запоминающий элемент | 1978 |

|

SU680054A1 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ИНТЕГРАЛЬНАЯ ТРАНЗИСТОРНАЯ MOS СТРУКТУРА | 2001 |

|

RU2207662C1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| Устройство для программирования дешифратора | 1987 |

|

SU1531165A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| КООРДИНАТНЫЙ ДЕТЕКТОР РЕЛЯТИВИСТСКИХ ЧАСТИЦ | 2000 |

|

RU2197036C2 |

Изобретение "Динамическая ячейка" относится к области электроники и может быть использовано, в частности, при создании оперативных и постоянных запоминающих устройств с повышенным быстродействием. В данной ячейке применен асинхронный принцип записи и отсутствуют тактовые сигналы, что повышает надежность ее работы в динамических оперативных запоминающих устройствах и обеспечивает достигаемый технический результат. Изобретение может быть использовано и в других дискретных логических устройствах. Ячейка содержит биполярный транзистор, два резистора и конденсатор. 6 ил.

Динамическая ячейка памяти, содержащая общую и входную шины и транзистор, отличающаяся тем, что транзистор выполнен биполярным, его коллектор подключен к выходной шине и через резистор к шине питания, эмиттер подключен к общей шине, а база подключена через другой резистор к общей шине и через конденсатор к входной шине, причем время хранения информации определяется временем рекомбинации неосновных носителей заряда, при котором

где tнас - время насыщения;

τ0 - время жизни неосновных носителей;

Iк, Iб - токи коллектора и базы соответственно;

h21э - коэффициент усиления тока в схеме с общим эмиттером.

| Полупроводниковые запоминающие устройства и их применение | |||

| /Под ред | |||

| А.Ю.Гордонова | |||

| - М.: Радио и связь, 1981, с | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| 0 |

|

SU242964A1 | |

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Советское радио, 1975, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Хоровиц П | |||

| и др | |||

| Искусство схемотехники | |||

| Т | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| - М.: Мир, 1973, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

Авторы

Даты

2000-04-20—Публикация

1997-06-11—Подача