Предлагаемое изобретение относится к технике автоматического управления, в частности к технике формирования управляющих сигналов, и может быть использовано, например, в резервированных системах управления космическими летательными аппаратами.

Известен релейный регулятор [1], содержащий аналого-цифровой преобразователь (АЦП), запоминающее устройство (ЗУ), цифровой компаратор, генератор импульсов, соединенный своим выходом с входом счетчика импульсов, триггер и мультиплексор, выходы которого подключены соответственно к шинам положительного и отрицательного управляющего сигнала. Этот регулятор не вносит запаздывания в систему управления и не уменьшает область устойчивости.

Недостаток этого регулятора состоит в том, что он не обладает достаточной надежностью. Так, при одном отказе какого-либо элемента релейный регулятор не обеспечивает выполнение своих функций, а система управления теряет свою работоспособность.

Наиболее близким техническим решением к релейному регулятору является устройство [2], содержащее (2m+1) (m=1, 2, …) канал, а в каждом канале аналого-цифровой преобразователь (АЦП), запоминающее устройство (ЗУ), цифровой компаратор, генератор импульсов, соединенный своим выходом с входом счетчика импульсов, элемент исключающее ИЛИ, первый и второй мажоритарные элементы, элемент ИЛИ, триггер и мультиплексор, выходы которого подключены соответственно к шинам положительного и отрицательного управляющего сигнала.

Недостаток этого релейного регулятора состоит в том, что при некоторых единичных отказах в одном из каналов он может формировать ложный выходной сигнал, определяемый характеристиками отказавшего канала, а при поступлении на вход каждого канала различных по величине сигналов известный регулятор при отсутствии отказов не обеспечивает функционирование, соответствующее формированию управляющего сигнала согласно изменению среднего по величине из всех входных сигналов.

Задача изобретения - повышение надежности релейного регулятора.

Эта задача достигается тем, что в релейный регулятор, содержащий (2m+1) (m=1, 2, …) канал, а в каждом канале аналого-цифровой преобразователь (АЦП), запоминающее устройство (ЗУ), цифровой компаратор, генератор импульсов, соединенный своим выходом с входом счетчика импульсов, триггер, первый элемент исключающее ИЛИ, первый и второй мажоритарные элементы, первый элемент ИЛИ, выход которого соединен с R-входом счетчика импульсов, вход АЦП соединен с входом релейного регулятора, а выходы регистра данных АЦП соединены с соответствующими входами регистра адреса ЗУ, выходы регистра данных которого соединены с соответствующими входами регистра первого сравниваемого числа цифрового компаратора, входы регистра второго сравниваемого числа которого соединены с соответствующими выходами счетчика импульсов, первый вход первого элемента исключающее ИЛИ соединен с выходом первого мажоритарного элемента, в каждый канал дополнительно введены второй, третий и четвертый элементы ИЛИ, второй элемент исключающее ИЛИ, одновибратор, инвертор, первый и второй элементы И, первые входы которых соединены с выходом триггера, выход первого элемента И соединен с первым входом первого мажоритарного элемента, вторым входом первого элемента исключающее ИЛИ и соответствующими входами первого мажоритарного элемента других каналов, выход второго элемента И соединен с первым входом второго мажоритарного элемента, вторым входом второго элемента исключающее ИЛИ и соответствующими входами второго мажоритарного элемента других каналов, выходы первого и второго элементов исключающее ИЛИ соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом цифрового компаратора, выход второго элемента ИЛИ соединен с входом одновибратора и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом одновибратора, вход триггера подключен к выходу первого элемента ИЛИ, второй вход которого соединен с выходом инвертора, вход которого соединен с выходом знакового разряда регистра данных АЦП и вторым входом второго элемента И, выход первого мажоритарного элемента соединен с шиной положительного управляющего сигнала и первым входом четвертого элемента ИЛИ, выход второго мажоритарного элемента соединен с шиной отрицательного управляющего сигнала, с первым входом второго элемента исключающее ИЛИ и вторым входом четвертого элемента ИЛИ, выход которого соединен с входом старшего разряда регистра адреса ЗУ.

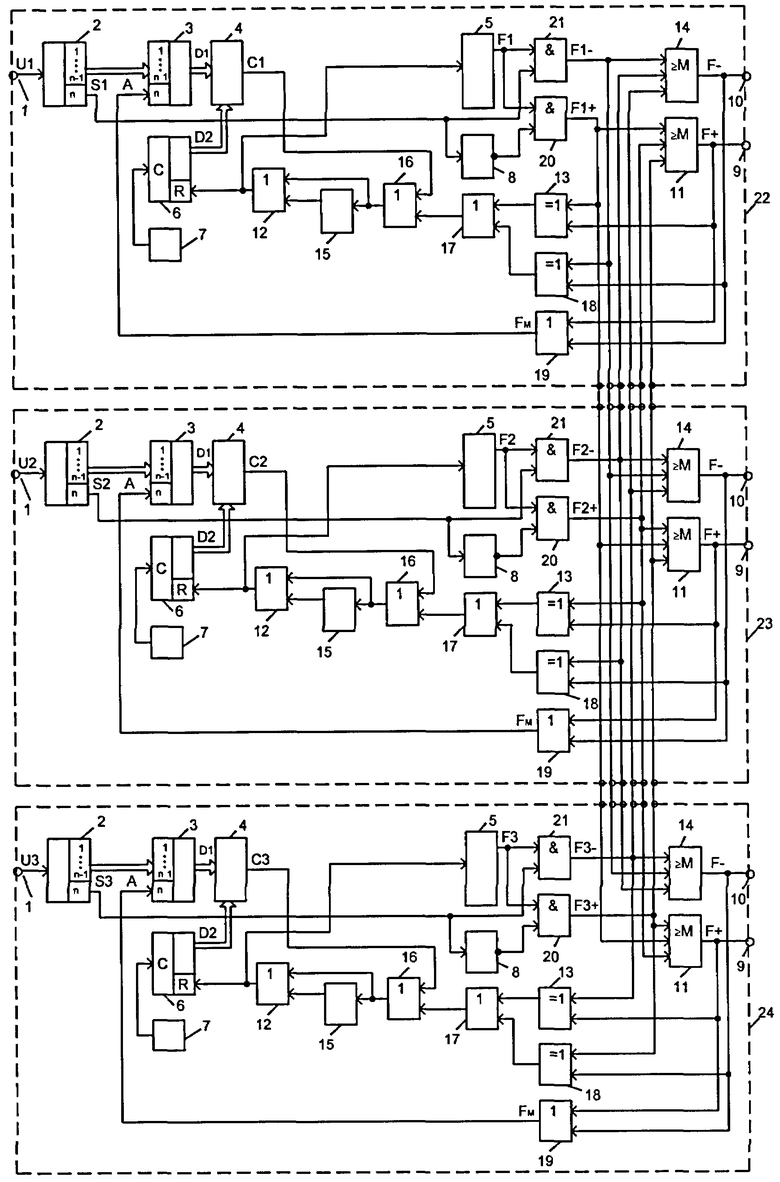

На чертеже: 1 - вход релейного регулятора, 2 - аналого-цифровой преобразователь (АЦП), 3 - запоминающее устройство (ЗУ), 4 - цифровой компаратор, 5 - триггер, 6 - счетчик импульсов, 7 - генератор импульсов, 8 - инвертор, 9 - шина положительного управляющего сигнала, 10 - шина отрицательного управляющего сигнала, 11 - первый мажоритарный элемент, 12 - первый элемент ИЛИ, 13 - первый элемент исключающее ИЛИ, 14 - второй мажоритарный элемент, 15 - одновибратор, 16 - второй элемент ИЛИ, 17 - третий элемент ИЛИ, 18 - второй элемент исключающее ИЛИ, 19 - четвертый элемент ИЛИ, 20 - первый элемент И, 21 - второй элемент И, 22 - первый канал, 23 - второй канал, 24 - (2m+1)-й (m=1,2, …) канал.

В каждом канале вход 1 релейного регулятора соединен с входом АЦП 2, выходы регистра данных которого соединены с соответствующими входами регистра адреса ЗУ 3. Выходы регистра данных ЗУ 3 соединены с соответствующими входами регистра первого сравниваемого числа цифрового компаратора 4, входы регистра второго сравниваемого числа которого соединены с соответствующими выходами счетчика импульсов 6, выход цифрового компаратора 4 соединен со вторым входом второго элемента ИЛИ 16, первый вход которого соединен с выходом третьего элемента ИЛИ 17. Выход второго элемента ИЛИ 16 соединен с входом одновибратора 15 и первым входом первого элемента ИЛИ 12, второй вход которого подключен к выходу одновибратора 15. Выход первого элемента ИЛИ 12 соединен со счетным входом триггера 5 и с R-входом счетчика импульсов 6, вход которого соединен с выходом генератора импульсов 7. Первые входы первого 20 и второго 21 элементов И соединены с выходом триггера 5, выход первого элемента И 20 соединен с первым входом первого мажоритарного элемента 11, вторым входом первого элемента исключающее ИЛИ 13 и соответствующими входами первого мажоритарного элемента 11 других каналов, выход второго элемента И 21 соединен с первым входом второго мажоритарного элемента 14, вторым входом второго элемента исключающее ИЛИ 18 и соответствующими входами второго мажоритарного элемента 14 других каналов. Выход первого мажоритарного элемента 11 соединен с шиной положительного управляющего сигнала 9, первым входом первого элемента исключающее ИЛИ 13 и первым входом четвертого элемента ИЛИ 19, выход второго мажоритарного элемента 14 соединен с шиной отрицательного управляющего сигнала 10, с первым входом второго элемента исключающее ИЛИ 18 и вторым входом четвертого элемента ИЛИ 19. Выходы первого 13 и второго 18 элементов исключающее ИЛИ соединены соответственно с первым и вторым входами третьего элемента ИЛИ 17, второй вход первого элемента И 20 соединен с выходом инвертора 8, вход которого соединен с выходом старшего разряда регистра данных АЦП 2 и вторым входом второго элемента И 21. Выход четвертого элемента ИЛИ 19 соединен с входом старшего разряда регистра адреса ЗУ3.

Релейный регулятор работает следующим образом. Для простоты будем рассматривать трехканальный релейный регулятор (m=1). Пусть на входы 1 каждого канала релейного регулятора подаются соответственно входные сигналы U1, U2, U3. Эти сигналы поступают на вход АЦП 2 соответственно первого 22, второго 23 и третьего 24 каналов и преобразуются в n-разрядный код, который фиксируется в регистре данных АЦП 2 соответствующего канала. В этих регистрах n-й разряд определяет знак входного сигнала, а разряды с 1 по (n-1) - значение (модуль) Ai (i=1, 2, 3) соответствующего входного сигнала Ui. Если Δt - время преобразования АЦП, то в течение этого времени состояние регистра данных АЦП 2 остается неизменным. Код числа Ai поступает на регистр адреса ЗУ 3, на старший n-й разряд которого подается выходной сигнал четвертого элемента ИЛИ 19. Состояние четвертого элемента ИЛИ 19 определяет на данный момент времени tk=kΔt (k=1, 2, …) формирование длительности τд или паузы τп выходного управляющего сигнала.

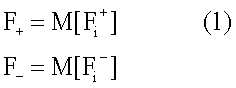

Будем предполагать, если входной сигнал U1>0, то знаковый разряд регистра данных АЦП 2 находится в нулевом состоянии и его выходной сигнал Si=0. Если входной сигнал U1<0, то знаковый разряд регистра данных АЦП 2 находится в единичном состоянии и его выходной сигнал Si=1. Если Fi - выходной сигнал триггера 5, то выходные сигналы Fi + первого элемента И 20 и Fi - второго элемента И 21 будут определяться равенствами

Fi +=0, если Fi=0 или Fi=1 и Si=1,

Fi +=1, если Fi=1 и Si=0,

Fi -=0, если Fi=0 или Fi=1 и Si=0,

Fi -=1, если F1=1 и Si=1.

Эти равенства непосредственно следуют из анализа схемы на чертеже. При Si=0 открыт первый элемент И 20 (выходной сигнал первого инвертора 8 равен единице), при Si=1 открыт второй элемент И 21.

Связь между выходным сигналом F+ первого мажоритарного элемента 11 и выходными сигналами Fi + первого элемента И 20 и между выходным сигналом F- второго мажоритарного элемента 14 и выходными сигналами Fi - второго элемента И 21 всех каналов определяется соотношением (1)

где функция М означает мажоритарный выбор значения большинства (m+1) функций Fi из возможного числа значений (2m+1).

Если F+=1 или F-=1, то выходной сигнал FM четвертого элемента ИЛИ 19 равен единице, что соответствует формированию длительности τд. Если F+=0 и F-=0, то выходной сигнал FM четвертого элемента ИЛИ 19 равен нулю, что соответствует формированию паузы τп.

Если выходной сигнал первого мажоритарного элемента 11 F+=1, то выходной сигнал F+ формируется на шине 9 положительного управляющего сигнала. Если выходной сигнал второго мажоритарного элемента 14 F-=1, то выходной сигнал F- формируется на шине 10 отрицательного управляющего сигнала.

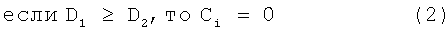

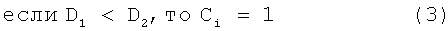

Выходной сигнал Сi цифрового компаратора 4 формируется следующим образом. Если значение числа D1, записанного в регистр первого сравниваемого числа цифрового компаратора 4, больше значения D2, записанного в регистр второго сравниваемого числа, то сигнал Ci=1, или

В запоминающем устройстве 3 каждого канала хранится массив Мτд заданных значений длительности τд и массив Мτп заданных значений паузы τп. Пусть на вход 1 каждого канала поступают близкие по значению входные сигналы соответственно U1, U2, U3, причем U1>U2>U3. Задача релейного регулятора состоит в том, чтобы сформировать выходные управляющие сигналы F+ и F- таким образом, чтобы эти сигналы формировались синхронно в каждом канале, а значения длительности τд и паузы τп выходного управляющего сигнала определялись средним из трех входных сигналов, в рассматриваемом случае сигналом U2. Будем предполагать, что с увеличением сигнала Ui происходит увеличение длительности τд и уменьшение паузы τп управляющего сигнала.

Пусть в некоторый момент времени происходит формирование длительности τд управляющего сигнала. В этом случае F+=1, FM=1, Fi=1, выходные сигналы цифрового компаратора 4, первого 13 и второго 18 элементов исключающее ИЛИ равны нулю. Выходной сигнал первого элемента ИЛИ 12 также равен нулю и на вход счетчика импульсов 6 каждого канала поступают импульсы с генератора 7. В соответствии со сделанным предположением формируемые длительность τд1 и пауза τп1 в первом канале 22, формируемые длительность τд2 и пауза τп2 во втором канале 23 и формируемые длительность τд3 и пауза τп3 в третьем канале 24 связаны соотношением τд1>τд2>τд3, τп1<τп2<τп3. Условия (3) первыми будут выполнены при формировании длительности τд3, т.е. в третьем канале 24. В этом случае выходной сигнал Ci=1 цифрового компаратора 4, проходя через второй элемент ИЛИ 16, одновибратор 15 и первый элемент ИЛИ 12, переводит триггер 5 третьего канала 24 в нулевое состояние и производит обнуление счетчика импульсов 6. Выходной сигнал триггера 5 третьего канала 24 F3=0, а так как согласно (1) F+=1, то выходной сигнал первого элемента исключающее ИЛИ 13 этого канала будет равен единице.

На R-вход счетчика импульсов 6 через третий 17, второй 16 и первый 12 элементы ИЛИ будет подан высокий уровень, что приводит к удержанию счетчика импульсов 6 в нулевом состоянии до тех пор, пока сигнал F+ не станет равным нулю. Это произойдет в тот момент, когда выполнятся условия (3) при формировании длительности τд2, т.е. во втором канале 23. С этого момента времени F2=0 и согласно (1) F+=0. В этот же момент времени выходной сигнал первого мажоритарного элемента 11 первого канала 22 F+=0, выходной сигнал триггера 5 этого канала F1=1 и выходной сигнал первого элемента И 20 Fi +=1. В результате на выходе первого элемента исключающее ИЛИ 13 формируется высокий уровень, который через третий 17, второй 16 и первый 12 элементы ИЛИ подается на вход триггера 5, устанавливая его в нулевое состояние. Таким образом, в момент формирования сигналов F+=0 триггеры 5 переходят в нулевое состояние во всех каналах и сигналы FM=0. В это же время заканчивается формирование длительности импульса τд и начинается формирование паузы τп, т.е. длительность τд управляющего сигнала F+ равна длительности τд2, определяемой сигналом U2.

С момента появления сигнала FM=0 начинается формирование паузы τп управляющего сигнала F+ и с этого момента выходной сигнал первого элемента ИЛИ 12 всех каналов имеет низкий уровень, вследствие чего счетчики импульсов 6 этих каналов начинают воспринимать импульсы генератора 7, формируя тем самым паузу τп управляющего сигнала F+. Условия (3) первыми выполняются для сигнала U1. В этот момент вырабатывается сигнал C1=1 и триггер 5 первого канала 22 переходит в единичное состояние (F1=1) согласно описанному выше алгоритму. Так как F1=1, F+=0, то выходной сигнал первого элемента исключающее ИЛИ 13 этого канала будет равен единице. На R-вход счетчика импульсов 6 будет подан высокий уровень, что приводит к удержанию счетчика импульсов 6 в нулевом состоянии до тех пор, пока сигнал F+ не станет равным единице. Условия (3) вторыми выполняются для сигнала U2. В этот момент вырабатывается сигнал C2=1 и триггер 5 второго канала 23 переходит в единичное состояние (F2=1). Так как сигналы F1=1, F2=1, то согласно (1) F+=1 и релейный регулятор переходит в режим формирования длительности τд управляющего сигнала F+. В момент формирования сигнала FM=1 на выходе первого элемента исключающее ИЛИ 13 третьего канала 24 формируется высокий уровень, который через третий 17, второй 16 и первый 12 элементы ИЛИ подается на вход триггера 5, устанавливая его в единичное состояние. Таким образом, сформированная пауза τп управляющего сигнала F+ определяется сигналом U2 и равна τп2. Итак, в рассматриваемом случае формирование длительности τд и паузы τп управляющего сигнала F+ осуществляется сигналом U2 и производится одновременно во всех каналах.

Аналогично производится формирование длительности τд и паузы τп управляющего сигнала при отрицательных сигналах Ui<0. В этом случае n-й знаковый разряд АЦП 2 переходит в единичное состояние и блокирует формирование сигнала F+. Выходной сигнал F- второго мажоритарного элемента 14 формируется теперь на шине 10 отрицательного управляющего сигнала аналогично описанному выше формированию положительного управляющего сигнала.

Отметим, что в момент начала формирования длительности τд или паузы τп управляющего сигнала триггеры 5 всех каналов устанавливаются в требуемое состояние.

Рассмотрим возможные случаи отказа в каком-либо канале релейного регулятора. При этом релейный регулятор считается исправно работающим, если, по крайней мере, (m+1) канал формируют управляющий сигнал синхронно и в соответствии с изменяющимся входным сигналом Ui. В резервированных системах управление релейными исполнительными органами осуществляется обычно путем формирования обобщенного мажорированного сигнала по правилу (1). В этом случае исправно работающие (m+1) каналы обеспечивают детерминированное управление. Пусть, например, в первом канале 22 отказал триггер 5 и его выходной сигнал F1=1 вне зависимости от его входного сигнала C1. В этом случае при формировании длительности τд (пусть в этот момент времени F2=1, F3=1) сначала формируется сигнал С3=1, переводя триггер 5 третьего канала 24 в нулевое состояние (F3=0), а затем формируется сигнал С2=1, переводя триггер 5 второго канала 23 в нулевое состояние (F2=0). С этого момента времени выходной сигнал второго мажоритарного элемента 14 всех каналов F-=0 и начинается формирование паузы τп управляющего сигнала. В зависимости от соотношения близких по значению сигналов U2 и U3 формируется либо сигнал C2=1, либо сигнал С3=1, переводя либо триггер 5 второго канала 23, либо триггер 5 третьего канала 24 в единичное состояние. С этого момента времени выходной сигнал второго мажоритарного элемента 14 всех каналов F-=1 и начинается формирование длительности τд управляющего сигнала. Таким образом, формирование длительности τд и паузы τп управляющего сигнала осуществляется входным сигналом исправно работающего канала.

При других вариантах отказа в любом канале, например при отказе первого мажоритарного элемента 11 первого канала 22 (постоянно формируется управляющий сигнал F+=1), по крайней мере, два канала из рассматриваемых трех формируют управляющий сигнал, в соответствии с входным сигналом исправно работающих каналов. Таким образом, при любом отказе в одном канале релейного регулятора в случае m=1 работоспособность релейного регулятора не нарушается. При других значениях m работоспособность релейного регулятора не нарушается при отказах в m каналах из (2m+1).

Рассмотрим отказ такого типа, когда в одном из отказавших каналов формирование управляющего сигнала F+ и F- происходит по закону, существенно отличающемуся от заданного (например, вследствие значительного увеличения частоты генератора 7 одного из каналов). В этом случае формируемые длительности τд и паузы τп управляющего сигнала отказавшего канала будут существенно меньше заданных. В предлагаемом регуляторе формирование длительности τд или паузы τп начинается всегда с момента установки триггеров 5 всех каналов в заданное состояние. А это означает, что формирование длительности τд и паузы τп производится по срабатыванию двух каналов из трех, т.е. по срабатыванию исправно работающего канала.

В известном [2] регуляторе формирование длительности τд или паузы τп начинается с момента установки триггеров 5 двух каналов из трех в заданное состояние, а это означает, что в случае рассматриваемого варианта отказа формирование длительности τд и паузы τп производится по сигналам неисправного канала.

Отметим, что известный регулятор [2] при наиболее часто встречающихся отказах типа "обрыв" или "замыкание" обеспечивает заданное функционирование регулятора.

Таким образом, предлагаемый регулятор обеспечивает исправное функционирование при всех возможных видах отказа в любом из каналов.

Рассмотрим теперь работу релейного регулятора в случае поступления на его входы существенно разных по уровню сигналов Ui. Пусть U1>U2>0, U3<0. В этом случае средним является сигнал U2. В рассматриваемом случае будут формироваться сигналы F1 +=1, F2 +=1, F3 -=1, а это означает, что сигнал F- всегда равен нулю, а сигнал F+ формируется сигналами F1 + и F2 +, при этом длительность τд выходного управляющего сигнала F+ определяется меньшим по уровню сигналом, т.е. сигналом U2.

Таким образом, рассматриваемый релейный регулятор формирует управляющий сигнал, закон изменения которого определяется "средним" из множества входных сигналов Ui, что повышает функциональную надежность релейного регулятора.

В известном регуляторе если, например, сигналы U1 и U3 близки по значению, то выходной управляющий сигнал будет определяться одним из этих сигналов, каждый из которых не является "средним" из множества входных сигналов Ui.

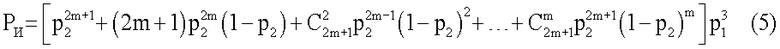

Оценим надежность известного [2] и предлагаемого решения. Пусть надежность одного канала равна p, причем надежность генератора импульсов 7, входящего в состав канала, равна p1, а надежность остальной части схемы этого канала равна p2, при этом p=p1 p2. Надежность Рп предлагаемого решения можно оценить в виде

где C2 2m+1 - число сочетаний из (2m+1) по 2, Cm 2m+1 - число сочетаний из (2m+1) по m.

Надежность Ри известного решения при учете возможной неисправности генератора импульсов можно оценить в виде

Пусть m=1, p1=0,99, p2=0,9. В этом случае из (4) и (5) соответственно имеем Рп=0,967, РИ=0,943. Таким образом, надежность предлагаемого регулятора Рп выше надежности известного регулятора РИ.

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень".

В качестве АЦП, ЗУ, цифрового компаратора могут быть использованы микросхемы типа 1113ПВ1, 556РТ5, 564ИП2, 564КП1. Реализация счетчика, триггера, элементов И, ИЛИ, исключающее ИЛИ хорошо известна (например, 564ИЕ14, 564ТМ2, 564ГГ1).

Литература

1. Патент РФ №2141124, G05В 11/26, 1999 г.

2. Патент РФ №2342690, G05В 11/26, 2008 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408045C2 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408046C2 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2007 |

|

RU2342690C1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408914C1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2422870C2 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2401449C1 |

| СПОСОБ ФОРМИРОВАНИЯ УПРАВЛЯЮЩЕГО СИГНАЛА В РЕЛЕЙНЫХ СИСТЕМАХ С ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ И ЗОНОЙ НЕПРЕРЫВНОГО УПРАВЛЕНИЯ И РЕЛЕЙНЫЙ РЕГУЛЯТОР ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2009 |

|

RU2413965C2 |

| СПОСОБ ФОРМИРОВАНИЯ УПРАВЛЯЮЩЕГО СИГНАЛА В РЕЛЕЙНЫХ СИСТЕМАХ И РЕЛЕЙНЫЙ РЕГУЛЯТОР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 1998 |

|

RU2141124C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2072548C1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

Предлагаемое изобретение относится к технике автоматического управления, в частности к технике формирования управляющих сигналов. Техническим результатом является повышение надежности релейного регулятора. Релейный регулятор содержит в каждом из (2m+1) каналов аналого-цифровой преобразователь (АЦП), запоминающее устройство (ЗУ), цифровой компаратор, генератор импульсов, счетчик импульсов, триггер, мультиплексор, первый и второй мажоритарные элементы, одновибратор, инвертор, первый, второй, третий и четвертый элементы ИЛИ и первый и второй элементы исключающее ИЛИ. Заданные параметры длительности τд и паузы τп управляющего сигнала как функции входного сигнала записаны в запоминающем устройстве и благодаря непрерывному сравнению фактических величин с заданными релейный регулятор не вносит запаздывания в систему управления, а благодаря определенным связям достигается исправное функционирование релейного регулятора при отказах в m каналах регулятора и заданное функционирование, соответствующее формированию управляющего сигнала согласно изменению среднего по величине из всех входных сигналов. Предлагаемый релейный регулятор может быть использован в различных системах управления, в частности в системах управления космическими аппаратами. 1 ил.

Релейный регулятор, содержащий (2m+1) (m=1, 2, …) канал, а в каждом канале аналого-цифровой преобразователь (АЦП), запоминающее устройство (ЗУ), цифровой компаратор, генератор импульсов, соединенный своим выходом с входом счетчика импульсов, триггер, первый элемент исключающее ИЛИ, первый и второй мажоритарные элементы, первый элемент ИЛИ, выход которого соединен с R-входом счетчика импульсов, вход АЦП соединен с входом релейного регулятора, а выходы регистра данных АЦП соединены с соответствующими входами регистра адреса ЗУ, выходы регистра данных которого соединены с соответствующими входами регистра первого сравниваемого числа цифрового компаратора, входы регистра второго сравниваемого числа которого соединены с соответствующими выходами счетчика импульсов, первый вход первого элемента исключающее ИЛИ соединен с выходом первого мажоритарного элемента, отличающийся тем, что в каждый канал дополнительно введены второй, третий и четвертый элементы ИЛИ, второй элемент исключающее ИЛИ, одновибратор, инвертор, первый и второй элементы И, первые входы которых соединены с выходом триггера, выход первого элемента И соединен с первым входом первого мажоритарного элемента, вторым входом первого элемента исключающее ИЛИ и соответствующими входами первого мажоритарного элемента других каналов, выход второго элемента И соединен с первым входом второго мажоритарного элемента, вторым входом второго элемента исключающее ИЛИ и соответствующими входами второго мажоритарного элемента других каналов, выходы первого и второго элементов исключающее ИЛИ соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом цифрового компаратора, выход второго элемента ИЛИ соединен с входом одновибратора и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом одновибратора, вход триггера подключен к выходу первого элемента ИЛИ, второй вход которого соединен с выходом инвертора, вход которого соединен с выходом знакового разряда регистра данных АЦП и вторым входом второго элемента И, выход первого мажоритарного элемента соединен с шиной положительного управляющего сигнала и первым входом четвертого элемента ИЛИ, выход второго мажоритарного элемента соединен с шиной отрицательного управляющего сигнала, с первым входом второго элемента исключающее ИЛИ и вторым входом четвертого элемента ИЛИ, выход которого соединен с входом старшего разряда регистра адреса ЗУ.

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2007 |

|

RU2342690C1 |

| СПОСОБ ФОРМИРОВАНИЯ УПРАВЛЯЮЩЕГО СИГНАЛА В РЕЛЕЙНЫХ СИСТЕМАХ И РЕЛЕЙНЫЙ РЕГУЛЯТОР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 1998 |

|

RU2141124C1 |

| US 3691452, 12.09.1972. | |||

Авторы

Даты

2011-01-20—Публикация

2009-05-25—Подача