Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя), в структуре входных каскадов аналоговых микросхем различного функционального назначения, например операционных усилителях.

Одним из классических вариантов построения буферных усилителей являются схемы так называемых «бриллиантовых» транзисторов, которые стали основой современных аналоговых микросхем [1-22]. Предлагаемое изобретение относится к данному классу устройств.

Ближайшим прототипом заявляемого устройства является буферный усилитель, представленный в патенте США №5.557.238 fig 6. Эта архитектура присутствует в большем числе других патентов [1-22].

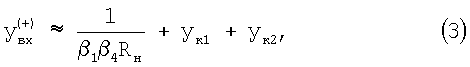

Существенный недостаток известного буферного усилителя (БУ) (фиг.1) состоит в том, что он не обеспечивает широкий диапазон линейного усиления входных сигналов при низкоомной нагрузке (например Rн=50 Ом) и малом собственном токопотреблении в статическом режиме.

Основная цель предлагаемого изобретения состоит в повышении максимально возможного тока в низкоомной нагрузке 1н.max при малых значениях токов, потребляемых от источников питания в статическом режиме. В конечном итоге это расширяет диапазон линейной работы устройства.

Дополнительная цель - повышение входного сопротивления (Rвx) устройства при малых сопротивлениях нагрузки (Rн=50 Ом), а также предельных значений Rвx при Rн=∞.

Поставленная цель достигается тем, что в буферном усилителе, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу 3 устройства, эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора и коллектором транзистора 5 первого управляемого источника тока, эмиттер второго 2 входного транзистора подключен к базе второго 6 выходного транзистора и коллектору транзистора 7 второго управляемого источника тока, причем эмиттеры первого 4 и второго 6 выходных транзисторов связаны с выходом 8 устройства, предусмотрены новые элементы и связи - в схему введены первый 9 и второй 10 дополнительные транзисторы, базы которых подключены к выходу 8 устройства, коллектор первого 9 дополнительного транзистора соединен с базой транзистора 5 первого управляемого источника тока, эмиттер первого дополнительного транзистора 9 связан с коллектором первого 1 входного транзистора и первым 11 дополнительным токостабилизирующим двухполюсником, коллектор второго 10 дополнительного транзистора подключен к базе транзистора 7 второго управляемого источника тока, а эмиттер второго 10 дополнительного транзистора связан с коллектором второго 2 входного транзистора и вторым 12 дополнительным токостабилизирующим двухполюсником.

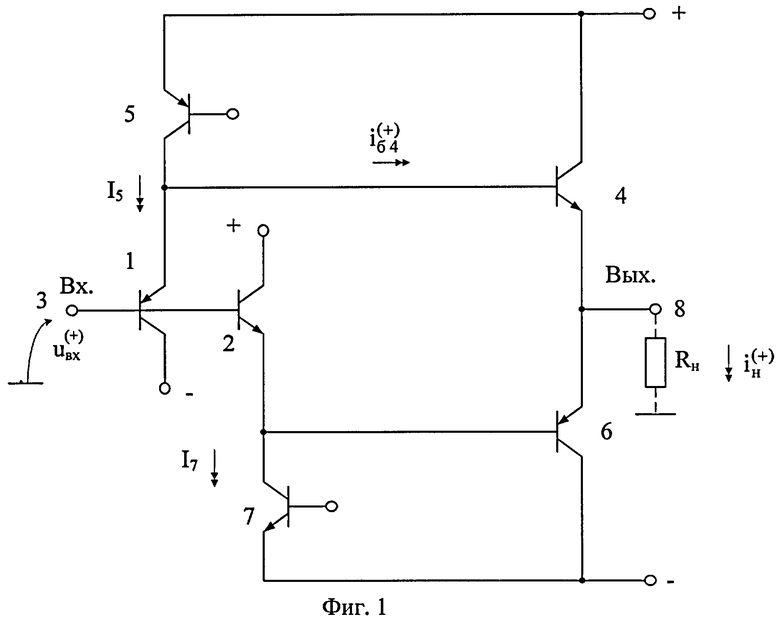

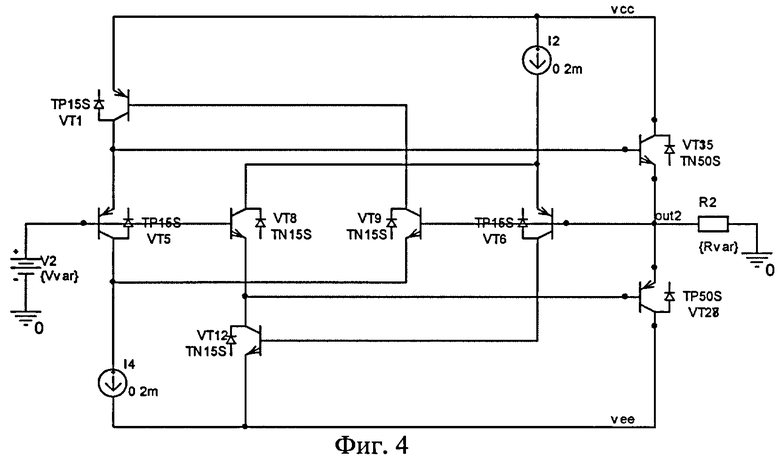

На фиг.2 приведена схема заявляемого устройства в соответствии с формулой изобретения. На фиг.3 и фиг.4 показаны схемы БУ прототипа (фиг.3) и заявляемого устройства (фиг.4) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП HПП "Пульсар".

Проходные характеристики сравниваемых БУ фиг.3 и фиг.4 при сопротивлении нагрузки Rн=50 Ом и одинаковом (достаточно малом собственном токопотреблении в статическом режиме Iпот=0,6 мА) показаны на фиг.5.

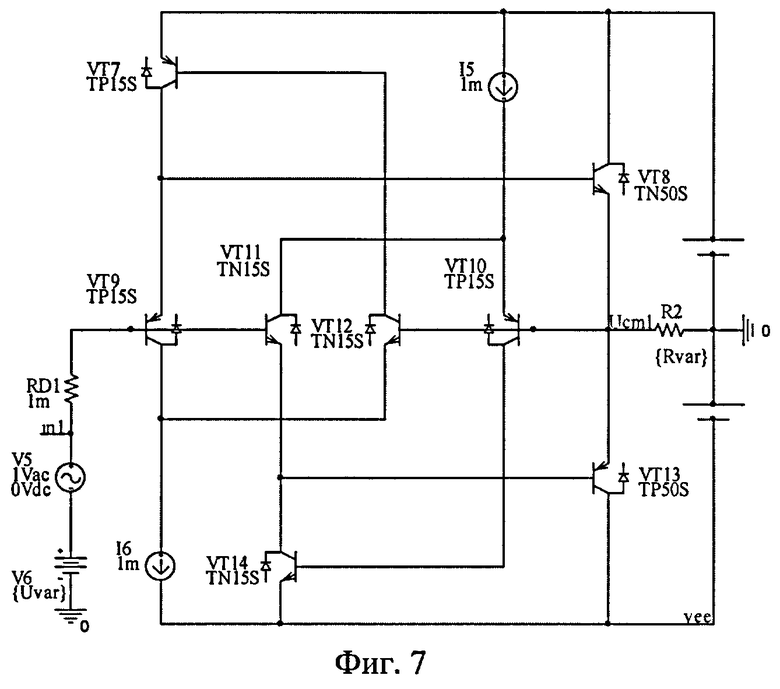

На фиг.6 и фиг.7 представлены соответственно схемы известного и заявляемого устройства в среде PaSpice на моделях интегральных транзисторов ФГУП HПП «Пульсар» для измерения их входных дифференциальных сопротивлений (Rвx).

На фиг.8 приведены графики частотной зависимости входных сопротивлений сравниваемых схем фиг.6 и фиг.7 при сопротивлении нагрузки Rн=50 Ом и изменении постоянной составляющей входного напряжения в пределах 0÷0,8 В.

Буферный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу 3 устройства, эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора и коллектором транзистора 5 первого управляемого источника тока, эмиттер второго 2 входного транзистора подключен к базе второго 6 выходного транзистора и коллектору транзистора 7 второго управляемого источника тока, причем эмиттеры первого 4 и второго 6 выходных транзисторов связаны с выходом 8 устройства. В схему введены первый 9 и второй 10 дополнительные транзисторы, базы которых подключены к выходу 8 устройства, коллектор первого 9 дополнительного транзистора соединен с базой транзистора 5 первого управляемого источника тока, эмиттер первого дополнительного транзистора 9 связан с коллектором первого 1 входного транзистора и первым 11 дополнительным токостабилизирующим двухполюсником, коллектор второго 10 дополнительного транзистора подключен к базе транзистора 7 второго управляемого источника тока, а эмиттер второго 10 дополнительного транзистора связан с коллектором второго 2 входного транзистора и вторым 12 дополнительным токостабилизирующим двухполюсником.

Рассмотрим работу буферных усилителей фиг.1 и фиг.2.

При  максимально возможный ток в нагрузке БУ фиг.1 (

максимально возможный ток в нагрузке БУ фиг.1 ( ) и максимальное выходное напряжение

) и максимальное выходное напряжение  зависят от статического тока эмиттера транзистора 1 (Iэ1=I5) и коэффициента усиления по току базы (β4) транзистора 4:

зависят от статического тока эмиттера транзистора 1 (Iэ1=I5) и коэффициента усиления по току базы (β4) транзистора 4:

При этом в режиме большого сигнала входная проводимость БУ фиг.1 имеет три составляющих:

где βi - коэффициент усиления по току базы i-го транзистора;

ук1, ук2 - проводимость коллектор-база транзисторов 1 и 2.

В заявляемом БУ фиг.2 положительное приращение напряжения  на входе 3 передастся практически с единичным коэффициентом на базу транзистора 4, что приводит к появлению тока базы

на входе 3 передастся практически с единичным коэффициентом на базу транзистора 4, что приводит к появлению тока базы  и тока нагрузки

и тока нагрузки  :

:

или

Ток базы транзистора 4 складывается из двух составляющих

Следует заметить, что максимально возможное значение коллекторного тока транзистора 5 зависит от статического тока (I11) двухполюсника 11

Поэтому максимально возможный ток базы  и максимально возможные значения выходного напряжения

и максимально возможные значения выходного напряжения  которого проходная характеристика БУ линейна, определяются формулами

которого проходная характеристика БУ линейна, определяются формулами

Сравнивая (9) и (2) можно сделать вывод о том, что предлагаемый БУ при идентичном токопотреблении в статическом режиме (I11=I12=I5=I7) имеет в β5 раз более высокие уровни максимального тока в нагрузке и характеризуется в β5 раз более широким диапазоном линейной работы при низкоомных нагрузках (Rн=20÷50 Ом). Данные выводы подтверждаются результатами компьютерного моделирования сравниваемых схем (фиг.5).

Замечательная особенность предлагаемого БУ состоит в том, что максимально возможная амплитуда его выходного напряжения  при Rн=∞ отличается от напряжения питания

при Rн=∞ отличается от напряжения питания  не более чем на 1÷1,2 В. Это весьма существенное достоинство схемы при малых

не более чем на 1÷1,2 В. Это весьма существенное достоинство схемы при малых  .

.

Кроме этого, заявляемый БУ имеет более высокие значения входного сопротивления Rвх=у-1 вх, т.к. его входная проводимость

где Ky1, Ку2 - коэффициенты передачи входного напряжения  в коллекторные цепи транзисторов 1 и 2;

в коллекторные цепи транзисторов 1 и 2;

Таким образом, в схеме фиг.2 при низкоомной нагрузке Rн входное сопротивление в β5-раз выше, чем в схеме фиг.1.

Если Rн=∞, то предельное значение Rвх в схеме фиг.2 на один-два порядка выше, чем в схеме фиг.1

,

,

где rк1, rк2 - сопротивления коллекторных переходов первого 1 и второго 2 входных транзисторов. Данные выводы подтверждены графиками фиг.8, из которых следует, что предлагаемая схема БУ имеет более чем в 30 раз лучшие значения входных сопротивлений.

Таким образом, заявляемое устройство характеризуется более высокими качественными показателями.

Литература

1. Патент США №6.268.769, fig.3.

2. Патент США №6.420.933.

3. Патент США №5.223.122.

4. Патентная заявка США №2004/0196101.

5. Патентная заявка США №2005/0264358, fig.1.

6. Патентная заявка США №2002/0175759.

7. Патент США №5.049.653, fig.8.

8. Патент США №4.837.523.

9. Патент США №5.179.355.

10. Патент Японии JP 10.163.763.

11. Патент Японии JP 10.270.954.

12. Патент США №5.170.134, fig.6.

13. Патент США №4.540.950.

14. Патент США №4.424.493.

15. Патент Японии JP 6310950.

16. Патент США №5.378.938.

17. Патент США №4.827.223.

18. Патент США №6.160.451.

19. Патент США №4.639.685.

20. А.св. СССР 1506512.

21. Патент США №5.399.991.

22. Патент США №6.542.032.

| название | год | авторы | номер документа |

|---|---|---|---|

| БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2401509C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2446553C1 |

| КОМПЛЕМЕНТАРНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444115C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА n-p-n БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786630C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| РАДИАЦИОННО-СТОЙКИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393625C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416152C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416155C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности, в структуре входных каскадов аналоговых микросхем различного функционального назначения. Буферный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), базы которых подключены ко входу (3) устройства, эмиттер первого Т(1) соединен с базой первого выходного Т(4) и коллектором Т(5) первого управляемого источника тока (УИТ), эмиттер второго входного Т(2) подключен к базе второго выходного Т(6) и коллектору Т(7) второго УИТ, причем эмиттеры Т(4) и Т(6) связаны с выходом (8) устройства. В схему введены первый Т(9) и второй Т(10), базы которых подключены к выходу (8) устройства, коллектор Т(9) соединен с базой Т(5) первого УИТ, эмиттер Т(9) связан с коллектором Т(1) и первым (11) дополнительным токостабилизирующим двухполюсником, коллектор Т (10) подключен к базе Т(7) второго УИТ, а эмиттер Т(10) связан с коллектором Т(2) и вторым (12) дополнительным токостабилизирующим двухполюсником. 8 ил.

Буферный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены ко входу (3) устройства, эмиттер первого (1) входного транзистора соединен с базой первого (4) выходного транзистора и коллектором транзистора (5) первого управляемого источника тока, эмиттер второго (2) входного транзистора подключен к базе второго (6) выходного транзистора и коллектору транзистора (7) второго управляемого источника тока, причем эмиттеры первого (4) и второго (6) выходных транзисторов связаны с выходом (8) устройства, отличающийся тем, что в схему введены первый (9) и второй (10) дополнительные транзисторы, базы которых подключены к выходу (8) устройства, коллектор первого (9) дополнительного транзистора соединен с базой транзистора (5) первого управляемого источника тока, эмиттер первого дополнительного транзистора (9) связан с коллектором первого (1) входного транзистора и первым (11) дополнительным токостабилизирующим двухполюсником, коллектор второго (10) дополнительного транзистора подключен к базе транзистора (7) второго управляемого источника тока, а эмиттер второго (10) дополнительного транзистора связан с коллектором второго (2) входного транзистора и вторым (12) дополнительным токостабилизирующим двухполюсником.

| US 5557238 А, 17.09.1996 | |||

| Двухтактный усилитель мощности | 1982 |

|

SU1113877A1 |

| СТЕНД ДЛЯ ПОДБОРА РАЗМЕРА ОТВЕРСТИЯ ПОД ПРОТИВОВЗРЫВНУЮ ПАНЕЛЬ | 2015 |

|

RU2646973C2 |

| US 6535063 B1, 18.03.2003. | |||

Авторы

Даты

2011-01-20—Публикация

2009-06-19—Подача