Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя), в структуре входных каскадов аналоговых микросхем различного функционального назначения, например операционных усилителях.

Одним из классических вариантов построения буферных усилителей (БУ) являются схемы так называемых «бриллиантовых» транзисторов, которые стали основой современных аналоговых микросхем [1-22]. Предполагаемое изобретение относится к данному классу устройств.

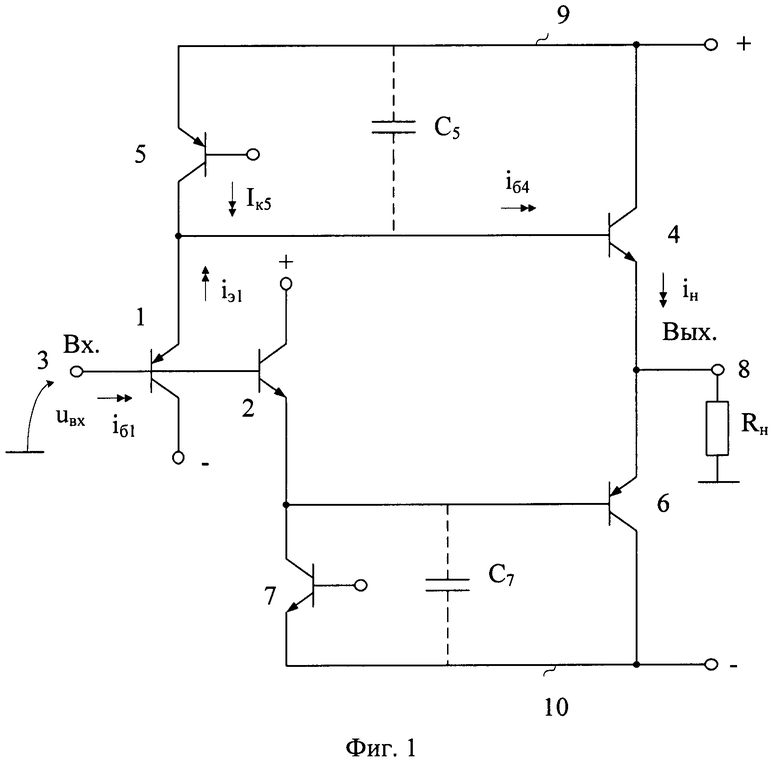

Ближайшим прототипом заявляемого устройства является буферный усилитель, представленный в патенте США №5557238 fig.6. Эта архитектура присутствует в большем числе других патентов [1-22]. Он содержит первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу 3 устройства, эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора и коллектором входного транзистора 5 первого управляемого источника тока, эмиттер второго 2 входного транзистора подключен к базе второго 6 выходного транзистора и коллектору входного транзистора 7 второго управляемого источника тока, причем эмиттеры первого 4 и второго 6 выходных транзисторов соединены с выходом 8 устройства, первый 9 источник напряжения питания, с которым связаны эмиттер входного транзистора 5 управляемого источника тока и коллектор первого 4 выходного транзистора, второй 10 источник напряжения питания, к которому подключены эмиттер входного транзистора 7 второго управляемого источника тока и коллектор второго 6 выходного транзистора.

Существенный недостаток известного буферного усилителя (БУ) состоит в том, что он не обеспечивает широкий диапазон линейного усиления входных сигналов при низкоомной нагрузке (например, Rн=50 Ом) и малом собственном токопотреблении в статическом режиме. Кроме того, известный БУ имеет малую скорость нарастания выходного напряжения (ϑвых), которая связана с величиной емкости на подложку транзисторов, применяемых в качестве цепей установления эмиттерного тока.

Основная задача предполагаемого изобретения состоит в повышении максимально возможного тока в низкоомной нагрузке (Iн.max) при малых значениях токов, потребляемых БУ от источников питания в статическом режиме. В конечном итоге это расширяет диапазон линейной работы устройства.

Первая дополнительная задача - повышение максимальной скорости нарастания выходного напряжения БУ при большом импульсном изменении входного напряжения.

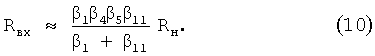

Вторая дополнительная задача - повышение входного сопротивления (Rвх) устройства при малых сопротивлениях нагрузки.

Поставленные задачи достигаются тем, что в буферном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу 3 устройства, эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора и коллектором входного транзистора 5 первого управляемого источника тока, эмиттер второго 2 входного транзистора подключен к базе второго 6 выходного транзистора и коллектору входного транзистора 7 второго управляемого источника тока, причем эмиттеры первого 4 и второго 6 выходных транзисторов соединены с выходом 8 устройства, первый 9 источник напряжения питания, с которым связаны эмиттер входного транзистора 5 управляемого источника тока и коллектор первого 4 выходного транзистора, второй 10 источник напряжения питания, к которому подключены эмиттер входного транзистора 7 второго управляемого источника тока и коллектор второго 6 выходного транзистора, предусмотрены новые элементы и связи - в схему введены первый 11 и второй 12 дополнительные транзисторы, базы которых подключены ко входу 3 устройства, коллектор первого 11 дополнительного транзистора соединен с базой входного транзистора 5 первого управляемого источника тока, а его эмиттер связан с коллектором первого 1 входного транзистора и первым 13 дополнительным токостабилизирующим двухполюсником, коллектор второго 12 дополнительного транзистора подключен к базе входного транзистора 7 второго управляемого источника тока, а его эмиттер связан с коллектором второго 12 входного транзистора и вторым 14 дополнительным токостабилизирующим двухполюсником.

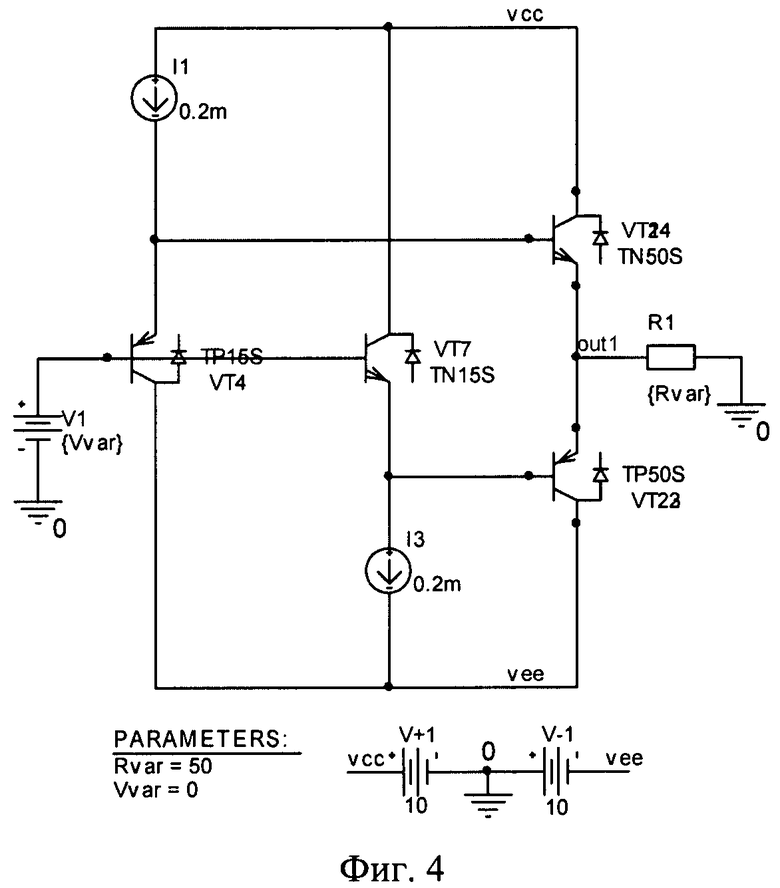

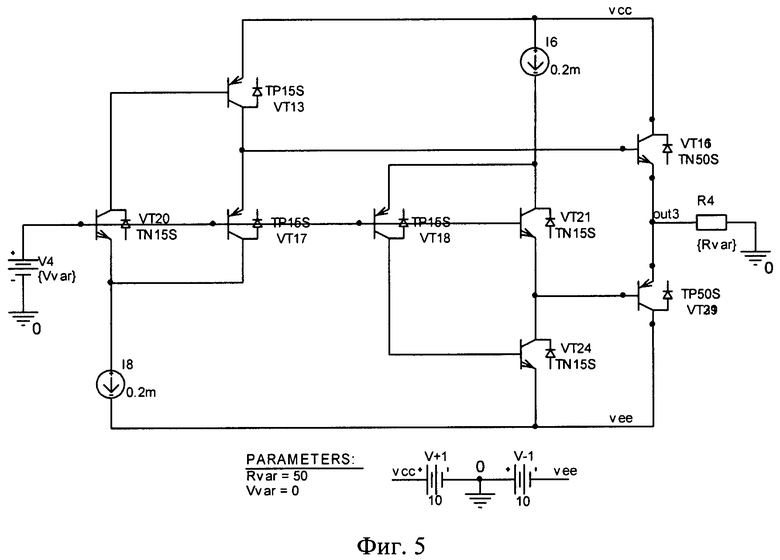

На чертеже фиг.2 приведена схема заявляемого устройства в соответствии с формулой изобретения. На чертеже фиг.3 показана схема фиг.2 для анализа переходных процессов. На чертежах фиг.4 и фиг.5 показаны схемы БУ прототипа (фиг.4) и заявляемого устройства (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар".

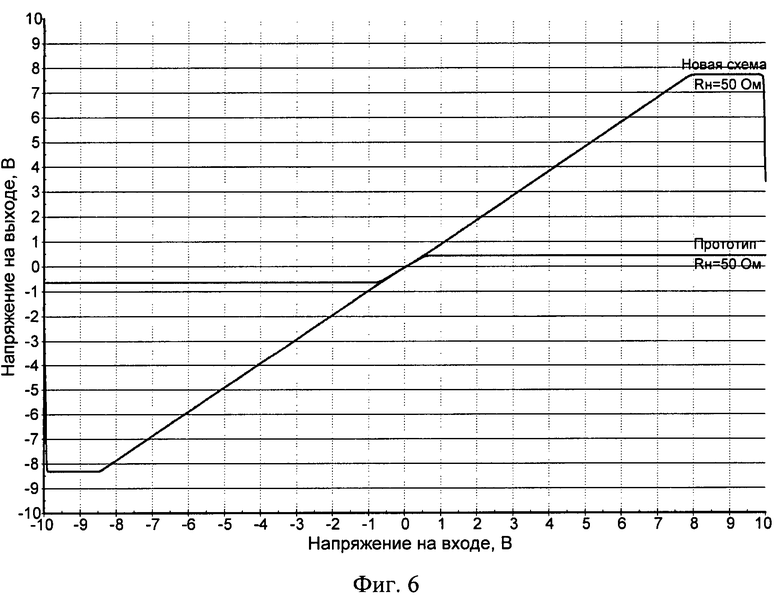

Проходные характеристики сравниваемых БУ фиг.4 и фиг.5 при сопротивлении нагрузки Rн=50 Ом и одинаковом (достаточно малом собственном токопотреблении в статическом режиме Iпот=0,6 мА) показаны на чертеже фиг.6.

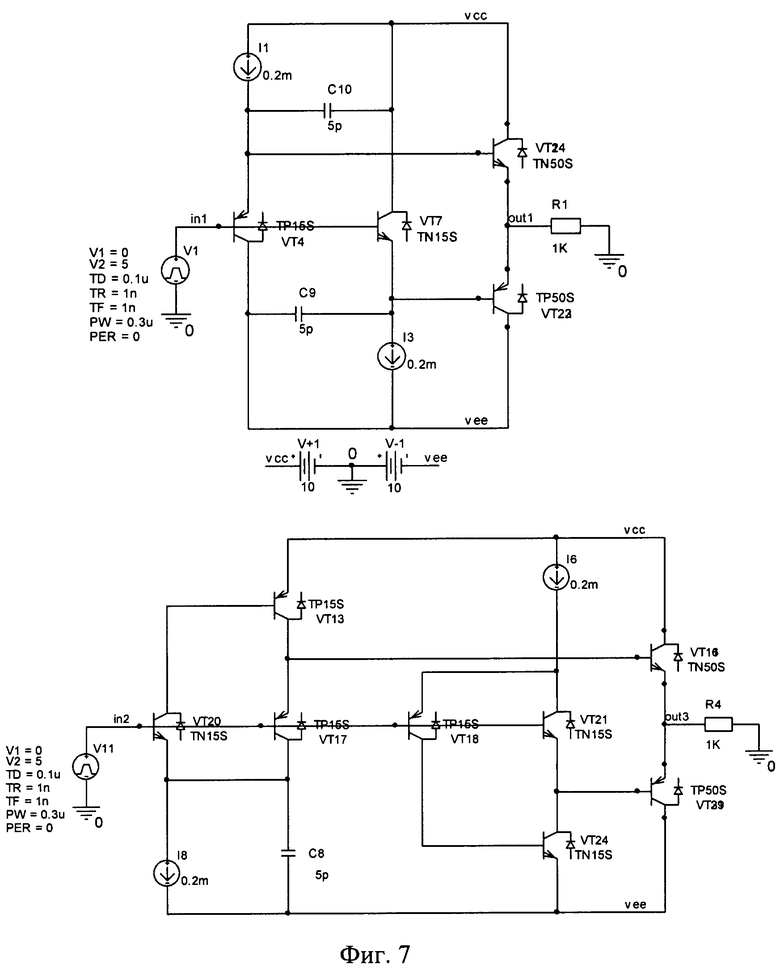

На чертеже фиг.7 представлены схемы известного и заявляемого устройства в среде PaSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для исследования их переходных процессов.

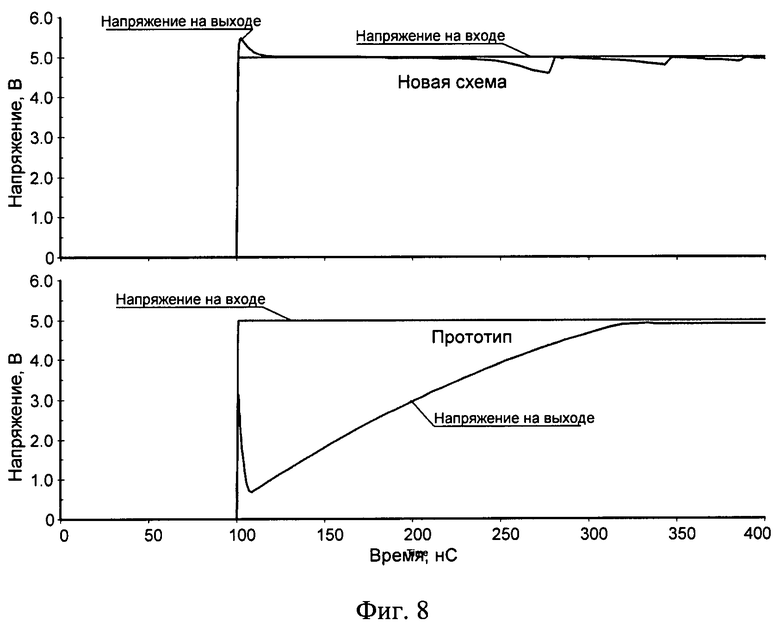

На чертеже фиг.8 приведены графики переходных процессов сравниваемых схем фиг.7 при импульсном изменении входного напряжения.

На чертеже фиг.9 показан переходной процесс фиг.8 в заявляемом устройстве в укрупненном масштабе.

Буферный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу 3 устройства, эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора и коллектором входного транзистора 5 первого управляемого источника тока, эмиттер второго 2 входного транзистора подключен к базе второго 6 выходного транзистора и коллектору входного транзистора 7 второго управляемого источника тока, причем эмиттеры первого 4 и второго 6 выходных транзисторов соединены с выходом 8 устройства, первый 9 источник напряжения питания, с которым связаны эмиттер входного транзистора 5 управляемого источника тока и коллектор первого 4 выходного транзистора, второй 10 источник напряжения питания, к которому подключены эмиттер входного транзистора 7 второго управляемого источника тока и коллектор второго 6 выходного транзистора. В схему введены первый 11 и второй 12 дополнительные транзисторы, базы которых подключены ко входу 3 устройства, коллектор первого 11 дополнительного транзистора соединен с базой входного транзистора 5 первого управляемого источника тока, а его эмиттер связан с коллектором первого 1 входного транзистора и первым 13 дополнительным токостабилизирующим двухполюсником, коллектор второго 12 дополнительного транзистора подключен к базе входного транзистора 7 второго управляемого источника тока, а его эмиттер связан с коллектором второго 12 входного транзистора и вторым 14 дополнительным токостабилизирующим двухполюсником.

В схеме фиг.3 конденсатор 15 моделирует выходную емкость первого 13 дополнительного токостабилизирующего двухполюсника, а конденсатор 16 - эквивалентную емкость в цепи базы транзистора 4.

Рассмотрим работу буферных усилителей фиг.1 и фиг.2.

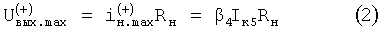

При  максимально возможный ток в нагрузке БУ фиг.1 (

максимально возможный ток в нагрузке БУ фиг.1 ( ) и максимальное выходное напряжение (

) и максимальное выходное напряжение ( ) зависят от статического тока эмиттера транзистора 1 (Iэ1=Iк5) и коэффициента усиления по току базы (β4) транзистора 4:

) зависят от статического тока эмиттера транзистора 1 (Iэ1=Iк5) и коэффициента усиления по току базы (β4) транзистора 4:

При этом в режиме большого сигнала входная проводимость БУ фиг.1:

где βi - коэффициент усиления по току базы i-го транзистора (1 и 4).

В заявляемом БУ фиг.2 положительное приращение напряжения  на входе 3 передается практически с единичным коэффициентом на базу транзистора 4, что приводит к появлению тока базы (

на входе 3 передается практически с единичным коэффициентом на базу транзистора 4, что приводит к появлению тока базы ( ) и тока нагрузки (

) и тока нагрузки ( ):

):

или

Ток базы транзистора 4 складывается из двух составляющих

Следует заметить, что максимально возможное значение коллекторного тока транзистора 5 зависит от статического тока (I13) двухполюсника 13:

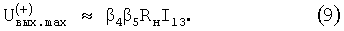

Поэтому максимально возможный ток базы  и максимально возможные значения выходного напряжения

и максимально возможные значения выходного напряжения  , для которого проходная характеристика БУ линейна, определяются формулами

, для которого проходная характеристика БУ линейна, определяются формулами

Сравнивая (9) и (2) можно сделать вывод о том, что предлагаемый БУ при идентичном токопотреблении в статическом режиме (I13=I14=Iк5=Iк7) имеет в β5 раз более высокие уровни максимального тока в нагрузке и характеризуется в β5 раз более широким диапазоном линейной работы при низкоомных нагрузках (Rн=20÷50 Ом). Данные выводы подтверждаются результатами компьютерного моделирования сравниваемых схем (фиг.6).

Замечательная особенность предлагаемого БУ состоит в том, что максимально возможная амплитуда его выходного напряжения  при Rн=∞ отличается от напряжения питания (

при Rн=∞ отличается от напряжения питания ( ) не более чем на 1÷1,2 В. Это весьма существенное достоинство схемы при малых

) не более чем на 1÷1,2 В. Это весьма существенное достоинство схемы при малых  .

.

Кроме того, заявляемый БУ имеет более высокие значения входного сопротивления Rвх:

Таким образом, в схеме фиг.2 при низкоомной нагрузке Rн входное сопротивление в β раз выше, чем в схеме фиг.1.

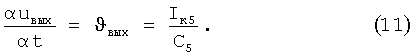

При большом импульсном изменении входного напряжения в БУ фиг.1 ( ) входной транзистор запирается, а эквивалентная емкость C5 в базе транзистора 4 заряжается постоянным по величине коллекторным током транзистора 5 (Iк5). Поэтому максимальная скорость нарастания выходного напряжения БУ фиг.1:

) входной транзистор запирается, а эквивалентная емкость C5 в базе транзистора 4 заряжается постоянным по величине коллекторным током транзистора 5 (Iк5). Поэтому максимальная скорость нарастания выходного напряжения БУ фиг.1:

Например, при Iк5=0,2 мА, C5=5 пФ находим, что ϑвых≈40 В/мксек.

В заявляемом БУ фиг.3 импульсное изменение входного напряжения (uвх>0) вызывает импульсное изменение тока эмиттера транзистора 11 ( ) и, далее, тока базы и тока коллектора транзистора 5:

) и, далее, тока базы и тока коллектора транзистора 5:

Поэтому эквивалентная емкость 16 в цепи базы транзистора 4 заряжается значительно быстрее, что существенно повышает максимальную скорость нарастания выходного напряжения БУ (ϑвых) фиг.3.

Как показывает компьютерное моделирование (фиг.8, фиг.9), ϑвых в схеме фиг.3 значительно (на два порядка) превышает ϑвых БУ-прототипа.

Следует заметить, что качество переходного процесса в схеме фиг.3 зависит от выбора оптимальных значений емкостей конденсаторов 16 и 15.

Таким образом, заявляемое устройство характеризуется более высокими качественными показателями по  , Rвх, ϑвых.

, Rвх, ϑвых.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6268769 fig.3.

2. Патент США №6420933.

3. Патент США №5223122.

4. Патентная заявка США №2004/0196101.

5. Патентная заявка США №2005/0264358 fig.1.

6. Патентная заявка США №2002/0175759.

7. Патент США №5049653 fig.8.

8. Патент США №4837523.

9. Патент США №5179355.

10. Патент Японии JP 10163763.

11. Патент Японии JP 10270954.

12. Патент США №5170134 fig.6.

13. Патент США №4540950.

14. Патент США №4424493.

15. Патент Японии JP 6310950.

16. Патент США №5378938.

17. Патент США №4827223.

18. Патент США №6160451.

19. Патент США №4639685.

20. А.с. СССР 1506512.

21. Патент США №5399991.

22. Патент США №6542032.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2668985C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2401509C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2409889C1 |

| КОМПЛЕМЕНТАРНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444115C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2674885C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩЕЙ ЦЕПЬЮ КОРРЕКЦИИ ПЕРЕХОДНОГО ПРОЦЕССА | 2018 |

|

RU2673003C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2006 |

|

RU2321157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416155C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности буферного усилителя (БУ), в структуре входных каскадов аналоговых микросхем различного функционального назначения, например операционных усилителях. Технический результат: повышение максимально возможного тока в низкоомной нагрузке (Iн.max) при малых значениях токов, потребляемых БУ от источников питания в статическом режиме. В конечном итоге это расширяет диапазон линейной работы устройства. Буферный усилитель содержит первый (1) и второй (2) входные транзисторы, базы которых подключены ко входу (3) устройства, эмиттер первого (1) входного транзистора соединен с базой первого (4) выходного транзистора и коллектором входного транзистора (5) первого управляемого источника тока, эмиттер второго (2) входного транзистора подключен к базе второго (6) выходного транзистора и коллектору входного транзистора (7) второго управляемого источника тока, причем эмиттеры первого (4) и второго (6) выходных транзисторов соединены с выходом (8) устройства, первый (9) источник напряжения питания, с которым связаны эмиттер входного транзистора (5) управляемого источника тока и коллектор первого (4) выходного транзистора, второй (10) источник напряжения питания, к которому подключены эмиттер входного транзистора (7) второго управляемого источника тока и коллектор второго (6) выходного транзистора. В схему введены первый (11) и второй (12) дополнительные транзисторы, базы которых подключены ко входу (3) устройства, коллектор первого (11) дополнительного транзистора соединен с базой входного транзистора (5) первого управляемого источника тока, а его эмиттер связан с коллектором первого (1) входного транзистора и первым (13) дополнительным токостабилизирующим двухполюсником, коллектор второго (12) дополнительного транзистора подключен к базе входного транзистора (7) второго управляемого источника тока, а его эмиттер связан с коллектором второго (12) входного транзистора и вторым (14) дополнительным токостабилизирующим двухполюсником. 9 ил.

Буферный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены ко входу (3) устройства, эмиттер первого (1) входного транзистора соединен с базой первого (4) выходного транзистора и коллектором входного транзистора (5) первого управляемого источника тока, эмиттер второго (2) входного транзистора подключен к базе второго (6) выходного транзистора и коллектору входного транзистора (7) второго управляемого источника тока, причем эмиттеры первого (4) и второго (6) выходных транзисторов соединены с выходом (8) устройства, первый (9) источник напряжения питания, с которым связаны эмиттер входного транзистора (5) управляемого источника тока и коллектор первого (4) выходного транзистора, второй (10) источник напряжения питания, к которому подключены эмиттер входного транзистора (7) второго управляемого источника тока и коллектор второго (6) выходного транзистора, отличающийся тем, что в схему введены первый (11) и второй (12) дополнительные транзисторы, базы которых подключены ко входу (3) устройства, коллектор первого (11) дополнительного транзистора соединен с базой входного транзистора (5) первого управляемого источника тока, а его эмиттер связан с коллектором первого (1) входного транзистора и первым (13) дополнительным токостабилизирующим двухполюсником, коллектор второго (12) дополнительного транзистора подключен к базе входного транзистора (7) второго управляемого источника тока, а его эмиттер связан с коллектором второго (12) входного транзистора и вторым (14) дополнительным токостабилизирующим двухполюсником.

| US 5557238 А, 17.09.1996 | |||

| ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2307456C1 |

| Двухтактный усилитель мощности | 1982 |

|

SU1113877A1 |

| US 5179355 А, 12.01.1993. | |||

Авторы

Даты

2012-03-27—Публикация

2010-08-30—Подача