Изобретение относится к области микроэлектроники и может быть использовано в качестве двухтактного выходного каскада в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.).

Известно значительное количество схем двухтактных буферных усилителей (БУ), которые реализуются на комплементарных биполярных (BJT) или полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах [1-28], а также при их совместном включении. Вышеназванные схемотехнические решения БУ наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов [1-28].

Особое место среди известных БУ занимают буферные усилители, реализация которых возможна только на n-p-n биполярных транзисторах [29-33], применение которых оказывает положительное влияние на себестоимость, например, операционных усилителей и их динамические параметры. Данное схемотехническое решение используется в серийных операционных усилителях OP27 и OP37 [30] фирмы Texas Instruments (США), а также в российских операционных усилителях 140УД30 [31], СВЧ интегральных усилителях с управляемым коэффициентом усиления [33]. Заявляемый БУ относится к данному классу устройств.

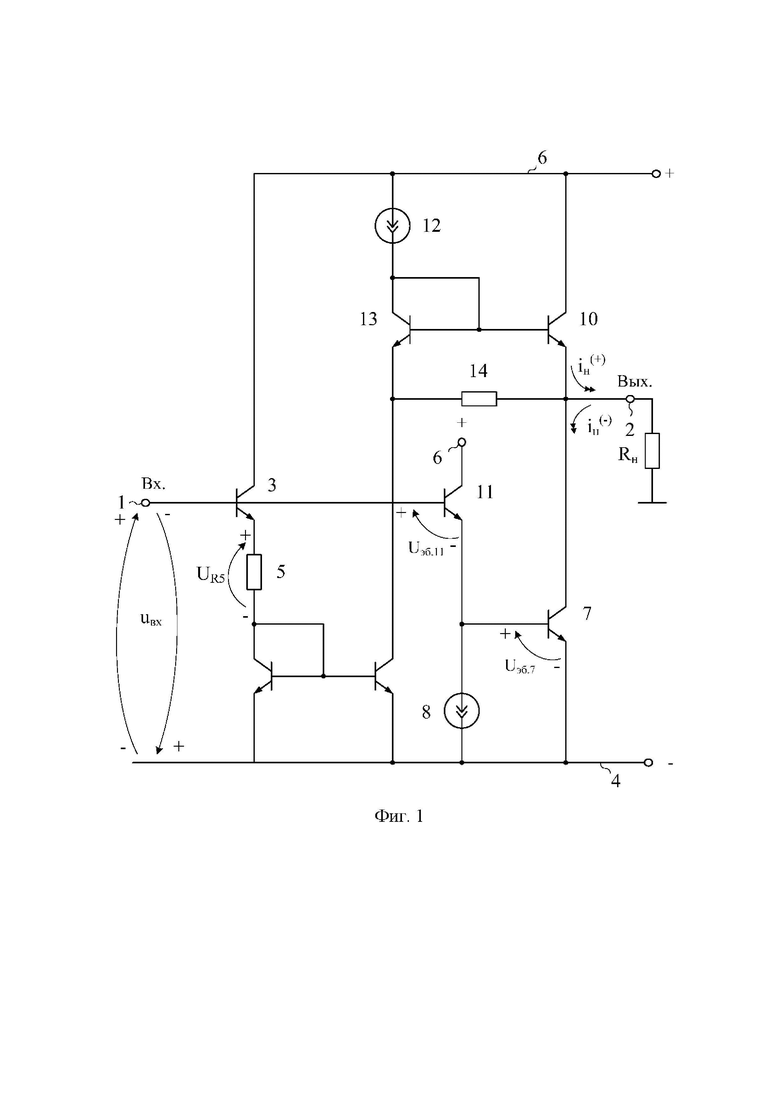

Ближайшим прототипом заявляемого устройства является буферный усилитель (фиг. 1) , представленный в патенте US 6.417.733, fig.1, 2002 г. Он содержит вход 1 и выход 2 устройства, входной транзистор 3, эмиттер которого связан с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник, коллектор подключен ко второй 6 шине источника питания, а база соединена со входом устройства 1, первый 7 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, коллектор соединен с выходом 2 устройства, а база связана с первой 4 шиной источника питания через второй 8 токостабилизирующий двухполюсник, второй 10 выходной транзистор, эмиттер которого соединен с выходом 2 устройства, а коллектор связан со второй 6 шиной источника питания, вспомогательный транзистор 11, коллектор которого соединен со второй 6 шиной источника питания, третий 12 токостабилизирующий двухполюсник, вспомогательный p-n переход 13 и вспомогательный резистор 14.

Основная особенность БУ-прототипа состоит в том, что он перспективен для аналоговых микросхем, реализуемых на однотипных n-p-n биполярных транзисторах. За счет применения SiGe технологий это позволяет получить предельные параметры по частотному диапазону операционных усилителей и других аналоговых устройств [33].

Существенный недостаток известного БУ состоит в том, что его вход должен быть «привязан» к первой 4 отрицательной шине источника питания. Схема БУ не работоспособна, если входной сигнал подается относительно общей шины первого 4 и второго 6 источников питания. Это существенно сужает области его практического использования, так как во многих случаях (например, в классических операционных усилителях) необходимы БУ, вход которых согласован с общей шиной источника питания.

Основная задача предлагаемого изобретения состоит в создании БУ на однотипных n-p-n биполярных транзисторах, например, SiGe, который обеспечивает передачу на выход устройства 2 входного напряжения относительно общей шины с близким к единице коэффициентом усиления и при сопротивлениях нагрузки, изменяющихся в широком диапазоне. По имеющимся сведениям, подобные схемы не существуют – в известных БУ статический потенциал входа должен быть согласован либо со второй 6 положительной, либо с первой 4 отрицательной шинами источников питания.

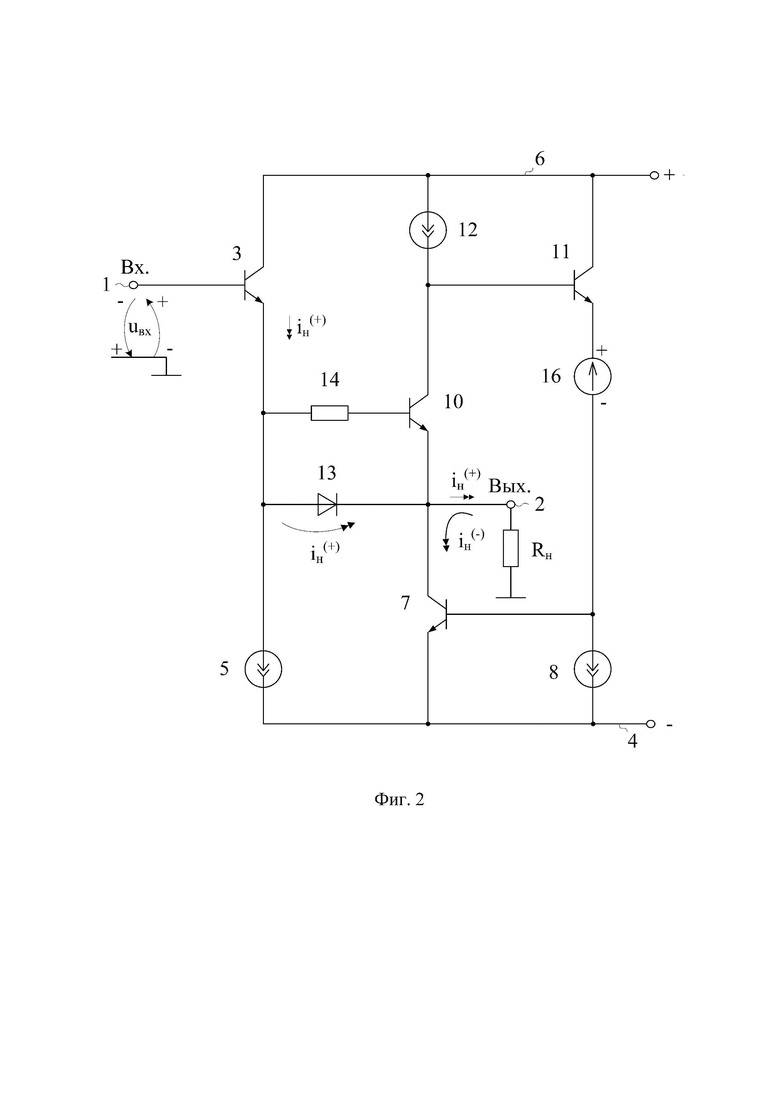

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, входной транзистор 3, эмиттер которого связан с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник, коллектор подключен ко второй 6 шине источника питания, а база соединена со входом устройства 1, первый 7 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, коллектор соединен с выходом 2 устройства, а база связана с первой 4 шиной источника питания через второй 8 токостабилизирующий двухполюсник, второй 10 выходной транзистор, эмиттер которого соединен с выходом 2 устройства, а коллектор связан со второй 6 шиной источника питания, вспомогательный транзистор 11, коллектор которого соединен со второй 6 шиной источника питания, третий 12 токостабилизирующий двухполюсник, вспомогательный p-n переход 13 и вспомогательный резистор 14, предусмотрены новые элементы и связи - коллектор второго 10 выходного транзистора связан со второй 6 шиной источника питания через третий 12 токостабилизирующий двухполюсник и подключен к базе вспомогательного транзистора 11, эмиттер которого связан с базой первого 7 выходного транзистора через цепь смещения потенциалов 16, причем база второго 10 выходного транзистора связана с эмиттером входного транзистора 3 через вспомогательный резистор 14, а эмиттер входного транзистора 3 связан с выходом 2 устройства через вспомогательный p-n переход 13.

На чертеже фиг. 1 приведена схема высоковольтного буферного усилителя–прототипа на n-p-n транзисторах по патенту US 6.417.733, fig.1, 2002 г.

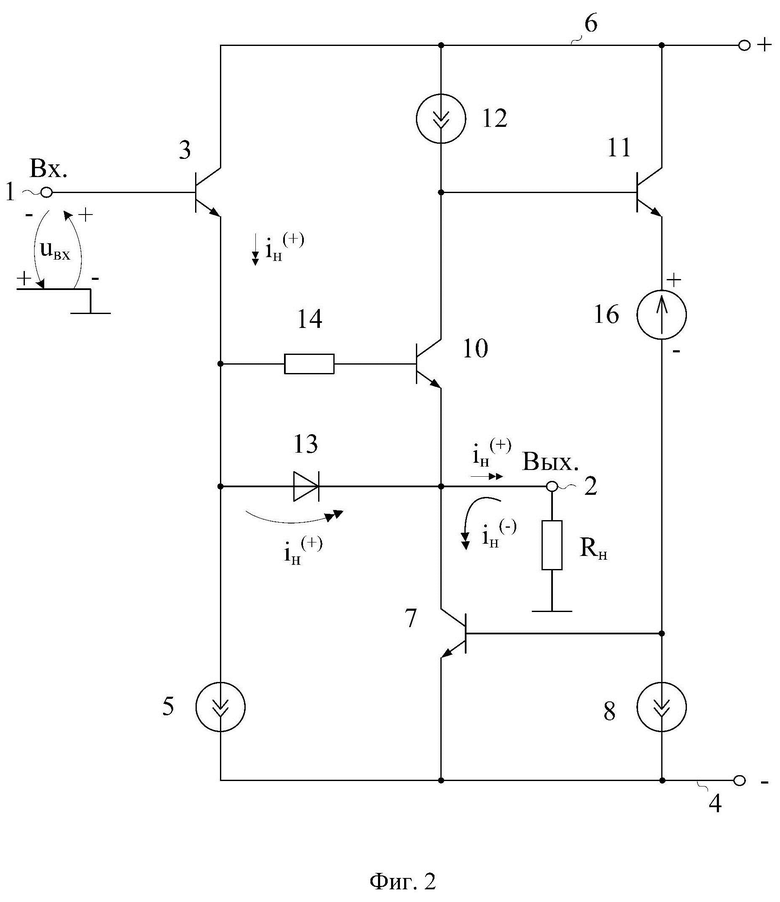

На чертеже фиг. 2 показана схема заявляемого БУ в соответствии с формулой изобретения.

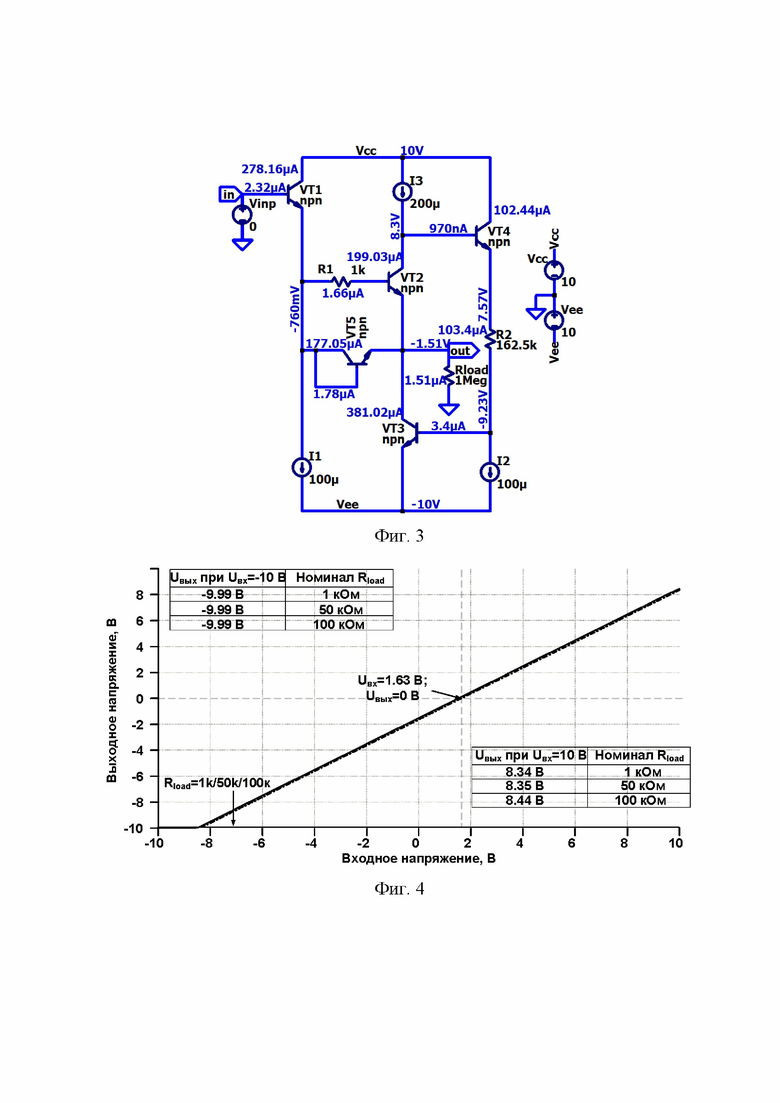

На чертеже фиг. 3 представлена схема для моделирования БУ фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=10 В, I1=I2=100 мкА, I3=200 мкА, R1=1 кОм, Rload=1 МОм, R2=162.5 кОм на моделях транзисторов базовых матричных кристаллов АО «Интеграл» (г. Минск) [34].

На чертеже фиг. 4 приведена амплитудная характеристика БУ фиг. 3 в среде LTspice при разных значениях сопротивлений нагрузки (Rload=1кОм/50кОм/100 кОм).

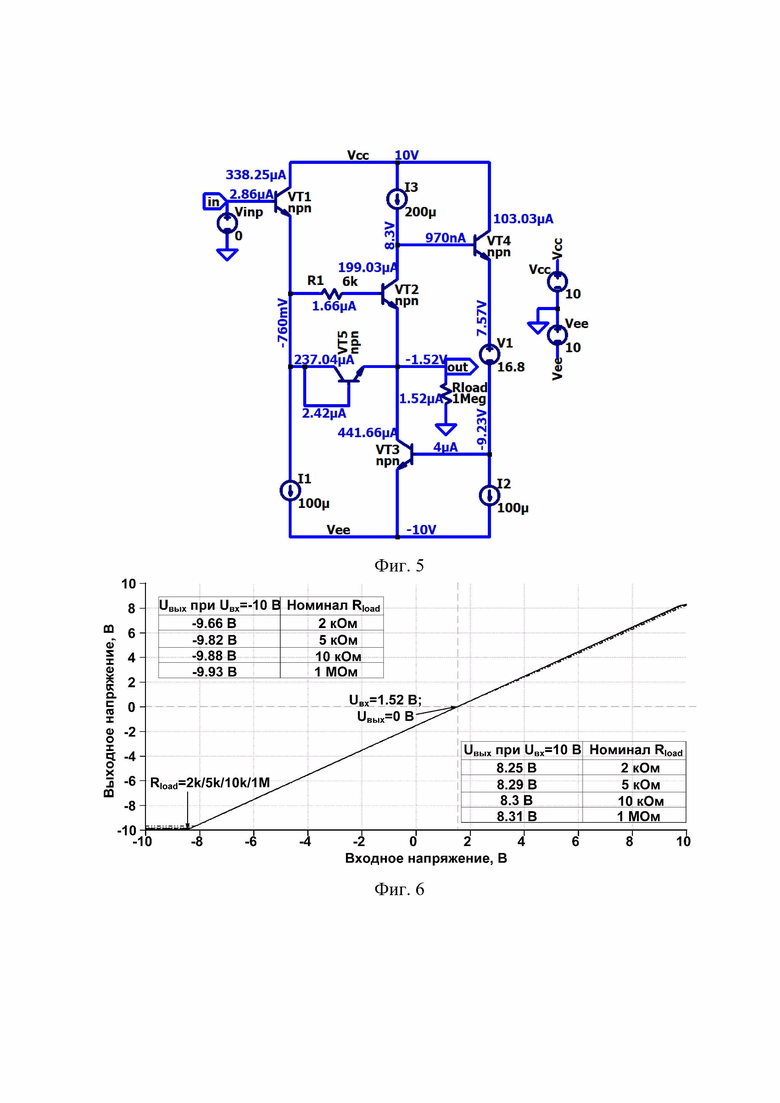

На чертеже фиг. 5 показана схема для моделирования БУ фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=10 В, I1=I2=100 мкА, I3=200 мкА, R1=6 кОм, Rload=1 МОм, источнике опорного напряжения V1=16.8 В, выполняющего функцию цепи смещения потенциала 16 (фиг. 2).

На чертеже фиг. 6 представлена амплитудная характеристика БУ фиг. 5 в среде LTspice при разных значениях сопротивлений нагрузки (Rload=2кОм/5кОм/10кОм/1МОм).

Буферный усилитель класса АВ на n-p-n биполярных транзисторах фиг. 2 содержит вход 1 и выход 2 устройства, входной транзистор 3, эмиттер которого связан с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник, коллектор подключен ко второй 6 шине источника питания, а база соединена со входом устройства 1, первый 7 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, коллектор соединен с выходом 2 устройства, а база связана с первой 4 шиной источника питания через второй 8 токостабилизирующий двухполюсник, второй 10 выходной транзистор, эмиттер которого соединен с выходом 2 устройства, а коллектор связан со второй 6 шиной источника питания, вспомогательный транзистор 11, коллектор которого соединен со второй 6 шиной источника питания, третий 12 токостабилизирующий двухполюсник, вспомогательный p-n переход 13 и вспомогательный резистор 14. Коллектор второго 10 выходного транзистора связан со второй 6 шиной источника питания через третий 12 токостабилизирующий двухполюсник и подключен к базе вспомогательного транзистора 11, эмиттер которого связан с базой первого 7 выходного транзистора через цепь смещения потенциалов 16, причем база второго 10 выходного транзистора связана с эмиттером входного транзистора 3 через вспомогательный резистор 14, а эмиттер входного транзистора 3 связан с выходом 2 устройства через вспомогательный p-n переход 13, который на практике (фиг. 3) реализуется на основе n-p-n биполярного транзистора. Двухполюсник Rн в схеме фиг. 2 моделирует свойства нагрузки.

Рассмотрим работу предлагаемого БУ фиг. 2.

Особенность схемы БУ фиг. 2 состоит в том, что она имеет два разных канала передачи положительных и отрицательных приращений входного напряжения uвх. Положительные приращения uвх передаются на выход устройства 2 по цепи эмиттера входного транзистора 3 через прямосмещенный вспомогательный p-n переход 13. При этом второй 10 выходной транзистор может входить в режим, близкий к режиму насыщения, а его влияние на передачу сигнала на выход 2 минимизируется вспомогательным резистором 14. При этом напряжение на базе вспомогательного транзистора 11 уменьшается, что передается через цепь смещения потенциалов 16 на базу первого 7 выходного транзистора, который в этом режиме запирается.

Если на вход 1 БУ подается отрицательное приращение входного напряжения, то это вызывает уменьшение тока коллектора второго 10 выходного транзистора и увеличение напряжения на базе вспомогательного транзистора 11, которое через цепь смещения потенциалов 16 поступает на базу первого 7 выходного транзистора. Как следствие, первый 7 выходной транзистор переходит в активный режим и создает отрицательное приращение тока  в нагрузке Rн.

в нагрузке Rн.

Работу БУ иллюстрируют графики на чертежах фиг. 4, фиг. 6, которые показывают, что при разных сопротивлениях нагрузки, в т.ч. Rн=1 КОм, максимальные выходные напряжения БУ близки к соответствующим напряжениям на второй 6 и первой 4 шинах источников питания.

Таким образом, предлагаемый буферный усилитель имеет существенные достоинства в сравнении с известным БУ-прототипом и может использоваться в различных аналоговых устройствах, в т.ч. операционных усилителях.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. А.св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. Патент US 6.417.733, fig. 1, 2002 г.

30. Low-noise high-speed precision operational amplifier OP037A Datasheet. Режим доступа: https://www.chipfind.ru/datasheet/ti/op37a.htm

31. Быстродействующий операционный усилитель 140УД30. Режим доступа: http://ic-info.ru/upload/iblock/449/140%D0%A3%D0%9430.pdf

32. I.M. Filanovsky, V.V. Ivanov, “Operational Amplifier Speed and Accuracy Improvement: Analog Circuit Design with Structural Methodology,” Kluwer Academiv Publishers, New York, Boston, Dordrecht, London, 2004. P. 123, fig. 7-4.

33. Savchenko Е.М., Budyakov А.S., Budyakov P.S., Prokopenko N.N. “The Method of Bandwidth Extension of SiGe BiCMOS Microwave Variable-Gain Amplifier Integrated Circuit”, Visnyk NTUU KPI Seriia – Radiotekhnica Radioaparatobuduvannia, 2017. Iss. 69, pp. 5–10, fig. 3

34. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. – М.: СОЛОН-Пресс, 2021. – 200 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ n-КАНАЛЬНЫХ ПОЛЕВЫХ И p-n-p БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2784376C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786191C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2023 |

|

RU2802051C1 |

Изобретение относится к области микроэлектроники. Технический результат: создание усилителя на однотипных n-p-n биполярных транзисторах, который обеспечивает передачу на выход устройства входного напряжения относительно общей шины с близким к единице коэффициентом усиления и при сопротивлениях нагрузки, изменяющихся в широком диапазоне. Для этого предложен буферный усилитель класса АВ на n-p-n биполярных транзисторах, который содержит вход (1) и выход (2) устройства, входной транзистор (3), первую (4) шину источника питания, первый (5) токостабилизирующий двухполюсник, вторую (6) шину источника питания, первый (7) выходной транзистор, второй (8) токостабилизирующий двухполюсник, второй (10) выходной транзистор, вспомогательный транзистор (11), третий (12) токостабилизирующий двухполюсник, вспомогательный p-n переход (13) и вспомогательный резистор (14). 6 ил.

Буферный усилитель класса АВ на n-p-n биполярных транзисторах, содержащий вход (1) и выход (2) устройства, входной транзистор (3), эмиттер которого связан с первой (4) шиной источника питания через первый (5) токостабилизирующий двухполюсник, коллектор подключен ко второй (6) шине источника питания, а база соединена с входом устройства (1), первый (7) выходной транзистор, эмиттер которого связан с первой (4) шиной источника питания, коллектор соединен с выходом (2) устройства, а база связана с первой (4) шиной источника питания через второй (8) токостабилизирующий двухполюсник, второй (10) выходной транзистор, эмиттер которого соединен с выходом (2) устройства, а коллектор связан со второй (6) шиной источника питания, вспомогательный транзистор (11), коллектор которого соединен со второй (6) шиной источника питания, третий (12) токостабилизирующий двухполюсник, вспомогательный p-n переход (13) и вспомогательный резистор (14), отличающийся тем, что коллектор второго (10) выходного транзистора связан со второй (6) шиной источника питания через третий (12) токостабилизирующий двухполюсник и подключен к базе вспомогательного транзистора (11), эмиттер которого связан с базой первого (7) выходного транзистора через цепь смещения потенциалов (16), причем база второго (10) выходного транзистора связана с эмиттером входного транзистора (3) через вспомогательный резистор (14), а эмиттер входного транзистора (3) связан с выходом (2) устройства через вспомогательный p-n переход (13).

| US 6417733 B1, 09.07.2002 | |||

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

Авторы

Даты

2022-12-23—Публикация

2022-09-19—Подача