Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве BiJFet (биполярно-полевых) буферных усилителей различных аналоговых устройств, в том числе допускающих работу в условиях воздействия проникающей радиации и низких температур.

Известно значительное количество схем буферных усилителей (БУ), которые реализуются на биполярных (BJT) и полевых (BiJFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-26]. Во многих задачах схема БУ адаптируется под конкретные технологические процессы и внешние воздействующие факторы, например, влияние низких температур и радиации, т.к. только в этом случае обеспечивается реализациях предельных параметров БУ.

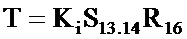

Ближайшим прототипом заявляемого устройства является буферный усилитель, представленный в патентной заявке US 2009/0051434, fig. 10. Он содержит вход 1 и выход 2 устройства, неинвертирующий повторитель напряжения 3, высокоомный вход которого 4 соединен со входом 1 устройства, токовый выход 5 связан с первой шиной источника питания 6, а низкоомный потенциальный выход 7 соединен с выходом устройства 2, инвертирующий усилитель 8, согласованный со второй 9 шиной источника питания, токовый выход которого 10 соединен с выходом 2 устройства, а вход 11 связан со второй 9 шиной источника питания через согласующий двухполюсник 12 и подключен к коллектору первого 13 вспомогательного транзистора, причем эмиттер первого 13 вспомогательного транзистора соединен с эмиттером второго 14 вспомогательного транзистора и через токостабилизирующий двухполюсник 15 связан с первой 6 шиной источника питания.

Существенный недостаток известного буферного усилителя состоит в том, что в рамках данной архитектуры его схема не может быть реализована только на комплементарных полевых транзисторах с управляющим p-n переходом, для которых подтверждена работоспособность [27, 28] в условиях проникающей радиации и низких, в т.ч. криогенных, температур, а также низкий уровень шумов. Формальная замена не радиационно-стойких и не низкотемпературных [28] p-n-p биполярных транзисторов 13, 14 в схеме БУ-прототипа фиг. 1 на полевые транзисторы с управляющим p-n переходом и p-каналом невозможна, т.к. в этом случае в известной схеме возникает неуправляемый сквозной ток Iскв. Это не позволяет установить стабильный статический режим известного БУ. Кроме этого, схема БУ-прототипа потребляет дополнительный ток I1. Таким образом, схема БУ-прототипа имеет ограниченное применение.

Основная задача предполагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного схемотехнического решения БУ, в т.ч. на комплементарных BJFet полевых транзисторах, обеспечивающего (при высокой линейности амплитудной характеристики) повышенную стабильность статического режима и низкий уровень шумов при работе в диапазоне низких температур.

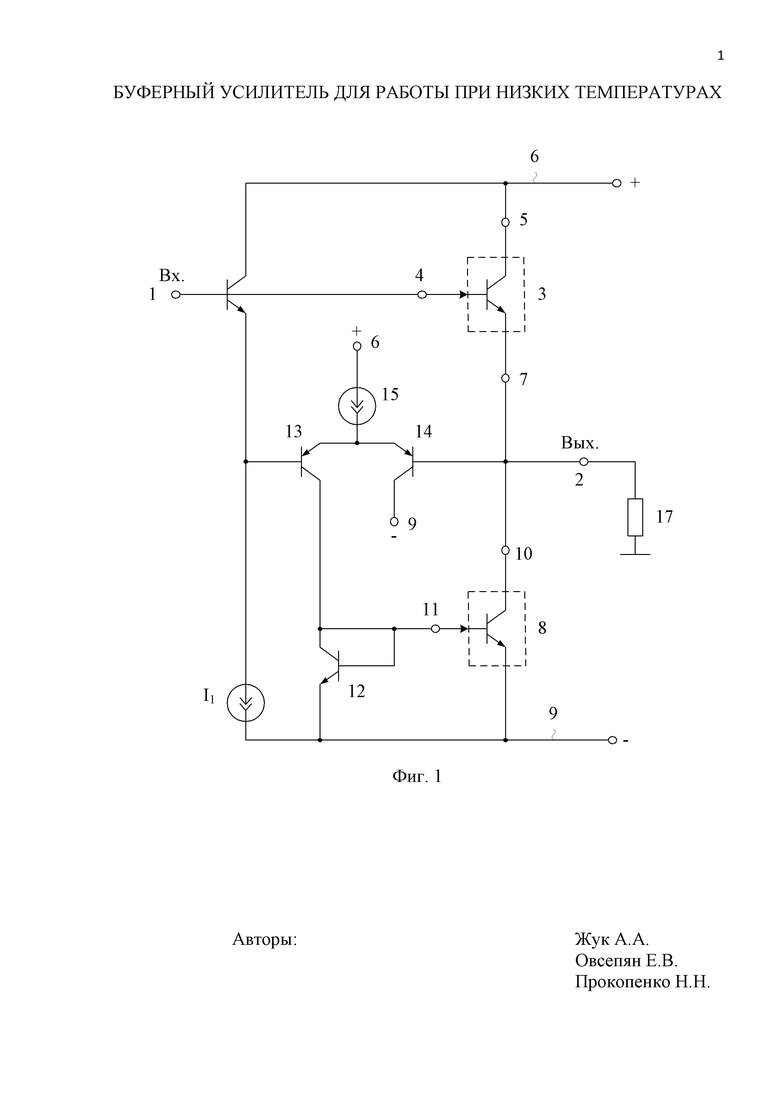

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, неинвертирующий повторитель напряжения 3, высокоомный вход которого 4 соединен со входом 1 устройства, токовый выход 5 связан с первой шиной источника питания 6, а низкоомный потенциальный выход 7 соединен с выходом устройства 2, инвертирующий усилитель 8, согласованный со второй 9 шиной источника питания, токовый выход которого 10 соединен с выходом 2 устройства, а вход 11 связан со второй 9 шиной источника питания через согласующий двухполюсник 12 и подключен к коллектору первого 13 вспомогательного транзистора, причем эмиттер первого 13 вспомогательного транзистора соединен с эмиттером второго 14 вспомогательного транзистора и через токостабилизирующий двухполюсник 15 связан с первой 6 шиной источника питания, предусмотрены новые элементы и связи - в качестве первого 13 и второго 14 вспомогательных транзисторов используются полевые транзисторы с управляющим р-n переходом, сток которых соответствует коллектору, исток - эмиттеру, а затвор - базе биполярного транзистора, токовый выход 5 неинвертирующего повторителя напряжения 3 связан с первой 6 шиной источника питания через измерительный резистор 16 и соединен с затвором второго 14 вспомогательного полевого транзистора, причем затвор первого 13 вспомогательного полевого транзистора связан с первой 6 шиной источника питания, а в качестве согласующего двухполюсника 12 используется источник опорного тока.

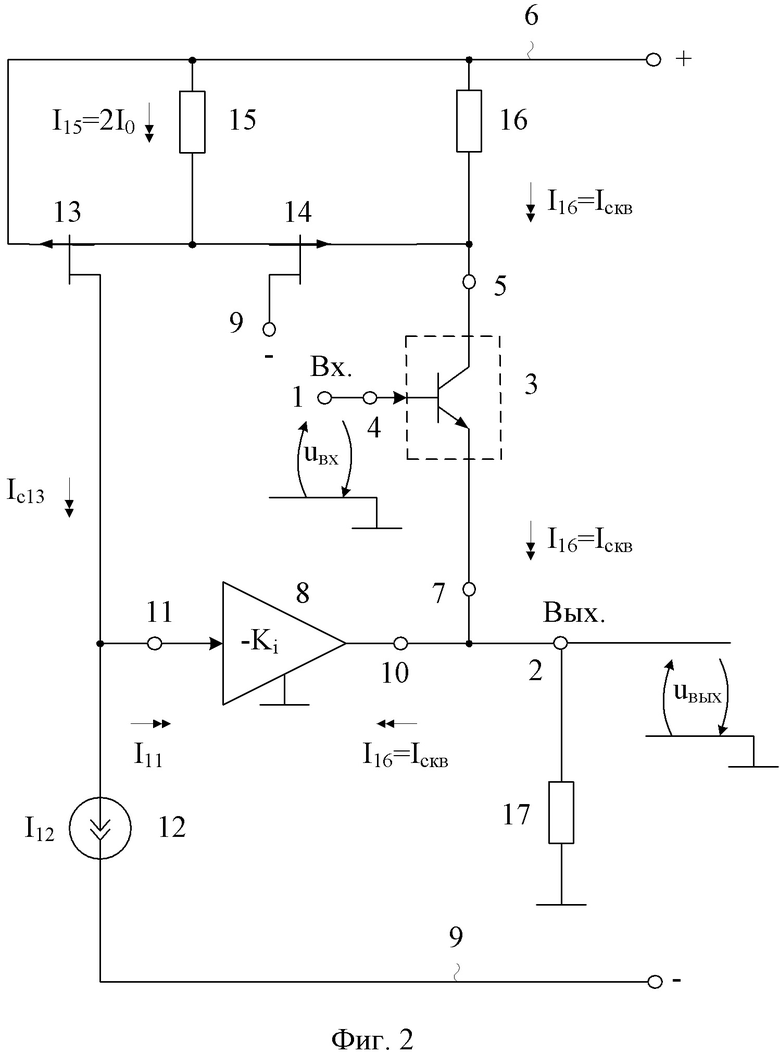

На чертеже фиг. 1 представлена схема БУ-прототипа, а на чертеже фиг. 2 - схема заявляемого БУ в соответствии с п. 1 формулы изобретения.

На чертеже фиг. 3 приведена схема БУ фиг.2 с конкретным выполнением неинвертирующего повторителя напряжения 3 (транзистор 18) и инвертирующего усилителя 8, который реализован на транзисторах 19 и 20.

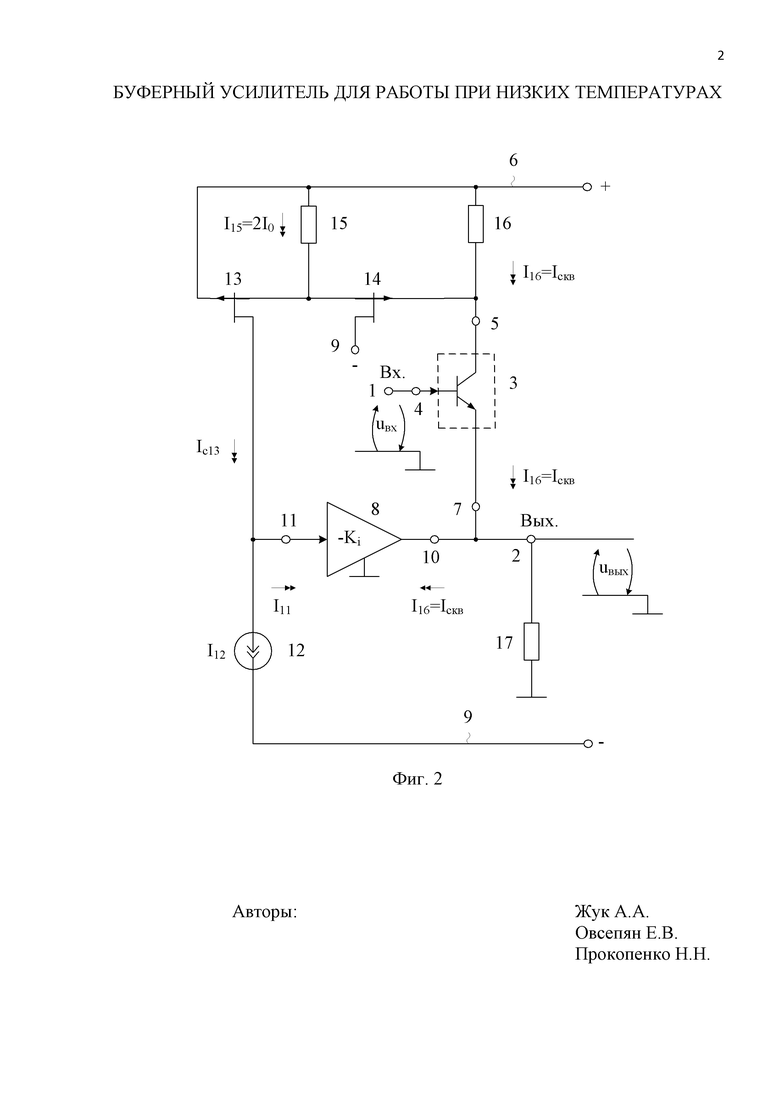

На чертеже фиг. 4 показана схема заявляемого БУ в соответствии с п. 2 формулы изобретения для случая, когда неинвертирующий повторитель напряжения 3 выполнен на биполярном n-p-n транзисторе 18 [28], а инвертирующий усилитель 8 - на биполярном транзисторе 22 (в общем случае - составном транзисторе по схеме Дарлингтона).

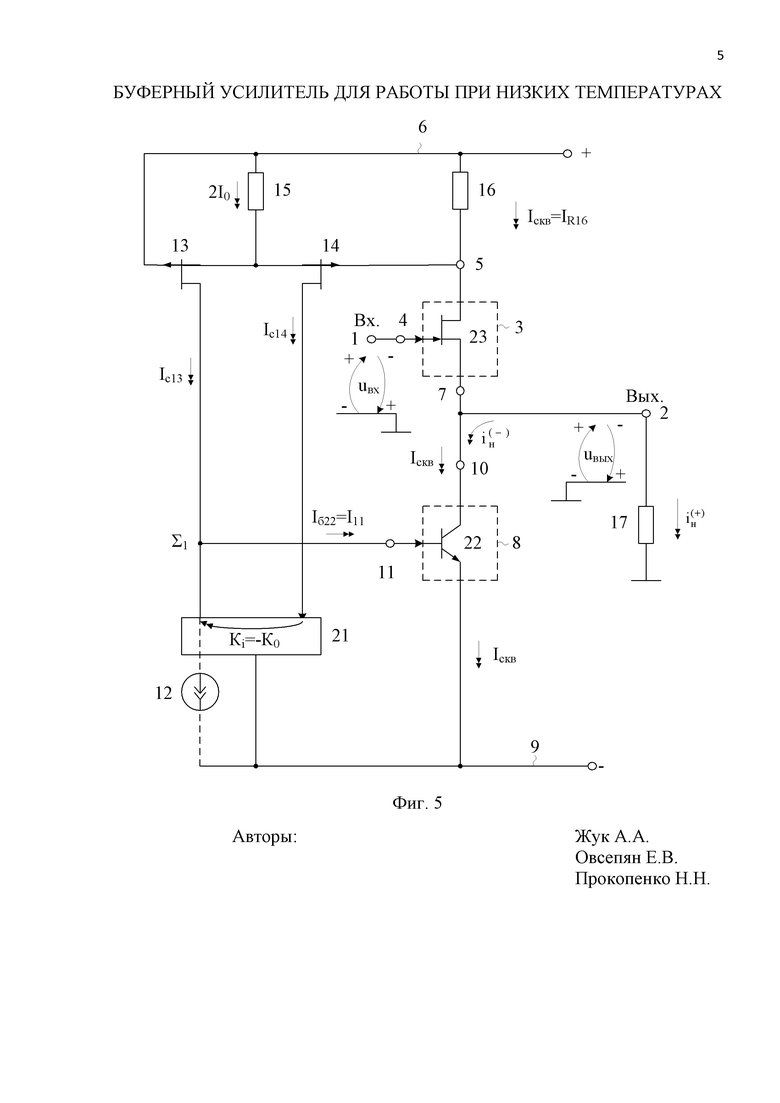

На чертеже фиг. 5 приведена схема заявляемого БУ в соответствии с п. 2 формулы изобретения для случая, когда неинвертирующий повторитель напряжения 3 выполнен на полевом транзисторе 23 с управляющим р-n переходом [28].

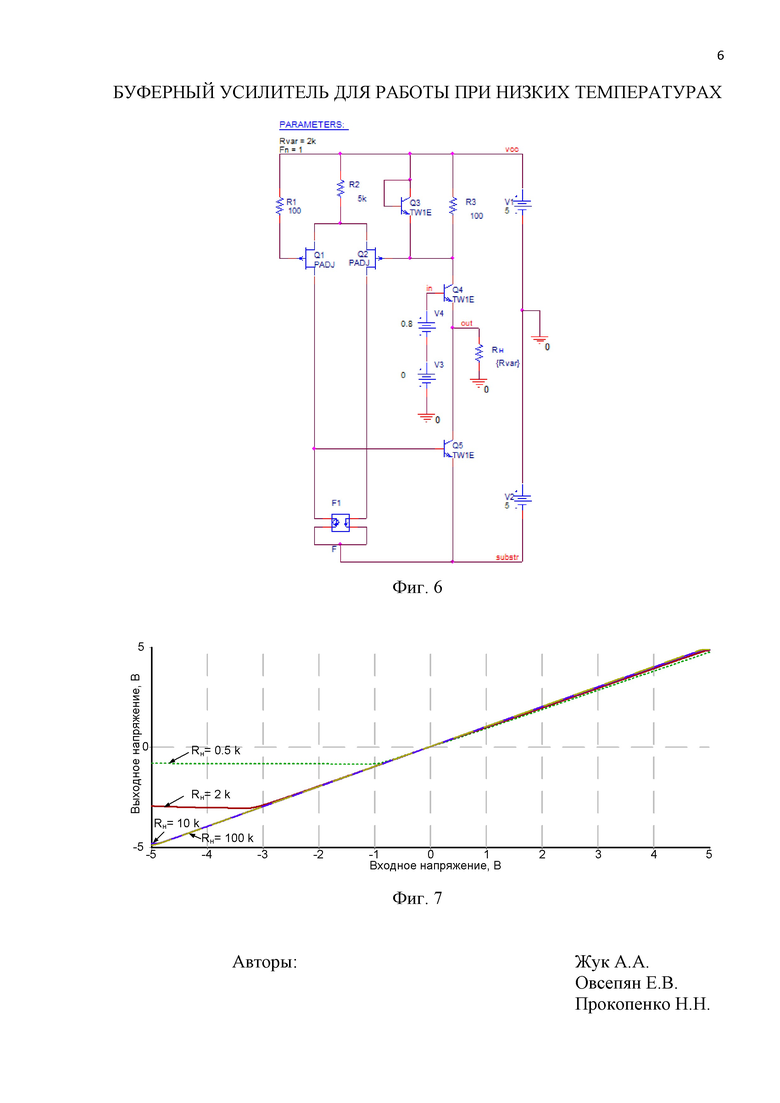

На чертеже фиг. 6 представлена схема BiJFet БУ фиг. 4 в среде Pspice при Ki токового зеркала 21 (F1) Ki=K0=0.9.

На чертеже фиг. 7 показана амплитудная характеристика БУ фиг. 6 при Ki=K0=0.9, V3=Vin==-5÷+5B, сопротивлении нагрузки RH=0.5/2/10/100 кОм и напряжении смещения V4=0.8 В.

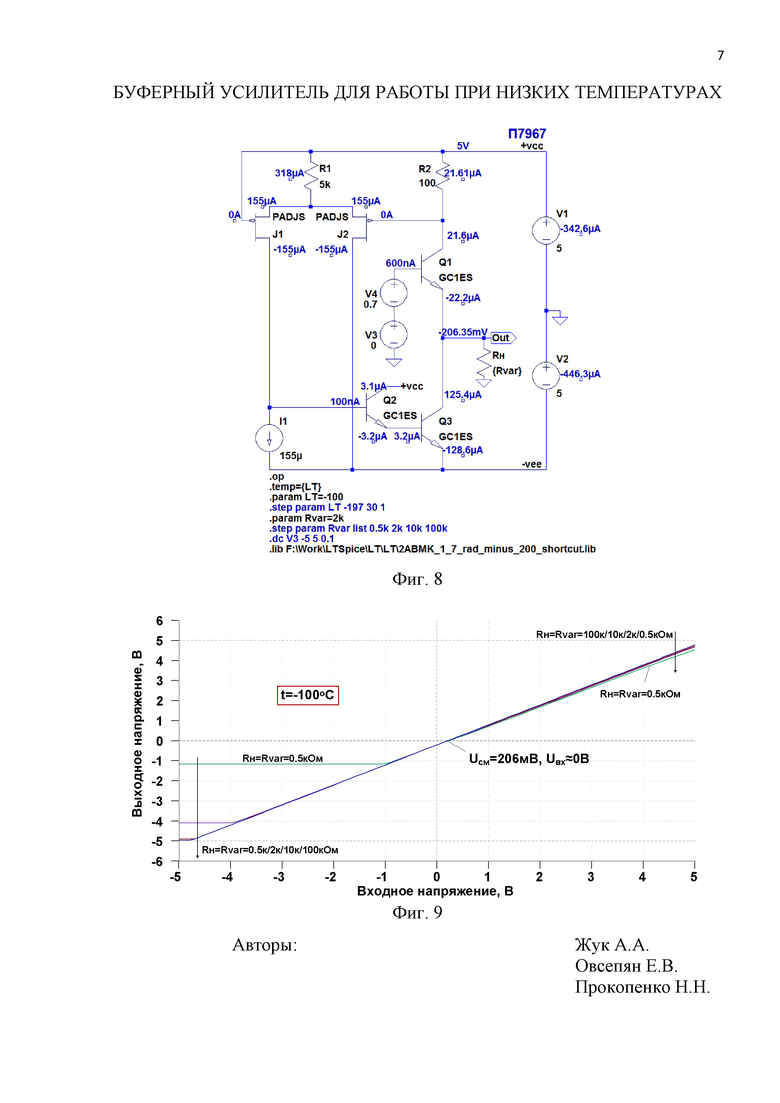

На чертеже фиг. 8 представлен статический режим ОУ фиг. 3 в среде LTSpice на транзисторах базового матричного кристалла АВМK_1_7_rad_minus_200_shortcut при отрицательных температурах (t=-100°С).

На чертеже фиг. 9 приведена амплитудная характеристика БУ фиг. 8 при t=-100°C при разных сопротивлениях нагрузки Rн (0.5 кОм, 2 кОм, 10 кОм, 100 кОм).

Буферный усилитель для работы при низких температурах фиг. 2 содержит вход 1 и выход 2 устройства, неинвертирующий повторитель напряжения 3, высокоомный вход которого 4 соединен со входом 1 устройства, токовый выход 5 связан с первой шиной источника питания 6, а низкоомный потенциальный выход 7 соединен с выходом устройства 2, инвертирующий усилитель 8, согласованный со второй 9 шиной источника питания, токовый выход которого 10 соединен с выходом 2 устройства, а вход 11 связан со второй 9 шиной источника питания через согласующий двухполюсник 12 и подключен к коллектору первого 13 вспомогательного транзистора, причем эмиттер первого 13 вспомогательного транзистора соединен с эмиттером второго 14 вспомогательного транзистора и через токостабилизирующий двухполюсник 15 связан с первой 6 шиной источника питания. В качестве первого 13 и второго 14 вспомогательных транзисторов используются полевые транзисторы с управляющим p-n переходом, сток которых соответствует коллектору, исток - эмиттеру, а затвор - базе биполярного транзистора, токовый выход 5 неинвертирующего повторителя напряжения 3 связан с первой 6 шиной источника питания через измерительный резистор 16 и соединен с затвором второго 14 вспомогательного полевого транзистора, причем затвор первого 13 вспомогательного полевого транзистора связан с первой 6 шиной источника питания, а в качестве согласующего двухполюсника 12 используется источник опорного тока.

На чертеже фиг. 3 неинвертирующий повторитель напряжения 3 реализован на биполярном транзисторе 18, который в рамках радиационно-стойкого технологического процесса 3КБТ (АО «Интеграл», г. Минск) удовлетворительно работает при низких температурах [28]. Здесь же инвертирующий усилитель 8 выполнен на транзисторах 19 и 20, включенных по схеме Дарлингтона.

На чертеже фиг. 4, в соответствии с п. 2 формулы изобретения, в качестве источника опорного тока 12 используется выход дополнительного токового зеркала 21, вход которого связан со стоком второго 14 вспомогательного полевого транзистора.

На чертеже фиг. 4 инвертирующий усилитель 8 выполнен на транзисторе 22.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, коэффициент передачи по току дополнительного токового зеркала 21 меньше единицы.

На чертежах фиг. 2, фиг. 3, фиг. 4 и фиг. 5 двухполюсник 17 моделирует свойства нагрузки БУ.

На чертеже фиг. 5 неинвертирующий повторитель напряжения 3 выполнен на полевом транзисторе 23 с управляющим p-n переходом.

В статическом режиме БУ фиг. 3 при нулевом входном сигнале (uвх=0) через измерительный резистор 16 протекает «сквозной» ток Iскв между шинами питания 6 и 9 (при Rн=R17=∞).

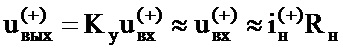

Рассмотрим работу БУ фиг. 2 при увеличении положительного напряжения

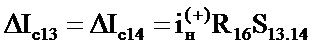

где S13-14 - крутизна дифференциального каскада на первом 13 и втором 14 вспомогательных полевых транзисторах.

Это вызывает более глубокое запирание по базе транзистора 19, его переход в отсечку. Таким образом, при положительном

Если на вход 1 БУ фиг. 3 подается напряжение отрицательной полярности

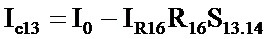

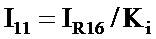

Для схемы фиг. 3 можно записать следующие уравнения Кирхгофа:

где Ic13 - статический ток первого 13 вспомогательного полевого транзистора,

Ki - коэффициент усиления по току инвертирующего усилителя 8.

Поэтому сквозной ток БУ I16=Iскв:

или

где

Таким образом, при большом петлевом усилении Т>>1 и большом сопротивлении нагрузки 17 сквозной ток БУ фиг. 3 определяется следующими формулами

Из последних формул следует, что сквозной ток IR16=Iскв в заявляемом БУ определяется, прежде всего, токами токостабилизирующего двухполюсника 15 и согласующего двухполюсника 12 и может быть выбран по усмотрению разработчика.

Амплитудные характеристики фиг. 7 и фиг. 9 показывают, что при отрицательных входных напряжениях максимальная амплитуда выходного напряжения БУ

Таким образом, заявляемое устройство характеризуется существенными преимуществами в сравнении с БУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US № 4.596.958, 1986 г.

2. Патент WO 2007135139, 2007 г.

3. Патент US 4743862, 1988 г.

4. Патент US 6433638, fig. 1a-2, 2002 г.

5. Патентная заявка US 2005/0253653, 2000 г.

6. Патент US 4825174, fig. 3, fig. 6, 1989 г.

7. Патент RU 2099856, fig. 3, 1997 г.

8. Патент US 4904953, fig. 2, 1990 г.

9. Патент US 7896339, fig. 4, 2011 г.

10. Патент US 6342814, 2002 г.

11. Патентная заявка US 2010/0182086, 2010 г.

12. Патент US 5387880, fig. 1, 1995 г.

13. Патент US 4598253, 1986 г.

14. Патент US 4667165, fig. 2, 1987 г.

15. Патент US 4596958, 1986 г.

16. Патент US 7116172, fig. 4, fig. 5, 2006 г.

17. Патент US 5648743, 1997 г.

18. Патент US 5367271, fig. 2, 1994 г.

19. Патентная заявка US 2000/0112075, fig. 3, 2000 г.

20. Патент US 5065043, fig. 1f, 1991 г.

21. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 2-е. - М.: Издательство БИНОМ. 2014. - 704 с. Рис. 3.26, рис. 3.28, рис. 3.29

22. Патентная заявка US 2007/0115056, fig. 2, 2007 г.

23. Патент US 7548117, fig. 5, 2009 г.

24. Патент EP 0 293486 B1, fig. 5, 1988 г.

25. Patt Boonyaporn, Varakorn Kasemsuwan. A High Performance Class AB CMOS Rail to Rail Voltage Follower // ASIC, 2002. Proceedings. 2002 IEEE Asia-Pacific Conference on, pp. 161-163

26. Патент US 4420726, fig. 1 - fig. 3, 1983 г.

27. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

28. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ "НАПРЯЖЕНИЕ-ТОК" С ШИРОКИМ ДИАПАЗОНОМ ЛИНЕЙНОЙ РАБОТЫ | 2017 |

|

RU2658818C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615066C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ УСИЛИТЕЛЬ ТОКА ДЛЯ ЗАДАЧ ПРОЕКТИРОВАНИЯ АКТИВНЫХ RC-ФИЛЬТРОВ | 2020 |

|

RU2727965C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в создании радиационно-стойкого и низкотемпературного схемотехнического решения буферного усилителя. Буферный усилитель для работы при низких температурах содержит вход и выход устройства, неинвертирующий повторитель напряжения, высокоомный вход которого соединен со входом устройства, токовый выход связан с первой шиной источника питания, а низкоомный потенциальный выход соединен с выходом устройства, инвертирующий усилитель, согласованный со второй шиной источника питания, токовый выход которого соединен с выходом устройства, а вход связан со второй шиной источника питания через согласующий двухполюсник и подключен к коллектору первого вспомогательного транзистора, причем эмиттер первого вспомогательного транзистора соединен с эмиттером второго вспомогательного транзистора и через токостабилизирующий двухполюсник связан с первой шиной источника питания, при этом в качестве первого и второго вспомогательных транзисторов используются полевые транзисторы с управляющим p-n-переходом, сток которых соответствует коллектору, исток – эмиттеру, затвор – базе биполярного транзистора, а в качестве согласующего двухполюсника используется источник опорного тока. 2 з.п. ф-лы, 9 ил.

1. Буферный усилитель для работы при низких температурах, содержащий вход (1) и выход (2) устройства, неинвертирующий повторитель напряжения (3), высокоомный вход которого (4) соединен с входом (1) устройства, токовый выход (5) связан с первой шиной источника питания (6), а низкоомный потенциальный выход (7) соединен с выходом устройства (2), инвертирующий усилитель (8), согласованный со второй (9) шиной источника питания, токовый выход которого (10) соединен с выходом (2) устройства, а вход (11) связан со второй (9) шиной источника питания через согласующий двухполюсник (12) и подключен к коллектору первого (13) вспомогательного транзистора, причем эмиттер первого (13) вспомогательного транзистора соединен с эмиттером второго (14) вспомогательного транзистора и через токостабилизирующий двухполюсник (15) связан с первой (6) шиной источника питания, отличающийся тем, что в качестве первого (13) и второго (14) вспомогательных транзисторов используются полевые транзисторы с управляющим p-n-переходом, сток которых соответствует коллектору, исток – эмиттеру, а затвор – базе биполярного транзистора, токовый выход (5) неинвертирующего повторителя напряжения (3) связан с первой (6) шиной источника питания через измерительный резистор (16) и соединен с затвором второго (14) вспомогательного полевого транзистора, причем затвор первого (13) вспомогательного полевого транзистора связан с первой (6) шиной источника питания, а в качестве согласующего двухполюсника (12) используется источник опорного тока.

2. Буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что в качестве источника опорного тока (12) используется выход дополнительного токового зеркала (21), вход которого связан со стоком второго (14) вспомогательного полевого транзистора.

3. Буферный усилитель для работы при низких температурах по п.2, отличающийся тем, что коэффициент передачи по току дополнительного токового зеркала (21) меньше единицы.

| РАДИАЦИОННО-СТОЙКИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393625C1 |

| КОМПЛЕМЕНТАРНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444115C1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 7961052 B2, 14.06.2011 | |||

| US 8031002 B2, 04.10.2011. | |||

Авторы

Даты

2019-05-07—Публикация

2018-07-23—Подача