Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления сигналов постоянного тока, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и прецизионных операционных усилителях (ОУ) с малыми значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные усилители (ДУ) с существенными различными параметрами. Особое место занимают ДУ с простейшей двухкаскадной архитектурой, содержащие входные составные транзисторы - так называемые каскады Дарлингтона. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу ДУ.

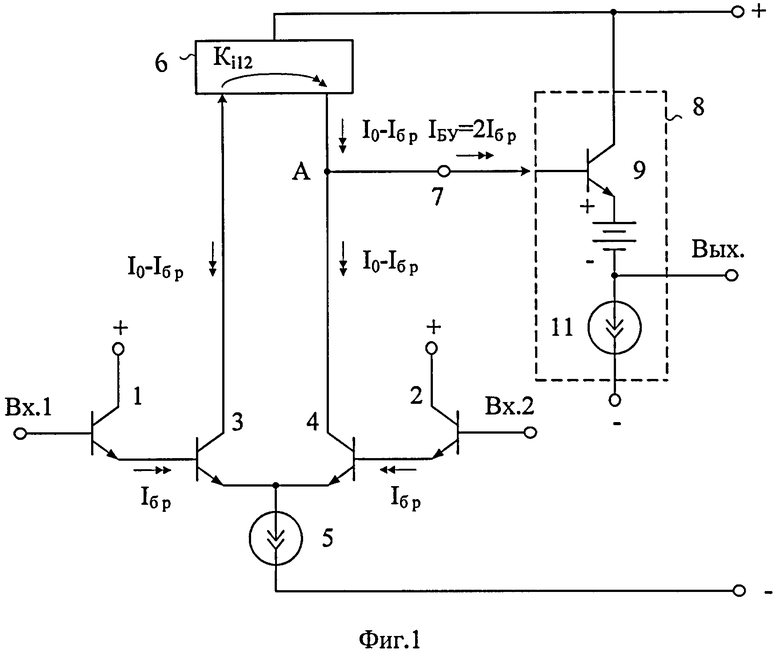

Наиболее близким по сущности к заявляемому техническому решению является классическая схема ДУ на основе входных составных транзисторов фиг.1, представленная в патенте фирмы National Semiconductor (США) №5.537.081, которая также присутствует в большом числе других патентов [1-22].

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении систематической составляющей абсолютного значения Uсм и величины его температурного дрейфа.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с соответствующими первым 3 и вторым 4 выходными транзисторами, источник опорного тока 5, связанный с эмиттерами первого 3 и второго 4 выходных транзисторов, токовое зеркало 6, вход которого соединен с коллектором первого 3 выходного транзистора, а выход подключен ко второму 4 выходному транзистору и входу 7 буферного усилителя 8 на входном транзисторе 9, тип проводимости которого совпадает с типом проводимости первого 3 и второго 4 выходных транзисторов, предусмотрены новые элементы и связи - коллекторы первого 1 и второго 2 входных транзисторов связаны по переменному току с коллектором первого 3 выходного транзистора.

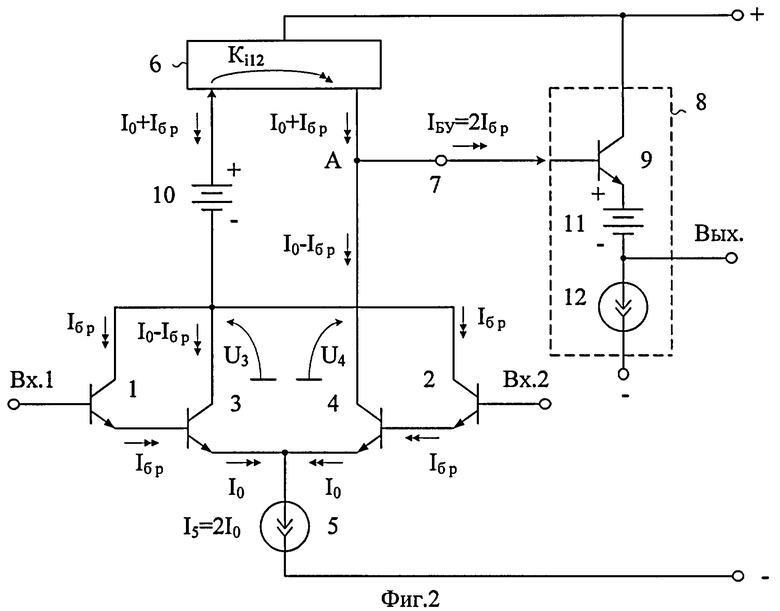

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

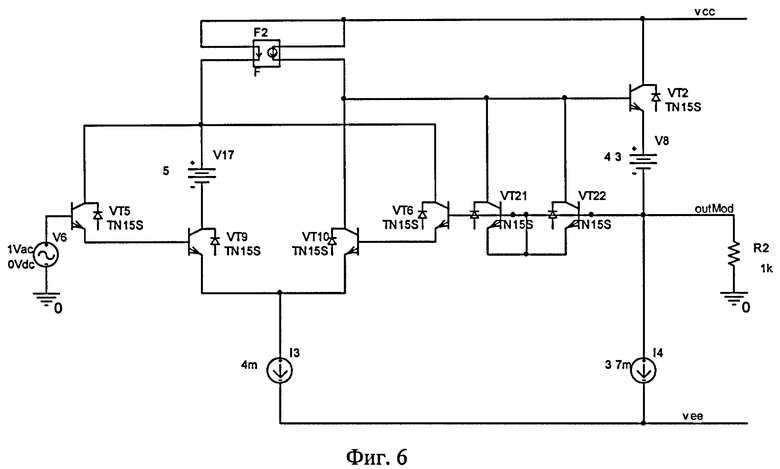

На фиг.3 показана схема заявляемого устройства в соответствии с п.3 формулы изобретения.

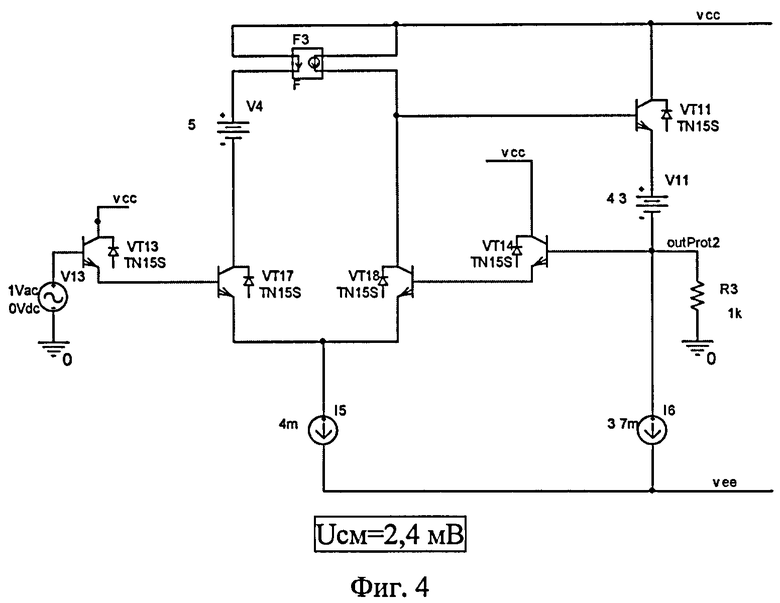

На фиг.4 представлена схема дифференциального усилителя-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НЛП «Пульсар».

На фиг.5 и фиг.6 представлены схемы заявляемых ДУ фиг.2 и фиг.3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 приведены температурные зависимости напряжения смещения нуля схем фиг.4, фиг.5 и фиг.6.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с соответствующими первым 3 и вторым 4 выходными транзисторами, источник опорного тока 5, связанный с эмиттерами первого 3 и второго 4 выходных транзисторов, токовое зеркало 6, вход которого соединен с коллектором первого 3 выходного транзистора, а выход подключен ко второму 4 выходному транзистору и входу 7 буферного усилителя 8 на входном транзисторе 9, тип проводимости которого совпадает с типом проводимости первого 3 и второго 4 выходных транзисторов. Коллекторы первого 1 и второго 2 входных транзисторов связаны по переменному току с коллектором первого 3 выходного транзистора.

На фиг.2, в соответствии с п.2 формулы изобретения, коллектор первого 3 выходного транзистора связан со входом токового зеркала 6 через первую цепь согласования потенциалов 10. Буферный усилитель 8 реализован на основе цепи смещения 11 и двухполюснике 12.

На фиг.3, в соответствии с п.3 формулы изобретения, ко входу 7 буферного усилителя 8 подключены коллекторы первого 13 и второго 14 дополнительных транзисторов терморадиационной компенсации.

В качестве токового зеркала 6 авторы рекомендуют использовать классические токовые зеркала (например, схему Вильсона), обладающие единичным коэффициентом передачи тока Ki12=-1.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2, т.е. зависящие от схемотехники ДУ.

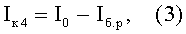

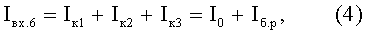

Если ток общей эмиттерной цепи 5 (I5) равен величине 2I0, то коллекторные токи транзисторов 1, 2, 3, 4:

где Iб.р=Iэ.i/βi - ток базы транзисторов 3 и 4 при эмиттерном токе;

Iэ.i=I0;

βi - коэффициент усиления по току базы транзисторов 3 и 4.

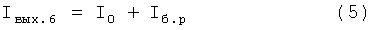

Поэтому входной (Iвх.6), а также выходной (Iвых.6) токи токового зеркала 6, имеющего коэффициент передачи по току Ki6=-1:

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ=2Iб.р - ток базы транзистора 9 буферного усилителя 8.

Подставляя IБУ в (6), находим, что разностный ток, определяющий Uсм.1

Как следствие, при Iр=0 не требуется смещения нуля ДУ фиг.2 на величину Uсм.1, подача которого на его входы Вх.1, Вх.2 компенсирует разностный ток Iр в узле «А».

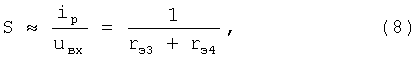

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая Uсм.1, обусловленная конечной величиной β транзисторов 3, 4, 9 и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм.1, так как разностный ток Iр в узле «A» создает Uсм.1, зависящее от крутизны преобразования входного дифференциального напряжения uвх ДУ в выходной ток узла «A»:

где rэ3=rэ4 - сопротивления эмиттерных переходов входных транзисторов 3 и 4 дифференциального каскада.

Поэтому для схем фиг.1-фиг.2

где φт=26 мВ - температурный потенциал.

В ДУ-прототипе фиг.1 Iр=IБУ=2Iб.р, поэтому здесь систематическая составляющая Uсм.1 получается на два порядка больше (Uсм.1=2,4 мВ), чем в заявляемой схеме (Uсм.1=14 мкВ).

Кроме этого в схеме фиг.2 величина второй составляющей Uсм.2, обусловленной внутренней обратной связью в транзисторах 3 и 4, также существенно уменьшается. При этом условие минимизации этой составляющей (Uсм.2) определяется формулой:

где U3, U4 - статические напряжения на коллекторах транзисторов 3 и 4.

Для обеспечения равенства (10) в схему вводится первая цепь смещения потенциалов 10.

Компьютерное моделирование схем фиг.3 и фиг.4 подтверждает (фиг.7) данные теоретические выводы.

Если необходимо обеспечить симметрию амплитуд положительных и отрицательных полуволн выходного напряжения ДУ фиг.2, то следует ввести вторую цепь смещения потенциалов 11 в структуру буферного усилителя 8.

Для минимизации Uсм.1 при повышенных температурах (t>80°C) в схеме фиг.3 предусмотрены транзисторы 13 и 14, которые находятся в закрытом состоянии. Однако токи через их р-n-переходы на подложку, которые существенно возрастают на высоких температурах (или при радиационных воздействиях), компенсируют соответствующие токи на подложку через p-n-переходы транзисторов 1 и 2. Это существенно уменьшает производную dUсм/dT при t>80°C (фиг.7).

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Интегральные микросхемы. Операционные усилители [Текст]: справочник. - М., Издательский дом «Додэка-XXI», 2001. - С.159, операционные усилители 574УД3.

2. Интегральные микросхемы. Операционные усилители [Текст]: справочник. - М., Издательский дом «Додэка-XXI», 2001. - С.30, рис.34а.

3. Патент США №3.936.731.

4. Патент США №4.109.215.

5. Патент США №3.482.177.

6. Патент США №3.262.064.

7. Патент США №3.491.307.

8. Патент США №5.537.081, fig.3.

9. Патент США №5.327.099, fig.1.

10. Патент США №5.872.811, fig.3.

11. Патент США №3.435.365.

12. Патент США №3.936.731, fig.13.

13. Патент США №3.444.472.

14. Патент США №4.293.824, fig.1.

15. Патент Англии 1366538.

16. Патент ФРГ 2055939.

17. Патент ФРГ 2032630.

18. Ав. свид. СССР 532957.

19. Ав. свид. СССР 269220.

20. Ав. свид. СССР 291308.

21. Ав. свид. СССР 336765.

22. Ав. свид. СССР 985933.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402870C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2408975C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402871C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402156C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2009 |

|

RU2416154C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412531C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2412528C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и прецизионных операционных усилителях (ОУ) с малыми значениями э.д.с. смещения нуля). Технический результат - уменьшение систематической составляющей абсолютного значения Uсм и величины его температурного дрейфа. Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), эмиттеры которых соединены с соответствующими первым (3) и вторым (4) выходными Т, источник опорного тока (5), связанный с эмиттерами первого Т (3) и второго Т (4), токовое зеркало (6), вход которого соединен с коллектором первого Т (3), а выход подключен ко второму Т (4) и входу (7) буферного усилителя (8) на входном Т (9), тип проводимости которого совпадает с типом проводимости первого Т (3) и второго Т (4). Коллекторы первого Т (1) и второго Т (2) связаны по переменному току с коллектором первого Т (3). 2 з.п. ф-лы, 7 ил.

1. Дифференциальный усилитель с малым напряжением смещения нуля, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых соединены с соответствующими первым (3) и вторым (4) выходными транзисторами, источник опорного тока (5), связанный с эмиттерами первого (3) и второго (4) выходных транзисторов, токовое зеркало (6), вход которого соединен с коллектором первого (3) выходного транзистора, а выход подключен ко второму (4) выходному транзистору и входу (7) буферного усилителя (8) на входном транзисторе (9), тип проводимости которого совпадает с типом проводимости первого (3) и второго (4) выходных транзисторов, отличающийся тем, что коллекторы первого (1) и второго (2) входных транзисторов связаны по переменному току с коллектором первого (3) выходного транзистора.

2. Устройство по п.1, отличающееся тем, что коллектор первого (3) выходного транзистора связан со входом токового зеркала (6) через первую цепь согласования потенциалов (10).

3. Устройство по п.1, отличающееся тем, что ко входу (7) буферного усилителя (8) подключены коллекторы первого (13) и второго (14) дополнительных транзисторов терморадиационной компенсации.

| US 5537081 А, 16.07.1996 | |||

| Дифференциальный усилитель | 1980 |

|

SU985933A1 |

| US 5327099 А, 05.07.1994 | |||

| US 3688209 А, 29.08.1972. | |||

Авторы

Даты

2011-02-10—Публикация

2009-07-21—Подача