Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, СВЧ операционных усилителях (ОУ), компараторах).

Известны схемы классических дифференциальных усилителей (ДУ) [1-14] с отрицательной обратной связью по синфазному сигналу, которые стали основой многих серийных аналоговых микросхем первого и второго поколения.

В последние годы ДУ данного класса стали снова активно применяться в структуре СВЧ-устройств [1, 2, 3], реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцевого диапазона для современных и перспективных систем связи. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1) B, которое характерно для SiGe-транзисторов с предельными частотами 100÷200 ГГц.

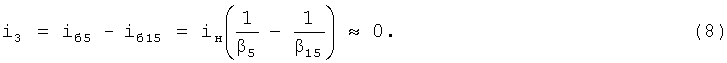

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в статье [2], содержащий входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с базами первого 4 и второго 5 выходных транзисторов, первый 6 и второй 7 двухполюсники нагрузки, выходной транзистор стабилизатора тока 8, коллектор которого соединен с общей эмиттерной цепью 9 входного параллельно-балансного каскада 1, вспомогательный двухполюсник 10, включенный параллельно эмиттерно-базовому переходу выходного транзистора стабилизатора тока 8, первый 11 и второй 12 резисторы обратной связи, первые выводы которых подключены к эмиттерам соответствующих первого 4 и второго 5 выходных транзисторов, а также первому 13 и второму 14 противофазным выходам дифференциального усилителя, а вторые выводы связаны с базой выходного транзистора стабилизатора тока 8.

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно небольшой коэффициент усиления по напряжению (Ky) при низкоомной нагрузке (например, Rн=50 Ом).

Основная задача предлагаемого изобретения состоит в увеличении коэффициента усиления по напряжению ДУ при низкоомной нагрузке без ухудшения энергетических параметров в статическом режиме.

Поставленная задача достигается тем, что в дифференциальном усилителе, фиг.1, содержащем входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с базами первого 4 и второго 5 выходных транзисторов, первый 6 и второй 7 двухполюсники нагрузки, выходной транзистор стабилизатора тока 8, коллектор которого соединен с общей эмиттерной цепью 9 входного параллельно-балансного каскада 1, вспомогательный двухполюсник 10, включенный параллельно эмиттерно-базовому переходу выходного транзистора стабилизатора тока 8, первый 11 и второй 12 резисторы обратной связи, первые выводы которых подключены к эмиттерам соответствующих первого 4 и второго 5 выходных транзисторов, а также первому 13 и второму 14 противофазным выходам дифференциального усилителя, а вторые выводы связаны с базой выходного транзистора стабилизатора тока 8, предусмотрены новые элементы и связи - в схему введены первый 15 и второй 16 дополнительные транзисторы, а также первый 17 и второй 18 дополнительные двухполюсники, база первого 4 выходного транзистора соединена с первым 6 двухполюсником нагрузки и базой второго 16 дополнительного транзистора через первый дополнительный двухполюсник 17, база второго 5 выходного транзистора соединена со вторым 7 двухполюсником нагрузки и базой первого 15 дополнительного транзистора через второй 18 дополнительный двухполюсник, коллектор первого 4 выходного транзистора соединен с эмиттером первого 15 дополнительного транзистора, коллектор второго 5 выходного транзистора соединен с эмиттером второго 16 дополнительного транзистора, причем коллекторы первого 15 и второго 16 дополнительных транзисторов связаны с шиной источника питания.

Схема заявляемого устройства, соответствующего формуле изобретения, показана на фиг.2.

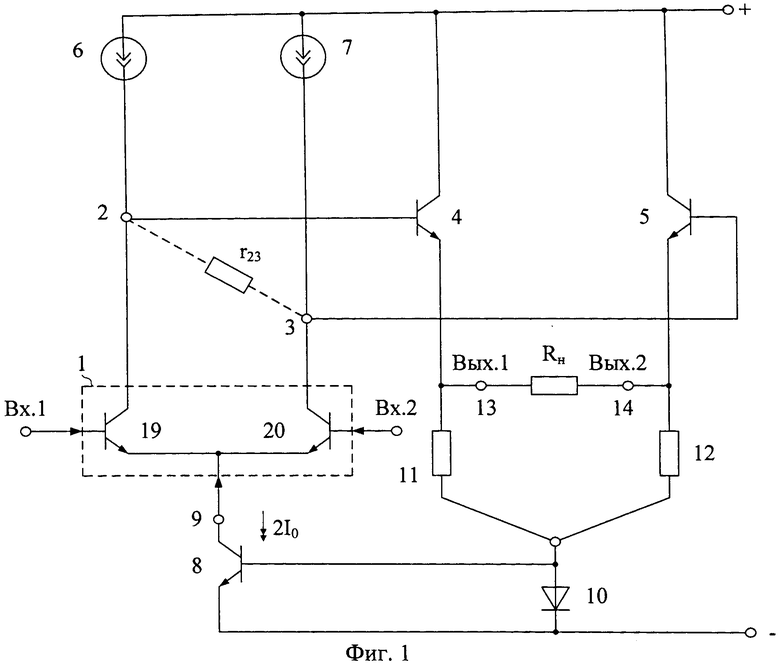

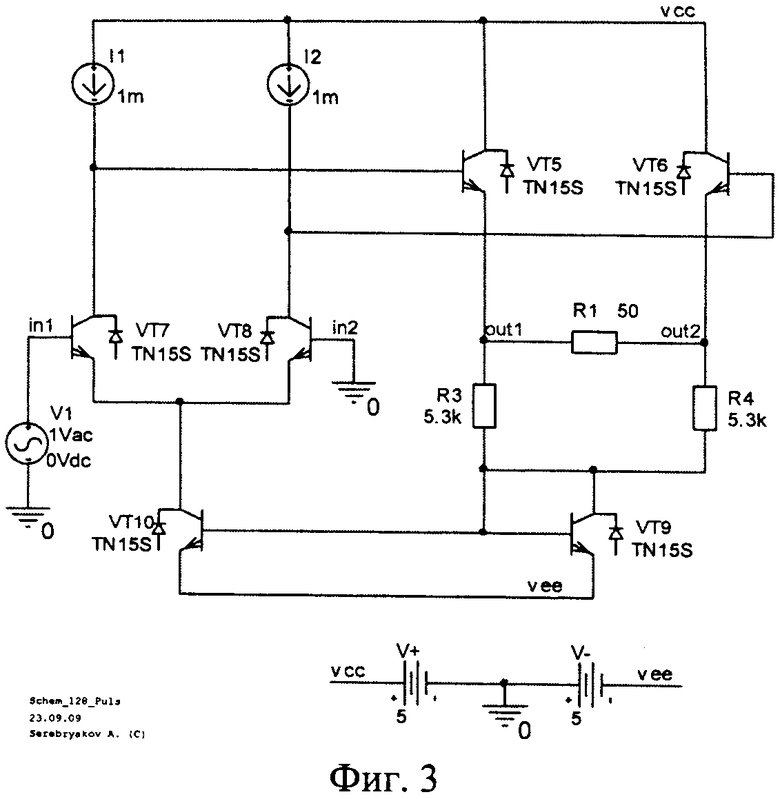

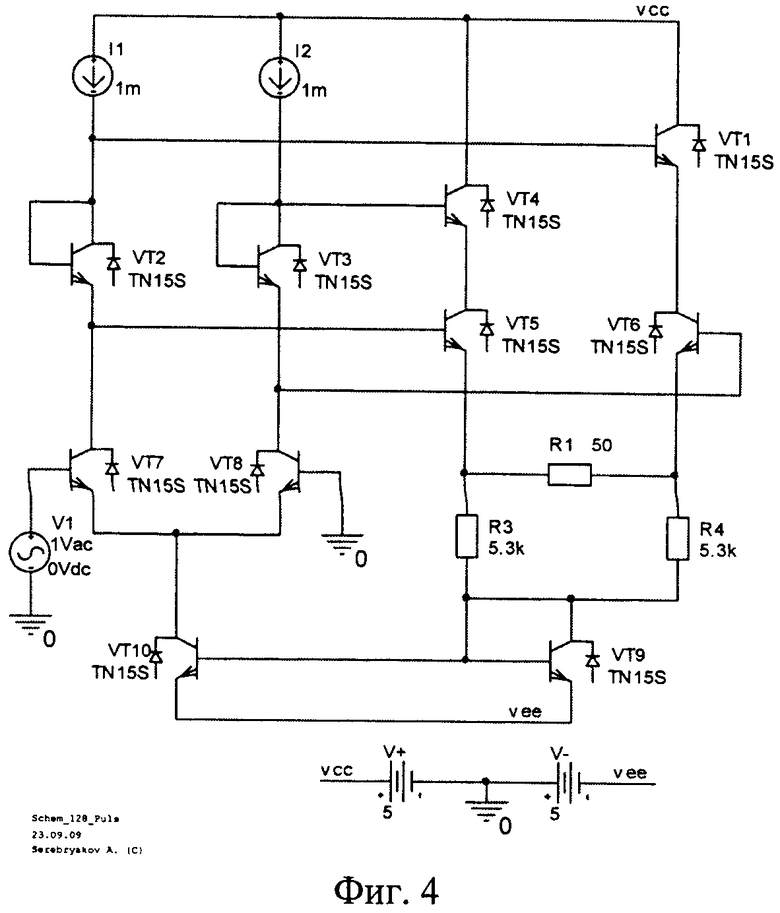

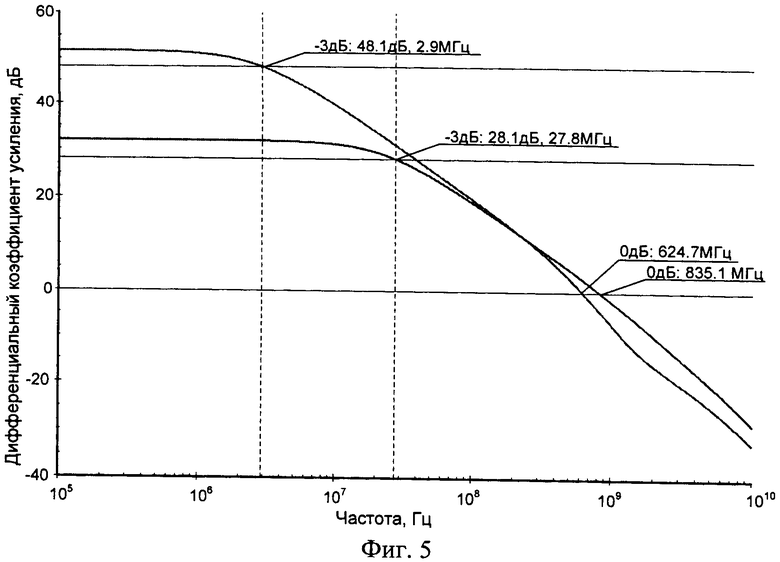

На фиг.3 и 4 показаны схемы ДУ-прототипа (фиг.3) и заявляемого ДУ (фиг.4) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.5 - зависимость Ky сравниваемых схем (фиг.3, 4) от частоты.

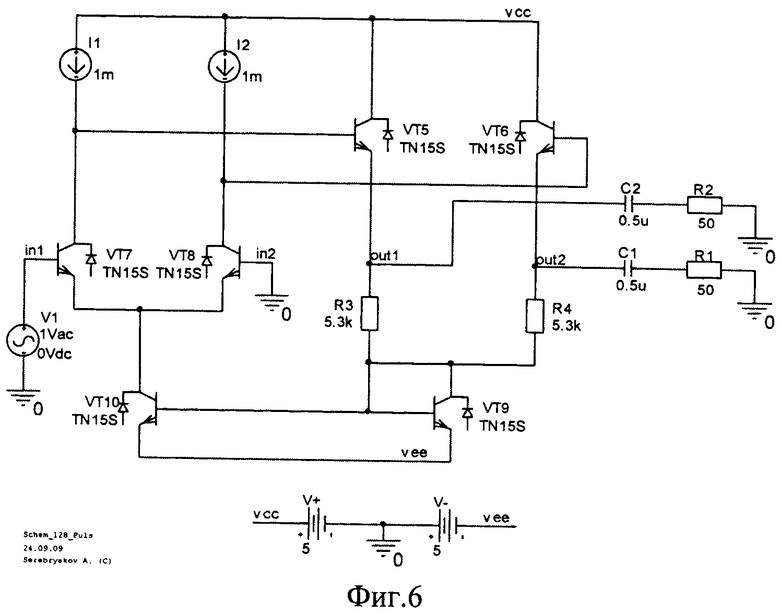

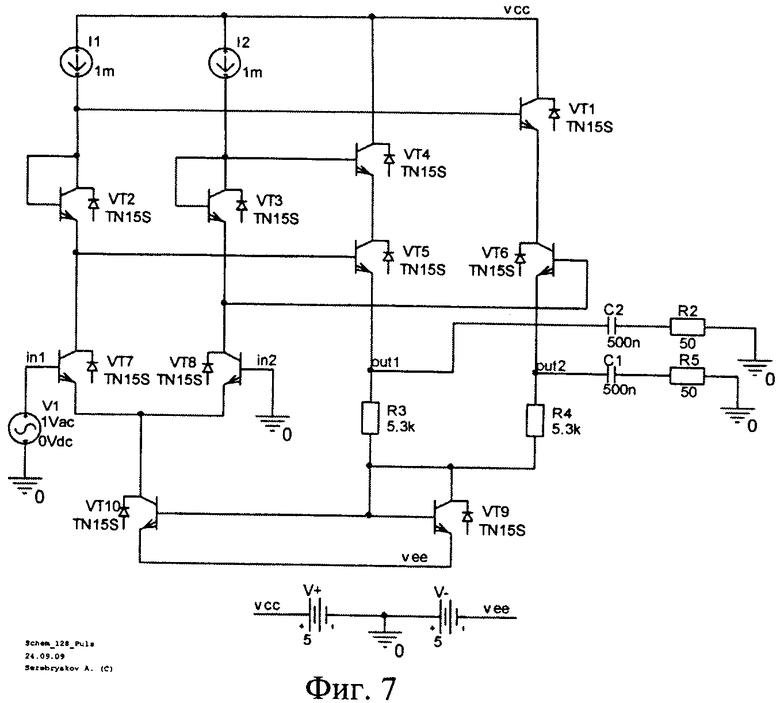

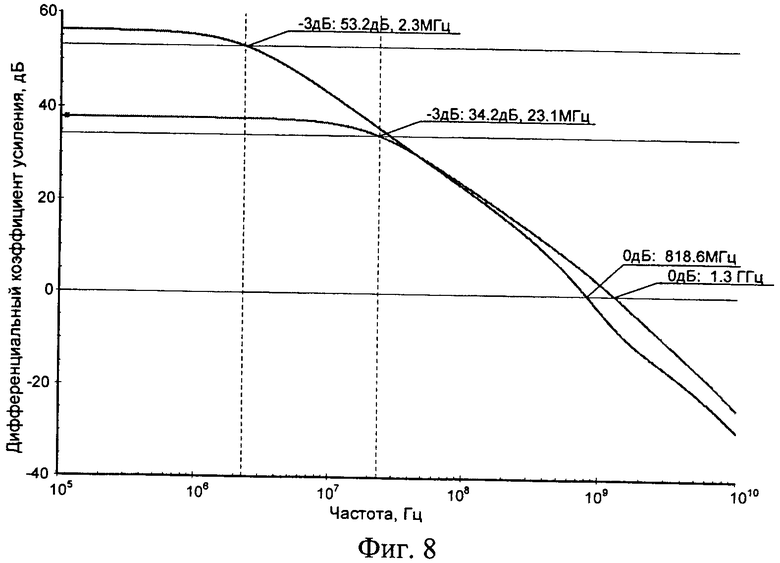

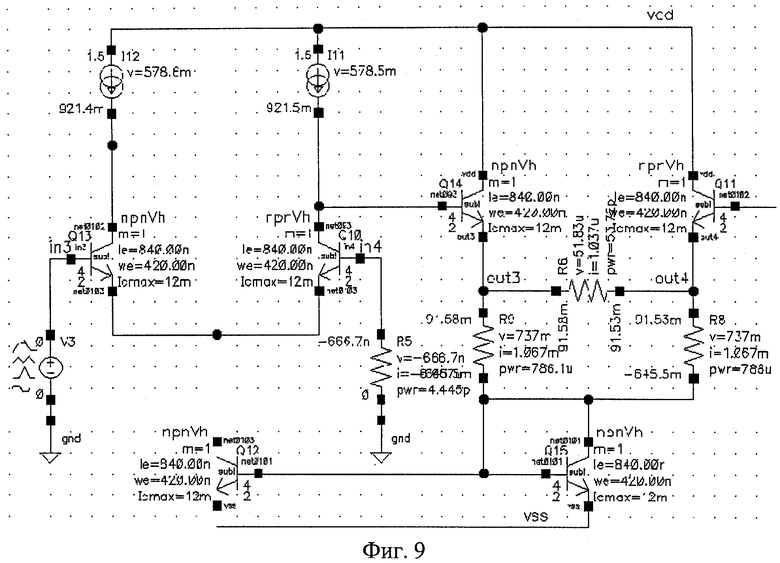

На фиг.6 и 7 показаны схемы ДУ-прототипа (фиг.6) и заявляемого ДУ (фиг.7) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда в ДУ используется несимметричное включение низкоомной нагрузки (50 Ом) между общей шиной источников питания и выходами устройств, а на фиг.8 - зависимость Ky сравниваемых схем (фиг.6, 7) от частоты.

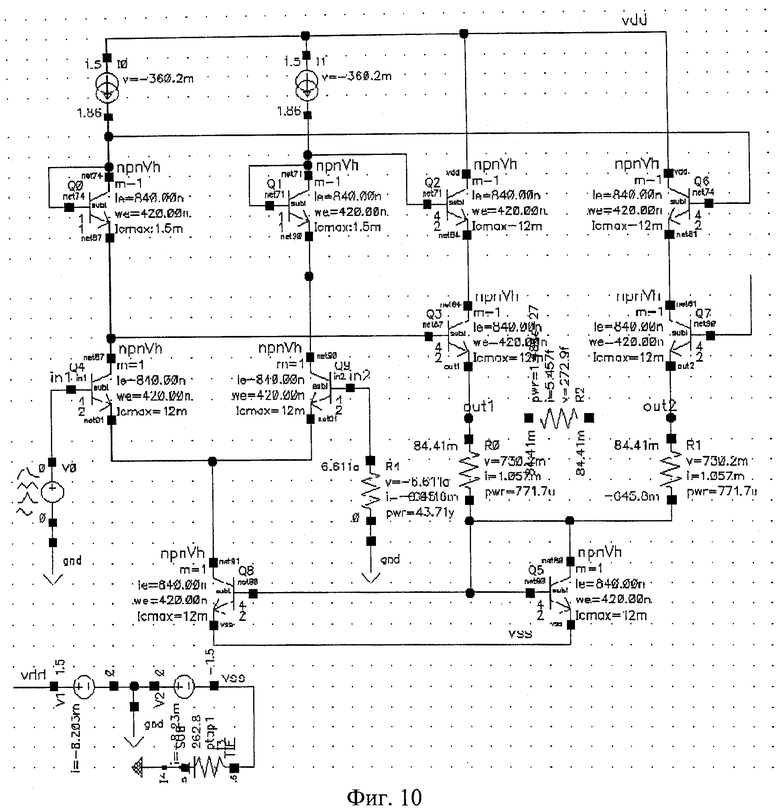

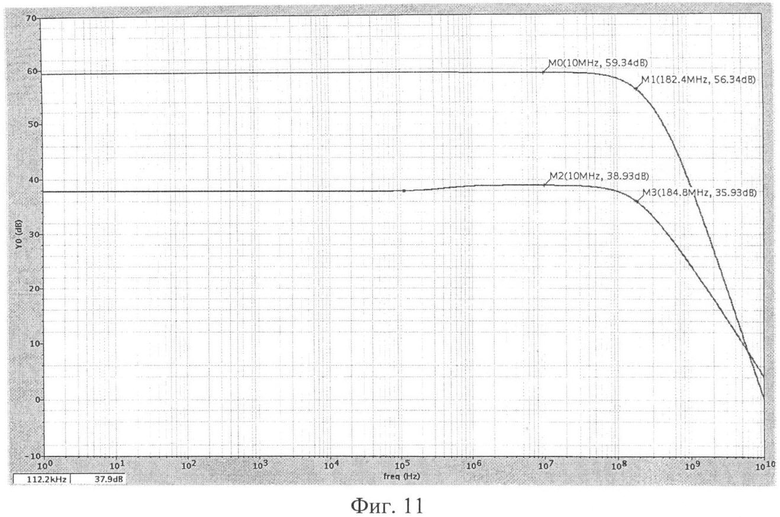

На фиг.9 и 10 показаны схемы ДУ-прототипа (фиг.9) и заявляемого ДУ (фиг.10) в среде компьютерного моделирования Cadence на моделях интегральных СВЧ-транзисторов IHP для случая, когда в ДУ используется симметричное включение низкоомной нагрузки (50 Ом), а на фиг.11 - зависимость Ky сравниваемых схем (фиг.9, 10) от частоты. Графики фиг.11 показывают, что предлагаемое устройство имеет в 9-10 раз больший коэффициент усиления по напряжению (≈20 дБ) при практически одинаковых значениях верхней граничной частоты (182 МГц). Это важное достоинство предлагаемого ДУ при его реализации в рамках технологического процесса SGB25VD.

Дифференциальный усилитель, фиг.2, содержит входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с базами первого 4 и второго 5 выходных транзисторов, первый 6 и второй 7 двухполюсники нагрузки, выходной транзистор стабилизатора тока 8, коллектор которого соединен с общей эмиттерной цепью 9 входного параллельно-балансного каскада 1, вспомогательный двухполюсник 10, включенный параллельно эмиттерно-базовому переходу выходного транзистора стабилизатора тока 8, первый 11 и второй 12 резисторы обратной связи, первые выводы которых подключены к эмиттерам соответствующих первого 4 и второго 5 выходных транзисторов, а также первому 13 и второму 14 противофазным выходам дифференциального усилителя, а вторые выводы связаны с базой выходного транзистора стабилизатора тока 8. В схему введены первый 15 и второй 16 дополнительные транзисторы, а также первый 17 и второй 18 дополнительные двухполюсники, база первого 4 выходного транзистора соединена с первым 6 двухполюсником нагрузки и базой второго 16 дополнительного транзистора через первый дополнительный двухполюсник 17, база второго 5 выходного транзистора соединена со вторым 7 двухполюсником нагрузки и базой первого 15 дополнительного транзистора через второй 18 дополнительный двухполюсник, коллектор первого 4 выходного транзистора соединен с эмиттером первого 15 дополнительного транзистора, коллектор второго 5 выходного транзистора соединен с эмиттером второго 16 дополнительного транзистора, причем коллекторы первого 15 и второго 16 дополнительных транзисторов связаны с шиной источника питания.

В частном случае входной параллельно-балансный каскад 1 в схеме фиг.2 реализован на транзисторах 19 и 20, а нагрузка 21 (Rн), имеет симметричное включение.

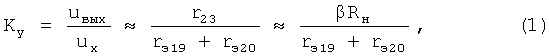

Коэффициент усиления по напряжению ДУ-прототипа, фиг.1, зависит от сопротивления нагрузки r23 между выходами 2 и 3:

где β4=β5=β3 - коэффициент усиления по току базы транзисторов 4 и 5;

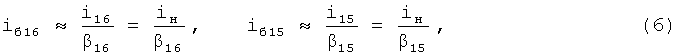

- сопротивление эмиттерных p-n переходов транзисторов входного параллельно-балансного каскада 1;

- сопротивление эмиттерных p-n переходов транзисторов входного параллельно-балансного каскада 1;

I0=Iк8/2=I6=I7 - статический ток двухполюсников нагрузки 6 и 7;

φт=26 мВ - температурный потенциал.

После преобразований (1) можно получить, что в схеме фиг.1

При Rн=50 Ом, β=60 численные значения Ky<60, что недостаточно во многих практических случаях.

Рассмотрим работу предлагаемого устройства, фиг.2.

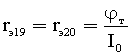

Статический режим по току транзисторов ДУ, фиг.2, устанавливается двухполюсниками нагрузки 6 и 7:

где Iкi - коллекторный ток i-го транзистора;

I0 - статический ток двухполюсников 6 и 7.

Сравнительно низкоомные резисторы 11 и 12 определяют статический режим по напряжению коллектор-база транзисторов входного параллельно-балансного каскада 1.

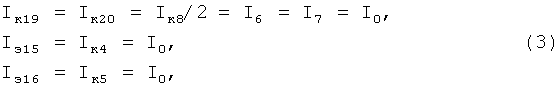

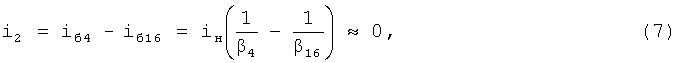

Если на вход ДУ, фиг.2, подается напряжение uвх, то это приводит к изменениям напряжений u2 и u3 на выходах 2 и 3, появлению тока iн в нагрузке 21 и токов базы транзисторов 4 и 5, 15 и 16:

где βi - коэффициент усиления по току базы i-го транзистора;

iэj - ток эмиттера j-го транзистора.

Поэтому суммарные приращения приведенных токов нагрузки в цепях выходов 2 и 3:

При β4=β16, β5=β15 получаем, что в коллекторной цепи входного каскада 1 обеспечивается компенсация близких по величине переменных токов, обусловленных низкоомной нагрузкой, что существенно повышает эквивалентное сопротивление между выходами 2 и 3 и, как следствие, коэффициент усиления по напряжению ДУ, фиг.2.

В практических схемах фиг.4, 7 и 10 выигрыш по Ky достигает одного порядка (фиг.5, 8 и 11). Следует заметить, что данный положительный эффект достигается без увеличения статического тока, потребляемого схемой от источников питания. Предлагаемая схема может быть реализована в рамках техпроцесса SGB25VD, внедряемого российскими предприятиями.

Таким образом, заявляемый дифференциальный усилитель при малом токопотреблении обеспечивает при низкоомной нагрузке Rн=50 Ом повышенный Ky, а также реализуется на основе техпроцесса SGB25VD, в котором нет p-n-p транзисторов. Это весьма существенные преимущества.

Источники информации

1. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / Под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007. - С.106-110.

2. S.P.Voinigescu, et al., "Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth," IEEE CSICS, Techn. Digest, pp.283-286, Nov. 2005, фиг.2.

3. S.P. Voinigescu, et al, "SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz," IEEE BCTM, pp.1-8, Oct. 2006.

4. Патент США №4.274.394, фиг.2.

5. Патент США №3.619.797.

6. Патент США №3.622.902.

7. Патент США №3.440.554.

8. А.св. СССР №299013.

9. Патент Англии №1.175.329, Н3Т.

10. Патент США №3.304.512.

11. Патент США №4.371.93.

12. А.св. СССР №421105.

13. А.св. СССР №764100.

14. А.св. СССР №669471.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421887C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2391769C1 |

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416146C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421890C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2007 |

|

RU2364020C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2008 |

|

RU2368067C1 |

Изобретение относится к области радиотехники и связи для усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, СВЧ операционных усилителях (ОУ), компараторах). Технический результат: увеличение коэффициента усиления по напряжению при низкоомной нагрузке. Дифференциальный усилитель (ДУ) содержит входной параллельно-балансный каскад (ПБК) (1), первый (2) и второй (3) токовые выходы которого связаны с базами первого (4) и второго (5) выходных транзисторов (Т), первый (6) и второй (7) двухполюсники нагрузки (ДН), выходной Т (8) стабилизатора тока, коллектор которого соединен с общей эмиттерной цепью (9) входного ПБК (1), вспомогательный двухполюсник (Д) (10), включенный параллельно эмиттерно-базовому переходу Т (8) стабилизатора тока, первый (11) и второй (12) резисторы обратной связи, первые выводы которых подключены к эмиттерам соответствующих первого (4) и второго (5) выходных Т, а также первому (13) и второму (14) противофазным выходам ДУ, а вторые выводы связаны с базой выходного Т (8) стабилизатора тока. В схему введены первый (15) и второй (16) дополнительные Т, а также первый (17) и второй (18) дополнительные Д, база Т (4) соединена с первым ДН (6) и базой Т (16) через первый (17) дополнительный Д, база Т (5) соединена со вторым ДН (7) и базой Т (15) через второй (18) дополнительный Д, коллектор Т (4) соединен с эмиттером Т (15), коллектор Т (5) соединен с эмиттером Т (16), причем коллекторы Т (15, 16) связаны с шиной источника питания. 11 ил.

Дифференциальный усилитель с парафазным выходом, содержащий входной параллельно-балансный каскад, первый и второй токовые выходы которого связаны с базами первого и второго выходных транзисторов, первый и второй двухполюсники нагрузки, выходной транзистор стабилизатора тока, коллектор которого соединен с общей эмиттерной цепью входного параллельно-балансного каскада, вспомогательный двухполюсник, включенный параллельно эмиттерно-базовому переходу выходного транзистора стабилизатора тока, первый и второй резисторы обратной связи, первые выводы которых подключены к эмиттерам соответствующих первого и второго выходных транзисторов, а также первому и второму противофазным выходам дифференциального усилителя, а вторые выводы связаны с базой выходного транзистора стабилизатора тока, отличающийся тем, что в схему введены первый и второй дополнительные транзисторы, а также первый и второй дополнительные двухполюсники, база первого выходного транзистора соединена с первым двухполюсником нагрузки и базой второго дополнительного транзистора через первый дополнительный двухполюсник, база второго выходного транзистора соединена со вторым двухполюсником нагрузки и базой первого дополнительного транзистора через второй дополнительный двухполюсник, коллектор первого выходного транзистора соединен с эмиттером первого дополнительного транзистора, коллектор второго выходного транзистора соединен с эмиттером второго дополнительного транзистора, причем коллекторы первого и второго дополнительных транзисторов связаны с шиной источника питания.

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2007 |

|

RU2364020C1 |

| US 7272728 A, 09.06.1981 | |||

| US 4007427 A, 08.02.1977 | |||

| US 3959733 A, 25.05.1976. | |||

Авторы

Даты

2011-02-27—Публикация

2009-10-12—Подача