Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) с дифференциальным выходом, компараторах, СВЧ-усилителях, фильтрах, драйверах линий связи и т.п.).

Известны схемы классических дифференциальных усилителей (ДУ) [1-14] с отрицательной обратной связью по синфазному сигналу, которые стали основой многих серийных аналоговых микросхем первого и второго поколений.

В последние годы ДУ данного класса стали снова активно применяться в структуре СВЧ-устройств [1, 2, 3], реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1) В, которое характерно для SiGe транзисторов с предельными частотами 120÷160 ГГц.

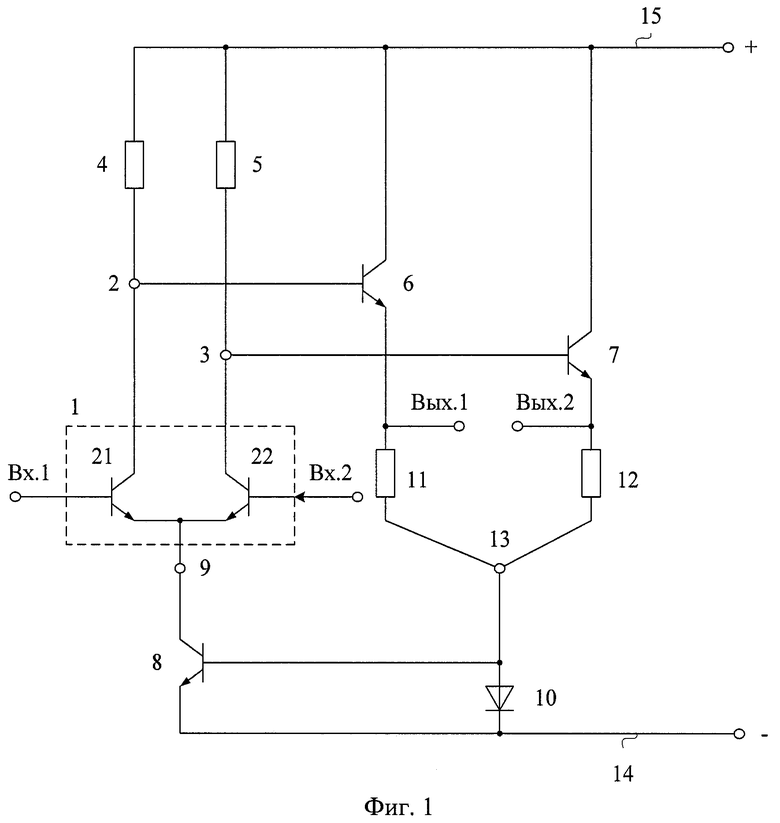

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте RU 2346382, содержащий входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с первыми выводами соответствующих первого 4 и второго 5 резисторов коллекторной нагрузки и базами первого 6 и второго 7 выходных транзисторов, выходной транзистор стабилизатора тока 8, коллектор которого соединен с общей эмиттерной цепью 9 входного параллельно-балансного каскада 1, а база связана с первым выводом вспомогательного прямосмещенного р-n перехода 10, первый 11 и второй 12 резисторы обратной связи, имеющие общий узел 13, подключенные к эмиттерам соответствующих первого 6 и второго 7 выходных транзисторов и первому и второму противофазным выходам дифференциального усилителя, причем общий узел 13 первого 11 и второго 12 резисторов обратной связи соединен с базой выходного транзистора стабилизатора тока 8, второй вывод вспомогательного прямосмещенного р-n перехода 10 и эмиттер выходного транзистора стабилизатора тока 8 соединены с первой 14 шиной источников питания, а коллекторы первого 6 и второго 7 выходных транзисторов связаны со второй 15 шиной источников питания.

Существенный недостаток известного ДУ фиг.1 (патент RU 2346382), архитектура которого присутствует также в других усилительных каскадах [1-14], состоит в том, что при ограничениях на напряжение питания (En), характерных для SiGe технологических процессов (En≤2,0÷2,5 В), его коэффициент усиления по напряжению (Ку) получается небольшим (Куmах=10÷20). В первую очередь, это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными. Поэтому для повышения Ку применяются так называемые динамические нагрузки (ДН), например, на биполярных транзисторах, которые требуют для обеспечения линейного режима работы 0,8÷1,6 В статического напряжения UДН между источником питания и выходом ДН. Причем численные значения UДН равны 0,8 В для простейших динамических нагрузок, имеющих, к сожалению, невысокое выходное дифференциальное сопротивление

,

,

где UЭрли - напряжение Эрли выходного р-n-р транзистора ДН;

Iэ=I0 - статический ток эмиттера р-n-р выходного транзистора ДН.

Для интегральных транзисторов ФГУП НПП «Пульсар», а также некоторых SiGe p-n-p транзисторов IHP и UЭрли=20÷30 В. Следовательно, при I0=1 мА применение классических динамических нагрузок не позволяет получить Ку>200÷300.

Более высокие выходные сопротивления RДН реализуются в токовых зеркалах Вильсона или каскодных схемах. Однако они работают только в том случае, когда статическое напряжение между выводами такой динамической нагрузки более чем 2Uэб≥1,6 В. При низковольтном питании это неприемлемо.

Таким образом, при малых напряжениях питания, а особенно в тех случаях, когда требуется получить более-менее значительные амплитуды выходного напряжения, классические схемотехнические решения ДУ неэффективны.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления по напряжению при низковольтном питании.

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с первыми выводами соответствующих первого 4 и второго 5 резисторов коллекторной нагрузки и базами первого 6 и второго 7 выходных транзисторов, выходной транзистор стабилизатора тока 8, коллектор которого соединен с общей эмиттерной цепью 9 входного параллельно-балансного каскада 1, а база связана с первым выводом вспомогательного прямосмещенного р-n перехода 10, первый 11 и второй 12 резисторы обратной связи, имеющие общий узел 13, подключенные к эмиттерам соответствующих первого 6 и второго 7 выходных транзисторов и первому и второму противофазным выходам дифференциального усилителя, причем общий узел 13 первого 11 и второго 12 резисторов обратной связи соединен с базой выходного транзистора стабилизатора тока 8, второй вывод вспомогательного прямосмещенного р-n перехода 10 и эмиттер выходного транзистора стабилизатора тока 8 соединены с первой 14 шиной источников питания, а коллекторы первого 6 и второго 7 выходных транзисторов связаны со второй 15 шиной источников питания, предусмотрены новые элементы и связи - в схему введены первый 16 и второй 17 дополнительные транзисторы, коллектор первого 16 дополнительного транзистора связан с первым 2 токовым выходом входного параллельно-балансного каскада 1, коллектор второго 17 дополнительного транзистора связан со вторым 3 токовым выходом входного параллельно-балансного каскада 1, второй вывод первого 4 резистора коллекторной нагрузки через первый 18 дополнительный двухполюсник соединен со второй 15 шиной источника питания и эмиттером первого 16 дополнительного транзистора, второй вывод второго 5 резистора коллекторной нагрузки через второй 19 дополнительный двухполюсник соединен со второй 15 шиной источника питания и эмиттером второго 17 дополнительного транзистора, причем базы первого 16 и второго 17 дополнительных транзисторов соединены с цепью смещения потенциалов 20.

Схема ДУ-прототипа показана на фиг.1.

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.2 и п.3 формулы изобретения.

На фиг.3 показана схема дифференциального усилителя-прототипа, а на фиг.4 - заявляемого ДУ фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW.

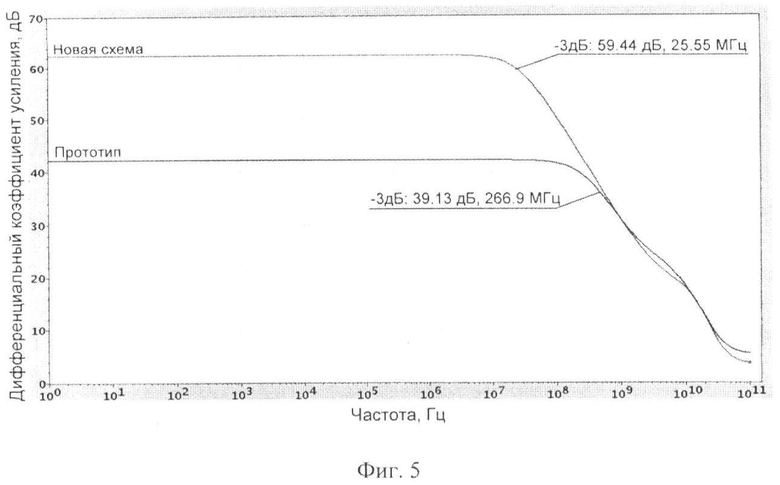

На фиг.5 приведены амплитудно-частотные характеристики сравниваемых схем фиг.3, фиг.4.

На фиг.6 приведена схема заявляемого устройства в соответствии с п.4 формулы изобретения.

На фиг.7 показана схема заявляемого устройства в соответствии с п.5 формулы изобретения.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с первыми выводами соответствующих первого 4 и второго 5 резисторов коллекторной нагрузки и базами первого 6 и второго 7 выходных транзисторов, выходной транзистор стабилизатора тока 8, коллектор которого соединен с общей эмиттерной цепью 9 входного параллельно-балансного каскада 1, а база связана с первым выводом вспомогательного прямосмещенного р-n перехода 10, первый 11 и второй 12 резисторы обратной связи, имеющие общий узел 13, подключенные к эмиттерам соответствующих первого 6 и второго 7 выходных транзисторов и первому и второму противофазным выходам дифференциального усилителя, причем общий узел 13 первого 11 и второго 12 резисторов обратной связи соединен с базой выходного транзистора стабилизатора тока 8, второй вывод вспомогательного прямосмещенного р-n перехода 10 и эмиттер выходного транзистора стабилизатора тока 8 соединены с первой 14 шиной источников питания, а коллекторы первого 6 и второго 7 выходных транзисторов связаны со второй 15 шиной источников питания. В схему введены первый 16 и второй 17 дополнительные транзисторы, коллектор первого 16 дополнительного транзистора связан с первым 2 токовым выходом входного параллельно-балансного каскада 1, коллектор второго 17 дополнительного транзистора связан со вторым 3 токовым выходом входного параллельно-балансного каскада 1, второй вывод первого 4 резистора коллекторной нагрузки через первый 18 дополнительный двухполюсник соединен со второй 15 шиной источника питания и эмиттером первого 16 дополнительного транзистора, второй вывод второго 5 резистора коллекторной нагрузки через второй 19 дополнительный двухполюсник соединен со второй 15 шиной источника питания и эмиттером второго 17 дополнительного транзистора, причем базы первого 16 и второго 17 дополнительных транзисторов соединены с цепью смещения потенциалов 20.

Кроме этого, на фиг.2, в соответствии с п.2 формулы изобретения, цепь смещения потенциалов 20 содержит вспомогательный источник напряжения 21, связанный с базами первого 16 и второго 17 дополнительных транзисторов. Входной дифференциальный каскад 1 реализован на транзисторах 22 и 23.

Далее, на фиг.2, в соответствии с п.3 формулы изобретения, первый 18 и второй 19 дополнительные двухполюсники выполнены в виде резисторов.

На фиг.6, в соответствии с п.4 формулы изобретения, первый 18 и второй 19 дополнительные двухполюсники выполнены в виде двух р-n переходов, причем цепь смещения потенциалов 20 содержит первый 24 и второй 25 вспомогательные источники опорного тока, каждый из которых соединен с базами соответствующего первого 16 и второго 17 дополнительных транзисторов и коллекторами соответствующих первого 26 и второго 27 вспомогательных транзисторов, причем база первого 26 вспомогательного транзистора связана с эмиттером первого 16 дополнительного транзистора, база второго 27 вспомогательного транзистора соединена с эмиттером второго 17 дополнительного транзистора, а эмиттеры первого 26 и второго 27 вспомогательных транзисторов связаны со второй 15 шиной источника питания.

На фиг.7, в соответствии с п.5 формулы изобретения, коллектор первого 16 дополнительного транзистора связан с первым 2 токовым выходом входного параллельно-балансного каскада 1 через первый 28 дополнительный прямосмещенный р-n переход и через первый 29 дополнительный источник тока соединен с первой 14 шиной источника питания, коллектор второго 17 дополнительного транзистора связан со вторым 3 токовым выходом входного параллельно-балансного каскада 1 через второй 30 дополнительный прямосмещенный р-n переход и через второй 31 дополнительный источник тока соединен с первой 14 шиной источника питания.

Рассмотрим работу ДУ фиг.2.

Статический режим по току транзисторов предлагаемого ДУ фиг.2 устанавливается дополнительными двухполюсниками (резисторами) 18 и 19, цепью смещения потенциалов 20, а также сравнительно низкоомными резисторами 11 и 12

где I0 - заданный статический ток (например, 0,5 мА);

Iкi - коллекторный ток 1-го транзистора;

I2=I3 - статические токи в цепи первого 2 и второго 3 токовых выходов входного дифференциального каскада 1;

IR4=IR5 - статические токи через резисторы коллекторной нагрузки 4 и 5.

Статические напряжения на токовых выходах 2 и 3 относительно первой 14 шины источников питания определяются уравнениями

где Uэб.б≈Ud.10≈0,7 В - напряжение на р-n переходах транзистора 6 и прямосмещенного р-n перехода 10.

Таким образом, за счет выбора сопротивления R11=R12 резисторов обратной связи 11 и 12 можно обеспечить заданный статический режим по напряжению на токовых выходах 2 и 3 входного дифференциального каскада 1.

При отрицательном входном напряжении uвх<0 напряжение на токовом выходе 2 (u2) увеличивается, а на токовом выходе 3 - уменьшается. Это приводит к изменению токов iR4 и iR5 через резисторы коллекторной нагрузки 4 и 5, а затем соответствующих токов эмиттера и коллектора транзисторов 16 и 17. Как следствие, суммарный переменный ток в цепи токовых выходов 2 и 3 не изменяется, что эквивалентно умножению эффективного значения сопротивления резисторов коллекторной нагрузки 4 и 5

где α16, α17=0,98-0,99 - коэффициент передачи по току эмиттера транзисторов 16 и 17.

Поэтому коэффициент усиления по напряжению ДУ фиг.2, несмотря на сравнительно малые значения R4 и R5, возрастает на 20 дБ, т.е. в 10 раз. Данные выводы подтверждаются графиками фиг.5.

Основная цель модернизации предлагаемого ДУ по п.4 формулы изобретения (фиг.6) - дальнейшее повышение коэффициента усиления по напряжению Ку в сравнении с ДУ фиг.2 за счет более рационального построения цепи смещения потенциалов 20. Данное техническое решение обеспечивает дополнительное повышение Ку на 8÷16 дБ в сравнении со схемой фиг.2 за счет более полной передачи токов iR5, iR4 в узлы «А» и «В».

Построение ДУ по п.4 формулы изобретения (фиг.6) может сопровождаться дополнительным ограничением на минимально возможное напряжение питания  . От этого недостатка свободна более перспективная схема ДУ фиг.7 (п.5 формулы изобретения), в которой за счет новых элементов и связей между ними реализуется не только повышенное (в сравнении с фиг.2) усиление, но и экстремально низкое напряжение питания. Действительно, в сравнении со схемой фиг.6 минимальное напряжение питания

. От этого недостатка свободна более перспективная схема ДУ фиг.7 (п.5 формулы изобретения), в которой за счет новых элементов и связей между ними реализуется не только повышенное (в сравнении с фиг.2) усиление, но и экстремально низкое напряжение питания. Действительно, в сравнении со схемой фиг.6 минимальное напряжение питания  в данной схеме на U28=U30=0,7÷0,8 В меньше, где U28=U30 - напряжения на прямосмещенных р-n переходах 28, 30.

в данной схеме на U28=U30=0,7÷0,8 В меньше, где U28=U30 - напряжения на прямосмещенных р-n переходах 28, 30.

Таким образом, предлагаемый дифференциальный усилитель имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст]. / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: Сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков. / Под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007. - С.106-110.

2. S.P.Voinigescu, et al., "Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth," IEEE CSICS, Techn. Digest, pp.283-286, Nov. 2005, фиг.2.

3. S.P. Voinigescu, et al., "SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz," IEEE BCTM, pp.1-8, Oct. 2006.

4. Патент США №4.274.394, фиг.2.

5. Патент США №3.619.797.

6. Патент США №3.622.902.

7. Патент США №3.440.554.

8. А.св. СССР №299013.

9. Патент Англии №1.175.329, Н3Т.

10. Патент США №3.304.512.

11. Патент США №4.371.93.

12. А.св. СССР №421105.

13. А.св. СССР №764100.

14. А.св. СССР №669471.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2012 |

|

RU2519544C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2009 |

|

RU2413355C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2504896C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432666C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМИ ВХОДНЫМИ ТРАНЗИСТОРАМИ | 2010 |

|

RU2423779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432665C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346386C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) с дифференциальным выходом, компараторах, СВЧ-усилителях, фильтрах и драйверах линий связи). Технический результат: повышение коэффициента усиления по напряжению при низковольтном питании. Дифференциальный усилитель с парафазным выходом содержит входной параллельно-балансный каскад (1), первый (2) и второй (3) токовые выходы которого связаны с первыми выводами соответствующих первого (4) и второго (5) резисторов коллекторной нагрузки и базами первого (6) и второго (7) выходных транзисторов, выходной транзистор стабилизатора тока (8), коллектор которого соединен с общей эмиттерной цепью (9) входного параллельно-балансного каскада (1), а база связана с первым выводом вспомогательного прямосмещенного p-n перехода (10), первый (11) и второй (12) резисторы обратной связи, имеющие общий узел (13), подключенные к эмиттерам соответствующих первого (6) и второго (7) выходных транзисторов и первому и второму противофазным выходам дифференциального усилителя, причем общий узел (13) первого (11) и второго (12) резисторов обратной связи соединен с базой выходного транзистора стабилизатора тока (8), второй вывод вспомогательного прямосмещенного p-n перехода (10) и эмиттер выходного транзистора стабилизатора тока (8) соединены с первой (14) шиной источников питания, а коллекторы первого (6) и второго (7) выходных транзисторов связаны со второй (15) шиной источников питания. В схему введены первый (16) и второй (17) дополнительные транзисторы, коллектор первого (16) дополнительного транзистора связан с первым (2) токовым выходом входного параллельно-балансного каскада (1), коллектор второго (17) дополнительного транзистора связан со вторым (3) токовым выходом входного параллельно-балансного каскада (1), второй вывод первого (4) резистора коллекторной нагрузки через первый (18) дополнительный двухполюсник соединен со второй (15) шиной источника питания и эмиттером первого (16) дополнительного транзистора, второй вывод второго (5) резистора коллекторной нагрузки через второй (19) дополнительный двухполюсник соединен со второй (15) шиной источника питания и эмиттером второго (17) дополнительного транзистора, причем базы первого (16) и второго (17) дополнительных транзисторов соединены с цепью смещения потенциалов (20). 4 з.п. ф-лы, 7 ил.

1. Дифференциальный усилитель с парафазным выходом, содержащий входной параллельно-балансный каскад (1), первый (2) и второй (3) токовые выходы которого связаны с первыми выводами соответствующих первого (4) и второго (5) резисторов коллекторной нагрузки и базами первого (6) и второго (7) выходных транзисторов, выходной транзистор стабилизатора тока (8), коллектор которого соединен с общей эмиттерной цепью (9) входного параллельно-балансного каскада (1), а база связана с первым выводом вспомогательного прямосмещенного p-n перехода (10), первый (11) и второй (12) резисторы обратной связи, имеющие общий узел (13), подключенные к эмиттерам соответствующих первого (6) и второго (7) выходных транзисторов и первому и второму противофазным выходам дифференциального усилителя, причем общий узел (13) первого (11) и второго (12) резисторов обратной связи соединен с базой выходного транзистора стабилизатора тока (8), второй вывод вспомогательного прямосмещенного p-n перехода (10) и эмиттер выходного транзистора стабилизатора тока (8) соединены с первой (14) шиной источников питания, а коллекторы первого (6) и второго (7) выходных транзисторов связаны со второй (15) шиной источников питания, отличающийся тем, что в схему введены первый (16) и второй (17) дополнительные транзисторы, коллектор первого (16) дополнительного транзистора связан с первым (2) токовым выходом входного параллельно-балансного каскада (1), коллектор второго (17) дополнительного транзистора связан со вторым (3) токовым выходом входного параллельно-балансного каскада (1), второй вывод первого (4) резистора коллекторной нагрузки через первый (18) дополнительный двухполюсник соединен со второй (15) шиной источника питания и эмиттером первого (16) дополнительного транзистора, второй вывод второго (5) резистора коллекторной нагрузки через второй (19) дополнительный двухполюсник соединен со второй (15) шиной источника питания и эмиттером второго (17) дополнительного транзистора, причем базы первого (16) и второго (17) дополнительных транзисторов соединены с цепью смещения потенциалов (20).

2. Дифференциальный усилитель с парафазным выходом по п.1, отличающийся тем, что цепь смещения потенциалов (20) содержит вспомогательный источник напряжения (21), связанный с базами первого (16) и второго (17) дополнительных транзисторов.

3. Дифференциальный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (18) и второй (19) дополнительные двухполюсники выполнены в виде резисторов.

4. Дифференциальный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (18) и второй (19) дополнительные двухполюсники выполнены в виде двух p-n переходов, причем цепь смещения потенциалов (20) содержит первый (24) и второй (25) вспомогательные источники опорного тока, каждый из которых соединен с базами соответствующего первого (16) и второго (17) дополнительных транзисторов и коллекторами соответствующих первого (26) и второго (27) вспомогательных транзисторов, причем база первого (26) вспомогательного транзистора связана с эмиттером первого (16) дополнительного транзистора, база второго (27) вспомогательного транзистора соединена с эмиттером второго (17) дополнительного транзистора, а эмиттеры первого (26) и второго (27) вспомогательных транзисторов связаны со второй (15) шиной источника питания.

5. Дифференциальный усилитель с парафазным выходом по п.4, отличающийся тем, что коллектор первого (16) дополнительного транзистора связан с первым (2) токовым выходом входного параллельно-балансного каскада (1) через первый (28) дополнительный прямосмещенный p-n переход и через первый (29) дополнительный источник тока соединен с первой (14) шиной источника питания, коллектор второго (17) дополнительного транзистора связан со вторым (3) токовым выходом входного параллельно-балансного каскада (1) через второй (30) дополнительный прямосмещенный p-n переход и через второй (31) дополнительный источник тока соединен с первой (14) шиной источника питания.

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2006 |

|

RU2321160C1 |

| Операционный усилитель | 1983 |

|

SU1259472A1 |

| US 4959622 A, 25.09.1990 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

Авторы

Даты

2011-06-20—Публикация

2010-05-27—Подача