Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-операционных усилителях (ОУ), компараторах).

Известны схемы классических дифференциальных усилителей (ДУ) [1-14] с отрицательной обратной связью по синфазному сигналу, которые стали основой многих серийных аналоговых микросхем первого и второго поколения.

В последние годы ДУ данного класса стали снова активно применяться в структуре СВЧ-устройств [1, 2, 3], реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1)В, которое характерно для высокочастотных транзисторов с предельными частотами 20÷60 ГГц.

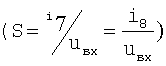

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в статье [2], содержащий входной параллельно-балансный каскад 1, общая эмиттерная цепь 2 которого соединена с выходом 3 первого токового зеркала 4, первый 5 и второй 6 двухполюсники нагрузки, подключенные к первому 7 и второму 8 выходам входного параллельно-балансного каскада 1 и базам первого 9 и второго 10 выходных транзисторов, первый согласующий резистор 11, включенный между эмиттером первого выходного транзистора 9 и входом 12 первого токового зеркала 4, второй согласующий резистор 13, первый вывод которого связан с эмиттером второго 10 выходного транзистора.

Существенный недостаток известного ДУ состоит в том, что статический потенциал его выходов не согласован с шинами питания, что затрудняет прямое подключение к этим выходам дополнительных каскадов усиления, в частности реализующих функцию rail-to-rail. Кроме этого, в известной схеме ДУ невозможно реализовать токовые выходы, «привязанные» к разным шинам источников питания. Это значительно сужает области применения известных схем, не позволяет выполнять на его основе широкополосные усилители со специфическими функциями (rail-to-rail, интеграторы, компараторы и т.д.).

Основная цель предлагаемого изобретения состоит в решении проблемы согласования статических потенциалов выходов ДУ фиг.1 с шиной источника питания и построения мультивыходного дифференциального усилителя (имеющего шесть выходов) с широким спектром технических характеристик.

Дополнительная цель - в увеличении максимального уровня выходного тока дифференциального усилителя Iн.max в широком диапазоне изменения выходного напряжения.

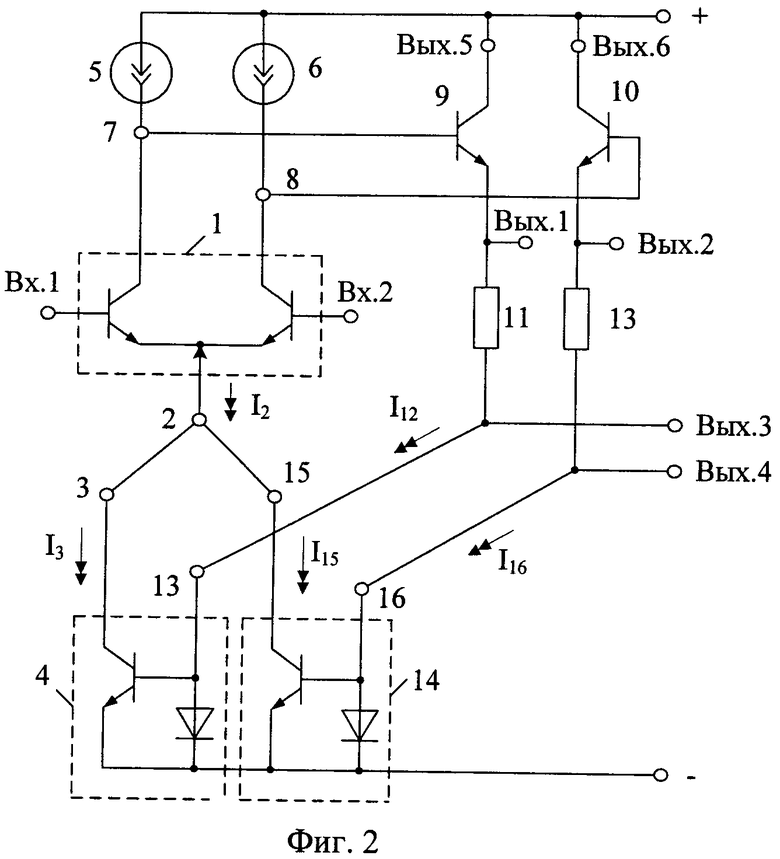

Поставленная цель достигается тем, что в дифференциальном усилителе, фиг.1, содержащем входной параллельно-балансный каскад 1, общая эмиттерная цепь 2 которого соединена с выходом 3 первого токового зеркала 4, первый 5 и второй 6 двухполюсники нагрузки, подключенные к первому 7 и второму 8 выходам входного параллельно-балансного каскада 1 и базам первого 9 и второго 10 выходных транзисторов, первый согласующий резистор 11, включенный между эмиттером первого выходного транзистора 9 и входом 12 первого токового зеркала 4, второй согласующий резистор 13, первый вывод которого связан с эмиттером второго 10 выходного транзистора, предусмотрены новые элементы и связи - в схему введено второе токовое зеркало 14, выход которого 15 подключен к общей эмиттерной цепи 2 входного параллельно-балансного каскада 1, а вход 16 соединен со вторым выводом второго 13 согласующего резистора (фиг.2).

Схема заявляемого устройства, соответствующего п.1 - п.5 формулы изобретения, показана на фиг.2.

На фиг.3 показана схема заявляемого устройства в соответствии с п.6 формулы изобретения.

На фиг.4 показана схема предлагаемого ДУ по п.7 формулы изобретения.

На фиг.5 показана схема предлагаемого устройства по п.8 и п.9 формулы изобретения.

На фиг.6 показана схема заявляемого ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НИН «Пульсар», соответствующая п.8 формулы изобретения (или фиг.5).

На фиг.7 показана зависимость выходного тока заявляемого ДУ (фиг.6) от входного напряжения.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, общая эмиттерная цепь 2 которого соединена с выходом 3 первого токового зеркала 4, первый 5 и второй 6 двухполюсники нагрузки, подключенные к первому 7 и второму 8 выходам входного параллельно-балансного каскада 1 и базам первого 9 и второго 10 выходных транзисторов, первый согласующий резистор 11, включенный между эмиттером первого выходного транзистора 9 и входом 12 первого токового зеркала 4, второй согласующий резистор 13, первый вывод которого связан с эмиттером второго 10 выходного транзистора. В схему введено второе токовое зеркало 14, выход которого 15 подключен к общей эмиттерной цепи 2 входного параллельно-балансного каскада 1, а вход 16 соединен со вторым выводом второго 13 согласующего резистора (фиг.2).

В частном случае (п.2 - п.5 формулы изобретения) в качестве основных противофазных потенциальных выходов используются входы 12 и 16 первого 4 и второго 14 токовых зеркал (фиг.2). В другом частном случае в качестве вспомогательных противофазных потенциальных выходов используются эмиттеры первого 9 и второго 10 выходных транзисторов (фиг.2). В качестве первой группы дополнительных противофазных выходов могут также использоваться коллектор первого выходного транзистора 9 и вход 16 второго 14 токового зеркала (фиг.2). В частном случае в качестве второй группы дополнительных противофазных выходов используются коллектор второго выходного транзистора 10 и вход 12 первого токового зеркала 4 (фиг.2).

В дифференциальном усилителе, соответствующем п.6 формулы изобретения (фиг.3), коллектор первого выходного транзистора 9 соединен со входом первого дополнительного токового зеркала 17, а вход 16 второго токового зеркала 4 подключен к базе первого дополнительного транзистора 18, причем выход первого дополнительного токового зеркала 17 соединен с коллектором первого дополнительного транзистора 18 и выходом 19 дифференциального усилителя.

В дифференциальном усилителе, соответствующем п.7 формулы изобретения (фиг.4), вход 12 первого 4 токового зеркала связан с базой первого 20 вспомогательного транзистора, вход 16 второго 14 токового зеркала подключен к базе второго вспомогательного транзистора 21, коллектор первого 20 вспомогательного транзистора соединен со входом второго 22 дополнительного токового зеркала, выход которого связан с коллектором второго 21 вспомогательного транзистора и выходом 23 дифференциального усилителя (фиг.4).

В дифференциальном усилителе, соответствующем п.8 формулы изобретения (фиг.5), коллектор второго выходного транзистора 10 соединен со входом третьего 24 дополнительного токового зеркала, а вход 12 первого токового зеркала 4 подключен к базе третьего 25 вспомогательного транзистора, причем выход третьего 24 дополнительного токового зеркала соединен с коллектором третьего 25 вспомогательного транзистора и выходом 26 дифференциального усилителя (фиг.5).

В дифференциальном усилителе, соответствующем п.9 формулы изобретения (фиг.5), в схему введено четвертое дополнительное токовое зеркало 27, четвертый 28 и пятый 29 вспомогательные транзисторы, причем выход четвертого дополнительного токового зеркала 27 соединен с выходом 26 дифференциального усилителя и выходом третьего 24 дополнительного токового зеркала, эмиттер четвертого дополнительного транзистора 28 соединен с базой пятого дополнительного транзистора 29 и эмиттером второго 10 выходного транзистора, база четвертого дополнительного транзистора 28 подключена к эмиттеру пятого 29 дополнительного транзистора и эмиттеру первого 9 выходного транзистора, а коллектор пятого 29 дополнительного транзистора соединен со входом четвертого 27 токового зеркала.

На фиг.9 представлена схема ДУ, фиг.3, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.10 - зависимость его выходного тока от входного напряжения.

На фиг.11 представлена схема ДУ, фиг.4, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НЛП «Пульсар», а на фиг.12 - зависимость его выходного тока от входного напряжения.

Рассмотрим работу заявляемого ДУ, фиг.2. Статический режим по току схемы ДУ, фиг.2, устанавливается двухполюсниками 5 и 6:

I2=I3+I15=I5+I6=const,

Iэ9=I12, Iэ10=I16,

UR11=I12R11, UR13=I16R13

Для получения максимального диапазона изменения выходного дифференциального напряжения необходимо выбирать

Uкб9≈UR11,

Uкб10≈UR13.

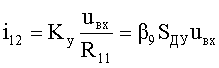

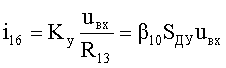

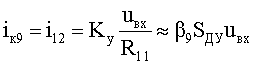

При положительном приращении напряжения на входе Вх.1 относительно входа 2 ток через резистор 13 увеличивается, а через резистор 11 уменьшается. Однако их сумма остается постоянной (I2=I5+I6=const). Выходное напряжение в узле 7 уменьшается на величину u7, а в узле 8 - увеличивается на u8=u7. При этом приращения токов на входах 12 и 16

,

,  ,

,

где u7=Ky7uвх,

u8=Ky8uвх,

Ky7=Ky8=Ky - коэффициенты усиления по напряжению со входов ДУ на выходы 7 и 8.

Причем

Ку≈β9R11SДУ≈β10R13SДУ>>1,

где β10 - коэффициент усиления по току базы транзисторов 9 и 10;

SДУ - крутизна входного каскада  .

.

Поэтому

,

,  .

.

Данные токи создают на входных сопротивлениях токовых зеркал 4 и 14 напряжения, которые выделяются на выходах Вых.3 и Вых.4 и передаются следующему каскаду (фиг.3, фиг.4).

Заметим, что при высокоомной нагрузке токи выходов Вых.5 и Вых.6

,

,

.

.

Это позволяет получить на данных выходах противофазные сигналы, которые могут сниматься и передаваться следующему каскаду (фиг.5, фиг.8). Следует заметить, что выход Вых.5 противофазен выходу Вых.4 и синфазен выходу Вых.3. В аналогичных фазовых соотношениях находятся выходы Вых.6, Вых.4, Вых.12.

На фиг.3 показана схема ДУ с функцией rail-to-rail, у которого выходные элементы 17 и 18 связаны с соответствующими выходами базовой схемы (фиг.2).

Показанная на фиг.4 схема иллюстрирует другой вариант подключения выходных элементов 20, 21, 22, обеспечивающих rail-to-rail каскад, ко входам 12 и 16 предлагаемого ДУ.

В схеме фиг.5 (фиг.6) вводится (за счет элементов 28, 29) нелинейная обратная связь, что позволяет получить на выходе 26 сравнительно большие токи в нагрузке при стабильном сквозном токе выходного каскада (фиг.7).

Полученные выше выводы подтверждаются результатами моделирования, фиг.7 (фиг.5, фиг.6) в среде PSpice - максимальный выходной ток данного ДУ в несколько десятков раз превышает максимальный выходной ток известного устройства и соответствующий статический ток выходных транзисторов. Такой режим характерен для усилителей класса АВ. Расширение диапазона изменения выходных токов ДУ в ДУ, фиг.6, без увеличения энергопотребления в статическом режиме позволяет увеличить быстродействие различных аналоговых устройств, работающих на емкостную нагрузку. Кроме этого, устройство (фиг.5, фиг.6) характеризуется предельно возможными значениями диапазона изменения выходного напряжения (от шины питания до шины питания), что характерно для усилителей класса rail-to-rail.

Проходные характеристики фиг.10 и фиг.12 показывают, что максимальный выходной ток ДУ фиг.9 и фиг.12 определяется статическим режимом выходных транзисторов, а этот режим характеризуется достаточно высокой стабильностью, которая зависит от токов двухполюсников 5 и 6.

Источники информации

1. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C, Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007 - С.106-110.

2. S.P.Voinigescu, et al., "Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth," IEEE CSICS, Techn. Digest, pp.283-286, Nov. 2005, фиг.2.

3. S.P.Voinigescu, et al., "SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz," IEEE BCTM, pp.1-8, Oct. 2006.

4. Патент США №4274394, фиг.2.

5. Патент США №3619797.

6. Патент США №3622902.

7. Патент США №3440554.

8. А.с. СССР №299013.

9. Патент Англии №1175329, Н3Т.

10. Патент США №3304512.

11. Патент США №437193.

12. Авт.св. СССР №421105.

13. Авт.св. СССР №764100.

14. Авт.св. СССР №669471.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2012 |

|

RU2519544C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2008 |

|

RU2346387C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346386C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2007 |

|

RU2331970C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат заключается в увеличении максимального уровня выходного тока в широком диапазоне изменения выходного напряжения. Дифференциальный усилитель (ДУ) содержит входной параллельно-балансный каскад (1), общая эмиттерная цепь (2) которого соединена с выходом (3) первого токового зеркала (4), первый (5) и второй (6) двухполюсники нагрузки, подключенные к первому (7) и второму (8) выходам входного каскада (1) и базам первого (9) и второго (10) выходных транзисторов, первый согласующий резистор (11), включенный между эмиттером первого выходного транзистора (9) и входом (12) первого токового зеркала (4), второй согласующий резистор (13), первый вывод которого связан с эмиттером второго (10) выходного транзистора. В схему введено второе токовое зеркало (14), выход которого (15) подключен к общей эмиттерной цепи (2) входного параллельно-балансного каскада (1), а вход (16) соединен со вторым выводом второго (13) согласующего резистора. 8 з.п. ф-лы, 12 ил.

1. Дифференциальный усилитель с отрицательной обратной связью по синфазному сигналу, содержащий входной параллельно-балансный каскад (1), общая эмиттерная цепь (2) которого соединена с выходом (3) первого токового зеркала (4), первый (5) и второй (6) двухполюсники нагрузки, подключенные к первому (7) и второму (8) выходам входного параллельно-балансного каскада (1) и базам первого (9) и второго (10) выходных транзисторов, первый согласующий резистор (11), включенный между эмиттером первого выходного транзистора (9) и входом (12) первого токового зеркала (4), второй согласующий резистор (13), первый вывод которого связан с эмиттером второго (10) выходного транзистора, отличающийся тем, что в схему введено второе токовое зеркало (14), выход которого (15) подключен к общей эмиттерной цепи (2) входного параллельно-балансного каскада (1), а вход (16) соединен со вторым выводом второго (13) согласующего резистора.

2. Устройство по п.1, отличающееся тем, что в качестве основных противофазных потенциальных выходов используются входы (12) и (16) первого (4) и второго (14) токовых зеркал.

3. Устройство по п.1, отличающееся тем, что в качестве вспомогательных противофазных потенциальных выходов используются эмиттеры первого (9) и второго (10) выходных транзисторов.

4. Устройство по п.1, отличающееся тем, что в качестве первой группы дополнительных противофазных выходов используются коллектор первого выходного транзистора (9) и вход (16) второго (14) токового зеркала.

5. Устройство по п.1, отличающееся тем, что в качестве второй группы дополнительных противофазных выходов используются коллектор второго выходного транзистора (10) и вход (12) первого токового зеркала (4).

6. Устройство по п.4, отличающееся тем, что коллектор первого выходного транзистора (9) соединен со входом первого дополнительного токового зеркала (17), а вход (16) второго токового зеркала (4) подключен к базе первого дополнительного транзистора (18), причем выход первого дополнительного токового зеркала (17) соединен с коллектором первого дополнительного транзистора (18) и выходом (19) дифференциального усилителя.

7. Устройство по п.2, отличающееся тем, что вход (12) первого (4) токового зеркала связан с базой первого (20) вспомогательного транзистора, вход (16) второго (14) токового зеркала подключен к базе второго вспомогательного транзистора (21), коллектор первого (20) вспомогательного транзистора соединен со входом второго (22) дополнительного токового зеркала, выход которого связан с коллектором второго (21) вспомогательного транзистора и выходом (23) дифференциального усилителя.

8. Устройство по п.5, отличающееся тем, что коллектор второго выходного транзистора (10) соединен со входом третьего (24) дополнительного токового зеркала, а вход (12) первого токового зеркала (4) подключен к базе третьего (25) вспомогательного транзистора, причем выход третьего (24) дополнительного токового зеркала соединен с коллектором третьего (25) вспомогательного транзистора и выходом (26) дифференциального усилителя.

9. Устройство по п.8, отличающееся тем, что в схему введено четвертое дополнительное токовое зеркало (27), четвертый (28) и пятый (29) вспомогательные транзисторы, причем выход четвертого дополнительного токового зеркала (27) соединен с выходом (26) дифференциального усилителя и выходом третьего (24) дополнительного токового зеркала, эмиттер четвертого дополнительного транзистора (28) соединен с базой пятого дополнительного транзистора (29) и эмиттером второго (10) выходного транзистора, база четвертого дополнительного транзистора (28) подключена к эмиттеру пятого (29) дополнительного транзистора и эмиттеру первого (9) выходного транзистора, а коллектор пятого (29) дополнительного транзистора соединен со входом четвертого (27) токового зеркала.

| VOINIQESCU S.P | |||

| et al | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| IEEE CSICS | |||

| Techn | |||

| Digest, pp.283-286, Nov | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Операционный усилитель | 1983 |

|

SU1259472A1 |

| Дифференциальный усилитель | 1982 |

|

SU1084964A1 |

| US 4105942 A, 08.08.1978. | |||

Авторы

Даты

2009-08-10—Публикация

2007-11-30—Подача