Изобретение относится к области электроники, а именно к цифроаналоговым преобразователям (ЦАП), и может применяться в цифровых радиопередатчиках.

Из уровня техники известны различные конструкции ЦАП, так, например, в патентах США №7,057,544 [1], 7,583,217 [2], 6,169,509 [3] описаны, в основном, преобразователи конденсаторного типа. Широкому применению таких ЦАП препятствует их невысокое быстродействие и значительное энергопотребление. Обзор отечественных и зарубежных ЦАП различной конструкции можно найти, например, в справочнике «Отечественные микросхемы и зарубежные аналоги». Перельман Б.Л., Шевеиев В.И. “НТЦ Микротех”, 1998 г., 376 с. [4].

Наиболее близким к заявленному изобретению является цифроаналоговый преобразователь, описанный в статье Моххамеда Реза Хассанзадеха, Джафара Талебзаден и Омида Шосай “Высокоскоростной, управляемый током цифроаналоговый преобразователь на основе 0.6 мкм КМОП технологии” (Page(s): 9-12 vol.1 Digital Object Identifier 10.1109/ICECS.2002.1045320) [5], архитектура которого представлена на Фиг.1. Конструкция основана, главным образом, на матричном дешифраторе, осуществляющем преобразование из двоичного в термометрический код, и включает в себя массив защелок и токовых ячеек.

Матричный дешифратор из двоичного в термометрический код состоит из двух дешифраторов из двоичного в термометрический код меньшей размерности. Пример такого дешифратора представлен на Фиг.2. В примере в качестве дешифратора меньшей размерности используется дешифратор, преобразующий 2 бита двоичного кода в 4 бита термометрического кода

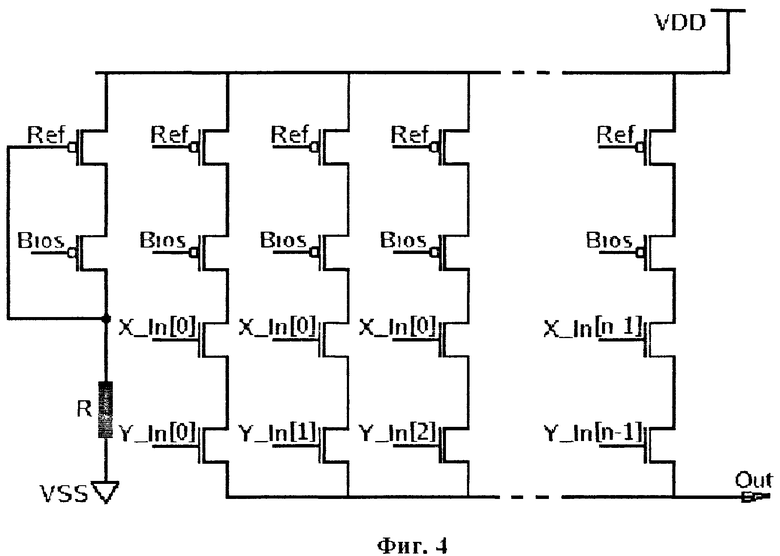

Таким образом, в данном примере матричный дешифратор из двоичного в термометрический код состоит из двух дешифраторов 2 бита в 4 бита (04 на Фиг.2, 3) и и-или или или-и матрицы, в зависимости от реализации (03 на Фиг.2 или или-и на Фиг.4). И-или матрица формируется следующим образом:

Outi∗8+j=hi&1j|hi+1,

Out7∗8+j=h7&1j.

Данный цифроаналоговый преобразователь выбран в качестве прототипа заявленного изобретения.

Недостатком традиционных ЦАП, в том числе ЦАП прототипа, является то, что их необходимо использовать вместе с умножителем, работающим на высокой частоте и повышающим общее потребление тока.

Задачей заявленного изобретения является создание цифроаналогового преобразователя со встроенным умножителем со сниженным потреблением мощности тока, упрощенной схемотехникой и увеличенным быстродействием.

Поставленная задача решена за счет встраивания умножителя внутрь цифроаналогового преобразователя, а именно за счет выполнения умножения путем включения источников тока цифроаналогового преобразователя и реализована путем создания цифроаналогового преобразователя со встроенным умножителем, содержащего два матричных дешифратора из двоичного в термометрический код, соединенных с массивом источников тока, отличающегося тем, что каждый источник тока содержит два последовательно включенных ключа, первый и второй, при этом выходы первого дешифратора соединены с первыми ключами источников тока, находящихся на одной строке массива, и выполнены с возможностью управления первыми ключами, а выходы второго дешифратора соединены со вторыми ключами источников тока, находящихся в одном столбце массива, и выполнены с возможностью управления вторыми ключами.

Для функционирования цифроаналогового преобразователя со встроенным умножителем важно, чтобы каждый источник тока был выполнен с возможностью включения при одновременном включении двух имеющихся в нем ключей, при этом первый ключ управляется напряжением на горизонтальном проводе, а второй ключ управляется напряжением на вертикальном проводе, причем N горизонтальных проводов заряжены высоким уровнем, и М вертикальных проводов заряжены высоким уровнем, при этом вертикальные и горизонтальные провода вместе выполнены с возможностью обеспечения включения M∗N источников тока.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими чертежами.

Фиг.1 - схема 10-битового сегментированного как 8+2 цифроаналогового преобразователя, известного из уровня техники.

Фиг.2 - схема дешифратора из двоичного (4 бита) в термометрический код (16 бит), известного из уровня техники.

Фиг.3 - схема дешифратора из двоичного (2 бита) в термометрический код (4 бита), известного из уровня техники.

Фиг.4 - схема источника тока, известного из уровня техники.

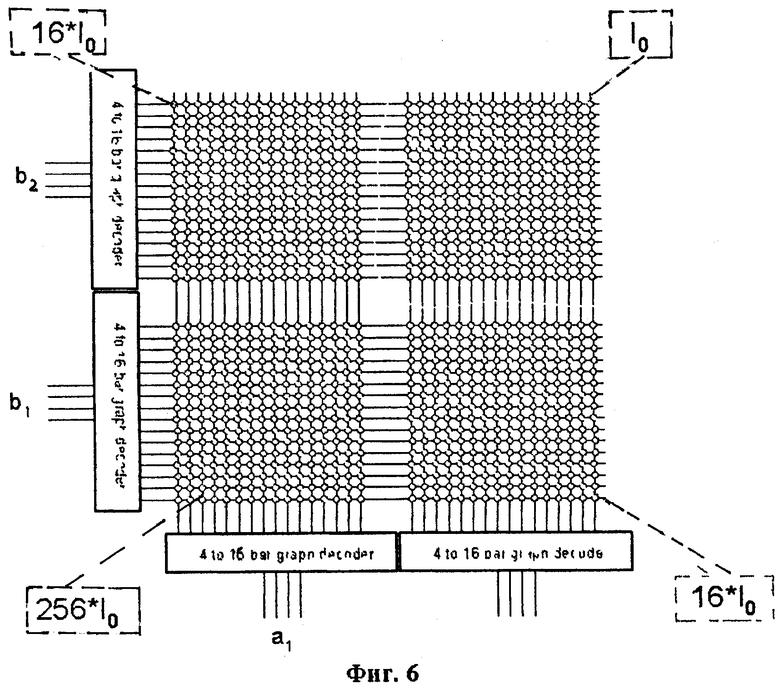

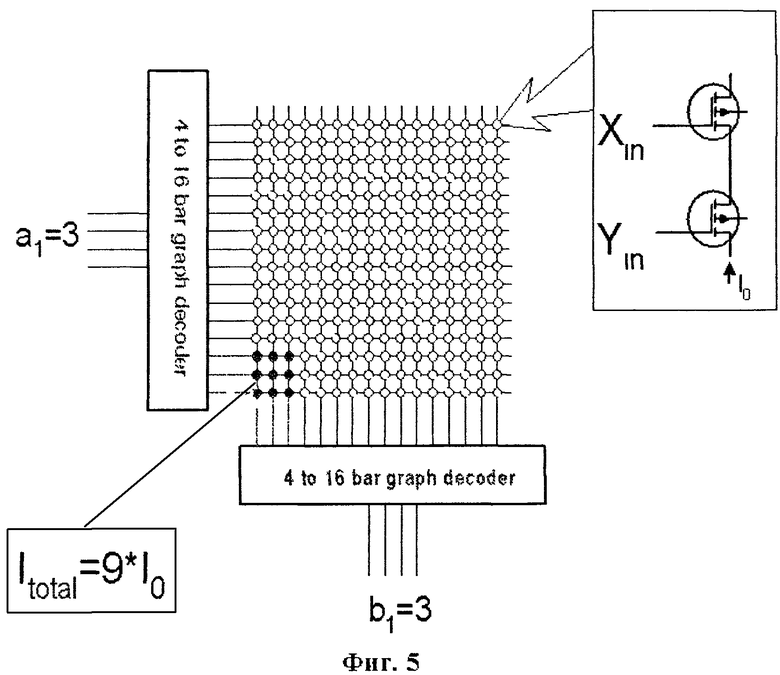

Фиг.5 - схема варианта цифроаналогового преобразователя со встроенным умножителем (4 бита∗4 бита) согласно изобретению.

Фиг.6 - схема варианта цифроаналогового преобразователя со встроенным умножителем (8 бит∗8 бит) согласно изобретению.

Рассмотрим вариант выполнения заявленного цифроаналогового преобразователя со встроенным умножителем 4×4 (Фиг.5). Для перемножения двух четырехразрядных чисел каждое число переводят в термометрический код. Провода, которые соединяют выходы обоих дешифраторов, образуют матрицу 16×16. В узлах матрицы горизонтальные (X) и вертикальные (Y) провода управляют двумя последовательно включенными ключами. Источник тока подключен к общему выходу только в случае, если обе управляющие ключом линии (и горизонтальная, и вертикальная) активны. На Фиг.5 показан случай умножения 3×3. В данном примере три младших бита первого слова (в термометрическом коде) равны единице, т.е. заряжены высоким уровнем напряжения, все остальные биты первого слова равны нулю (заряжены низким уровнем напряжения). Три младших бита второго слова (в термометрическом коде) равны единице, т.е. заряжены высоким уровнем напряжения, все остальные биты второго слова равны нулю (заряжены низким уровнем напряжения). Только те источники тока, которые расположены в узлах пересечения трех горизонтальных и трех вертикальных проводов, будут открыты. Будут открыты 9 источников тока. В общем случае количество открытых источников тока равно произведению X горизонтальных проводов, заряженных высоким уровнем, и y вертикальных проводов, заряженных высоким уровнем.

Представленное устройство преобразует два входных числа в двоичной кодировке в аналоговое значение сигнала, соответствующее произведению входных чисел.

Данное устройство не может быть физически разделено на умножитель и цифроаналоговый преобразователь. Все устройство целиком функционирует как умножитель, интегрированный с ЦАПом. Только соединение декодера, ключей и источников тока заявленным способом будет функционировать как умножитель, итерированный с ЦАПом.

Непосредственная реализация умножения 10-разрядных чисел матричным методом слишком громоздка (1024×1024=1048576 узлов). В этом случае предпочтительнее использовать вариант заявленного ЦАП с сегментной архитектурой (Фиг.6). На Фиг 6 показан вариант ЦАП с умножителем 8×8.8-битовое число представлено в виде двух 4-битовых.

D1=a1b1, D2=a2b2; тогда А=a1b1∗a2b2=256∗а1∗а2+16∗a2b1+16∗a1b2+b1b2,

т.е. в данном варианте используют 4 различных массива источников тока (256:16:16:1).

Заметим, что вклад наименьшего массива (b1b2) невелик, и мы можем его отбросить без значительных потерь в точности.

В случае 10-битового числа, его можно представить в виде 4, 3 и 3 бита, или 4, 4 и 2 бита. Соответственно для 10-битового числа будет использоваться вариант заявленного ЦАП с 3×3=9 массивов источников тока, и наименьшие массивы могут быть отброшены.

Потребление тока цепи, содержащей заявленный ЦАП со встроенным умножителем, порядка потребления одного ЦАП без умножителя (около 6 мВт), к нему лишь добавляется потребление двух дешифраторов, примерно по 0,6 мВт на дешифратор.

Заявленное изобретение может быть реализовано на основе КМОП технологии.

Хотя указанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

Изобретение относится к области электроники, а именно к цифроаналоговым преобразователям со встроенным умножителем, и может применяться в цифровых радиопередатчиках. Техническим результатом является снижение потребляемой мощности тока и увеличение быстродействия за счет встраивания умножителя внутрь цифроаналогового преобразователя. Цифроаналоговый преобразователь со встроенным умножителем содержит два матричных дешифратора из двоичного в термометрический код, соединенных с массивом источников тока, каждый источник тока содержит два последовательно включенных ключа, первый и второй, при этом выходы первого дешифратора соединены с первыми ключами источников тока, находящихся на одной строке массива, и выполнены с возможностью управления первыми ключами, а выходы второго дешифратора соединены со вторыми ключами источников тока, находящихся в одном столбце массива, и выполнены с возможностью управления вторыми ключами. 1 з.п. ф-лы, 6 ил.

1. Цифроаналоговый преобразователь со встроенным умножителем, содержащий два матричных дешифратора из двоичного в термометрический код, соединенных с массивом источников тока, отличающийся тем, что каждый источник тока содержит два последовательно включенных ключа, первый и второй, при этом выходы первого дешифратора соединены с первыми ключами источников тока, находящихся на одной строке массива, и выполнены с возможностью управления первыми ключами, а выходы второго дешифратора соединены со вторыми ключами источников тока, находящихся в одном столбце массива, и выполнены с возможностью управления вторыми ключами.

2. Цифроаналоговый преобразователь со встроенным умножителем по п.1, отличающийся тем, что каждый источник тока выполнен с возможностью включения при одновременном включении имеющихся в нем ключей, при этом первый ключ управляется напряжением на горизонтальном проводе, а второй ключ управляется напряжением на вертикальном проводе, причем N горизонтальных проводов заряжены высоким уровнем, и М вертикальных проводов заряжены высоким уровнем, при этом вертикальные и горизонтальные провода вместе выполнены с возможностью обеспечения включения M·N источников тока.

| US 6169509 B1, 02.01.2001 | |||

| Устройство для подачи изделий | 1987 |

|

SU1465348A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ | 2000 |

|

RU2201032C2 |

| ЦИФРО-АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 0 |

|

SU232616A1 |

Авторы

Даты

2011-02-27—Публикация

2009-09-21—Подача