Известны цифро-аналоговые устройства для умножения, содержащие амнлитудно-позиционные сумматоры, амплитудный дискриминатор, цифро-аналоговый преобразователь, дешифраторы, аналоговые квадраторы, усилители-сумматоры, пороговые схемы и матрицы резисторов.

Предложенное устройство отличается от известных тем, что в нем входные амплитуднопозиционные сумматоры подключены к двум амплитудно-позиционным квадраторам, в каждом из которых амплитудный дискриминатор, соединенный через дешифратор с матрицами резисторов, подключен к цифро-аналоговому преобразователю выходного кода амплитудного дискриминатора, связанного с младшим разрядом входной величины амплитудно-позиционного квадратора, аналоговый квадратор, на вход которого подан младший разряд входной величины амплитуднопозиционного квадратора, подключен к одному из аналоговых усилителей-сумматоров и одной из пороговых схем, вход другого аналогового усилителя-сумматора и другой пороговой схемы - с одной из матриц резисторов, а выходы пороговых схем связаны с амплитудно-позиционным сумматором квадратора. Такое выполнение устройства для умножения повышает точность вычислений.

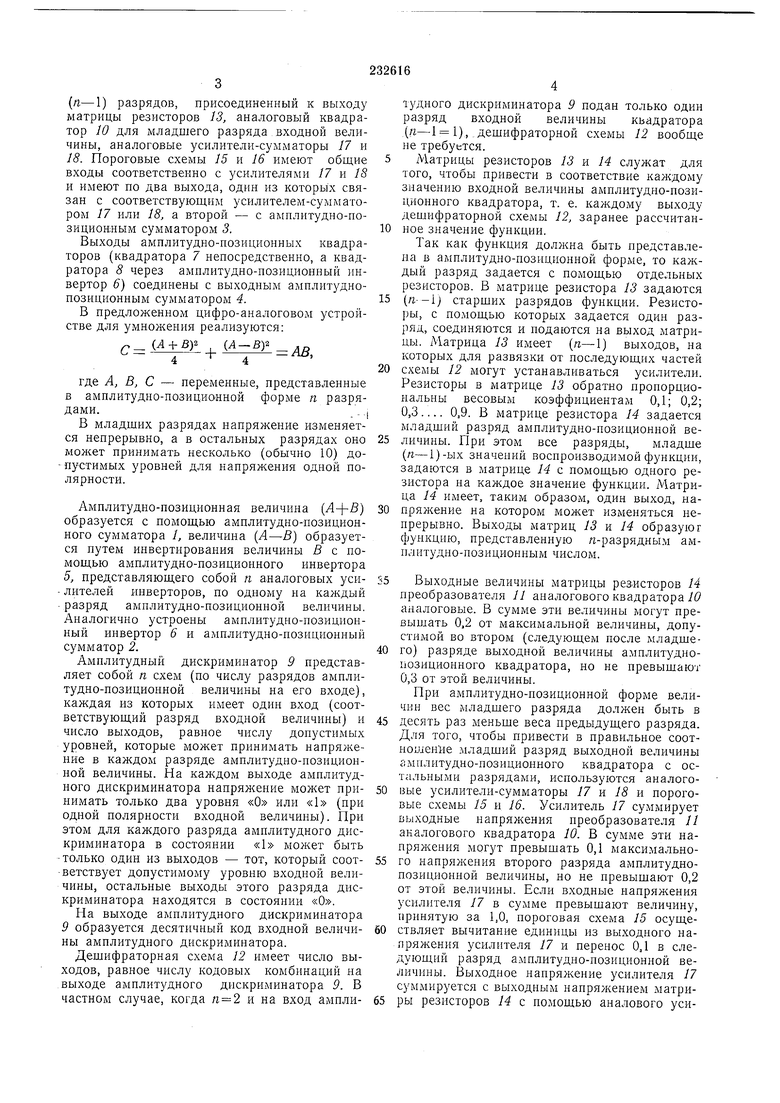

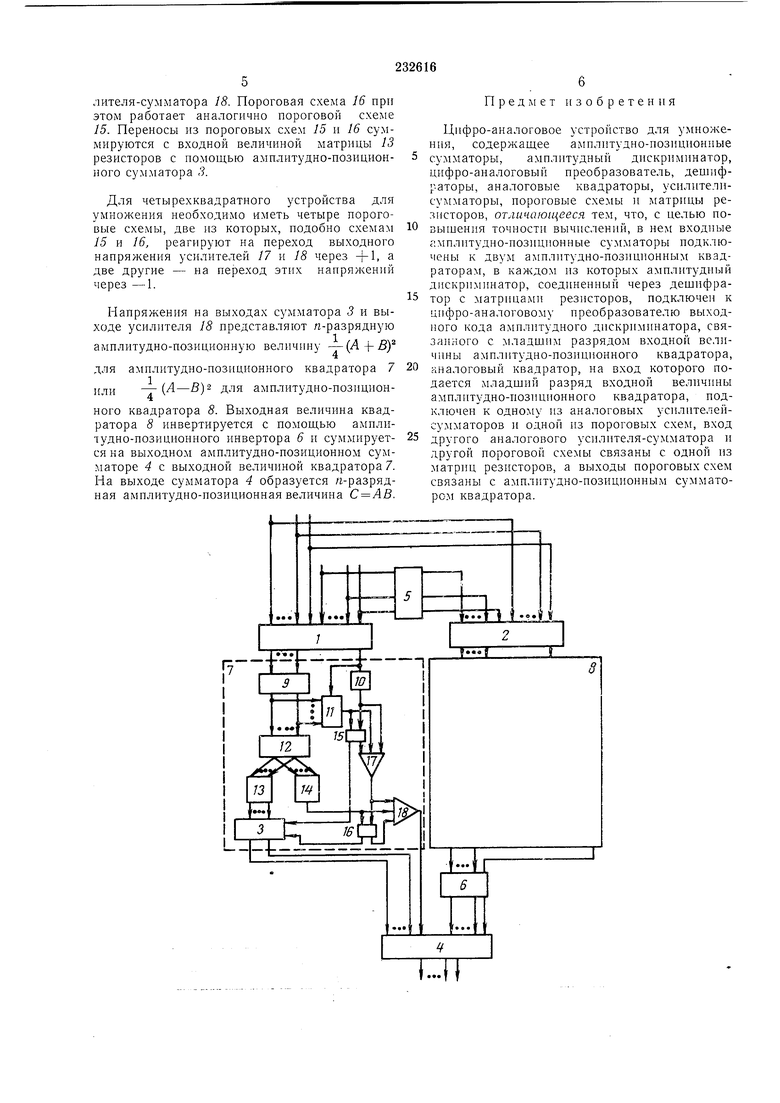

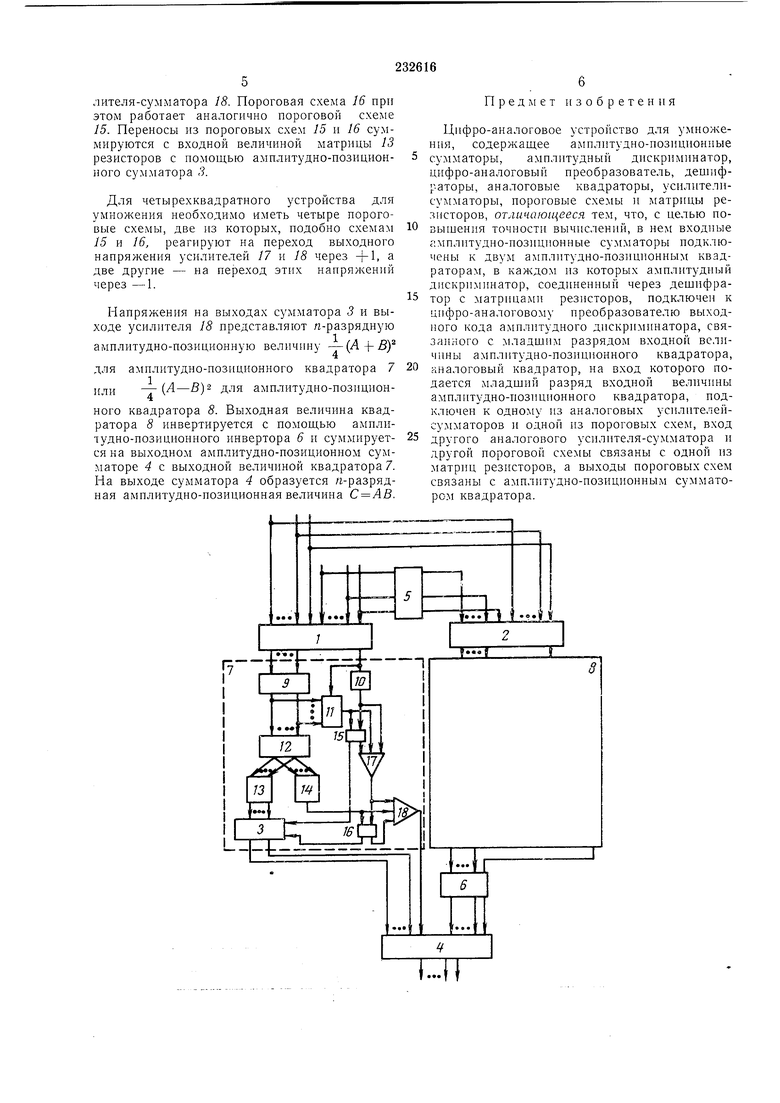

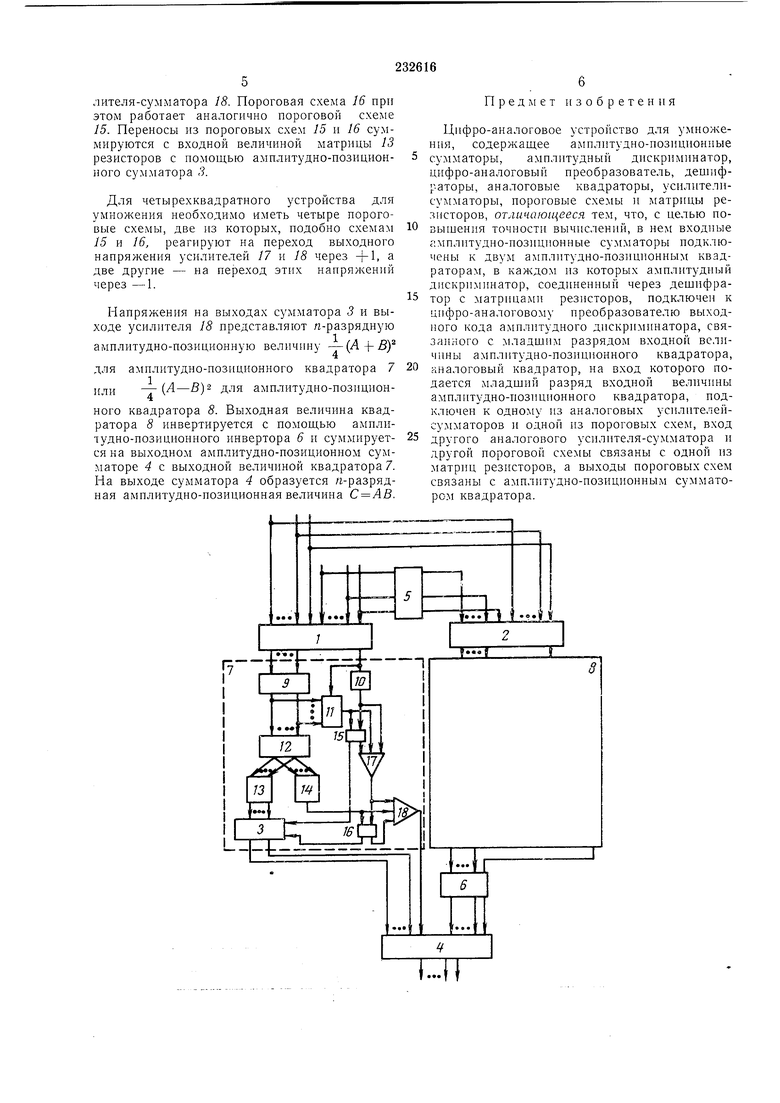

на чертеже. Устройство содержит амплитудно-позиционные сумматоры 1, 2, 3 и 4 соответственно 1-го, 2-го, (З-д)-го и 4-(/1-1)-го разрядов, амплитудно-позиционные инверторы 5 и 6, амплнтздно-нозиционные квадраторы 7 и 8, амплитудный дискриминатор 9, аналоговый квадратор 10 (аналоговый функциональный преобразователь, воспроизводящий квадратичную зависимость), цифро-аналогоБый преобразователь 11, дешифраторную схему 12, матрицы резисторов 13 и 14, пороговые схемы 15 и 16, аналоговые усилители-сумматоры 17 и 18.

Входные неременные А и В, представленные в амплитудно-нознционной форме я разрядами, подаются на амплитудно-позиционные сумматоры 1 п 2, причем на сумматор 2 переменная В подается через амплитудно-позиционный инвертор 5.

Выходы амплитудно-позиционных сумматоров 1 п 2 подсоединены к амплитудно-позиционным квадраторам 7 и 8. Каждый из квадраторов содержит амнлитудный дискриминатор 9 для (п-1) разрядов входной велнчины,

к выходу которого присоединены цифро-аналоговый преобразователь //, опорным напряжением которого служит младший разряд входной величины квадратора, и дешифраторная схема 12 с матрицами резисторов 13 и 14,

(ft-1) разрядов, присоединенный к выходу матрицы резисторов 13, аналоговый квадратор 10 для младшего разряда входной величины, аналоговые усилители-сумматоры 17 и 18. Пороговые схемы 15 и 16 имеют общие входы соответствеиио с усилителями 17 и 18 и имеют по два выхода, один из которых связан с соответствующим усилителем-сумматором 17 или 18, а второй - с амилитудно-иозициоЕНым сумматором 3,

Выходы амплитудно-иозициоииых квадраторов (квадратора 7 непосредственно, а квадратора 8 через амилитудно-позиционный инвертор 6) соединены с выходным амплитуднопозиционным сумматором 4.

В предложенном цифро-аналоговом устройстве для умножения реализуются:

,

где А, В, С - переменные, представленные в амплитудно-позиционной форме п разрядами.,-.| В младших разрядах напряжение изменяется непрерывно, а в остальных разрядах оно может принимать несколько (обычно 10) до пустимых уровней для напряжения одной полярности.

Амплитудно-позиционная величина () образуется с помощью амплитудно-позиционного сумматора /, величина (А-В) образуется путем инвертирования величины В с помощью амплитудно-позиционного инвертора 5, представляющего собой п аналоговых уси-лителей инверторов, по одному иа каждый

-разряд амплитудно-позиционной величины. Аналогично устроены амплитудно-позиционный инвертор 6 и амплитудно-позиционный сумматор 2.

Амплитудный дискриминатор 9 представляет собой п схем (по числу разрядов амплитудно-позиционной величины на его входе), каждая из которых имеет один вход (соответствующий разряд входной величины) и число выходов, равное числу допустимых уровней, которые может принимать напряжение в каждом разряде амплитудно-позиционной величины. На каждом выходе амилитудиого дискриминатора напряжение может принимать только два уровня «О или «1 (при одной полярности входной величины). При этом для каждого разряда амплитудного дискриминатора в состоянии «1 может быть -только один из выходов - тот, который соот-ветствует допустимому уровню входной величины, остальные выходы этого разряда дискриминатора находятся в состоянии «О.

Па выходе амплитудного дискримииатора 9 образуется десятичный код входной величины амплитудного дискриминатора.

тудного дискриминатора 9 подан только один разряд входной величины квадратора (га-1 1),. дешифраторной схемы 12 вообще не требуется.

Матрицы резисторов 13 и 14 служат для того, чтобы привести в соответствие каждому значению входной величины амплитудно-позиционного квадратора, т. е. каждому выходу дешифраторной схемы 12, заранее рассчитанное значение функции.

Так как функция должна быть представлена в амплитудно-позиционной форме, то каждый разряд задается с помощью отдельных резисторов. В матрице резистора 13 задаются

(ft--l) старщих разрядов функции. Резисторы, с помощью которых задается одии разряд, соединяются и иодаются на выход матрицы. Матрица 13 имеет (я-1) выходов, на которых для развязки от последующих частей

схемы 12 могут устанавливаться усилители. Резисторы в матрице 13 обратно пропорциональны весовым коэффициентам 0,1; 0,2; 0,3- 0,9. В матрице резистора 14 задается младщий разряд амплитудно-позиционной величины. При этом все разряды, младще (п-1)-ых значеиий восироизводимой функции, задаются в матрице 14 с помощью одного резистора на каждое значение функции. Матрица 14 имеет, таким образом, один выход, напряжение на котором может изменяться непрерывно. Выходы матриц 13 и 14 образуют функцию, представленную п-разрядным амплитудно-позиционным числом.

Выходные величины матрицы резисторов 14 преобразователя // аналогового квадратора/( аналоговые. В сумме эти величины могут превышать 0,2 от максимальной величины, допустимой во втором (следующем после младшего) разряде выходной величины амплитуднопозиционного квадратора, но не превышают 0,3 от этой величины.

При амплитудно-позиционной форме величин вес младшего разряда должен быть в

десять раз меньше веса предыдущего разряда. Для того, чтобы привести в правильное соотношение младший разряд выходной величины ймилитудно-позиционного квадратора с остальными разрядами, используются аналоговые усилители-сумматоры 17 и 18 и пороговые схемы 15 и 16. Усилитель 17 суммирует выходные напряжения преобразователя // аналогового квадратора 10. В сумме эти напряжеиия мог)т превышать 0,1 максимального напряжения второго разряда амплитуднопозиционной величины, но не иревышают 0,2 от этой величины. Если входные напряжения усилителя 17 в сумме превыщают величину, принятую за 1,0, пороговая схема 15 осуществляет вычитание единицы из выходного напряжения усилителя 17 и перенос 0,1 в следующий разряд амплитудно-позиционной величины. Выходное нанряжение усилителя 17 суммируется с выходным напряжением матрилителя-сумматора 18. Пороговая схема 16 при этом работает аналогично пороговой схеме 15. Переносы из пороговых схем 15 и 16 суммируются с входной величиной матрицы 13 резисторов с помощью амплитудно-позиционного сумлштора 3.

Для четырехквадратного устройства для умножения необходимо иметь четыре порогоBt)ie схемы, две из которых, подобно схемам 15 и 16, реагируют на переход выходного напряжения усилителей /7 и 18 через +1, а две другие - на переход этих напряжений через -1.

Напряжения на выходах сумматора 3 и выходе усилителя 18 представляют я-разрядную

амплитудно-позиционную величину -(Л-j-5) для амплитудно-позиционного квадратора 7 или Г - амплитудно-позиционного квадратора 8. Выходная величина квадратора 8 инвертируется с помощью амплитудно-позициопного инвертора 6 и суммируется на выходном амплитудно-позиционном сумматоре 4 с выходной величиной квадратора 7. На выходе сумматора 4 образуется я-разрядная амплитудио-позиционная величина С АВ.

Предмет изобретения

Цифро-аналоговое устройство для умножения, содержащее амилитудно-позиционные сумматоры, амплптудный дпскриминатор, цифро-аналоговый преобразователь, дешифраторы, аналоговые квадраторы, усилителисумматоры, пороговые схемы и матрицы резисторов, отличающееся тем, что, с целью по0вышения точности вычислений, в нем входные амплитудно-иозиционные сумматоры подключены к двум амилитудно-поз 1ционным квадраторам, в калчдом из которых амплитудный дискрим шатор, соединенный через дешифра5тор с матрицами резисторов, подключен к цифро-аналоговому иреобразователю выходного кода амилитудного дпскрпмииатора, связанного с младшим разрядом входной величины амплитудно-позиционного квадратора,

0 аналоговый квадратор, на вход которого подается младший разряд входной величины амплптудио-иозицпонного квадратора, подключен к одному из аналоговых усилителейсумматоров и одной из пороговых схем, вход другого аналогового ycилитeля-cy мaтopa и другой иороговой схемы связаны с одной из матриц резисторов, а выходы пороговых схем связаны с амплитудно-позиционным сумматором квадратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1967 |

|

SU224919A1 |

| УСТРОЙСТВО ЦЕНТРИРОВАНИЯ СЛУЧАЙНЫХ ПРОЦЕССОВ ДЛЯ ЦИФРОВЫХ СТАТИСТИЧЕСКИХ АНАЛИЗАТОРОВ | 1973 |

|

SU388266A1 |

| ЦИФРО-АНАЛОГОВОЕ УСТРОЙСТВО | 1968 |

|

SU217750A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ СЕТЕВЫХ ГРАФИКОВ | 1970 |

|

SU269627A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

| Двухотсчетный следящий привод | 1989 |

|

SU1700535A1 |

| Разрядно-аналоговый сумматор | 1988 |

|

SU1589293A1 |

Даты

1969-01-01—Публикация