Изобретение относится к области бортовых вычислительных систем повышенной надежности и может найти применение при создании вычислительных систем обработки информации критических функций в бортовых средствах автоматизированного управления процессами авиационных и ракетно-технических систем.

Известен способ, когда отказоустойчивость обработки информации достигается за счет создания избыточных каналов обработки в бортовых комплексах воздушных судов гражданской авиации и ракет носителей [1, 2, 3]. Управление избыточностью в этих системах при обработке информации критических функций достигается за счет мажоритарного контроля каждым устройством канала сигналов, поступающих из канальных устройств, обрабатывающих сигналы критических функций до этого устройства. При этом реконфигурация системы для обработки информации исправными устройствами осуществляется мажоритарным выбором правильно обработанной информации.

Известен способ отказоустойчивой обработки критических функций в потоковых системах обработки посредством однородных вычислительных сред [4]. Отказоустойчивая обработка в этих системах достигается за счет избыточного количества систолических процессоров, которые в фоновом режиме самодиагностируются и автоматически отключаются при возникновении отказов.

Известен способ надежной обработки информации в бортовых системах, построенных на сетевых структурах [5]. Управление избыточностью в этих системах осуществляется по кластерному принципу. В кластерных системах избыточность, направленная на концентрацию вычислительных ресурсов для решения сложных функциональных задач, не разделяется с избыточностью, направленной на обеспечение надежной обработки информации.

Известен способ отказоустойчивой обработки, при котором высокая надежность достигается за счет управляемой избыточности, но при этом элементы управления избыточностью не входят в состав избыточных резервированных устройств обработки, а выделяются в отдельное устройство, включаемое последовательно им [6]. Надежность обработки информации в таких системах, кроме надежности, достигаемой за счет избыточности, определяется надежностью средств управления избыточностью.

По своему назначению и функциональным возможностям наиболее близким к заявленному способу является способ [6, 7], реализованный в отказоустойчивом бортовом контроллере, который был принят авторами в качестве прототипа.

Прототип имеет следующие недостатки:

- надежность обработки информации зависит от надежности средств управления избыточностью, которые включены последовательно к системе резервированных микроЭВМ,

- процесс управления избыточностью не отделен от процесса обработки информации,

- анализируются сигналы текущего функционирования без их статистической обработки.

Целью предлагаемого изобретения является повышение надежности и достоверности обработки критических функций отказоустойчивой вычислительной системы.

Указанная цель достигается тем, что в основу предложенного способа положено многократное резервирование трактов реализации критических функций, при которой процессы управления избыточностью и вычислительный процесс разделены в цикле реального времени (Real Time) и частично аппаратно. При этом в каждом из вычислительных трактов производится мажоритарное сравнение сигналов, прошедших через каждый тракт. Неоднозначность мажоритарного сравнения сигналов в различных трактах устраняют мажоритарным сравнением результатов сравнения сигналов. Достоверности мажоритарного контроля сигналов достигают путем статистической обработки случайного процесса изменения критического параметра, вычисления остаточной дисперсии и ее мажоритарного сравнения.

Сущность данного изобретения поясняется графическими материалами:

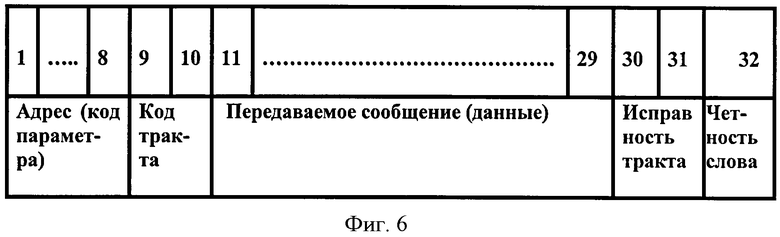

- на фиг.1 - структурная схема избыточности системы;

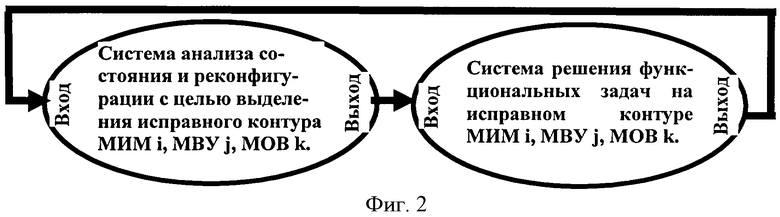

- на фиг.2 - принцип независимого, но взаимосвязанного функционирования систем в программно-аппаратном пространстве;

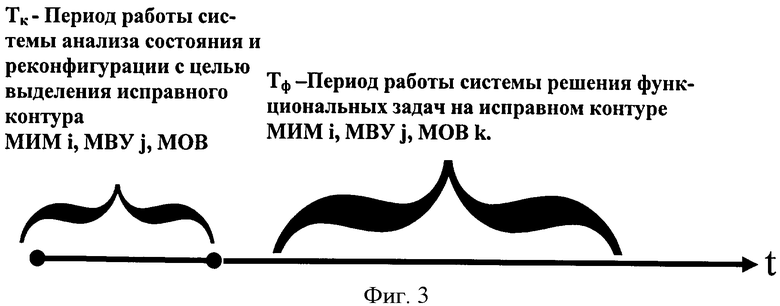

- на фиг.3 - принцип независимого, но взаимосвязанного функционирования систем в пространстве Real Time;

- на фиг.4 - структура слова с результатами тестового контроля;

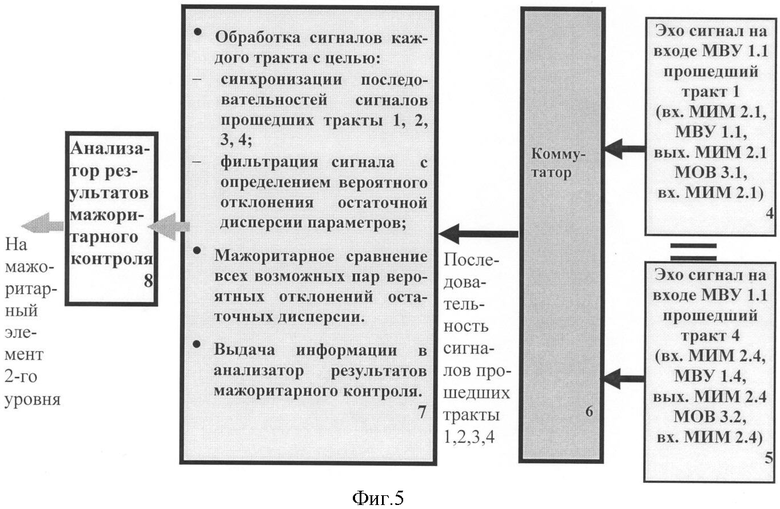

- на фиг.5 - структурная схема мажоритарного элемента 1-го уровня МВУ 1.1;

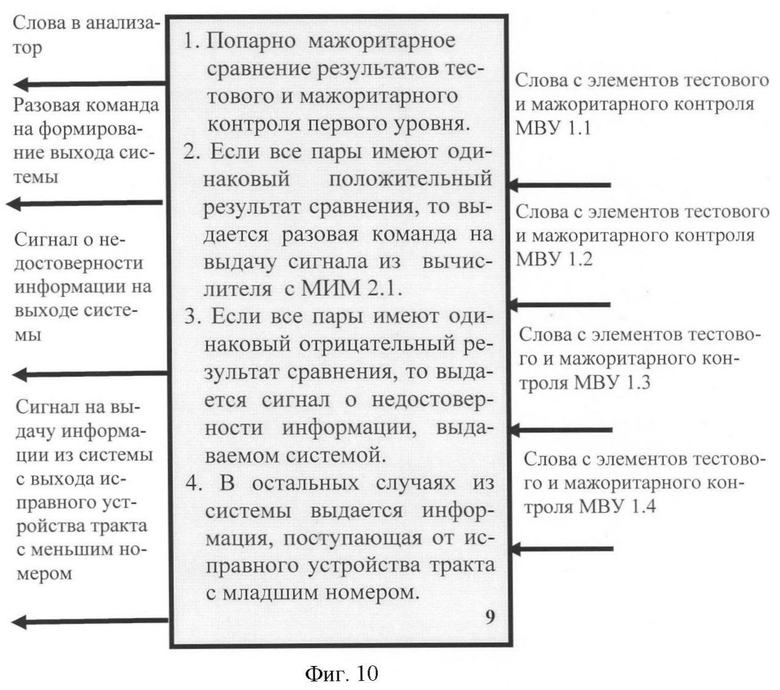

- на фиг.6 - структура слова в стандарте ARINC-429;

- на фиг.7 - диаграмма синхронизирующих и информационных импульсов в ARINC-429;

- на фиг.8 - диаграмма совместного появления слов на входе модуля обработки данных в момент t;

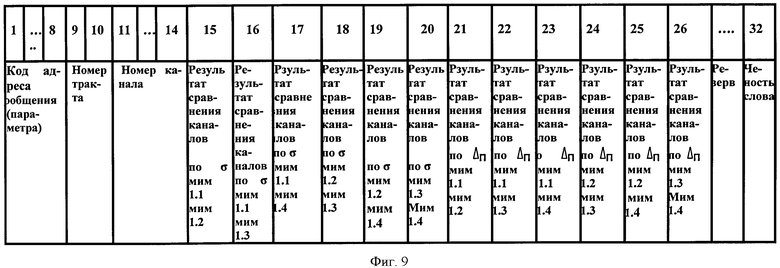

- на фиг.9 - структура слова, поступающего из мажоритарного элемента 1-го уровня;

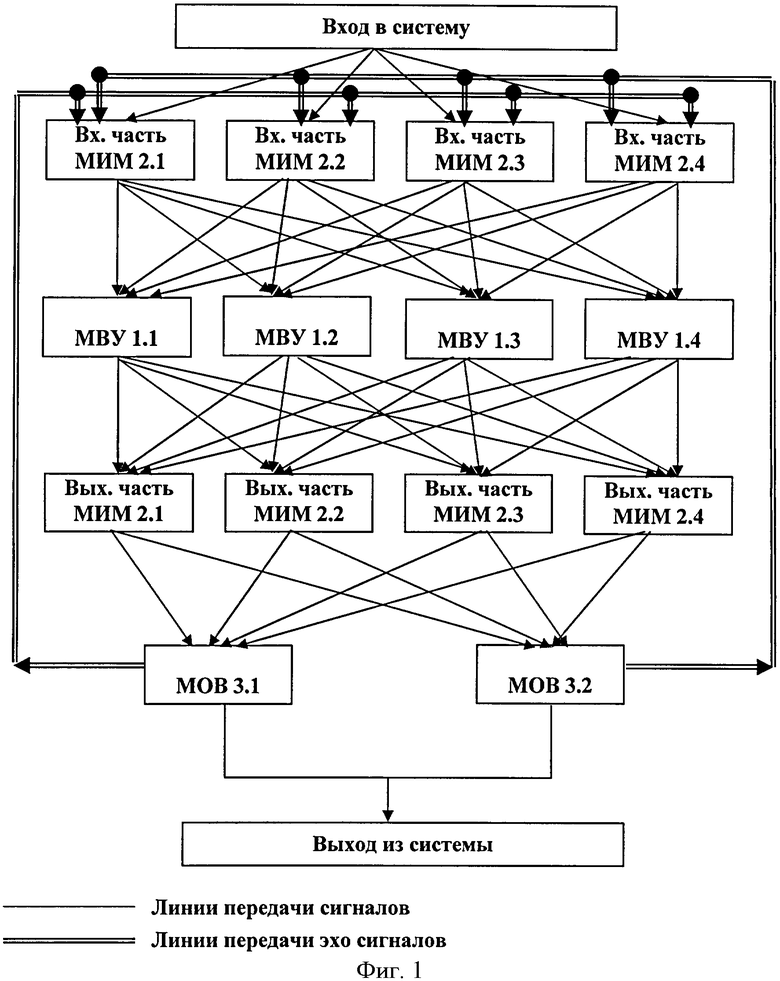

- на фиг.10 - структурная схема мажоритарного элемента 2-го уровня.

Структурная схема избыточной системы приведена на фиг.1. Как видно из чертежа, избыточность создается за счет 4-кратного резервирования интерфейсно-вычислительного тракта, который состоит из модуля вычислительного узла (МВУ), многофункционального интерфейсного модуля (МИМ) и модуля объединения выходов (MOB). Для удобства описания входная и выходная части интерфейсного модуля изображены раздельно, хотя выполнены в единой конструкции.

С выходных каналов модулей объединения выходов (MOB) 3.1, 3.2 эхо-сигналы критических параметров подаются на мажоритарные элементы каждого (МВУ) 1.1, 1.2, 1.3, 1.4 через входные каналы каждого (МИМ) 2.1, 2.2, 2.3, 2.4.

В Real Time независимо, но взаимосвязанно функционируют две следующие аппаратно-программные системы:

- анализа состояния вычислительной системы и ее реконфигурации;

- решения функциональных задач на исправном контуре МИМ i, МВУ j, MOB k,

где: i - 2.1, 2.2, 2.3, 2.4;

j - 1.1, 1.2, 1.3, 1.4;

k - 3.1, 3.2.

Принцип независимого, но взаимосвязанного функционирования этих систем в программно-аппаратном и временном пространствах показан соответственно на фиг.2; 3.

Функциями системы анализа состояния вычислительной системы и ее реконфигурации являются:

- тестовый контроль модулей МВУ, МИМ, MOB;

- мажоритарный контроль состояния системы;

- анализ результатов тестового и мажоритарного контроля;

- реконфигурация системы с целью выделения контура (МИМ i, MBY j, MOB k), формирующего выходной сигнал.

Элементы тестового контроля реализованы в каждом МВУ. Они содержат тесты и программы, реализующие процедуры контроля модулей МВУ (включая и тот, на котором реализован данный элемент тестового контроля), МИМ и MOB. В каждом цикле Real Time тестовый контроль выполняет элемент тестового контроля каждого МВУ (в порядке возрастания номеров МВУ) за период, равный одной четверти Тк. После окончания этого периода осуществляется прерывание тестового контроля данного элемента с запоминанием всех составляющих состояния контроля. В каждом следующем Real Time тестовый контроль данного элемента продолжается с момента прерывания предыдущего цикла. После полного завершения процедуры тестового контроля из элемента тестового контроля на мажоритарный элемент второго уровня подается слово с результатами контроля. Структура этого слова приведена на фиг.4.

Одновременно с тестовым контролем в каждом из интерфейсно-вычислительных трактов выполняется мажоритарный контроль сигналов, прошедших через все интерфейсно-вычислительные тракты, то есть мажоритарный контроль первого уровня.

Структурная схема мажоритарного элемента 1-го уровня, который реализован в МВУ каждого тракта, приведена на фиг.5. Мажоритарный элемент 1-го уровня выполняет следующие функции.

1. Коммутация сигналов

Поскольку мажоритарные элементы, реализованные в МВУ 1.2, МВУ 1.3, МВУ 1.4, работают аналогично мажоритарному элементу МВУ 1.1, то в дальнейшем будет описана работа только мажоритарного элемента МВУ 1.1. Сигналы, прошедшие через все 4 интерфейсно-вычислительных тракта: МИМ i, MBУ j, MOB k, с выходов модулей объединения выходов MOB 3.1 и MOB 3.2, через линии передачи эхо-сигналов (фиг.1), поступают вновь на вход МИМ 2.1 и через него на МВУ 1.1. На МВУ 1.1, как и на всех остальных МВУ, реализован мажоритарный элемент первого уровня. Коммутатор (позиция 6 фиг.5) последовательно коммутирует сигналы, прошедшие через все 4 интерфейсно-вычислительных тракта на вход модуля обработки данных (позиция 7 фиг.5).

2. Обработка сигналов

2.1. Синхронизация сигналов

Мажоритарный элемент обрабатывает последовательности сигналов как синхронизированных, так и не синхронизированных между собой состояний. В мажоритарном элементе синхронизируются друг с другом только сигналы, в структуре слова которых имеется идентификатор параметра. В частности, в структуре слова, записанного в стандарте ARINC-429 (фиг.6), идентификатор параметра записывается в первых 10 разрядах 32-разрядного слова.

Формат 32-разрядного слова в ГОСТ 18977-79 РТМ 1495-75 и АРИНК-429 имеет следующую структуру:

- разряды 1-8 содержат информацию о коде параметра;

- разряды 9,10 содержат информацию о коде тракта;

- разряды 11-29 содержат информацию о передаваемом сообщении;

- разряды 30-31 содержат информацию об исправности тракта, в котором было сформировано сообщение (информацию о матрице состояния);

- разряд 32 содержит информацию о четности сформированного слова.

Первой операцией обработки сигналов является поиск одних и тех же слов, поступивших из разных трактов, для их мажоритарного сравнения. На фиг.7 приведена диаграмма этих импульсов в сообщениях. Наличие синхронизирующих и информационных импульсов позволяет отделять между собой слова, так как в паузах между словами синхронизирующие импульсы не передаются. Поскольку каждый импульс соответствует одному биту передаваемой информации, то период передачи одного бита равен Т (фиг.7).

Паузу между словами П разрешается выполнять в пределах:

4Т≤П≤40Т.

Следовательно, период между словами Тс будет находиться в пределах:

36Т≤П≤72Т.

Принцип синхронизации сводится к совмещению сигналов с одними и теми же словами (кодами параметров), содержащими информацию о параметрах, измеренных в один и тот же момент. Поступающие на входы модулей обработки данных сигналы с информацией одной и той же последовательности параметров со всех четырех информационно-вычислительных трактов из-за асинхронной работы трактов будут сдвинуты относительно друг друга по фазе. Обозначим величину этого сдвига через τзад.

На фиг.8 приведена диаграмма совместного появления слов с 3-х информационно-вычислительных трактов на вход модуля обработки данных в момент t. У сигналов, пришедших с тракта 1, время задержки до начала обработки τзад. минимально, и момент t не совпадает с началом слова. У сигналов, пришедших с тракта 2, эта задержка больше, а у сигналов, пришедших с тракта 3, она достигла величины Тп, то есть периода передачи сообщений. При временах задержки, больших Тп, возникает вероятность совмещения сигналов со сдвигом на один период. Следовательно, условием правильной синхронизации является τзад>Тп.

Процедура синхронизации сводится к следующей последовательности операций.

- Сигналы, поступающие на модуль обработки данных (позиция 7 фиг.5), запоминаются в нем.

- По коду параметра (первые 8 разрядов слова (фиг.6)) первого полного слова, поступившего с тракта 1 (фиг.5), сравниваются все слова сигналов, поступившие со второго, третьего и четвертого трактов. Обозначим код первого параметра П1 (разряды 1…8 (фиг.6)).

- Сигналы, поступившие со второго, третьего и четвертого трактов на вход обработки данных, кроме сигналов, поступивших с первого тракта, сдвигаются по фазе таким образом, чтобы первым словом сигнала стало слово с кодом параметра П1.

- Если не у одного из слов, поступивших со всех трактов в модуль обработки данных, кроме первого тракта, слов с параметром П1 в сигналах не обнаруживается, то в анализатор результатов мажорирования (позиция 8 фиг.5) посылается сигнал в виде слова (фиг.4) с информацией о неисправности тракта 1, и повторяются операции предыдущих двух и настоящего пунктов относительно тракта 2.

- Состояние после сдвига сигналов по фазе, когда первые полные слова первых слов всех трактов имеют одинаковые коды параметров, является синхронизированным состоянием сигналов.

2.2. Статистическая обработка сигналов

Каждый параметр каждого тракта подвергается статистической обработке сигналов по следующему алгоритму.

А) Группа операций по формированию матрицы данных

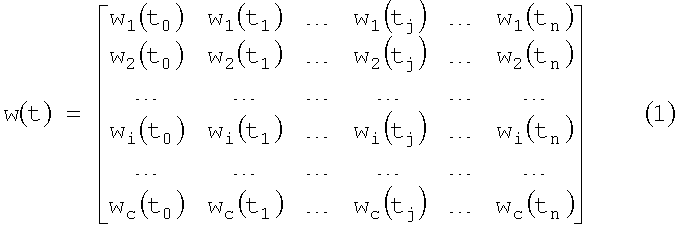

Данные первого слова (разряды 11-29 фиг.6) первого параметра (идентификатор П1), поступившие с тракта 1, обозначим идентификатором W1(t1). Индекс «1(t1)» означает, что это данные первого элемента, соответствующего моменту «t1». Индекс «1» означает, что эти данные относятся к первой строке матрицы данных (1), которая имеет следующий вид:

Как видно из матрицы (1), число данных случайного процесса изменения параметров, равное величине с·n+1, разрезается на с строк (реализаций случайного процесса), каждая из которых состоит из n+1 значений параметра П1. Матрица (1) запоминается как матрица исходных данных.

Б) Группа операций по формированию ковариационной матрицы

Операция по оценке математического ожидания по каждому j-му столбцу матрицы (1) определяется по следующей формуле (2):

где:

- MW(tj) - математическое ожидание элементов j-го столбца;

- С - количество строк;

- Wi(tj) - элемент матрицы (1);

- ac(tj) - значение математического ожидания элементов j-го столбца.

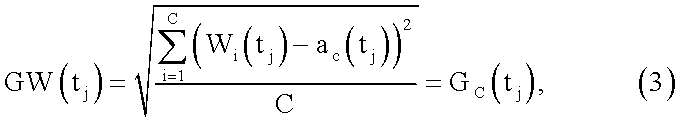

Операция по оценке стандартного (среднеквадратического) отклонения по каждому j-му столбцу матрицы (1) определяется по следующей формуле (3):

где:

- GW(tj) - стандартное (среднеквадратическое) отклонение элементов в сечении j;

- Gc(tj) - значение стандартного (среднеквадратического) отклонения элементов в сечении j.

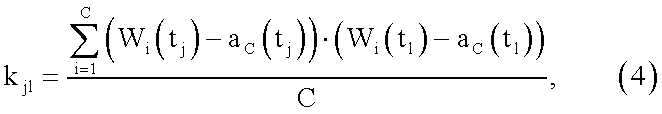

Операция по оценке элементов ковариационной матрицы (6) между сечениями j и l матрицы (1) (l=1, 2 … n; j=1, 2 … n) определяется по следующей формуле (4):

где:

- kj,l - элемент ковариационной матрицы (6) между сечениями j и l исходной матрицы (1).

Операция по оценке элементов ковариации между сечениями j=0 и l матрицы (1) (l=1, 2 … n; j=0) определяются по следующей формуле (5):

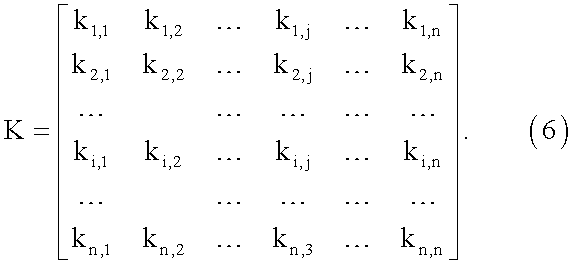

Ковариационная матрица (6), имеющая следующий вид, хранится в памяти:

Ковариационная матрица имеет следующие особенности:

- Она является квадратной и имеет размерность n×n;

- Она симметрична относительно диагональных элементов, то есть ki,j=kj,i;

- Диагональными элементами являются дисперсии j-x столбцов матрицы (1), то есть ki,j=i=Gc(tj).

В) Группа операций по определению коэффициента линейной регрессии и остаточной дисперсии

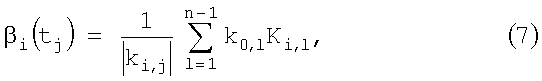

Операция по оценке коэффициента линейной регрессии βj по каждому j-му столбцу матрицы (6) определяется по следующей формуле (7):

где:

- βi(tj) - оценка i-го коэффициента линейной регрессии в сечении tj матрицы (5);

- |ki,j| - детерминант ковариационной матрицы (6);

- k0,l - оценка элемента ковариации между сечениями 0 и l матрицы (5),

- Ki,l - алгебраическое дополнение элемента ki,l (l=1,2…n-l) ковариационной матрицы (6).

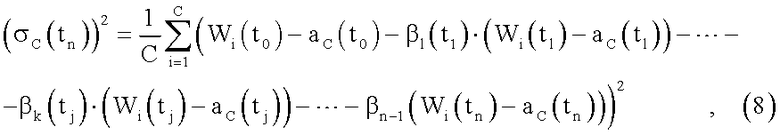

Операция по оценке остаточной дисперсии (σc(tn))2 регрессии параметра П1 по данным матрицы (1) определяется по формуле (8):

где:

- (σc(tn))2 - остаточная дисперсия регрессии параметра П1;

- j=1, 2 … n-1.

Г) Группа операций по определению и анализу доверительных интервалов на вероятное отклонение остаточной дисперсии

Операция по определению доверительного интервала на вероятное отклонение остаточной дисперсии

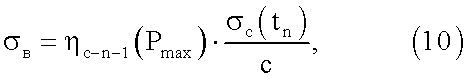

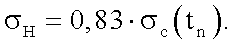

Нижняя и верхняя оценки вероятного отклонения остаточной дисперсии σн и σв определяются соответственно по формулам (9) и (10):

где:

- σн - нижняя оценка вероятного отклонения остаточной дисперсии;

- σв - верхняя оценка вероятного отклонения остаточной дисперсии;

- ηc-n-1(Pmin) - минимальный квантиль распределения χ2 с (С-n-1) степенями свободы, соответствующий вероятности Pmin;

- ηc-n-1(Pmax) - максимальный квантиль распределения χ2 с (С-n-1) степенями свободы, соответствующий вероятности Pmax.

Минимальное количество измерений параметра, обеспечивающее эргодичность (период достижения достоверности характеристик случайного процесса), составляет 1000 (n=10, с=100). Примем величину вероятности доверия Рд=Pmax-Pmin равной 0,989 (Pmax=0,999, Pmin=0,01). При этих данных выражения (9) и (10) примут следующий вид:

Обозначим нижнюю и верхнюю оценки вероятного отклонения остаточной дисперсии i-го и j-го устройств соответственно через σнуi, σвуi и σнуj, σвуj. Тогда доверительные интервалы i-го и j-го устройства будут соответственно равны:

Условие несравнения доверительных интервалов устройств запишется:

Для того чтобы сохранить достоверность определения оценок характеристик случайного процесса изменения параметра и в то же время минимизировать интервалы между определениями остаточных дисперсией, объем измерений, равный (n+1)·с, сдвигают на шаг, равный n+1 измерениям.

Д) Группа операций по определению и анализу отклонений от допуска на параметр

Для того чтобы гарантировать систему мажоритарного контроля от ошибок, когда по каким-то причинам произошло отклонение параметра от допуска по точности ΔП, а вероятное отклонение остаточной дисперсии осталось в пределах доверительных интервалов, необходимо выполнить группу следующих операций относительно трактов, подвергающихся мажоритарному контролю:

где:

- Wуi - значение критического параметра тракта под номером i;

- Wуj - значение критического параметра тракта под номером j;

- ΔП - допуск на параметр П;

где сочетания i-j принимают значения: 1-2, 1-3, 1-4, 2-3, 2-4, 3-4.

Е) Группа операций по анализу результатов мажоритарного контроля

Выполнение условий (12) и (13) означает, что тракт yi либо тракт yj неисправны. Если трактов как минимум три, то мажоритарным сравнением доверительных интервалов трех трактов можно установить какой из этих трактов неисправен. Условием неисправности тракта является непересечение доверительных интервалов для вероятного отклонения остаточных дисперсий с двумя остальными трактами.

Результаты анализа неисправных трактов записываются в 32-разрядные слова со структурой данных, представленных на фиг.9. Каждое слово содержит информацию:

- о контролируемом параметре;

- о мажоритарном элементе конкретного тракта (номер тракта);

- о контролируемом канале (номер канала);

- о результатах сравнения сигналов мажоритарных элементов МВУ 1.1-1.2, 1.1-1.3, 1.1-1.4, 1.2-1.3, 1.2-1.4, 1.3-1.4;

- о контроле на четность слова.

Если результат сравнения положительный, то в разрядах 15-19 записывается 0, в противном случае записывается 1.

Результаты мажоритарного контроля первого уровня поступают в мажоритарный элемент второго уровня.

Работа мажоритарного элемента второго уровня

Мажоритарный элемент второго уровня предназначен для мажорирования результатов тестового контроля и мажоритарного контроля первого уровня. Мажоритарный элемент второго уровня, так же как и первого уровня реализуется во всех четырех трактах.

Структура мажоритарного элемента второго уровня приведена на фиг.10.

В мажоритарном элементе второго уровня сопоставляются слова с одинаковыми параметрами, каналами, но с различными номерами мажоритарных элементов 1-го уровня (номер тракта). У этих слов анализируется информация о результатах сравнения сигналов с выходов трактов соответственно: 1.1-1.2, 1.1-1.3, 1.1-1.4, 1.2-1.3, 1.2-1.4, 1.3-1.4, полученных в каждом мажоритарном элементе первого уровня. Если обнаруживаются каналы с одинаковыми, положительными сравнениями у различных мажоритарных элементов 1-го уровня, то есть устанавливается набор трактов, на выходе которых имеется правильная информация, то на систему реконфигурации подается сигнал о том из этих трактов, у которого меньше номер. Если одинаковых, положительных сравнений, установленных различными мажоритарными элементами, не обнаруживается, то с выхода мажоритарного элемента второго уровня выдается сигнал о недостоверности информации по данному параметру.

Анализ результатов тестового и мажоритарного контроля

Анализатор состояний трактов вычислителя (позиция 8, фиг.5) анализирует результаты мажоритарного контроля мажоритарных элементов на предмет возникновения:

- сбоев;

- перемежающихся отказов;

- устойчивых отказов.

Если в течение 5 циклов мажоритарного контроля отказавший канал восстанавливается, то в память анализатора записывается информация о возникшем сбое на конкретном канале и моменте его возникновения. Если восстановление происходит после 4 циклов контроля, и периодически происходят процессы отказа и восстановления, то в памяти анализатора фиксируется перемежающийся отказ и момент его возникновения.

Реконфигурация системы с целью выделения контура (МИМ i, МВУ j, MOB k), формирующего выходной сигнал

Если отказ, возникший в определенный момент, не восстанавливается, то фиксируется устойчивый отказ с моментом его возникновения. Если по окончании полного цикла тестового контроля отказ не обнаруживается, то фиксируется отказ элементов контура контролируемого канала, в части канала, в котором отсутствует тестовый контроль. Отказ фиксируется в памяти анализатора с моментом его возникновения.

Если отказ, обнаруженный мажоритарным элементом, подтверждается тестовым контролем, то в память анализатора вводится следующая информация:

- о моменте возникновения отказа;

- о результатах мажоритарного контроля;

- о результатах тестового контроля.

При этом отказавшее устройство тракта отключается от системы мажоритарного контроля. Если отказавшим устройством оказывается устройство тракта под номером 4, то переименование номером не происходит. Если отказывает устройство тракта с другим номером, то отказавшее устройство заменяется соответствующим номером 4. При этом номер 4 заменяется на номер отказавшего устройства.

Технико-экономическая эффективность

Аппаратные и программные модули системы управления избыточностью встроены в каждый из интерфейсно-вычислительных трактов и тем самым также 4-кратно резервированы. Но при этом возможна неоднозначность в определении отказавшего тракта и принятия решения на реконфигурацию вычислительного ресурса по причине того, что эти операции выполнены системами управления избыточностью различных трактов. Для устранения этой неоднозначности в системе управления избыточностью создан мажоритарный контроль второго уровня, который мажоритарно сравнивает результаты мажоритарного контроля первого уровня и выбирает правильное решение.

Наличие во внешнем интерфейсе каждого тракта как низкочастотного интерфейса ARINC-429, согласованного с низкочастотной датчиковой системой, так и высокочастотного (сетевого AFDX, видеоинтерфейса DVI, оптического Fibre Channel, технического Ethernet) позволяют согласовать обработку информации низкочастотных датчиков с высокочастотными сетевыми структурами. Вычислительный ресурс обладает:

- высокой производительностью за счет наличия в модуле вычислительного узла (МВУ) 2-х независимых компьютеров (2-х процессоров «PowerPC 405» с частотой 450 МГц, оперативной памяти 512 Мбайт, скоростных каналов обмена) суммарной производительностью до 600-700 миллионов операций в секунду (MIPS),

- энергонезависимой памятью типа NAND-Flash емкостью 4 Гбайт,

- скоростными каналами обмена как внутри каждого тракта, так и между трактами,

- операционной системой реального времени (Real Time).

Перечисленные особенности позволяют на основе базового вычислителя создать унифицированный ряд вычислителей для оснащения современных комплексов бортового оборудования ЛА, способных реализовать функции самолетовождения, автоматического полета, индикации, управления общесамолетным оборудованием, а также для осуществления модернизации ранее разработанных и эксплуатируемых ИКБО. Экономические расчеты показывают, что при этом затраты на техническую эксплуатацию уменьшатся в 130 раз за счет:

- снижения стоимости вычислительной части комплексов бортового оборудования ЛА в 2,2 раза,

- отсутствия потребности в обменных фондах,

- снижения стоимости ремонта в 20 раз.

Источники информации

1. Бортовая Система Телеизмерений (БСТИ) для изделия РН АНГАРА на основе аппаратуры ПИРИТ.

2. Научно-технический отчет №34-97-VIII. «Результаты анализа видов и последствий отказов ЦПНК-114 на этапе "Взлет" самолета ИЛ-114», г.Жуковский, 1997 г.

3. Научно-технический отчет №35-97-VIII. «Результаты анализа видов и последствий отказов ЦПНК-114 на этапе "Крейсерского полета" самолета ИЛ-114», г.Жуковский, 1997 г.

4. А.А.Авакян, В.С.Седов «Использование однородных вычислительных сред для решения задач обмена информацией между цифровыми системами летательных аппаратов и побитного мажоритарного контроля систем с тройным резервированием», сборник докладов Международной научно-технической конференции «Актуальные проблемы анализа и обеспечения надежности и качества приборов, устройств и систем», г.Пенза, 1996 г.

5. Чуянов Г.А., Златомрежев В.И., Галушкин В.В., Ковернинский И.В., Екимов М.В., Егоров К.А., Лихоткина О.Ф. «Исследования по оптимизации архитектур полностью интегрированных комплексов бортового оборудования (ИКБО) и в их составе интегрированных комплексов», ГОСНИИАС. 100.0054-001, М., 2003 г.

6. О.Гобачевский. «Применение MicroPC в вычислительных комплексах специального назначения». Системная интеграция-Космонавтика, М., 1997 г.

7. Патент РФ №205470, приоритет от 15.08.93.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ИЗБЫТОЧНОСТЬЮ НЕОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2612569C2 |

| Способ обеспечения отказоустойчивого функционирования перспективного комплекса средств автоматизации командных пунктов военного назначения и устройство, его реализующее | 2019 |

|

RU2738730C1 |

| Способ функционирования комплексов средств автоматизации систем обработки информации и управления и устройство, его реализующее | 2020 |

|

RU2767018C2 |

| АРХИТЕКТУРА СИСТЕМЫ ОТКАЗОУСТОЙЧИВОЙ КОММУТАЦИИ ИНФОРМАЦИИ | 2016 |

|

RU2665227C2 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Способ отказоустойчивого функционирования вычислительных комплексов для систем обработки информации военного назначения и устройство его реализующее | 2022 |

|

RU2775259C1 |

| СПОСОБ КОНТРОЛЯ ДЛЯ ФУНКЦИОНАЛЬНОЙ РЕКОНФИГУРАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2022 |

|

RU2792920C1 |

| Способ формирования отказоустойчивой комплексной системы управления (КСУ) и отказоустойчивая КСУ | 2016 |

|

RU2629454C2 |

| Способ формирования самоорганизующейся структуры навигационного комплекса | 2016 |

|

RU2635825C1 |

| СПОСОБ РЕКОНФИГУРАЦИИ БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНЫХ СУДОВ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2024 |

|

RU2835221C1 |

Данная группа изобретений относится к области бортовых вычислительных систем повышенной надежности и может найти применение при создании вычислительных систем обработки информации в бортовых средствах авиационных и ракетно-технических систем. Техническим результатом является повышение надежности и достоверности обработки критических функций отказоустойчивой вычислительной системы. В основу предлагаемых способа и устройства положено многократное резервирование трактов, на которых реализованы критические функции комплексов бортового оборудования ЛА. Процессы управления избыточностью и вычислительный процесс разделены частично аппаратно, а программно разделены в цикле реального времени (Real Time). При этом в каждом из вычислительных трактов производится мажоритарное сравнение сигналов, прошедших через каждый тракт. Неоднозначность мажоритарного сравнения сигналов в различных трактах устраняют мажоритарным сравнением результатов сравнения сигналов. Достоверности мажоритарного контроля сигналов достигают путем статистической обработки случайного процесса изменения критического параметра, вычисления остаточной дисперсии и ее мажоритарного сравнения. 2 н.п. ф-лы, 10 ил.

1. Способ обеспечения отказоустойчивости в вычислительной системе обработки информации критических функций летательных аппаратов, заключающийся в том, что отказоустойчивость достигают путем многократного резервирования трактов реализации критических функций, отличающийся тем, что процессы управления избыточностью и вычислительный процесс разделяют в цикле реального времени (Real Time) и в каждом из вычислительных трактов производят мажоритарное сравнение сигналов, прошедших через каждый тракт, при этом неоднозначность мажоритарного сравнения сигналов в различных трактах устраняют неоднократным мажоритарным сравнением результатов сравнения сигналов, причем достоверность мажоритарного контроля сигналов достигают путем статистической обработки случайного процесса изменения критического параметра, вычисления остаточной дисперсии и ее мажоритарного сравнения.

2. Система управления избыточностью, которая включает в себя элемент тестового контроля, состоящий из аппаратных средств тестового контроля, которые содержат источники информации о состоянии элементов интерфейсно-вычислительных трактов, линии связи, через которые подается эта информация на программный модуль тестового контроля, многоуровневый (как минимум два уровня) элемент мажоритарного контроля, состоящий из аппаратных средств эхоконтроля, которые обеспечивают прохождение сигналов через все интерфейсно-вычислительные тракты и подачу их на программный модуль мажоритарного контроля, элемент реконфигурации интерфейсно-вычислительных трактов, состоящий из аппаратных средств реконфигурации, которые включают переключатели трактов, модули объединения выходов и программный модуль управления реконфигурацией, при этом аппаратные и программные средства управления избыточностью встроены в многократно резервированные интерфейсно-вычислительные тракты.

| ВЫЧИСЛИТЕЛЬ КОРРЕКТИРУЮЩИХ ФУНКЦИЙ | 2002 |

|

RU2225992C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДАТЧИКОВ УГЛОВОЙ ОРИЕНТАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2003 |

|

RU2241247C1 |

| РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО | 1991 |

|

RU2015544C1 |

| US 4403584 А, 13.09.1983. | |||

Авторы

Даты

2011-03-10—Публикация

2008-11-17—Подача