Изобретение относится к авиационной электронике, в частности к электродистанционным системам управления (fly by wire), и может быть использовано в системах устойчивости и управляемости летательными аппаратами.

Современная авиация характеризуется широким использованием систем автоматического управления (САУ), но это внешний контур управления самолетом, а система электродистанционного управления (ЭДСУ) - это внутренний контур. Бортовые системы автоматического управления превратились из средств, облегчающих летчику процесс управления самолетом, в средства, обеспечивающие эффективную эксплуатацию современного самолета, причем в САУ летчик включен во внешний контур управления, а в ЭДСУ - во внутренний. Современные самолеты, особенно истребители, для обеспечения высокой степени маневренности, проектируются статически неустойчивыми, и управлять ими с помощью механической проводки в принципе невозможно. Эффективным средством обеспечения продольной и боковой устойчивости являются ЭДСУ, которые одновременно выполняют функции демпферов колебаний. Оборудование самолета такими системами привело к тому, что летчик воспринимает в процессе управления продольное и боковое движение как движение самолета с хорошей устойчивостью и управляемостью.

Широко известны для автоматической управляемости самолета автопилоты, которые выполняют полет по заданной траектории с высокой степенью точности, но это все "саушные" задачи и для управления и парирования короткопериодических колебаний, особенно для самолета с неустойчивостью >10% не годятся.

Известна система управления ЭДСУ, представляющая собой резервированную аналоговую, построенную на прецизионных элементах, включающая систему улучшения устойчивости и управляемости. Система принимает, обрабатывает и передает команды управления летчика на исполнительные механизмы, а также демпфирует колебания самолета и улучшает его управляемость на летных режимах. За счет трехкратного резервирования ЭДСУ обеспечивает управление самолетом даже после возникновения в ней двух независимых отказов по тангажу, крену и направлению, см. "Многоцелевой боевой самолет MRGA PANAVIA 200", ОЦАОНТИ, М., 1976, с. 32-35.

Недостатками данной ЭДСУ являются:

- применение аналоговых вычислителей в каждом канале, что требует больших материальных затрат, т.к. вычислительные операции с аналоговыми величинами достаточно сложны;

- внесение изменений в программу вычислений (коррекция передаточных чисел) тем более сложна, требует "перепайки" во всех каналах, особенно это сложно на этапе отработки и испытаний.

Известна ЭДСУ, применяемая на истребителе F-16, которая является первой аналоговой ЭДСУ, имеющей четырехканальную схему резервирования без резервной механической проводки. Самолет статически неустойчив, его устойчивость обеспечивается искусственно путем отклонения управляющих поверхностей, кроме того, ЭДСУ ограничивает угол атаки самолета и перегрузки. Четыре независимых электрических канала обеспечивают нормальный полет самолета при двух отказавших канала, см. “Истребитель Дженерал Дайнэмикс, F-16 Файтинг Фолкон", ЦАГИ. - М., 1985, с. 20.

К недостаткам построения данной ЭДСУ относятся также сложность отработки вычислителей в процессе летных испытаний, дополнительные настройки (подстройки) в каналах управления при замене датчиков углов крена, тангажа, атаки и т.д.

Известна цифровая электродистанционная система фирмы Cneppu, обеспечивающая соответствующее управление на всех режимах полета вертолета АН-64 для обеспечения хороших летных характеристик, а именно повышения устойчивости, усиления команд управления, выдерживания заданных режимов полета, координации разворота, усиление управления на режиме висения и выдерживания курса, см. Боевой вертолет Макдоннел-Дуглас Ан-64А АПАЧ, ЦАГИ. - М, 1989, с. 29 - прототип.

Несмотря на привлекательность применения “цифры” в ЭДСУ, полностью цифровая система управления обладает следующими недостатками:

- датчики первичной информации (угловых скоростей, угла атаки и пр.) почти все являются аналоговыми, т.е. приспособлены для аналоговых потребителей, поэтому преобразование их сигналов в “цифру” представляет определенные сложности;

- привода управляющих поверхностей (элеронов, дифференциальных стабилизаторов и т.д.) также в большинстве случаев аналоговые, так что требуется обратное преобразование из “цифры” в “аналог”;

- помехоустойчивость цифровых систем значительно хуже аналоговых;

- в чисто цифровом вычислителе довольно трудно реализовать фильтры высших порядков (второго и выше), кроме того, существует проблемы цифровой фильтрации по сравнению с аналоговой, такие как: восстановление фильтров после сбоя напряжения питания, погрешности квантования, увеличения части измерительного канала, для которой необходимо предусматривать расширенный диапазон изменения сигнала, учитывающий возможную помеху.

Технической задачей изобретения является повышение эффективности применения ЭДСУ за счет

- применения комбинированной электрической схемы вычислителя: аналоговой и цифровой, т.е. аналого-цифровой;

- простоты и удобства перестройки передаточных коэффициентов трактов крена, тангажа и направления путем простого перепрограммирования нужных ячеек схемы памяти вычислителя, для чего применяется РПЗУ;

- введения перекрестных связей между каналами управления, что упрощает общую технологическую прозрачность законов управления вычислителя;

- снижение габаритно-массовых характеристик и потребляемой мощности.

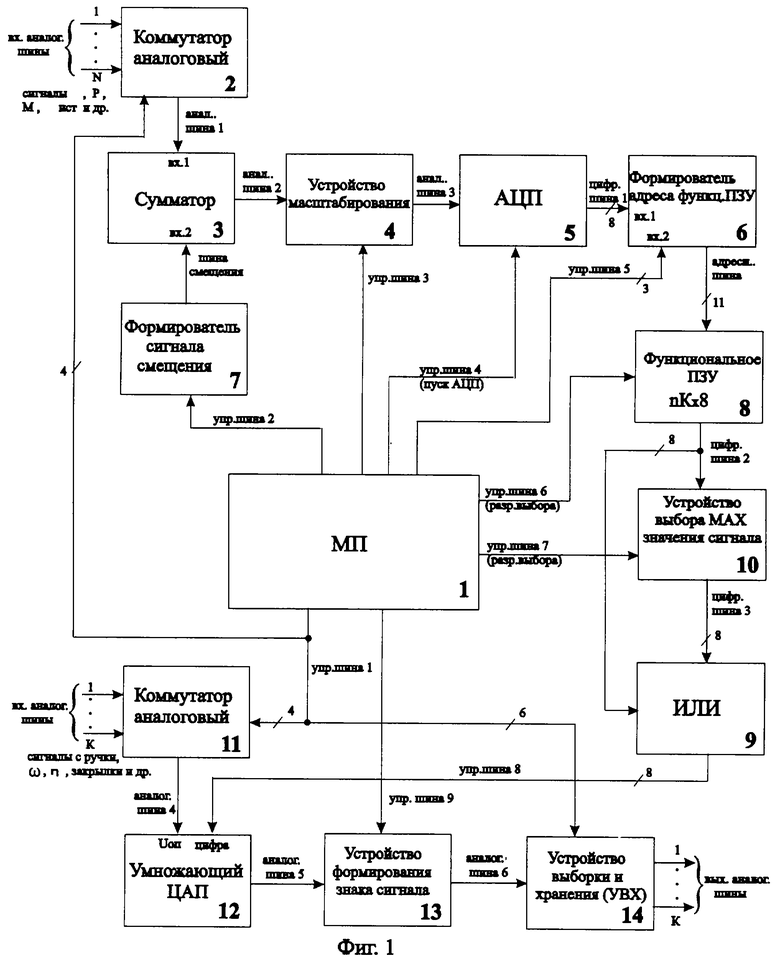

Для решения поставленной задачи предлагается вычислитель корректирующих функций, содержащий микропроцессор, вторые входные аналоговые шины 1...К, первые входные аналоговые шины 1...N, выходные аналоговые шины 1...К, первый и второй коммутаторы, сумматор, устройство масштабирования, АЦП, формирователь адреса функционального ПЗУ, устройство выбора максимального сигнала, умножающий ЦАП, устройство формирования знака сигнала, устройство выборки и хранения, межблочные аналоговые шины 1-6, межблочные цифровые шины 1-3, шины управления 1-10, шину смещения, адресную шину, соединенные следующим образом: входные аналоговые шины 1...К через первый аналоговый коммутатор, сумматор и устройства масштабирования первой, второй и третьей аналоговыми шинами соответственно соединены с входом АЦП, выход которого цифровым восьмиразрядным кодом первой цифровой шиной соединен с формирователем адреса функционального ПЗУ, который по шине управления 5 соединен также с выходом микропроцессора тремя разрядами цифрового кода; выход формирователя адреса функционального ПЗУ одиннадцатиразрядной адресной шиной соединен с функциональным ПЗУ, выход которого второй цифровой шиной соединен с первым входом схемы ИЛИ непосредственно, а со вторым входом - через устройство выбора максимума сигнала, выход этой схемы ИЛИ девятой цифровой шиной соединен с цифровыми входами умножающего ЦАПа, но аналоговый вход которого через второй аналоговый коммутатор четвертой аналоговый шиной соединен со вторыми входными аналоговыми шинами 1...К, выход умножающего ЦАПа пятой аналоговой шиной соединен с устройством формирования знака сигнала, выход которого шестой аналоговой шиной соединен с УВХ, выходы которого являются выходами вычислителя и соединены с выходными аналоговыми шинами 1...К; микроконтроллер также соединен первой управляющей шиной с управляющими входами первого и второго аналоговых коммутаторов и устройством выборки и хранения, второй управляющей шиной - с управляющим входом формирователя сигнала смещения, выход которого шиной смещения соединен с вторым входом сумматора, третьей управляющей шиной - с управляющим входом устройства масштабирования, четвертой управляющей шиной - с управляющим входом АЦП, шестой управляющей шиной - с управляющим входом функционального ПЗУ, седьмой управляющей шиной - с управляющим входом устройства выбора максимума сигнала, восьмой управляющей шиной - с управляющим входом умножающего ЦАПа, девятой управляющей шиной - с управляющим входом устройства формирования знака сигнала.

На фиг.1 показана структурная схема вычислителя, которая содержит: 1 - микропроцессор (МП), 2 и 11 - первый и второй аналоговые коммутаторы соответственно, 3 - сумматор, 4 - устройство масштабирования, 5 -АЦП, 6 - формирователь адреса функционального ПЗУ, 7 - формирователь сигнала смещения, 8 - функциональное ПЗУ, 9 - схема ИЛИ, 10 - устройство выбора максимума сигнала, 12 - умножающий ЦАП, 13 - устройство формирования знака сигнала, 14 - устройство выборки и хранения (УВХ), вторые входные аналоговые шины 1...К, первые входные аналоговые шины 1...N, выходные аналоговые шины 1...К, шины управления 1...9, аналоговые межблочные шины 1...6, цифровые межблочные шины 1...3, шину смещения, адресную шину.

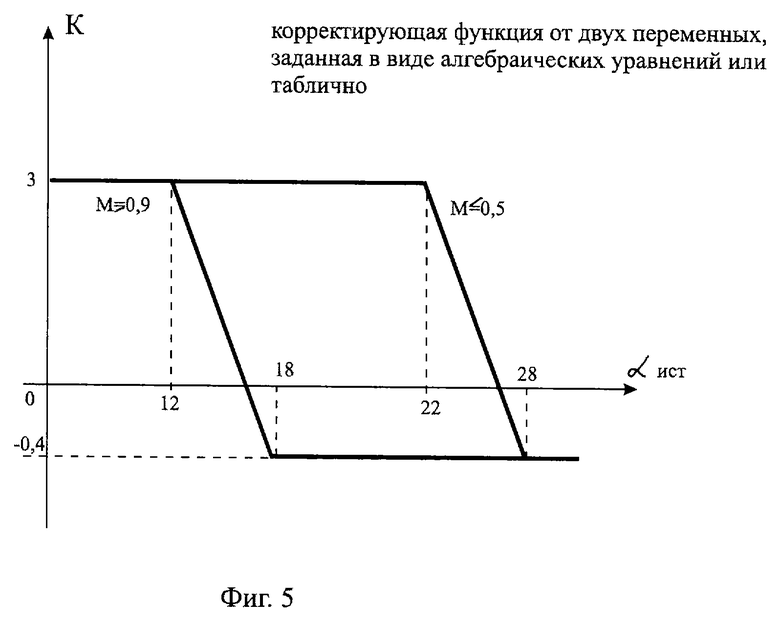

На фиг.2-5 показаны примеры корректирующих функций.

Первые входные аналоговые шины 1...N соединены с входами первого аналового коммутатора 2, выходная первая аналоговая шина которого соединена с первым входом сумматора 3, с вторым входом которого соединена шина смещения с выхода формирователя сигнала смещения 7, выход сумматора 3 второй аналоговой шиной соединен с входом устройства масштабирования 4, выход которого третьей аналоговой шиной соединен с входом АЦП 5, выход которого восьмиразрядной параллельной первой цифровой шиной соединен с первым входом формирователя адреса функционального ПЗУ 6, второй вход которого трехразрядной пятой шиной управления соединен с соответствующим выходом МП 1, выход формирователя адреса 6 одиннадцатиразрядной адресной шиной соединен с адресными входами функционального ПЗУ 8, выходная вторая цифровая восьмиразрядная шина данных которого соединена с первым входом схемы ИЛИ 9 непосредственно, а со вторым ее входом - через устройство выбора максимального сигнала 10 третьей цифровой шиной, выход схемы ИЛИ 9 восьмой управляющей шиной соединена с цифровыми входами умножающего ЦАП 12, вторые входные аналоговые шины 1...К соединены с входами второго аналогового коммутатора 11, выходная четвертая аналоговая шина которого соединена с входом Uoп умножающего ЦАПа 12, а его выходная пятая аналоговая шина соединена с входом устройства формирования знака сигнала 13, выходная шестая аналоговая шина которого соединена с входом УВХ 14, аналоговые выходы 1...К которого являются выходом вычислителя; МП 1 управляющими шинами соединен с узлами вычислителя, причем первой управляющей шиной - с первым и вторым аналоговыми коммутаторами 2 и 11 соответственно и с УВХ 14, второй управляющей шиной - с формирователем сигнала смещения 7, третьей управляющей шиной - с устройством масштабирования 4, четвертой управляющей шиной - с входом запуск АЦП 5, пятой управляющей шиной - с входом 2 формирователя адреса функционального ПЗУ 6, шестой управляющей шиной - с входом разрешения выборки функционального ПЗУ 8, седьмой управляющей шиной - с устройством выбора МАХ сигнала 10, девятой управляющей шиной - с устройством формирования знака сигнала 13, восьмая управляющая шина соединяет выход схемы ИЛИ 9 с умножающим ЦАП 12.

Вычислитель может быть выполнен на следующих известных элементах. МП 1 - на ИМС РIС16С74 фирмы MICRO-CHIP; аналоговые коммутаторы 2 и 11 - на ИМС серии 590, см. “Цифровые и аналоговые интегральные микросхемы", Справочник. - М.: Радио и Связь, 1989, с. 447-450; сумматор 3, устройство формирования знака сигнала 13 и устройство масштабирования 4 - на операционных усилителях серии 140, см. там же, с. 343-345; АЦП 5 и умножающий ЦАП 12 - на ИМС серии 572, см. там же, с. 428, 434; формирователь адреса функционального ПЗУ 6 - на регистрах ТМ9 и цифровом коммутаторе КП11 ИМС серии 1533, см. там же, с. 53 и 55 соответственно; функциональное ПЗУ 8 - на ИМС серии 556 РТ 7А (в серии, а на этапе отработки ИМС 573), см. там же, с. 316 и 317; схема ИЛИ 9 - на ИМС серии 533, там же, с. 49; устройство выбора МАХ сигнала - на цифровых коммутаторах КП11 и цифровых схемах сравнения СП1, регистрах ИР 23 ИМС серии 1533, см. там же, с. 55 и 50 соответственно; устройство формирования знака сигнала - на аналоговом ключе ИМС серии 590 и операционном усилителе серии 140, см. там же; УВХ 14 на ИМС 1100СК2 ж. "Схемотехника" №6, 2001, с. 16 и 17.

Вычислитель работает следующим образом.

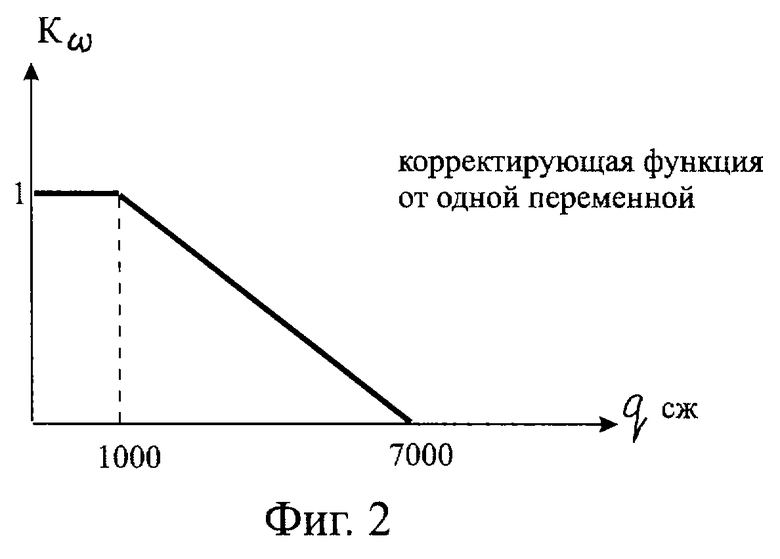

Вначале, для более полного понятия работы вычислителя, внесем несколько общих замечаний. Маневр самолета при ручном управлении от ручки управления (штурвала) в общем виде ограничивается несколькими параметрами: так радиус боевого разворота ограничивается допустимой угловой скоростью разворота, скоростью (скоростным напором gсж), высотой полета (давлением Рст), допустимым углом атаки (αист) и пр., т.е. при очень энергичном управлении, не учитывающем эти факторы, можно или разрушить планер самолета (при большой угловой скорости или ускорении) или потерять управляемость (сваливание на крыло при превышении допустимого угла атаки, вхождение в штопор при входе в разворот при малой скорости и большом угле крена) и т.д. ЭДСУ строится таким образом, что по заранее рассчитанным математическим образом законам (для данного типа самолета) она не позволит выйти на критические режимы, как бы пилот не старался это сделать. Можно сказать, что маневренные возможности самолета, а также возможность осуществления того или иного режима полета определяются и ограничены его аэродинамическими, прочностными характеристиками и энерговооруженностью. Практически это выглядит следующим образом. Для каждого канала управления самолета (продольного, крена и направления) рассчитываются, а затем и моделируются основные зависимости, например, зависимость коэффициента угловой скорости (Кω) от скоростного напора (см. фиг.2), из которого видно, что чем больше скоростной напор (qcж), тем меньше допустимая величина Кω.

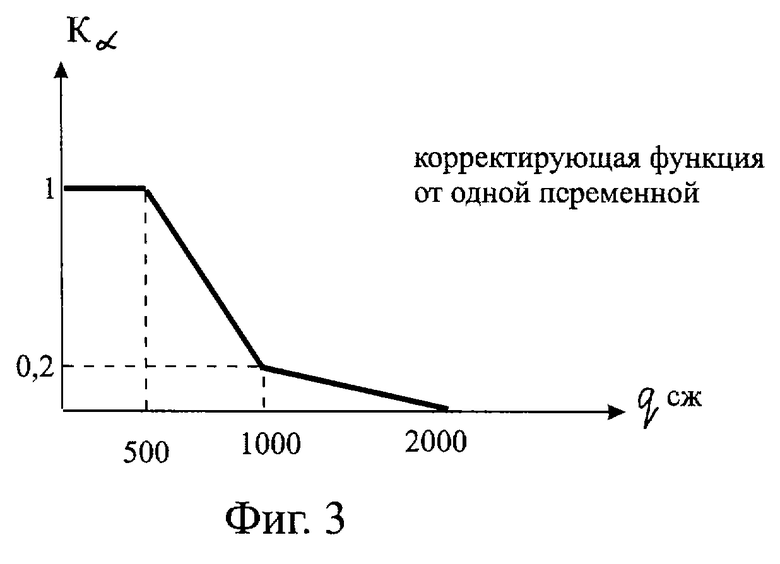

На фиг.3 показана зависимость коэффициента угла атаки Кα также от скоростного напора qсж. Для каждого типа самолета определяются графики существенно важных зависимостей (корректирующих функций), которые закладываются в структурные схемы ЭДСУ. Конкретные точки всех этих графиков для каждого момента полета определяются предложенным вычислителем и выводятся в каналы управления ЭДСУ.

Работу вычислителя определяет микропроцессор МП 1, который по заранее составленной программе всех временных зависимостей работы узлов и блоков вычислителя во времени и между собой вырабатывает управляющие сигналы. Рассмотрим работу вычислителя на примере обработки простой корректирующей функции (фиг.2). Первый управляющий сигнал по упр. шине 1 управляет работой аналоговых коммутаторов 2 и 11, поочередно включая по циклу все входные аналоговые шины.

При включении шины значение сигнала, например qcж, проходит на выход аналогового коммутатора 2, а соответствующее ему значение тракта управления, например, ω, - на выход коммутатора 11. С выхода коммутатора 2 значение qсж поступает на первый вход сумматора 3. Сумматор 3 служит для смещения функций, имеющих отрицательные значения, в положительную область и для выделения только переменной части функции, путем смещения начала переменной части функции к оси ординат, так как на фиг.2 функция имеет положительные значения, то она смещается к оси ординат и выделяется для дальнейшей обработки только часть от 1000 до 7000 ед.

qcж - величина смещения и выделения переменной части функций определяется программно заранее для каждой функции, а величины смещения и выделения формируются на формирователе сигнала смещения 7 и поступают на второй вход сумматора 3. Обработанный входной сигнал поступает по второй аналоговой шине на устройство масштабирования 4, где нормализуется, т.е. приводится к полной шкале АЦП 5. Приведенный т.о. аналоговый сигнал по третьей аналоговой шине поступает на вход АЦП 5, где преобразуется в цифровой восьмиразрядный код и по первой цифровой шине поступает на первый вход формирователя адреса функционального ПЗУ 6, на второй вход которого по пятой управляющей шине с МП 1 поступает трехразрядный цифровой код, который дополняет старшими разрядами код АЦП, образуя одиннадцатиразрядный код, выставляемый по адресной шине на функциональное ПЗУ 8. В соответствии с этим адресом на выходе ПЗУ 8 (по заранее записанным данным), выполненном для удобства в формате 2К×8, на второй цифровой шине появляется цифровой восьмиразрядный код, который в случае простой функции (функции от одной переменной) непосредственно через схему ИЛИ 9 поступает на цифровые входы умножающего ЦАПа 12, на опорный вход которого Uoп по четвертой аналоговой шине поступает аналоговый сигнал с выхода коммутатора 11, так в случае обработки функции на фиг.2 это значение тракта угловой скорости ω. Программа МП 1 состоит из подпрограмм, число которых соответствует числу обрабатываемых функций. Умножающий ЦАП 12 имеет коэффициент передачи в диапазоне от 1 до 0 в соответствии с заранее вычисленными значениями. Всего при обработке каждой функции на всю ее величину приходится 256 уровней квантования, что вполне достаточно для плавного управления. После умножающего ЦАПа 12 сигнал по пятой аналоговой шине поступает на устройство формирования знака сигнала 13, который задается с МП 1 по девятой управляющей шине, после чего по шестой аналоговой шине он поступает на УВХ 14, где запоминается на время до следующей обработки данного тракта. Выходные напряжения УВХ 14 далее поступают в продольный канал (крена, направления). В каждом канале ставится свой вычислитель. Сама же ЭДСУ также имеет четыре канала по каждой координате (тракту управления). Каналы ЭДСУ имеют несколько сечений контроля, которые построены по принципу мажоритарного выбора.

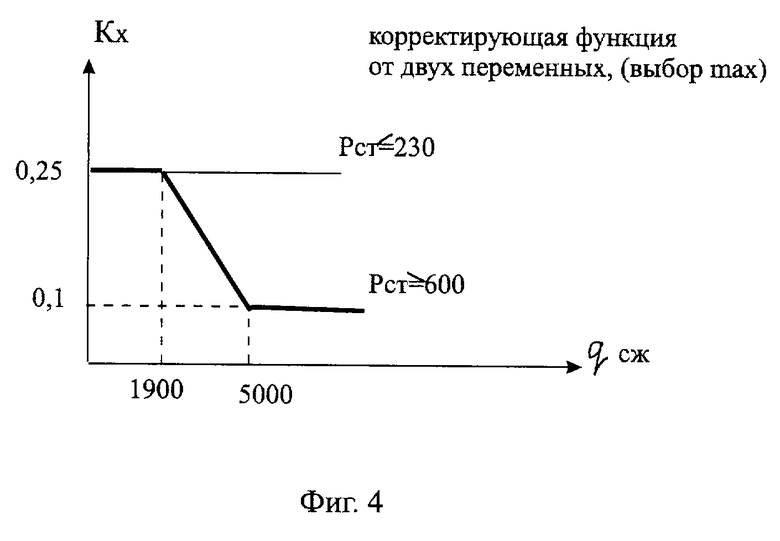

Обработка более сложной корректирующей функции от двух переменных, например qсж и Pст типа выбор МАХ (фиг.4) происходит точно таким же образом за два такта управления.

Т.к. подобную функцию можно представить в виде двух простых от одной переменной qсж и Рст соответственно, то в первом такте управления, как было представлено выше, обрабатывается функция, например от qcж, и цифровой восьмиразрядный код с выхода функционального ПЗУ 8 по 1-му сигналу управляющей шины 7 записывается в первый регистр устройства выбора МАХ 10. Во втором такте управления обрабатывается функция от Рст и соответствующий цифровой восьмиразрядный код с выхода функционального ПЗУ 8 по 2-му сигналу управляющей шины 7 записывается во второй регистр устройства выбора МАХ 10.

Затем по 3-му сигналу управляющей шины 7 разрешается выбор максимального значения цифрового восьмиразрядного кода устройством выбора МАХ 10, который через схему ИЛИ 9 поступает на цифровые входы умножающего ЦАПа 12.

Дальнейшее прохождение сигналов аналогично описанному выше для простой функции от одной переменной.

Обработка сложной корректирующей функции от двух переменных, например αист и М, (фиг.5), которая может быть представлена в виде алгебраических уравнений или таблицы, происходит за два такта управления следующим образом.

В первом такте управления аналогично обработке функции от одной переменной на выходе АЦП 5 при обработке параметра αист формируется цифровой восьмиразрядный код, старшие шесть разрядов которого по цифровой шине 1 поступают на первый вход формирователя адреса функционального ПЗУ 6 и по 1-му сигналу управляющей шины 5 записываются в первый регистр формирователя 6.

Во втором такте управления аналогично обрабатывается параметр М и с выхода АЦП 5 старшие пять разрядов цифрового восьмиразрядного кода по цифровой шине 1 поступают на первый вход формирователя 6 и по второму сигналу управляющей шины 1 записываются во второй регистр формирователя 6.

Таким образом формируется одиннадцатиразрядный адрес функционального ПЗУ 8 путем "склеивания" шестиразрядного и пятиразрядного адресов. Преобразование параметра в шестиразрядный или пятиразрядный код определяется скоростью изменения входного параметра. Быстро меняющиеся во времени параметры преобразуются в шестиразрядный код, медленно меняющиеся - в пятиразрядный.

Дальнейшее прохождение сигналов аналогично описанному выше для простой функции от одной переменной.

Построение вычислителя по предложенному принципу удачно объединяет достоинства аналоговой и цифровой техники, при минимальных габаритно-массовых характеристиках, высокой точности, легкой перестраиваемости коэффициентов путем простого перепрограммирования функционального ПЗУ 8.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫСОКОСТАБИЛЬНЫЙ ДАТЧИК УГЛОВОЙ СКОРОСТИ | 2003 |

|

RU2286581C2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

| Устройство для измерения температуры | 1986 |

|

SU1377609A1 |

| Замкнутый шаговый электропривод с самокоммутацией и дроблением шага | 1988 |

|

SU1511842A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Аналого-цифровой анализатор сигналов | 2024 |

|

RU2826857C1 |

Изобретение относится к авиационной электронике в системах устойчивости и управляемости летательными аппаратами. Технический результат заключается в повышении эффективности применения электродистанционной системы управления (ЭДСУ). Особенностями предложенной системы является применение комбинированной электрической схемы вычислителя - аналоговой и цифровой, простота и удобство перестройки передаточных коэффициентов трактов крена, тангажа и направления путем перепрограммирования нужных ячеек памяти вычислителя, введение перекрестных связей между каналами управления для упрощения законов управления вычислителя, снижение массогабаритных характеристик и потребляемой мощности. 5 ил.

Вычислитель корректирующих функций электродистанционной системы управления, содержащий микропроцессор, входные аналоговые шины 1...К, входные аналоговые шины 1...N и которые являются входами вычислителя, выходные аналоговые шины 1...М, первый и второй коммутаторы, сумматор, устройство масштабирования, АЦП, формирователь адреса функционального ПЗУ, устройство выбора максимального сигнала, умножающий ЦАП, устройство формирования знака сигнала, устройство выборки и хранения (УВХ), межблочные аналоговые шины, межблочные цифровые шины, шины управления, шину смещения, адресную шину, соединенные следующим образом: входные аналоговые шины 1...К через первый аналоговый коммутатор, сумматор и устройства масштабирования первой, второй и третьей аналоговыми шинами соответственно соединены с входом АЦП, выход которого цифровым восьмиразрядным кодом первой цифровой шиной соединен с формирователем адреса функционального ПЗУ, который по шине управления соединен также с выходом микропроцессора тремя разрядами цифрового кода; выход формирователя адреса функционального ПЗУ одиннадцатиразрядной адресной шиной соединен с функциональным ПЗУ, выход которого второй цифровой шиной соединен с первым входом схемы ИЛИ непосредственно, а со вторым входом - через устройство выбора максимума сигнала, выход схемы ИЛИ цифровой шиной соединен с цифровыми входами умножающего ЦАПа, аналоговый вход которого через второй аналоговый коммутатор четвертой аналоговый шиной соединен с аналоговыми шинами 1...N; выход умножающего ЦАПа пятой шиной соединен с устройством формирования знака сигнала, выход которого шестой аналоговой шиной соединен с УВХ, выходы которого являются выходами вычислителя; микропроцессор соединен первой управляющей шиной с управляющими входами первого и второго аналоговых коммутаторов и устройством выборки и хранения, второй управляющей шиной - с управляющим входом формирователя сигнала смещения, выход которого шиной смещения соединен с вторым входом сумматора, третьей управляющей шиной - с управляющим входом устройства масштабирования, четвертой управляющей шиной - с управляющим входом АЦП, шестой управляющей шиной - с управляющим входом функционального ПЗУ, седьмой управляющей шиной - с управляющим входом устройства выбора максимума сигнала, девятой управляющей шиной - с управляющим входом устройства формирования знака сигнала.

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| - М., 1989 | |||

| RU 2058495 С1, 20.04.1996 | |||

| ПУЛЬТ, СИСТЕМА И СПОСОБ РУЧНОГО УПРАВЛЕНИЯ И СТАБИЛИЗАЦИИ РЕГУЛИРУЕМОЙ ВЕЛИЧИНЫ ДВИЖЕНИЯ ЛЕТАТЕЛЬНОГО АППАРАТА (ВАРИАНТЫ) "АРЖЕСАН" | 1996 |

|

RU2128600C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АДАПТИВНЫМ МОБИЛЬНЫМ РОБОТОМ | 1998 |

|

RU2143334C1 |

| US 4403584, 13.09.1983. | |||

Авторы

Даты

2004-03-20—Публикация

2002-03-19—Подача