Заявление о приоритете в соответствии с 35 §119 Кодекса законов США

Настоящая заявка на выдачу патента испрашивает приоритет по предварительной заявке США №60/822,279, озаглавленной «Способ и устройство для совместной передачи прерывания в общей шине в многоранковой подсистеме памяти», поданной 14 августа 2006 г., переуступленной правопреемнику настоящей заявки и настоящим полностью включена в настоящий документ посредством ссылки.

Область техники, к которой относится изобретение

Настоящее раскрытие относится, в общем, к системам памяти, более конкретно к сигнализации между контроллером памяти и памятью в системе памяти.

Уровень техники

В настоящее время системы памяти широко используются в системах обработки данных для хранения данных, необходимой для различных процессорных модулей. Система памяти обычно включает в себя контроллер памяти, который управляет доступом к памяти. Память, как правило, сконфигурирована в виде матрицы, образованной строками и столбцами ячеек памяти, и каждая ячейка памяти способна хранить один бит информации. Блок ячеек памяти может быть доступен процессорному модулю или другому источнику посредством обеспечения подходящего адреса контроллеру памяти.

Адрес от процессорного модуля может быть отправлен контроллеру памяти по шине с адресом строки, занимающим старшие разряды и адресом начала столбца, занимающим младшие разряды. Для отправки в память адреса строки после адреса начала столбца контроллер памяти использует схему уплотнения.

Когда процессорному модулю требует доступ к блоку памяти, он направляет команду считывания или записи на контроллер памяти. Каждая команда считывания и записи включает в себя адрес. Порядок, по которому контроллер памяти исполняет каждую команду, зависит от того, пытается ли процессорный модуль осуществить доступ к открытой странице памяти. Обычно «страница» ассоциируется со строкой памяти, а «открытая страница» означает, что память указывает на строку памяти и для доступа к блоку памяти требуется только адрес начала столбца и строб доступа к столбцу (CAS). Для доступа к неоткрытой странице памяти контроллер памяти должен представить адрес строки и строб доступа к строке (RAS) в память для перемещения указателя перед тем, как представить в память адрес начала столбца и CAS.

В настоящее время в системах памяти используются разнообразные памяти. Синхронное динамическое оперативное запоминающее устройство (SDRAM) является лишь одним примером. Когда процессорный модуль производит запись в SDRAM или иную память, данные передаются по шине данных между контроллером памяти и памятью. Маска данных может быть применена контроллером памяти для маскирования данных в информационной шине. Когда маска данных не утверждается, данные на информационной шине будут записаны в память. Если маска данных утверждается, данные на информационной шине будут проигнорированы, а операция записи не будет выполнена.

Маска данных применяется только во время операции записи. Когда процессорный модуль не производит запись в SDRAM или другие устройства памяти, контроллер памяти трижды определяет маску данных. Таким образом, существует возможность использовать маску данных для других целей, когда процессорный модуль не выполняет операцию записи. Используя маску данных таким образом, дополнительные связи могут осуществляться между контроллером памяти и данной памятью без увеличения количества выводов на устройстве памяти.

Раскрытие изобретения

Раскрывается один аспект системы памяти. Система памяти включает в себя первое и второе устройства памяти и контроллер памяти, сконфигурированный для селективного активирования одного из устройств памяти, причем контроллер памяти имеет первую линию, связанную с первым и вторым устройствами памяти, и вторую линию, связанную с первым и вторым устройствами памяти. Первое устройство памяти сконфигурировано так, чтобы предоставлять сообщение на контроллер памяти по первой линии, а второе устройство памяти сконфигурировано так, чтобы предоставлять сообщение на контроллер по второй линии. Первое устройство памяти дополнительно сконфигурировано так, чтобы не загружать первую линию, а второе устройство памяти дополнительно сконфигурировано так, чтобы не загружать вторую линию, когда контроллер памяти осуществляет запись в активированное устройство памяти.

Раскрывается другой аспект изобретения. Система памяти включает в себя первый и второй ранки памяти, каждый из ранков памяти имеет устройство памяти, а контроллер памяти сконфигурирован для селективного активирования одного из ранков памяти и записи данных в активированный ранк памяти, причем контроллер памяти имеет первую и вторую линии, каждая связана с первым и вторым ранками памяти, первая и вторая линии сконфигурированы так, чтобы обеспечивать маску данных, относящуюся к упомянутым данным. Устройство памяти в первом ранке памяти сконфигурировано так, чтобы предоставить сообщение на контроллер памяти по первой линии, а устройство памяти во втором ранке памяти сконфигурировано так, чтобы предоставить сообщение на контроллер памяти по второй линии.

Раскрывается один аспект способа передачи данных между контроллером памяти и памятью, имеющей первое и второе устройства памяти. Контроллер памяти включает в себя линию, связанную с первым и вторым устройствами памяти. Способ включает в себя этапы, на которых предоставляют сообщение от первого устройства памяти на контроллер памяти по первой линии, активируют второе устройство памяти таким образом, чтобы контроллер памяти записывал данные во второе устройство памяти, и установки первого устройства памяти в такое состояние, в котором линия не нагружается, когда контроллер памяти записывает во второе устройство памяти.

Другой аспект способа передачи данных между контроллером памяти и памятью, имеющей первый и второй ранки памяти. Каждый из ранков памяти включает в себя устройства памяти. Контроллер памяти включает в себя первую линию, связанную с устройством первого ранка памяти, и вторую линию, связанную с устройством второго ранка памяти. Способ включает в себя этапы, на которых предоставляют сообщение от устройства первого ранка памяти на контроллер памяти по первой линии, активируют второй ранк памяти таким образом, чтобы контроллер памяти записывал во второй ранк памяти, предоставляют маску данных от контроллера памяти в второй ранк памяти по первой и второй линиям, когда контроллер памяти записывает во второе устройство памяти.

Раскрывается дополнительный аспект системы памяти. Система памяти включает в себя первое и второе устройства памяти и контроллер памяти, сконфигурированный для селективного активирования одного из устройств памяти, контроллер памяти имеет первую линию, связанную с первым и вторым устройствами памяти и вторую линию, связанную с первым и вторым устройствами памяти. Первое устройство памяти дополнительно включает в себя средство для предоставления сообщения на контроллер памяти по первой линии, а второе устройство памяти включает в себя средство для предоставления сообщения на контроллер памяти по второй линии. Средство для предоставления сообщения на контроллер памяти по первой линии и средство для предоставления сообщения на контроллер памяти по второй линии каждое сконфигурировано так, чтобы не загружать соответствующую ей линию, когда контроллер памяти производит запись на активированное устройство памяти.

Раскрывается другой аспект системы памяти. Система памяти включает в себя первый и второй ранки памяти, каждый из ранков памяти имеет устройство памяти и контроллер памяти, сконфигурированный так, чтобы селективно активировать один из ранков памяти и записывать данные в активированный ранк памяти. Контроллер памяти имеет первую и вторую линии, каждая из которых связана с первым и вторым ранками памяти, первая и вторая линии сконфигурированы так, чтобы выводить маску данных, относящуюся к данным. Устройство памяти в первом ранке памяти включает в себя средство для предоставления сообщения на контроллер памяти по первой линии, и устройство памяти во втором ранке памяти включает в себя средство для предоставления сообщения на контроллер памяти по второй линии.

Понятно, что другие аспекты настоящего изобретения будут легко понятны для специалистов в данной области техники из подробного описания, в котором показаны различные варианты осуществления изобретения вместе с приложенными чертежами. Понятно, что изобретение может быть осуществлено и в других различных вариантах, его некоторые детали могут быть модифицированы в разных отношениях, не выводящих его за рамки настоящего изобретения. Соответственно, чертежи и подробное описание следует рассматривать как иллюстративный, но не ограничивающий объем заявки, материал.

Краткое описание чертежей

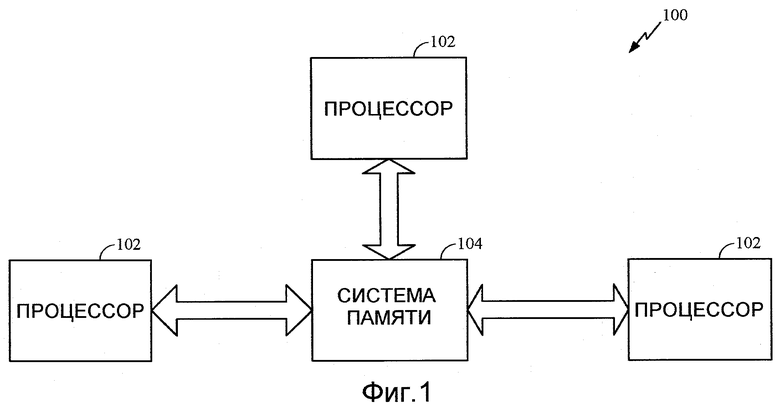

Фиг.1 - концептуальная блок-схема, представляющая пример системы обработки данных;

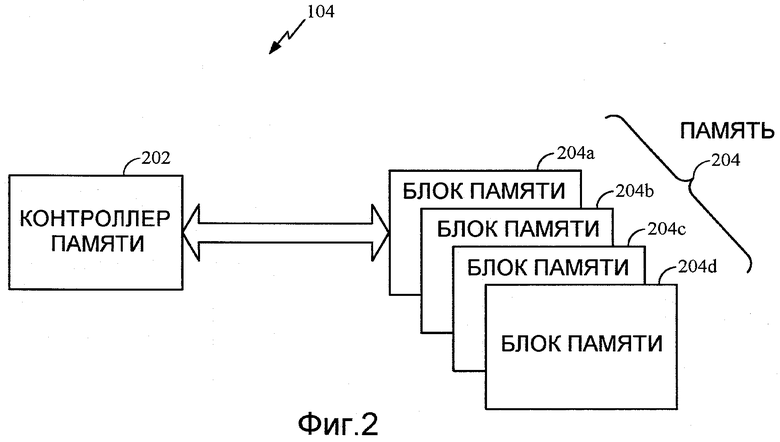

Фиг.2 - концептуальная блок-схема системы памяти;

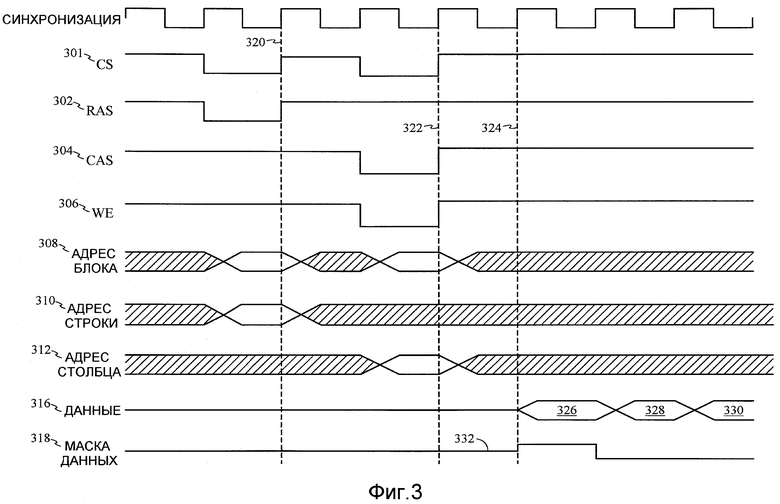

Фиг.3 - временная диаграмма, представляющая пример выполнения операции записи в систему памяти;

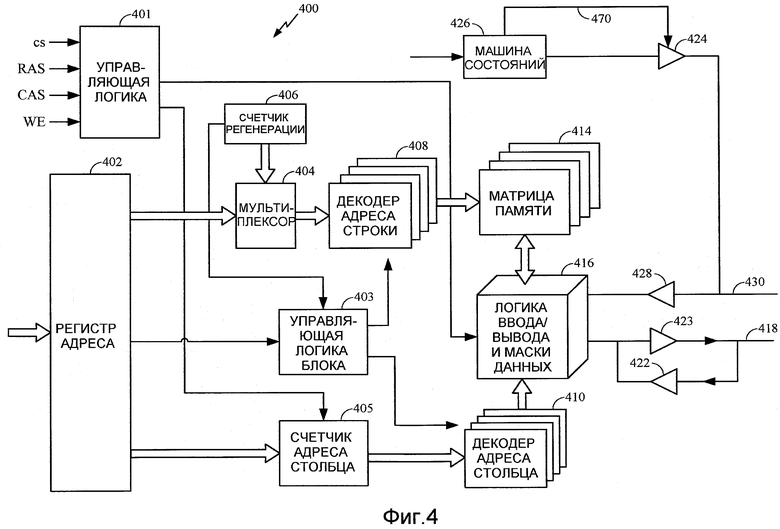

Фиг.4 - функциональная блок-схема, представляющая пример устройства памяти;

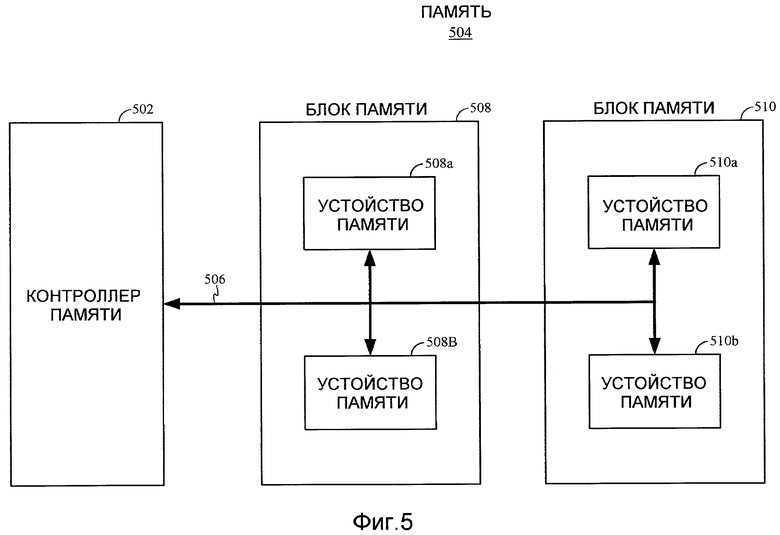

Фиг.5 - концептуальная блок-схема, представляющая другой пример системы памяти;

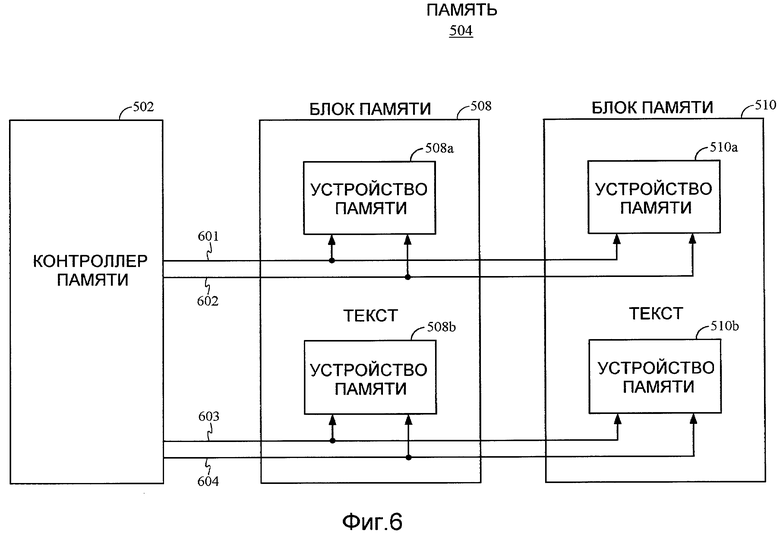

Фиг.6 - концептуальная блок-схема, представляющая пример сигнализации в системе памяти на Фиг.5;

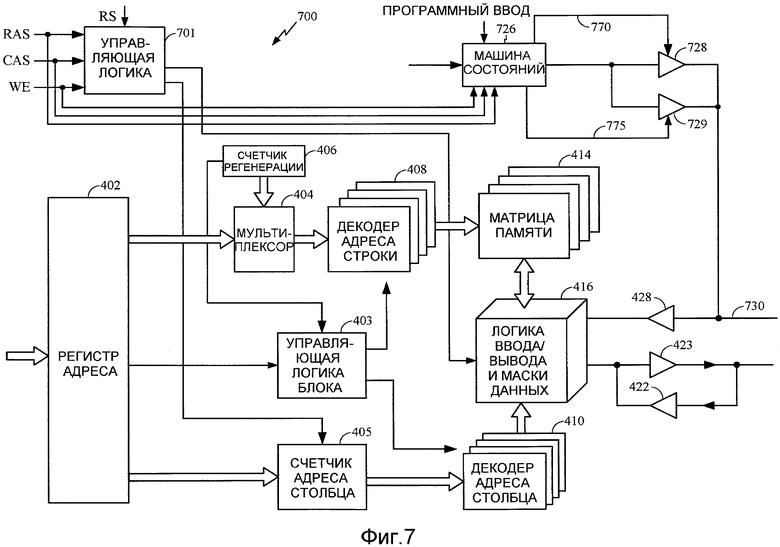

Фиг.7 - функциональная блок-схема, представляющая другой пример устройства памяти.

Осуществление изобретения

Подробное описание, приведенное ниже вместе с приложенными чертежами, предназначено для описания различных вариантов осуществления настоящего изобретения и не подразумевает представления только этих вариантов, как единственно возможных, в которых может быть реализовано настоящее изобретение. Раздел осуществления изобретения содержит конкретные детали с целью обеспечения полного понимания настоящего изобретения. Однако, очевидно, что для специалистов в данной области техники, настоящее изобретение может быть осуществлено без этих конкретных подробностей. В некоторых случаях на блок-схемах изображены хорошо известные структуры и компоненты, с тем, чтобы избежать неопределенности, и представляют концепцию настоящего изобретения.

На Фиг.1. приведена концептуальная блок-схема, иллюстрирующая пример системы обработки данных. Система 100 обработки данных может быть набором устройств, которые взаимодействуют для выполнения одной или нескольких процессорных функций. Обычные приложения системы 100 обработки данных включают в себя, но этим не ограничиваются, настольные ПК, портативные ПК, серверы, мобильные телефоны, персональные цифровые секретари (PDA), игровые консоли, пейджеры, модемы, аудиоустройства, медицинские устройства, самодвижущиеся устройства, видеоустройства, промышленное оборудование, или любые другие машины или устройства, способные обрабатывать информацию, извлекать и хранить информацию.

Система 100 обработки данных показана с системой 104 памяти, которая может быть доступна любому количеству процессорных модулей. В конфигурации, показанной на Фиг.1, изображены три процессора 102 в соединении с системой 104 памяти. Каждый процессор 102 может быть универсальным вычислительным устройством, таким как микропроцессор, специализированным вычислительным устройством, таким как устройство цифровой обработки сигналов (DSP), специализированная интегральная микросхема (ASIC), контроллер прямого доступа в память (DMA), мост, программируемый логический компонент или любые другие устройства, которым требуется доступ в систему 104 памяти.

На Фиг.2 представлена блок-схема системы памяти. Система 104 памяти содержит контроллер 202 памяти, который управляет доступом в память 204. На Фиг.2 показана память 204 как группа блоков памяти с четырьмя блоками 204a-204d, но может иметь любое количество блоков в зависимости от особенностей применения. Группа блоков памяти может пониматься как набор отдельных памятей, интегрированных в едином кристалле кремния. В альтернативных вариантах осуществления системы 104 памяти контроллер 202 памяти может быть сконфигурирован для управления доступом к множеству устройств памяти, причем каждое устройство памяти является одноблоковым или многоблоковым устройством. Специалистам в данной области техники будет понятно, что разнообразные концепции, приведенные в настоящем описании, могут быть применены в системах памяти с различной конфигурацией.

Контроллер 202 памяти может быть устройством, которое управляет работой одного или нескольких устройств памяти, включающих в себя специальную микросхему контроллера памяти, процессор, который непосредственно управляет памятью, схему контроллера в устройстве памяти или любая другая подходящая конфигурация. Каждое устройство памяти может быть любого вида устройства временного хранения, таким как синхронное динамическое ОЗУ (SDRAM), динамическое ОЗУ (DRAM) или оперативное запоминающее устройство (RAM), или устройства длительного хранения, таким как постоянное запоминающее устройство (ROM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM) и т.д. В данном примере устройство памяти будет описано в контексте SDRAM, однако различные концепции, приведенные в настоящем описании, могут быть распространены на другие устройства памяти.

Пример операции записи в устройство памяти будет описан в соответствии с временной диаграммой, представленной на Фиг.3. Устройство памяти активируется по утверждению сигнала выбора 301 микросхемы (CS). Перед выполнением операции считывания или записи в блок внутри устройства памяти должна быть открыта строка этого блока. Это выполняется отправкой обоих адресов - адреса 308 блока и адреса 310 строки - в устройство памяти и утверждением CS 301 и RAS 302 путем перевода его в состояние логического «0» в момент 320. В этом примере все сигналы управления, кроме маски данных, «утверждаются» состоянием логического «0», однако на практике могут переключаться полярности.

Когда строка устройства памяти открыта, контроллер памяти может считывать или записывать в эту строку. В момент времени 322 контроллер памяти инициирует операции записи отправкой в устройство памяти адреса 308 блока и адреса 312 начала столбца и утверждением CS 301, CAS 304 и активирования 306 записи (WE). После предварительно заданной задержки следующей за утверждением WE 306, контроллер памяти начинает передачу данных, подлежащих записи, в устройство памяти по шине 316 данных (см. момент 324). Устройство памяти проигнорирует информацию в шине 316 и не произведет операцию записи, если утверждена маска данных. В данном примере маска данных утверждена (например, переведена в состояние логической «I») во время первого информационного интервала 326. В результате эта информация не является записанной в устройство памяти. Во время второго 328 и третьего 330 информационных интервалов маска данных снимается, и данные, передаваемые по шине 316, записываются в устройство памяти. Как было отмечено ранее, полярность утвержденной маски данных выбрана в этом примере для удобства объяснения, но на практике может быть любой полярности. Перед моментом 332 и вслед за операцией записи шина 316 данных и маска 318 данных не загружаются, например, за счет перевода в состояние высокого импеданса или в режим троичного состояния.

На Фиг.4 приведена блок-схема, иллюстрирующая пример устройства 400 памяти. Устройство 400 памяти содержит управляющую логику 401, которая принимает CS, RAS, CAS, WE команды от контроллера памяти (не показано) и генерирует соответствующие переключения для выполнения операций считывания и записи.

Устройство 400 памяти содержит также регистр 402 адреса, который принимает адрес от контроллера памяти. Регистр 402 адреса разделяет адреса, отправляя адреса блока в логику 403 управления блока, адрес строки на мультиплексор 404 и адрес начала столбца на счетчик 405 адреса столбца. Логика 403 управления блока разделяет декодеры от декодеров 408, 410 адресов строк и столбцов, размещенных в адресе блока. Мультиплексор 404 мультиплексирует адрес строки из адресного регистра 402 с выходным сигналом из счетчика 406 регенерации на выбранный декодер в декодере 408 адреса строки. Счетчик 406 регенерации используется для генерации последовательности адресов во время заданного цикла. Выбранный декодер в декодере 408 адресов строк декодирует адрес строки, когда он принимает пусковой сигнал от управляющей логики 401. Декодированный адрес строки предоставляется в матрицу 414 памяти для открытия строки в блоке памяти, управляемой выбранным декодером в декодере 408 адреса строки.

Когда строка открыта в блоке памяти, выдается адрес начала столбца из счетчика 405 адреса столбца, когда он принимает пусковой сигнал от управляющей логики 401. Последующие пусковые сигналы от управляющей логики 401 используются для приращения счетчика 405 адреса столбца и для создания последовательности адресов столбцов, достаточной для доступа в блок памяти в строке блока памяти и для завершения операции считывания или записи. Адрес столбца отправляется на декодер в декодере 410 адреса столбца, выбранном управляющей логикой 405. Выбранный декодер декодирует адрес столбца и предоставляет декодированный адрес в устройство ввода/вывода и логический блок 416 маскирования информации. Сигнал из управляющей логики 401 отправляется также в устройство ввода/вывода и логический блок 416 маски данных, чтобы указать, что обмен с шиной производится в режиме считывания или записи. В случае операции считывания, контент матрицы 414 памяти определяется блоком, строкой, и адрес столбца считывается в устройство ввода/вывода и логику 416 маски данных, перед тем как будет передано в контроллер памяти с помощью драйвера 423 шины данных через драйвер 418 шины. В случае операции записи обмен данных с шиной 418 данных происходит через устройство ввода/вывода и логику 416 маски данных с помощью приемника 422 шины. Маска 430 данных передается на устройство ввода/вывода и логику 416 маски данных с помощью приемника 428 маски данных. Если маска данных снята устройство ввода/вывода и логика 416 маски данных записывает данные в заданный адрес в матрице 414 памяти. Если, наоборот, маска данных утверждена, данные не считываются и операция записи не выполняется.

Как было объяснено выше, маска данных имеет три состояния, кроме режима, когда контроллер памяти записывает в устройство 400 памяти. В течение этого времени маска данных может быть использована для предоставления данных или сообщения, какого-либо типа, на контроллер памяти. В одной конфигурации устройства 400 памяти маска данных может быть использована для индикации контроллеру памяти, что произошло изменение статуса устройства 400 памяти. Эта концепция может быть использована для устранения необходимости опрашивать статус устройства 400 памяти и обеспечить режим работы контроллера как сигнализатора события. В качестве примера, но не как ограничение, устройство 400 памяти может использовать маску данных для индикации изменения температуры. Альтернативно, или в дополнение к указанному, маска данных может использоваться для индикации ошибки синхронизации, такой как цикловой. Маска данных может также использоваться для индикации ошибки в ЕСС (корректирующего ошибки кода). Специалисты в данной области техники легко могут определить информацию или типы сообщений, которые лучше всего подходят к конкретному случаю применения.

Машина 426 состояний или другое устройство используется для мониторинга изменений в статусе устройства 400 памяти. Когда обнаруживается изменение, сигнал или прерывание выводится из машины 426 состояний и предоставляется на вход драйвера 424 маски данных. Машина 426 состояний также предоставляет сигнал 470 активирования в драйвер 424 маски данных. Сигнал 470 активирования деактивируется из драйвера 424 маски данных, когда операция записи выполняется. Деактивированием сигнала активирования, драйвер 424 маски данных переключается в троичное состояние, которое позволяет контроллеру памяти использовать маску данных во время операции записи. В одном варианте машина 426 состояний содержит внутренний таймер (не показан), чьи выходные данные управляют сигналом активирования. Внутренний таймер (не показан) переключается или активизируется, когда WE утверждается, и остается активированным в течение периода времени, достаточного для завершения операции записи. Сигнал активирования снимается из драйвера 424 маски данных, пока внутренний таймер (не показан) активизирован.

На Фиг.5 приведена концептуальная блок-схема другого примера системы памяти. В этом примере контроллер 502 памяти показан в соединении с двухранковой памятью 504 через 32-разрядную информационную шину 506. Первый ранк 508 включает в себя два 16-разрядных устройства 508А-508В памяти, соединенных вместе для поддержания связи с 32-разрядной шиной. В качестве примера, устройство 508А памяти может быть использовано для разрядов низшего порядка, устройство 508В может быть использовано для разрядов высшего порядка при взаимодействии с шиной. Второй ранк 510 также включает в себя два 16-разрядных устройства 510А-510В памяти, соединенных друг с другом подобным образом. Каждое устройство 508А-508В, 510А-510В может быть одноблоковым или многоблоковым устройством.

Схема сигнализации и адресации между контроллером 502 памяти и памятью 504 подобна той, которая была описана касательно Фиг.3 с общим сигналом CS для каждого устройства памяти в ранке. Этот общий сигнал CS может рассматриваться как сигнал выбора ранка (RS) потому, что он выбирает все устройства памяти в ранке. В этом примере, контроллер 502 памяти посылает адрес по шине 506 данных на устройства памяти в выбранный ранк, утверждает RAS для открытия строки в блоке устройства памяти и утверждает CAS для считывания или записи в эту строку. В случае операции записи, контроллер памяти также утверждает WE.

На Фиг.6 приведена блок-схема, иллюстрирующая пример сигнализации маски данных в системе памяти, представленной на Фиг.5. Маска данных может быть выработана для каждого байтового тракта шины 506 данных (см. Фиг.5). Так как шина имеет четыре байтовых тракта (т.е. 32 разрядных), имеется четыре маски 601-604 данных. Устройства 508А, 510А, соединенные с двумя байтовыми трактами, содержащими разряды низшего порядка, принимают две маски 601, 602 данных. Устройства памяти 508В, 510В, соединенные с байтовыми трактами, содержащими разряды высшего порядка, принимают маски 603, 604 данных. Четыре маски 601-604 данных используются для облегчения передачи информации между контроллером 502 памяти и памятью, когда используется только часть шины данных. В качестве примера, при взаимодействии с шиной может требоваться только запись одного байта в память 504. Контроллер 502 может выполнять эту передачу отправкой данных по одному байтовому тракту шины данных и утверждением масок данных для других байтовых трактов. Маски данных используются ранком памяти с утвержденным сигналом RS для определения, по какому байтовому тракту передаются данные.

Маски 601-604 данных могут также использоваться памятью 504 для индикации изменения статуса, как было обсуждено ранее в отношении Фиг.4. Различные маски данных могут быть назначены для каждого устройства 508А-508В, 510А-510В памяти для отправки сигнала или прерывания на контроллер памяти, когда операция записи не выполняется. В качестве примера, первая маска 601 данных может быть присвоена устройству 508А, обрабатывающему разряды низшего порядка в первом ранке 508, вторая маска 602 данных может быть присвоена устройству 510А, обрабатывающему разряды низшего порядка во втором ранке 510, третья маска 603 данных может быть присвоена устройству 508В памяти, обрабатывающему разряды высшего порядка в первом ранке 508, и четвертая маска 601 данных может быть присвоена устройству 510В памяти, обрабатывающему разряды высшего порядка во втором ранке 510. Контроллер памяти может определить, какое из четырех устройств 508А-508В, 510А-510В памяти посылает данные или сообщение, основываясь на конкретной маске данных, несущей сигнал или прерывание. Все четыре маски 601-604 данных не могут быть загружены устройствами 508А-508В, 510А-510В памяти во время операции записи в какое-либо из устройств памяти. Могут применяться различные способы для предотвращения загрузки масок 601-604 устройствами 508А-508В, 510А-510В памяти во время операции записи, включающие в себя, такие как троичное состояние линии, ограничение линий, переключающие технологии и др.

На Фиг.7 приведена функциональная блок-схема устройства памяти, представленного на Фиг.6. В этом примере управляющая логика 701 принимает RAS, CAS, WE от контроллера памяти (не показано). С утвержденным сигналом RS управляющая логика 701 вырабатывает соответствующие переключения для выполнения операций считывания и записи. Управляющая логика 701 не вырабатывает соответствующие переключения, если сигнал RS не утвержден.

Сигналы RAS, CAS, WE предоставляются на машину 726 состояний независимо от состояния сигнала RS. Как было объяснено выше в отношении Фиг.4, WE может быть использован для переключения внутреннего таймера (не показан), который удаляет сигнал активирования из драйвера 728 маски данных, пока работает внутренний таймер. Внутренний таймер включается на период времени, которого достаточно для завершения операции записи в устройство памяти любого ранка в системе памяти. Во время, когда внутренний таймер не активирован, драйвер 728 маски данных может быть использован для отправки прерывания или сигнала в контроллер памяти для передачи сообщения об изменении статуса.

В одном варианте осуществления изобретения маска данных, используемая устройством 700 памяти для индикации изменения статуса, программируется. В этом варианте драйвер маски данных, либо драйвер 728 или 729 маски данных, предоставляется для каждого изменения статуса. Как показано на Фиг.7, изготовитель оборудования, поставщик и/или потребитель может выбрать один или два драйвера маски данных для выполнения прерывания через программный вход машины 726 состояний. В ответ на входные данные программы, машина 726 состояний может выбрать драйвер 728 маски данных, активируя сигнал 770 активирования для возбуждения маски 730 данных. В частности, машина 726 состояний активирует драйвер 728 маски данных на время, пока включен внутренний таймер (не показан). Деактивируя сигнал 775 активирования, другой драйвер 729 деактивируется машиной 726 состояний, переводя драйвер 729 маски данных в троичное состояние. Программное изменение может быть сделано для выбора другого драйвера маски данных путем соединения внутреннего таймера с другим драйвером 729 маски данных и деактивирования первоначально выбранного драйвера 728 маски данных.

Различные иллюстративные логические блоки, модули, схемы, элементы и/или компоненты, описанные в материалах, относящиеся к вариантам осуществления настоящего изобретения, могут быть применены или выполнены с универсальным процессором, устройством цифровой обработки сигналов (DSP), специализированной интегральной микросхемой (ASIC), программируемой пользователем логической матрицей (FPGA) или другими программируемыми логическими компонентами, дискретными ключевыми или транзисторными логическими устройствами, дискретными аппаратными компонентами или любой их комбинацией, сконструированной для выполнения приведенных в настоящих материалах функций. Универсальный процессор может быть микропроцессором, но и в другом варианте, процессор может быть любым стандартным процессором, контроллером, микроконтроллером или машиной состояний. В качестве процессора может быть также применена комбинация вычислительных компонентов, например комбинация устройств цифровой обработки информации DSP и микропроцессор, множество микропроцессоров, один или несколько микропроцессоров, объединенных в сети DSP или любые другие такие конфигурации.

Способы и алгоритмы, описанные для раскрытых здесь вариантов осуществления изобретения, могут быть выполнены непосредственно на аппаратных средствах программными модулями, реализованными процессором или комбинацией обоих вариантов. Программный модуль может размещаться в оперативной памяти, флэш-памяти, постоянном запоминающем устройстве, программируемом стираемом ПЗУ, электрически стираемом программируемом ПЗУ, в регистрах, на жестких дисках, на съемных дисках, компакт дисках или любых других видах машиночитаемых носителей, известных из уровня техники. Машиночитаемые носители могут быть связаны с процессором так, чтобы процессор мог считывать с них и записывать на них информацию. Возможен другой вариант, когда машиночитаемые носители могут быть интегрированы в процессор.

Приведенное выше описание раскрытых вариантов осуществления изобретения предназначено для того, чтобы специалисты могли создать или использовать настоящее изобретение. Различные модификации этих вариантов осуществления будут легко понятны для специалистов в данной области техники, характерные принципы, определенные в настоящих материалах, могут быть легко применены к другим вариантам осуществления без изменения сущности и объема настоящего изобретения. Таким образом, настоящее изобретение не считается ограниченным примерами осуществления, приведенными здесь, но должно быть в соответствии с полным объемом притязаний, содержащихся в формуле изобретения, где ссылка на элемент в единственном числе не подразумевает значение «один и только один», если специально это не оговаривается, но даже означает «один или более». Все структурные и функциональные эквиваленты элементов в различных вариантах осуществления, описанных во всех настоящих материалах, которые известны или станут известны впоследствии для тех, кто имеет обычную квалификацию в данной области техники, являются включенными в настоящие материалы по ссылкам, и полагается, что входят в объем заявки. Более того, никакие материалы, раскрытые здесь не считаются открытыми для общественности, невзирая на то, что такое раскрытие подробно изложено в формуле изобретения. Ни один пункт формулы не должен рассматриваться по положениям раздела 35 Кодекса законов США, §112, 6 параграф, если этот пункт формулы не был определенно изложен с использованием фразы «средство для», или в случае пункта формулы на способ, пункт формулы излагается с использованием оборота «этап для».

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2682387C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2642960C2 |

| КОНТРОЛЛЕР ПАМЯТИ, КОТОРЫЙ ВЫПОЛНЯЕТ КОМАНДЫ СЧИТЫВАНИЯ И ЗАПИСИ НЕ В ПОРЯДКЕ ПРОСТОЙ ОЧЕРЕДИ | 1996 |

|

RU2157562C2 |

| СПОСОБ И СИСТЕМА ВНЕШНЕГО ХРАНЕНИЯ ДАННЫХ | 2005 |

|

RU2383952C2 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| СПОСОБ ЗАПИСИ ДАННЫХ И СИСТЕМА ПАМЯТИ | 2014 |

|

RU2621611C1 |

| УСТРОЙСТВО ПАМЯТИ И СИСТЕМА ПАМЯТИ | 2015 |

|

RU2682843C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| СИСТЕМА ВЗАИМОРАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2000 |

|

RU2188451C2 |

Изобретение относится к системам памяти, более конкретно к сигнализации между контроллером памяти и памятью в системе памяти. Техническом результатом является возможность передачи сигналов о прерывании общей шины в многоранковой подсистеме памяти. Система памяти включает в себя первое и второе устройства памяти и контроллер памяти, сконфигурированный для селективного активирования одного из устройств памяти, причем контроллер памяти имеет первую линию, связанную с первым и вторым устройствами памяти, и вторую линию, связанную с первым и вторым устройствами памяти. Первое устройство памяти сконфигурировано для предоставления сообщения на контроллер памяти по первой линии и второе устройство памяти сконфигурировано для предоставления сообщения на контроллер памяти по второй линии. Первое устройство памяти дополнительно сконфигурировано так, чтобы не загружать первую линию, и второе устройство памяти дополнительно сконфигурировано так, чтобы не загружать вторую линию, когда контроллер записывает на активированное устройство памяти. 6 н. и 18 з.п. ф-лы, 7 ил.

1. Система памяти, содержащая:

первое и второе устройства памяти; и

контроллер памяти, сконфигурированный для селективного активирования одного из устройств памяти, причем контроллер памяти имеет первую линию, связанную с первым и вторым устройствами памяти, и вторую линию, связанную с первым и вторым устройствами памяти;

при этом первое устройство памяти сконфигурировано для предоставления сообщения на контроллер памяти по первой линии, и второе устройство памяти сконфигурировано для предоставления сообщения на контроллер памяти по второй линии, и при этом

первое устройство памяти включает в себя драйвер, сконфигурированный для предоставления своего сообщения на контроллер памяти по первой линии, и второе устройство памяти включает в себя драйвер, сконфигурированный для предоставления своего сообщения на контроллер памяти по второй линии, и в которой каждое из устройств памяти дополнительно сконфигурировано для перевода своего драйвера в троичное состояние, чтобы не загружать первую и вторую линии, когда контроллер памяти записывает в активированное устройство памяти.

2. Устройство памяти по п.1, в котором первое устройство памяти дополнительно содержит средство для программирования своего драйвера для предоставления сообщения первого устройства памяти на контроллер памяти, и второе устройство памяти содержит средство для программирования своего драйвера для предоставления сообщения второго устройства памяти на контроллер памяти.

3. Система памяти по п.1, в которой контроллер памяти дополнительно сконфигурирован для передачи сигнала об операции записи на активированное устройство памяти, каждое из устройств памяти сконфигурировано для переключения своего драйвера в троичное состояние в ответ на упомянутый сигнал.

4. Система памяти по п.1, дополнительно содержащая первый и второй ранки, причем первый ранк содержит первое множество устройств памяти, включающее в себя первое устройство памяти, и второй ранк содержит второе множество устройств памяти, включающее в себя второе устройство памяти, и при этом контроллер памяти дополнительно сконфигурирован для активирования первого устройства памяти активированием первого ранка и для активирования второго устройства памяти активированием второго ранка.

5. Система памяти по п.1, в которой контроллер памяти дополнительно сконфигурирован для предоставления одной маски данных по первой и второй линиям, когда контроллер памяти записывает в активированное устройство памяти.

6. Система памяти по п.1, в которой сообщение, предоставленное на контроллер памяти первым устройством памяти, указывает изменение в статусе первого устройства памяти, и сообщение, предоставленное на контроллер памяти вторым устройством памяти, указывает изменение в статусе второго устройства памяти.

7. Система памяти, содержащая:

первый и второй ранки памяти, каждый из ранков памяти имеет устройство памяти; и

контроллер памяти, сконфигурированный для селективного активирования одного из ранков памяти и записи данных в активированный ранк памяти, причем контроллер памяти имеет первую и вторую линии, каждая из которых связана с первым и вторым ранками памяти, первая и вторая линии сконфигурированы для предоставления маски данных, относящейся к данным;

причем устройство памяти в первом ранке памяти сконфигурировано для предоставления сообщения на контроллер памяти по первой линии, и устройство памяти во втором ранке памяти сконфигурировано для предоставления сообщения на контроллер памяти по второй линии.

8. Система памяти по п.7, в которой устройство памяти в первом ранке памяти сконфигурировано так, чтобы не загружать первую линию, и второе устройство памяти сконфигурировано так, чтобы не загружать вторую линию, когда контроллер памяти записывает информацию в активированный ранк памяти.

9. Система памяти по п.8, в которой устройство памяти в первом ранке памяти включает в себя драйвер, сконфигурированный для предоставления своего сообщения на контроллер памяти по первой линии, и устройство памяти во втором ранке памяти включает в себя драйвер, сконфигурированный для предоставления сообщения на контроллер памяти по второй линии, и в которой каждое устройство памяти дополнительно сконфигурировано для перевода своего драйвера в троичное состояние с тем, чтобы не загружать первую и вторую линии, когда контроллер памяти производит запись в активированный ранк памяти.

10. Система памяти по п.9, в которой контроллер памяти дополнительно сконфигурирован для передачи сигнала об операции записи на активированный ранк памяти, причем каждое устройство памяти сконфигурировано для перевода своего драйвера в троичное состояние в ответ на упомянутый сигнал.

11. Система памяти по п.7, в которой каждое устройство памяти включает в себя первый драйвер, связанный с первой линией, и второй драйвер, связанный со второй линией, и в которой устройство памяти в первом ранке памяти дополнительно сконфигурировано для использования своего первого драйвера для предоставления своего сообщения на контроллер памяти, и устройство памяти во втором ранке памяти дополнительно сконфигурировано для использования своего второго драйвера для предоставления своего сообщения на контроллер памяти.

12. Устройство памяти по п.11, в котором устройство памяти в первом ранке памяти дополнительно содержит средство для программирования своего первого драйвера для предоставления своего сообщения на контроллер памяти, и устройство памяти во втором ранке памяти содержит средство для программирования своего второго драйвера для предоставления своего сообщения на контроллер памяти.

13. Устройство памяти по п.7, в котором сообщение, предоставленное на контроллер памяти каждым из устройств памяти, указывает на изменение статуса такого устройства памяти.

14. Способ передачи данных между контроллером памяти и памятью, имеющей первое и второе устройства памяти, причем контроллер памяти, имеющий линию, связанную с первым и вторым устройствами памяти, содержит этапы, на которых:

предоставляют сообщение от первого устройства памяти на контроллер памяти по первой линии;

активируют второе устройство памяти с тем, чтобы контроллер памяти мог записывать во второе устройство памяти;

устанавливают первое устройство памяти в состояние, при котором устройство не загружает первую линию, когда контроллер памяти записывает во второе устройство памяти.

15. Способ по п.14, в котором контроллер памяти дополнительно содержит вторую линию, связанную с первым и вторым устройствами памяти, при этом способ дополнительно содержит этап, на котором предоставляют сообщение от второго устройства памяти на контроллер памяти по второй линии.

16. Способ по п.14, дополнительно содержащий этап, на котором предоставляют маску данных от контроллера памяти на второе устройство памяти, когда контроллер памяти записывает во второе устройство памяти.

17. Способ по п.14, дополнительно содержащий этап, на котором передают сигнал об операции записи на второе устройство памяти, и причем первое устройство памяти использует упомянутый сигнал для установки его в состояние, которое не загружает линию, когда контроллер памяти записывает во второе устройство памяти.

18. Способ по п.14, в котором сообщение, предоставленное на контроллер памяти первым устройством памяти, указывает изменение статуса первого устройства памяти.

19. Способ передачи данных между контроллером памяти и памятью, имеющей первый и второй ранки памяти, причем каждый ранк памяти имеет устройство памяти, и при этом контроллер памяти включает в себя первую линию, связанную с устройством памяти в первом ранке, и вторую линию, связанную с устройством памяти во втором ранке, причем способ содержит этапы, на которых:

предоставляют сообщение от устройства памяти в первом ранке памяти на контроллер памяти по первой линии;

активируют второй ранк памяти для того, чтобы контроллер памяти мог записывать во второй ранк памяти;

предоставляют маску данных от контроллера памяти на второй ранк памяти по первой и второй линиям, когда контроллер памяти записывает во второе устройство памяти.

20. Способ по п.19, дополнительно содержащий этап, на котором устанавливают устройство памяти в первом ранке памяти в состояние, которое не загружает первую линию, когда контроллер памяти производит запись во второй ранк памяти.

21. Способ по п.20, дополнительно содержащий этап, на котором передают сигнал об операции записи во второй ранк памяти и используют упомянутый сигнал для установки устройства памяти в первом ранке памяти в состояние, которое не загружает первую линию, когда контроллер памяти записывает во второй ранк памяти.

22. Способ по п.19, в котором сообщение, предоставленное устройством памяти в первом ранке памяти на контроллер памяти, указывает на изменение статуса такого устройства памяти.

23. Система памяти, содержащая:

первое и второе устройства памяти; и

контроллер памяти, сконфигурированный для селективного активирования одного из устройств памяти, причем контроллер памяти имеет первую линию, связанную с первым и вторым устройствами памяти, и вторую линию, связанную с первым и вторым устройствами памяти;

причем первое устройство памяти дополнительно включает в себя средство для предоставления сообщения на контроллер памяти по первой линии, и второе устройство памяти включает в себя средство для предоставления сообщения на контроллер памяти по второй линии;

причем средство для предоставления сообщения на контроллер памяти по первой линии и средство для предоставления сообщения на контроллер памяти по второй линии каждое сконфигурированы так, чтобы не загружать соответствующую линию, когда контроллер памяти записывает данные в активированное устройство памяти.

24. Система памяти, содержащая:

первый и второй ранки памяти, каждый из ранков памяти имеет устройство памяти; и

контроллер памяти, сконфигурированный для селективного активирования одного из ранков памяти и записи данных на активированный ранк памяти, причем контроллер памяти имеет первую и вторую линии, каждая из которых связана с первым и вторым ранками памяти, при этом первая и вторая линии сконфигурированы для вывода маски данных, относящейся к данным;

причем устройство памяти в первом ранке данных включает в себя средство для предоставления сообщения на контроллер памяти по первой линии, и устройство памяти во втором ранке памяти включает в себя средство для предоставления сообщения на контроллер памяти по второй линии.

| US 5860080 А, 12.01.1999 | |||

| КОНТРОЛЛЕР ПАМЯТИ, КОТОРЫЙ ВЫПОЛНЯЕТ КОМАНДЫ СЧИТЫВАНИЯ И ЗАПИСИ НЕ В ПОРЯДКЕ ПРОСТОЙ ОЧЕРЕДИ | 1996 |

|

RU2157562C2 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2011-03-10—Публикация

2007-08-08—Подача