ПЕРЕКРЕСТНАЯ ССЫЛКА НА СВЯЗАННЫЕ ЗАЯВКИ

Настоящая заявка основана на и испрашивает приоритет предварительной заявки США № 62/131,113, поданной 10 марта 2015, все содержание которой включено в настоящий документ посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Настоящие варианты осуществления относятся к устройству памяти и системе памяти.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Устройство памяти, использующее магниторезистивный элемент, известно как устройство магнитной памяти, включенное в систему памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

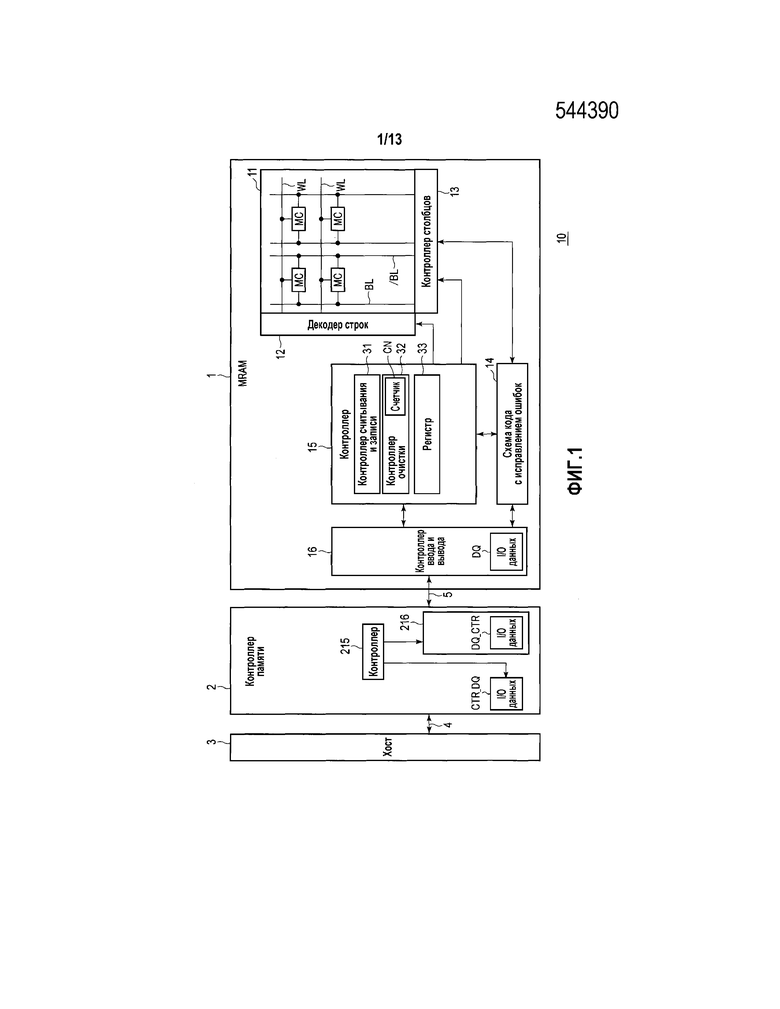

Фиг. 1 иллюстрирует пример функциональных блоков системы памяти в соответствии с первым вариантом осуществления;

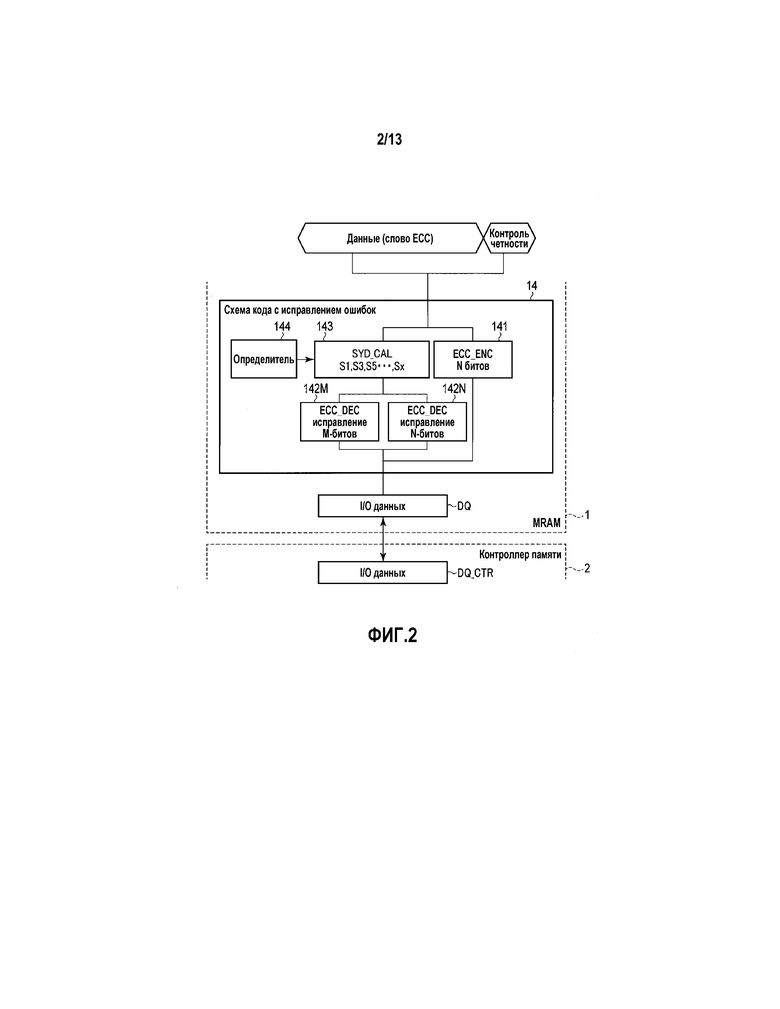

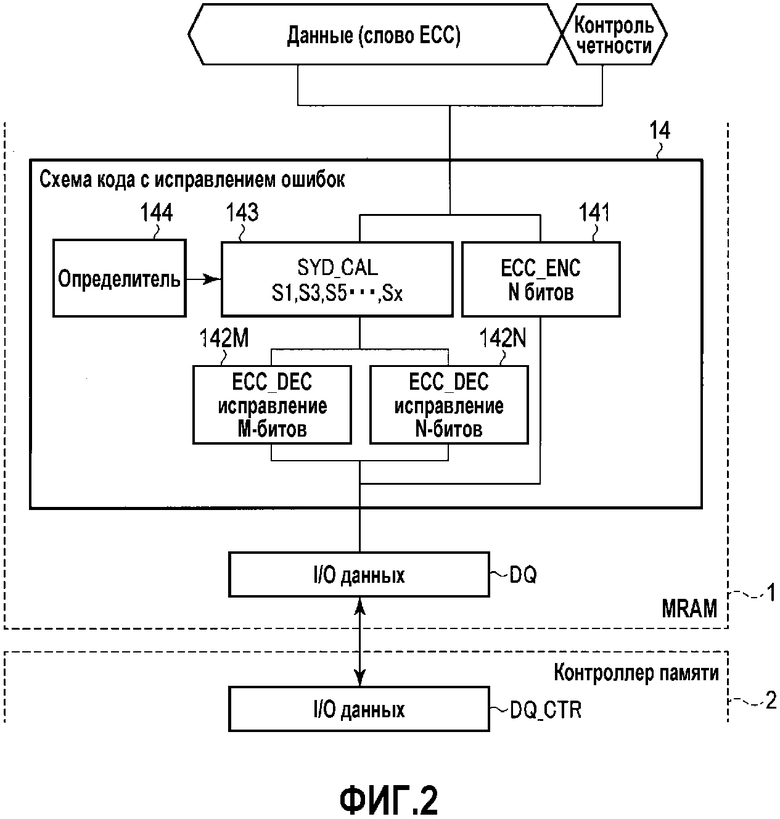

Фиг. 2 схематично иллюстрирует пример структуры схемы исправления ошибок, включенной в устройство магнитной памяти в соответствии с первым вариантом осуществления;

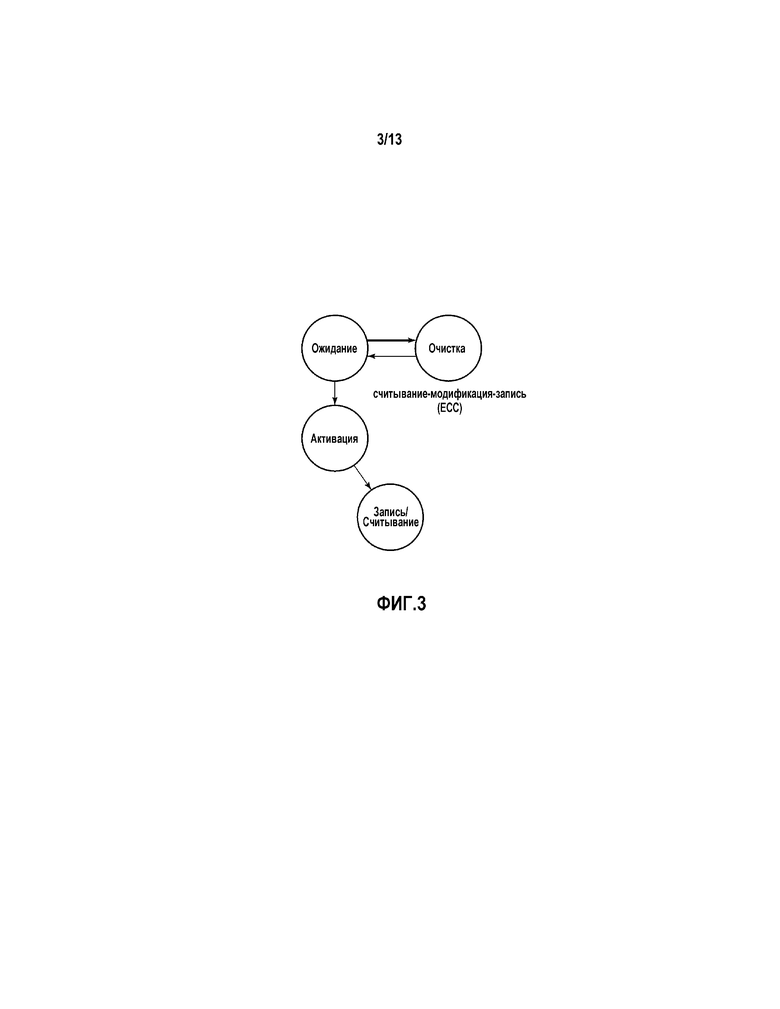

Фиг. 3 иллюстрирует, как состояние устройства магнитной памяти изменяется в соответствии с первым вариантом осуществления;

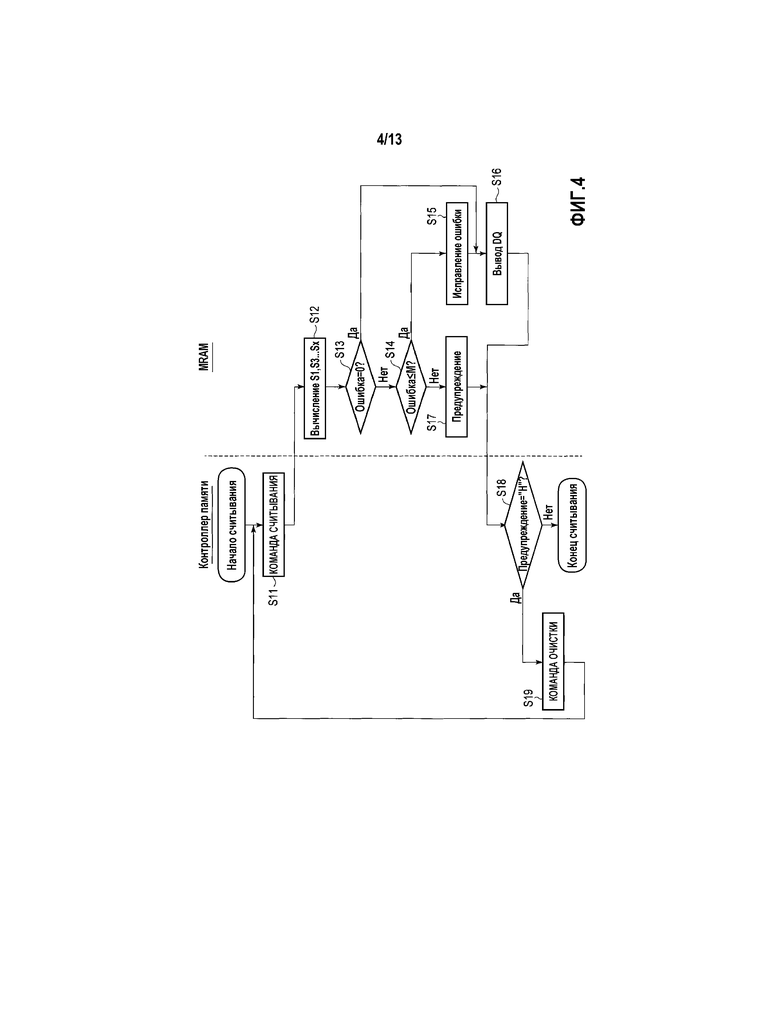

Фиг. 4 иллюстрирует поток операции считывания системы памяти в соответствии с первым вариантом осуществления;

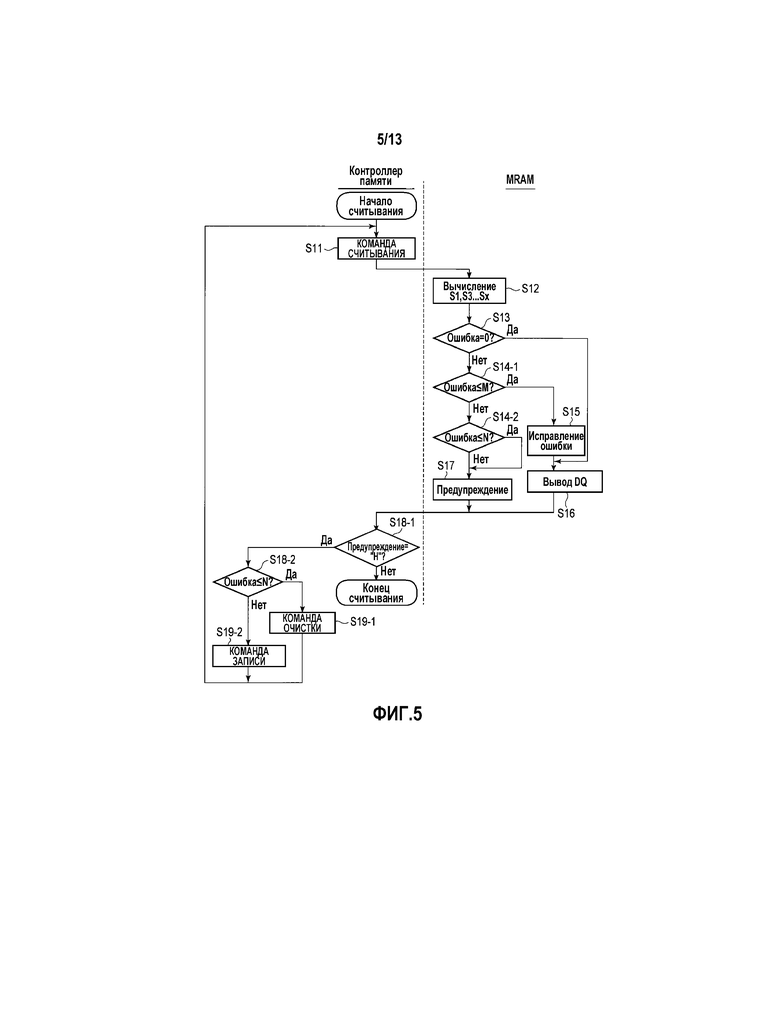

Фиг. 5 иллюстрирует поток другого примера операции считывания системы памяти в соответствии с первым вариантом осуществления;

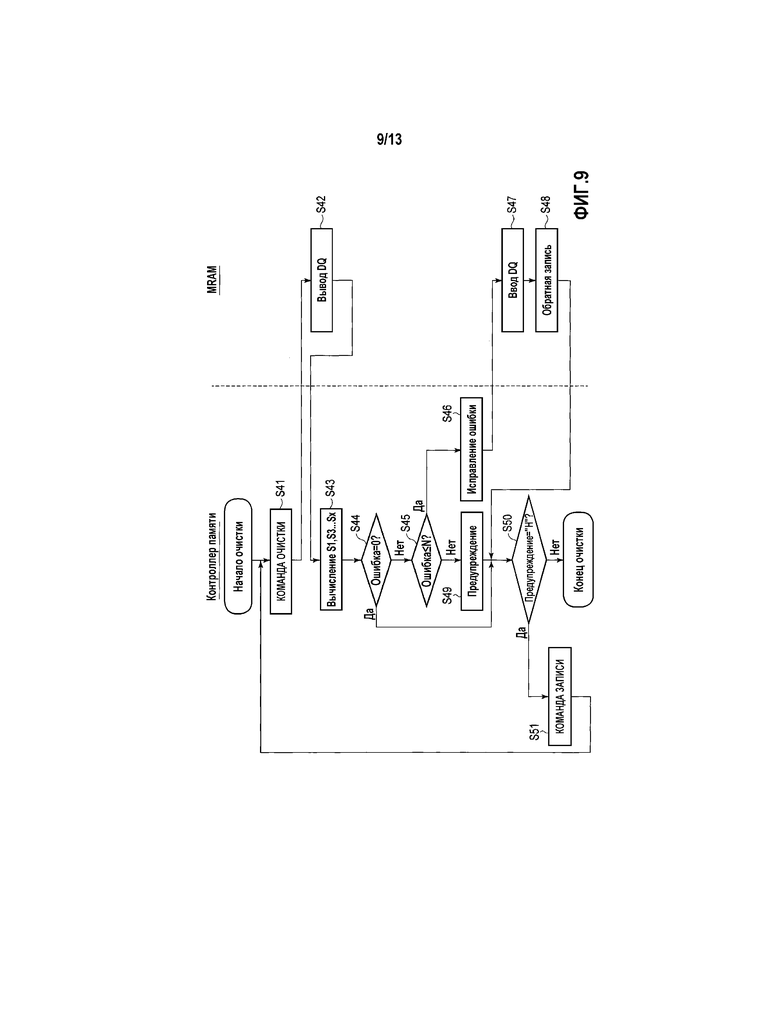

Фиг. 6 иллюстрирует поток операции очистки системы памяти в соответствии с первым вариантом осуществления;

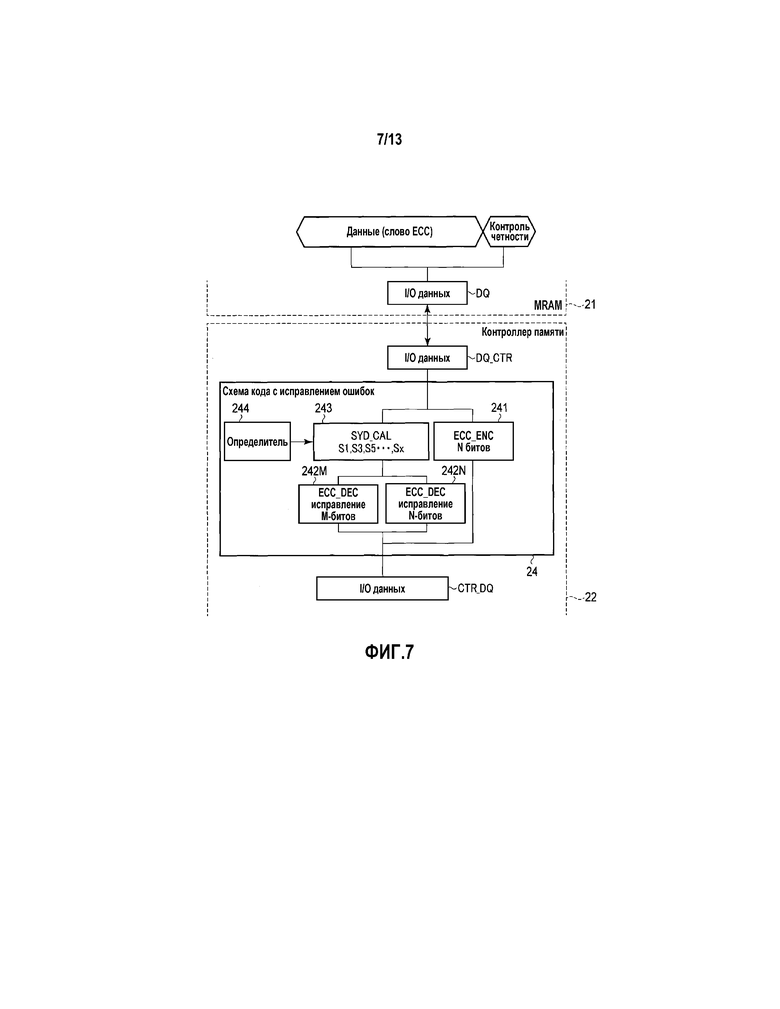

Фиг. 7 схематично иллюстрирует пример структуры схемы исправления ошибок, включенной в контроллер памяти согласно второму варианту осуществления;

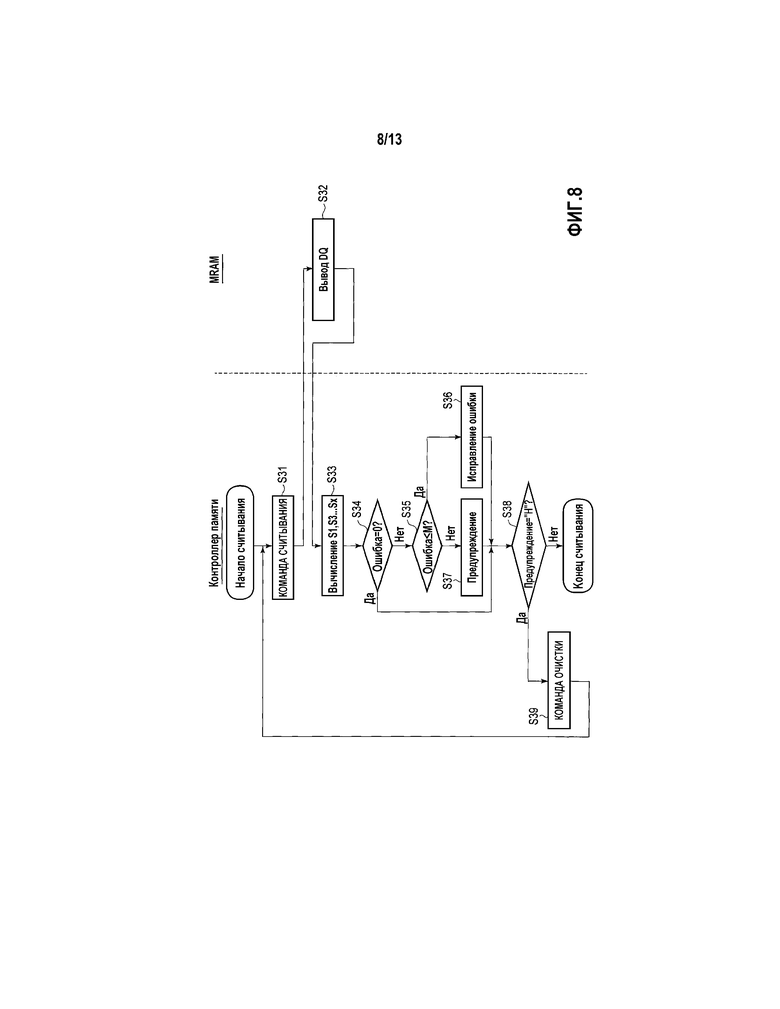

Фиг. 8 иллюстрирует поток операции считывания системы памяти согласно второму варианту осуществления;

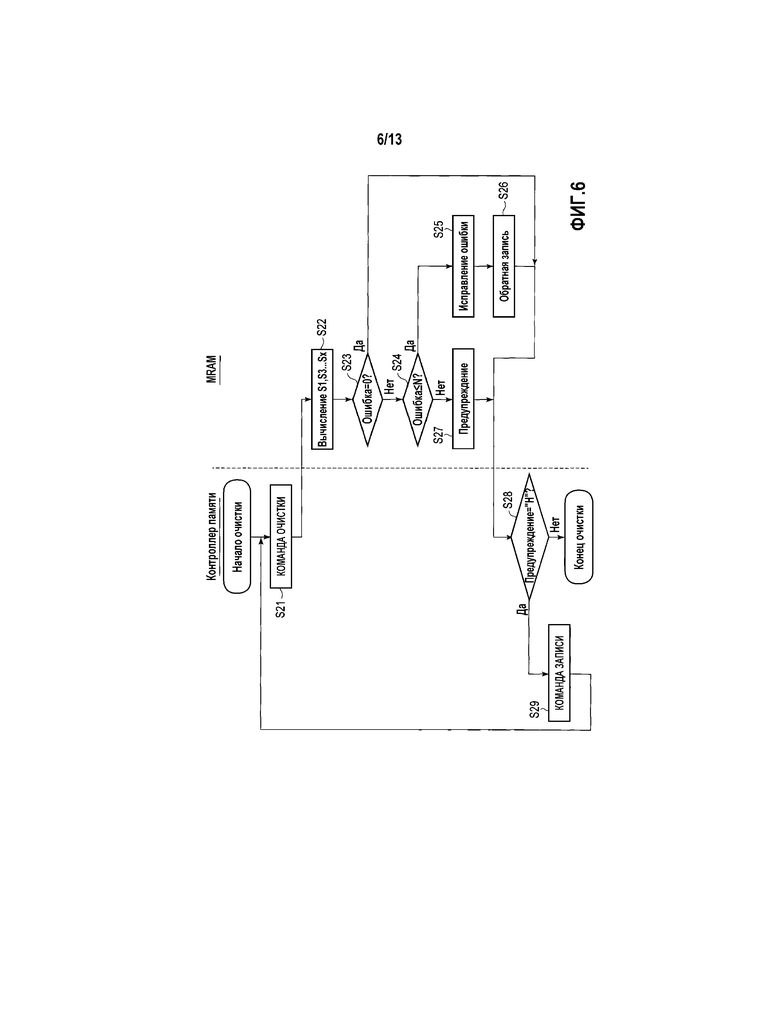

Фиг. 9 иллюстрирует поток операции очистки системы памяти согласно второму варианту осуществления;

Фиг. 10 иллюстрирует пример последовательности команд в системе памяти согласно второму варианту осуществления;

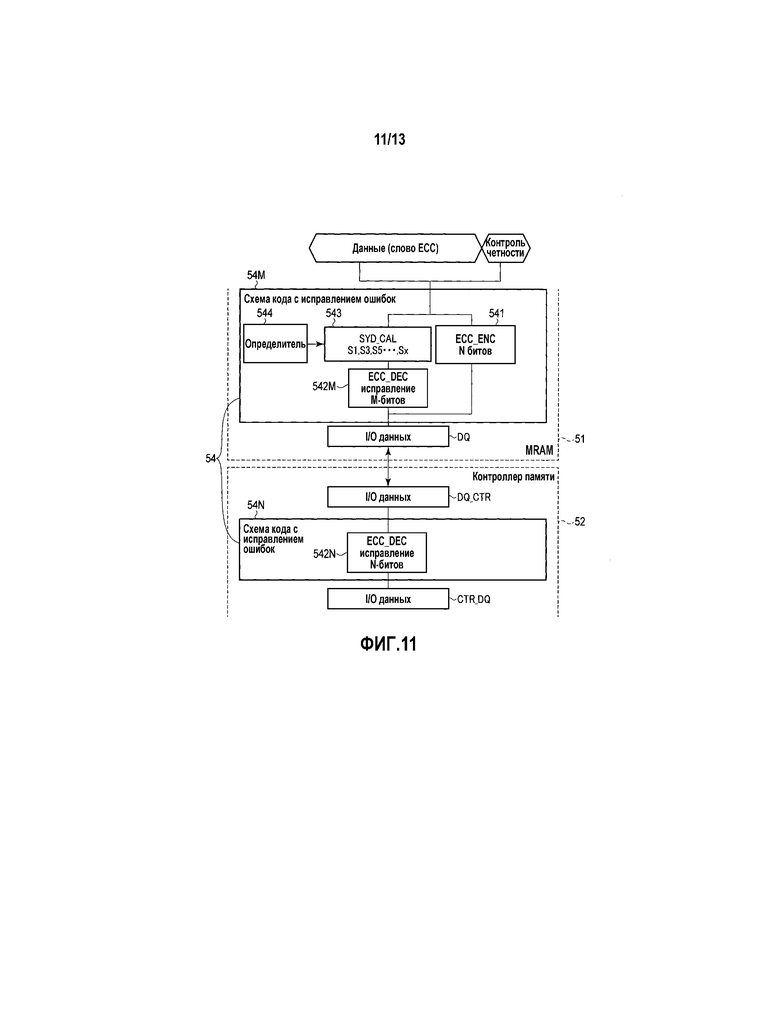

Фиг. 11 схематично иллюстрирует пример структуры схемы исправления ошибок, включенной в систему памяти согласно третьему варианту осуществления;

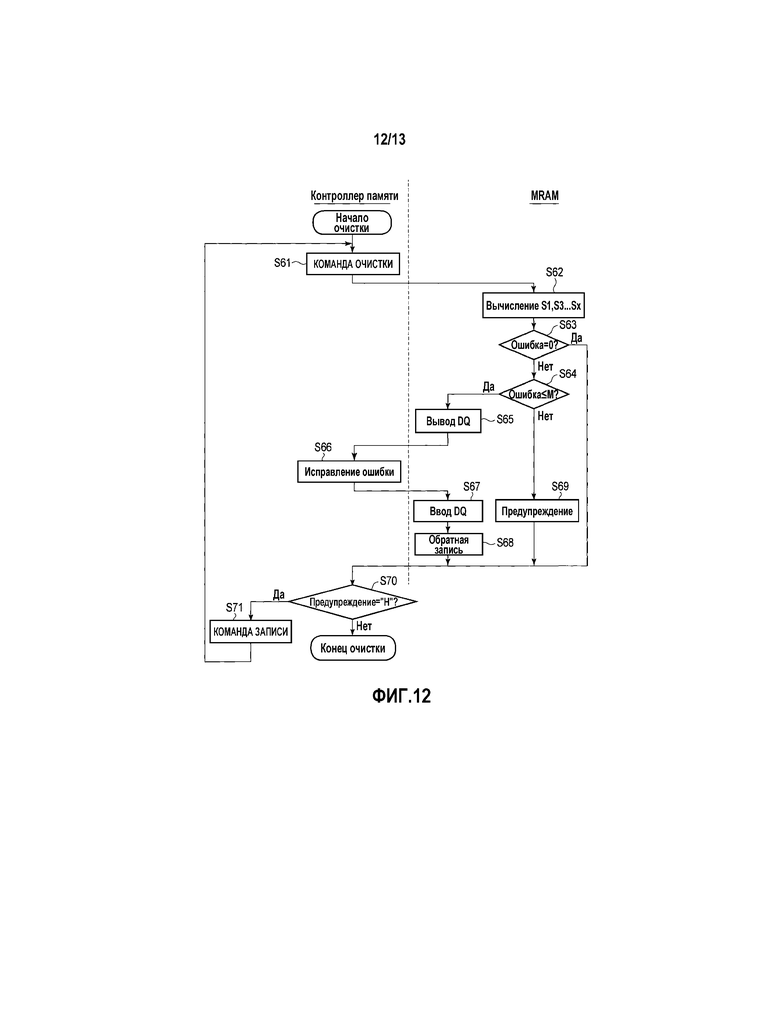

Фиг. 12 иллюстрирует поток операции очистки системы памяти согласно третьему варианту осуществления; и

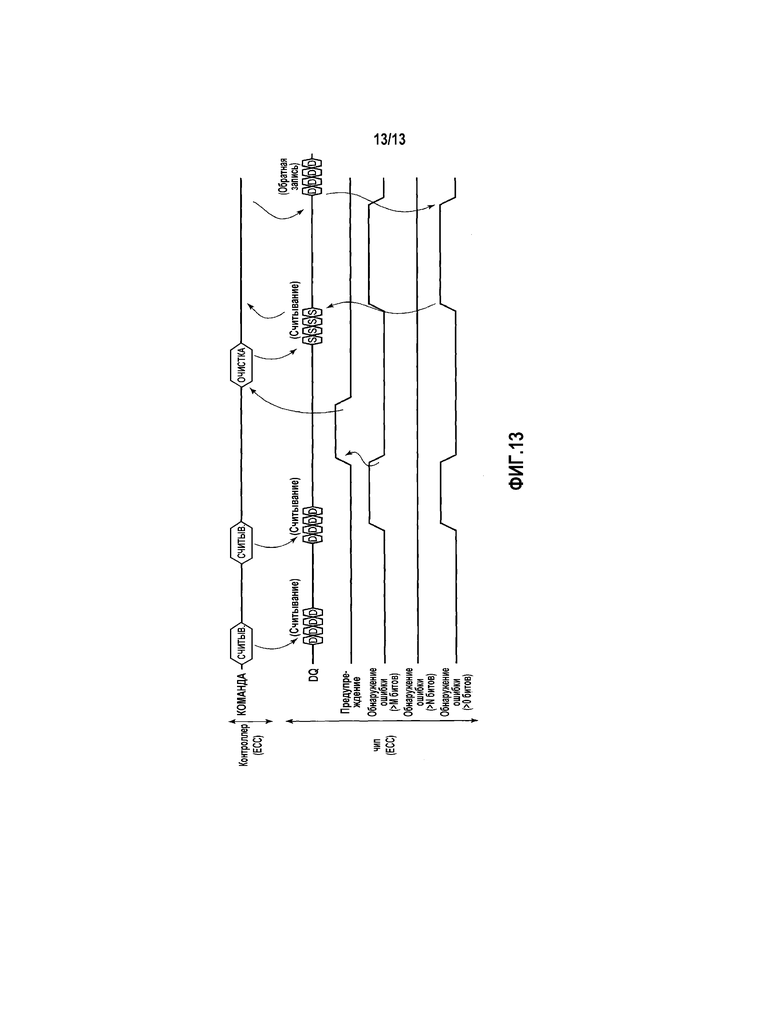

Фиг. 13 иллюстрирует пример последовательности команд в системе памяти согласно третьему варианту осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

Магнитное устройство памяти включает в себя множество ячеек памяти. Каждая ячейка памяти включает в себя, например, магниторезистивный элемент. Магниторезистивный элемент может хранить данные, принимая любое одно из двух состояний сопротивления.

Однако существует вероятность того, что магниторезистивный элемент изменит свое резистивное состояние, непреднамеренно инвертируя (перебрасывая из одного состояния в другое) сохраненные данные.

В соответствии с вариантами осуществления, описанными ниже, переброшенные из одного состояния в другое данные детектируются как ошибка, и данные записываются обратно в течение времени, в которое пользователь не осуществляет доступ к устройству магнитной памяти (то есть, в которое контроллер памяти не получает инструкции от пользователя через хост-устройство и не выполняет никакой проверки данных или никакой повторной записи, другими словами, в режиме ожидания устройства магнитной памяти). Эта операция упоминается как ʺочисткаʺ. В соответствии с нижеприведенными вариантами осуществления, очистка может быть выполнена для повышения надежности устройства памяти при поддержании высокой скорости работы устройства памяти. В частности, устройство памяти в одном варианте осуществления включает в себя элементы памяти, которые хранят данные, и контроль четности (контрольное число); первый декодер, который, когда выполняется очистка данных, пока внешний доступ не осуществляется к устройству памяти, использует синдром, генерируемый из данных и контроля четности для исправления ошибки максимум из N битов в блоке данных; и второй декодер, который, когда выполняется считывание данных, использует синдром для исправления ошибки максимум из М битов в блоке данных. М битов представляет число битов, меньшее, чем N битов.

Варианты осуществления описаны ниже со ссылкой на прилагаемые чертежи. На чертежах аналогичные компоненты обозначены одинаковыми ссылочными позициями. Каждый функциональный блок не обязательно должен различаться, как в следующих примерах. Например, некоторые функции могут быть реализованы функциональными блоками, отличными от тех, которые показаны ниже. Кроме того, проиллюстрированный функциональный блок может быть разделен на функциональные подблоки.

<Первый вариант осуществления>

Далее будет описано устройство памяти и система памяти в соответствии с настоящим вариантом осуществления. Устройство памяти в соответствии с настоящим вариантом воплощения представляет собой устройство с магнитной памятью, такое как магниторезистивная память с произвольным доступом (MRAM) с переносом спинового момента (STT). В MRAM в качестве элемента памяти используется элемент магнитного туннельного перехода (MTJ), который является магниторезистивным элементом.

(1) Пример структуры системы памяти

Сначала, со ссылкой на фиг. 1, будет описан пример структуры системы памяти в соответствии с настоящим вариантом осуществления. Фиг. 1 иллюстрирует примерную функциональную блок-схему системы памяти согласно настоящему варианту осуществления.

Как показано на фиг. 1, система 10 памяти включает в себя MRAM 1 STT-типа в качестве устройства магнитной памяти, контроллер 2 памяти и хост-устройство 3.

Хост-устройство 3 выдает инструкцию операций, таких как операции записи и считывания в MRAM 1, в контроллер 2 памяти. Хост-устройство 3 коммуникативно соединено с контроллером 2 памяти посредством соединительной линии 4. Соединительная линия 4 включает в себя, например, линию источника питания, шину данных, командную линию и так далее.

Контроллер 2 памяти передает различные команды в MRAM 1 в соответствии с инструкцией от хост-устройства 3 и инструктирует MRAM 1 о таких операциях, как операции записи и считывания данных. Контроллер 2 памяти передает адрес, в который будут записываться данные, и адрес, из которого данные будут считываться, в MRAM 1, и указывает область, затронутую операцией, такой как запись или считывание, среди областей памяти MRAM 1.

Кроме того, контроллер 2 памяти автономно передает команду очистки в MRAM 1 независимо от инструкции от хост-устройства 3 и выдает инструкцию операции очистки данных в MRAM 1. Операция очистки включает в себя проверку и повторную запись данных, хранящихся в ячейке МС памяти. Повторная запись данных может быть выполнена по мере необходимости.

Контроллер 2 памяти включает в себя контроллер 215, контроллер 216 ввода и вывода и блок CTR_DQ ввода и вывода данных и так далее. Контроллер 215 управляет всей работой контроллера 2 памяти, включая операции блока CTR_DQ ввода и вывода данных и контроллера 216 ввода и вывода. Блок CTR_DQ ввода и вывода данных соединен с хост-устройством 3 через соединительную линию 4 и управляет передачей и к хост-устройству 3 приемом данных от него. Контроллер 216 ввода и вывода включает в себя блок DQ_CTR ввода и вывода данных и коммуникативно соединен с MRAM 1 через соединительную линию 5. Соединительная линия 5 включает в себя, например, линию источника питания, шину данных, командную линию и т. д.

Вышеописанные функции контроллера 2 памяти могут быть реализованы процессором, таким как центральный процессор (CPU), и аппаратными средствами, такими как постоянная память (ROM) и память с произвольным доступом (RAM). Например, программа, хранимая в ROM, может считываться в RAM, и программа в RAM может исполняться посредством CPU для выполнения операции контроллера 2 памяти.

MRAM 1 включает в себя массив 11 ячеек памяти, декодер 12 строк, контроллер 13 столбцов, схему 14 кода с исправлением ошибок (ECC), контроллер 15 и контроллер 16 ввода и вывода. MRAM 1 выполняет такие операции, как запись, считывание и очистка, в соответствии с различными типами команд из контроллера 2 памяти.

Массив 11 ячеек памяти включает в себя множество ячеек МС памяти. Ячейки МС памяти соединены с множеством битовых линий BL и соответствующими битовыми линиями /BL, которые образуют пары с битовыми линиями BL, и множеством числовых линий WL.

Ячейка МС памяти включает в себя элемент MTJ и транзистор ячейки. Элемент MTJ может удерживать данные, используя магниторезистивный эффект. Транзистор ячейки соединен последовательно с элементом MTJ и управляет подачей и прекращением подачи тока на элемент MTJ.

Более конкретно, элемент MTJ включает в себя два магнитных слоя и немагнитный слой между двумя магнитными слоями. В первом магнитном слое, ориентация намагниченности или магнитная анизотропия неизменна. Во втором магнитном слое, ориентация намагниченности или магнитная анизотропия является переменной. Когда ток записи течет из первого магнитного слоя к второму магнитному слою, ориентации намагниченности двух магнитных слоев становятся параллельными друг с другом. Когда ориентации намагниченности двух магнитных слоев параллельны, элемент MTJ имеет минимальное значение сопротивления. Когда ток записи течет от второго магнитного слоя к первому магнитному слою, ориентации намагниченности двух магнитных слоев становятся антипараллельными друг с другом. Когда ориентации намагниченности двух магнитных слоев антипараллельны друг с другом, элемент MTJ демонстрирует максимальное значение сопротивления. Эти два состояния, представляющие два разных значения сопротивления, присваиваются двоичным данным.

Декодер 12 строк соединен с числовыми линиями WL. Декодер 12 строк выбирает одну из числовых линий WL в соответствии с адресом строки.

Контроллер 13 столбцов соединен с парами битовых линий BL, /BL. Контроллер 13 столбцов включает в себя декодер столбцов, селектор столбцов, усилитель считывания, драйвер записи и так далее. Контроллер 13 столбцов выбирает пару среди пар битовых линий BL, /BL в соответствии с адресом столбца и записывает данные в выбранную ячейку МС памяти или считывает данные из выбранной ячейки МС памяти.

Схема 14 исправления ошибок обрабатывает данные записи из контроллера 2 памяти и переносит данные записи в контроллер 13 столбцов. Схема 14 исправления ошибок исправляет ошибку данных, принятых от контроллера 13 столбцов. Схема 14 исправления ошибок будет подробно описана ниже.

Контроллер 16 ввода и вывода управляет передачей сигнала между MRAM 1 и контроллером 2 памяти. Контроллер 16 ввода и вывода подает команду и адрес из контроллера памяти 2 в контроллер 15. Контроллер 16 ввода и вывода также включает в себя блок DQ ввода и вывода данных. Блок DQ ввода и вывода данных управляется контроллером 16 ввода и вывода для приема данных записи из контроллера 2 памяти и передачи данных записи в схему 14 исправления ошибок. Кроме того, блок DQ ввода и вывода данных управляется посредством контроллера 16 ввода и вывода для передачи данных из схемы 14 исправления ошибок в качестве данных считывания в контроллер 2 памяти.

Контроллер 15 включает в себя контроллер 31 считывания и записи, контроллер 32 очистки, регистр 33, декодер команд, защелку, буфер, генератор напряжения и так далее. Контроллер 15 управляет компонентами MRAM 1 в соответствии с командой и адресом из контроллера 2 памяти.

Контроллер 31 считывания и записи управляет считыванием и записью данных из массива 11 и в массив 11 ячеек памяти. Контроллер 31 считывания и записи управляет декодером 12 строк и контроллером 13 столбцов в соответствии с командой и адресом. Соответственно, данные считываются из или записываются в одну или несколько ячеек МС памяти, указанных адресом.

Контроллер 32 очистки управляет операцией очистки. После приема команды очистки из контроллера 2 памяти, контроллер 32 очистки выполняет очистку данных, хранящихся в ячейках МС памяти. Объем ячеек памяти, для которых одновременно выполняется операция очистки, упоминается как блок выполнения очистки и определяется заранее. Блок выполнения очистки может быть определен на основе, например, числа ячеек МС памяти, которые считываются вместе. В качестве альтернативы, блок выполнения очистки может быть определен на основе местоположений ячеек MC памяти в массиве 11 ячеек памяти.

Контроллер 32 очистки может содержать, например, счетчик CN. Контроллер 32 очистки использует счетчик CN для управления адресами ячеек МС памяти для каждого блока выполнения очистки. Счетчик CN содержит адрес ячейки МС памяти, которая была последней целью операции очистки. Каждый раз, когда MRAM 1 принимает команду очистки и выполняется операция очистки, контроллер 32 очистки сообщает приращение адресу, которым обладает счетчик CN.

Регистр 33 содержит данные относительно операции очистки, такие как адрес ячейки МС памяти, которая содержит ошибочные данные.

(2) Пример структуры схемы исправления ошибок

Схема 14 исправления ошибок будет подробно описана ниже со ссылкой на фиг. 2. На фиг. 2 схематично показан пример структуры схемы исправления ошибок, включенной в устройство магнитной памяти в соответствии с настоящим вариантом осуществления.

Как показано на фиг. 2, схема 14 исправления ошибок включает в себя кодер 141 ECC, декодеры 142M, 142N ECC, генератор 143 синдрома и определитель 144.

Схема 14 исправления ошибок обрабатывает данные записи (строку битов 1 и 0) с помощью кодера 141 ECC и передает обработанные данные в контроллер 13 столбцов.

В частности, данные записи передаются из контроллера 2 памяти в блок DQ ввода и вывода данных. В блоке DQ ввода и вывода данных, контроллер 16 ввода и вывода 16 делит данные записи на множество блоков данных, причем каждый блок данных имеет заданное число битов. Каждый разделенный блок данных также может упоминаться, например, как слово ECC. Эти слова ECC переносятся в схему 14 исправления ошибок.

Кодер 141 ECC генерирует код с исправлением ошибок (контроль четности) из слова ECC и связывает контроль четности со словом ECC. Контроль четности представляет собой битовую строку или тому подобное, сформированное в соответствии с предопределенным правилом генерации кода с исправлением ошибок и используемое при последующем обнаружении ошибок. Число битов слова ECC также является предопределенным в соответствии с правилом генерации кода с исправлением ошибок.

Правило формирования кода с исправлением ошибок, используемое в схеме 14 исправления ошибок, сконфигурировано так, чтобы разрешить обнаружение ошибки, имеющей максимум N битов для каждого блока данных или, другими словами, слова ECC. То есть, контроль четности генерируется в соответствии с правилом генерации кода с исправлением ошибок таким образом, что контроль четности может использоваться при обнаружении ошибок для ошибки, имеющей максимум N битов. Известны различные правила генерации кода с исправлением ошибок. Например, правило генерации кода с исправлением ошибок, используемое в схеме 14 исправления ошибок, может быть выбрано из таких известных правил генерации кода с исправлением ошибок.

Кодер 141 ECC выполняет обработку данных во время, например, операции записи. Набор слова ECC и контроля четности переносится в контроллер 13 столбцов и записывается в ячейку МС памяти.

Схема 14 исправления ошибок исправляет ошибку в данных считывания с использованием декодера 12M или 142N ЕСС и генератора 143 синдрома.

В частности, схема 14 исправления ошибок принимает данные, считанные из ячейки МС памяти. Подобно данным при записи, данные, считанные из ячейки памяти, включают в себя наборы слова ECC и контроля четности.

Генератор 143 синдрома вычисляет синдром согласно матрице декодирования, который соответствует правилу генерации кода с исправлением ошибок, описанному выше, и наборам слова ECC и контроля четности. Синдром может быть получен, например, путем умножения битовой строки, в которой наборы слова ECC и контроля четности конкатенированы, на матрицу декодирования. Синдром представляет собой битовую строку или подобное, включающее в себя информацию об ошибках данных. Информация об ошибках данных может включать в себя, например, информацию о наличии или отсутствии ошибки в отдельных словах ECC, информацию об идентификации битовой позиции ошибки, информацию о числе ошибочных битов и т.д. Генератор 143 синдрома соответствует правилу генерации кода с исправлением ошибок, используемому в схеме 14 исправления ошибок, и может генерировать синдром, способный обнаруживать ошибку, имеющую максимум N битов для каждого блока данных. То есть, генератор 143 синдрома использует матрицу декодирования, способную обнаруживать ошибку, имеющую максимум N битов для каждого блока данных.

Определитель 144 определяет, превышает ли число ошибочных битов определенные критерии. В частности, определитель 144 обращается к синдрому, чтобы определить, является ли число ошибочных битов равным нулю или равным или меньшим, чем М битов или N битов.

Декодер 142N ECC может исправить ошибку, имеющую максимум N битов для каждого блока данных, на основе информации об ошибках, включенной в синдром. Декодер 142N ECC идентифицирует позиции ошибок или подобное максимум N битов для каждого блока данных путем выполнения операции с синдромом и полиномом исправления ошибок, который соответствует правилу генерации кода с исправлением ошибок. Чтобы идентифицировать позиции ошибки максимум N битов для каждого блока данных, чтобы тем самым обеспечить исправление ошибок, может использоваться полином исправления ошибок, например, уравнения N-ой степени с N неизвестными. В идентифицированных позициях ошибки, декодер 142N ECC инвертирует данные ʺ0ʺ и данные ʺ1ʺ. Соответственно, исправляется ошибка, имеющая максимум N битов для каждого блока данных. Декодер 142N ЕСС выполняет коррекцию ошибок во время, например, операции очистки.

Декодер 142M ECC может исправить ошибку, имеющую максимум М битов для каждого блока данных, в соответствии с информацией об ошибках, включенной в синдром. М битов меньше, чем N битов, упомянутых выше. Декодер 142M ECC идентифицирует позиции ошибок или подобное максимум M битов для каждого блока данных, выполняя операцию с синдромом и полиномом, упрощенным из полинома исправления ошибок, используемого в декодере 142N ECC, или полинома исправления ошибок более низкой степени. Чтобы идентифицировать позиции ошибок максимум М битов для каждого блока данных, чтобы тем самым обеспечить исправление ошибок, может использоваться полином исправления ошибок, например, уравнения М-ой степени с М неизвестными. Декодер 142M ЕСС инвертирует данные, расположенные в идентифицированных позициях ошибок. Соответственно, исправляется ошибка, имеющая максимум М битов для каждого блока данных. Декодер 142M ECC выполняет исправление ошибок во время, например, операции считывания.

Число ошибочных битов, такое как N битов или М битов, определяется путем уравновешивания, например, времени, необходимого для исправления ошибок, с надежностью, необходимой для данных. По мере увеличения числа битов, которые необходимо исправить, для исправления ошибок требуется больше времени, и наоборот. Время, необходимое для исправления ошибок, также зависит от размера данных, подлежащих обработке с помощью одной операции считывания или очистки. По мере увеличения размера данных, для исправления ошибок требуется больше времени, и наоборот. Между тем, по мере увеличения числа исправляемых битов, надежность данных улучшается, и наоборот. Ввиду вышеизложенного, число ошибочных битов, такое как N битов или М битом, может быть определено, как изложено ниже.

N представляет максимальное число исправляемых ошибочных битов для каждого блока данных в операции очистки. Операция очистки может быть выполнена, например, для обеспечения надежности хранимых данных. Поэтому требуется высокая надежность. Между тем, операция очистки выполняется с использованием времени, когда, например, никакой внешний доступ не осуществляется к MRAM 1, или тому подобного (т. е. во времени ожидания MRAM 1), что будет описано ниже. Даже когда время, затрачиваемое на исправление ошибок, становится дольше в определенной степени, не будет иметь место существенное влияние на скорость операции MRAM 1. Кроме того, размер данных, обрабатываемых одной операцией очистки, эквивалентен упомянутому выше блоку выполнения очистки. Путем надлежащей настройки блока выполнения очистки, можно регулировать время исправления ошибок. Поэтому предпочтительно устанавливать N на максимально возможное значение, которое попадает в такой диапазон, чтобы не влиять на операционную скорость MRAM 1.

M представляет максимальное число исправляемых ошибочных битов для каждого блока данных в операции считывания. В операции считывания, MRAM 1 требуется быстро отправлять данные, запрошенные контроллером 2 памяти, в контроллер 2 памяти. Время, выделенное для исправления ошибок, и, следовательно, число исправляемых ошибочных битов во время операции считывания ограничено. В операции считывания необходимо учитывать обработку маски данных, размер считываемых данных и т.д. Ввиду этих моментов, число исправляемых ошибочных битов также может быть ограничено. Поэтому M устанавливается на значение, меньшее, чем N, чтобы минимизировать влияние на скорость считывания данных, сохраняя при этом надежность, необходимую для считываемых данных.

(3) Пример операции системы памяти

Пример операции системы 10 памяти будет описан ниже со ссылкой на фиг. 3-6.

[Пример перехода состояния устройства магнитной памяти]

Сначала, со ссылкой на фиг. 3, будет приведено описание примера перехода состояния MRAM 1, на котором основаны различные операции. Фиг. 3 иллюстрирует, как изменяется состояние устройства магнитной памяти в соответствии с настоящим вариантом осуществления.

Как показано на фиг. 3, MRAM 1 имеет состояние ожидания и активное состояние.

В состоянии ожидания, MRAM 1 не выполняет операции, такие как запись, считывание и очистка.

В активном состоянии, MRAM 1 может выполнять операции, такие как запись или считывание. Состояние MRAM 1 переходит из состояния ожидания в активное состояние в ответ на команду активации из контроллера 2 памяти. В активном состоянии, MRAM 1 может принимать команду, такую как команда записи или команда считывания, из контроллера 2 памяти.

Напротив, MRAM 1 может напрямую изменять свое состояние из состояния ожидания на операцию очистки. То есть, MRAM 1 может принять команду очистки из контроллера 2 памяти в состоянии ожидания. В ответ на команду очистки, MRAM 1 запускает операцию очистки. Операция очистки включает в себя ряд операций, таких как считывание, исправление ошибки схемой 14 исправления ошибок и возобновление записи. Такие операции могут также упоминаться как операция ʺсчитывания-модификации-записиʺ.

Ввиду вышеизложенного, далее будет описан поток операции MRAM 1 и контроллера 2 памяти в таких операциях, как запись, считывание и очистка.

[Пример операции записи]

Далее будет описан пример операции записи системы 10 памяти.

После приема инструкции записи от хост-устройства 3, контроллер 215 контроллера 2 памяти выдает команду записи и передает команду записи с данными записи и адресом назначения для записи в MRAM 1.

Контроллер 16 ввода и вывода MRAM 1 переносит команду записи и адрес назначения записи в контроллер 15. Контроллер 15 передает адрес строки адреса назначения записи в декодер 12 строк и адрес столбца - в контроллер 13 столбцов.

Контроллер 16 ввода и вывода MRAM 1 также делит данные записи на множество слов ECC. Данные, разделенные на слова ECC, передаются в схему 14 исправления ошибок. Кодер 141 ECC генерирует контроль четности из отдельных слов ECC и конкатенирует слова ECC с контролем четности. Схема 14 исправления ошибок выводит наборы значений слова ECC и контроля четности на контроллер 13 столбцов.

Декодер 12 строк и контроллер 13 столбцов выбирают целевую ячейку МС памяти для записи в соответствии с адресом строки и адресом столбца. Контроллер 31 считывания и записи контроллера 15 записывает слово ECC и контроль четности в выбранную ячейку МС памяти в соответствии с командой записи.

Затем операция записи завершается.

[Пример операции считывания]

Пример операции считывания системы 10 памяти будет описан ниже со ссылкой на фиг. 4 и 5. Фиг. 4 иллюстрирует поток операции считывания системы памяти в соответствии с настоящим вариантом осуществления. Фиг. 5 иллюстрирует поток другого примера операции считывания системы памяти в соответствии с настоящим вариантом осуществления. Фиг. 4 и 5 в основном иллюстрируют операции относительно исправления ошибок.

Как показано на фиг. 4, после получения инструкции считывания от хост-устройства 3, контроллер 215 контроллера 2 памяти выдает команду считывания и передает команду считывания в MRAM 1 с адресом источника считывания (этап S11).

Контроллер 16 ввода и вывода MRAM 1 передает команду считывания и адрес источника считывания в контроллер 15. Контроллер 15 передает адрес строки адреса источника считывания в декодер 12 строк, одновременно перенося адрес столбца в контроллер 13 столбцов.

Декодер 12 строк и контроллер 13 столбцов выбирают целевые ячейки МС памяти для считывания в соответствии с адресом строки и адресом столбца. Контроллер 31 считывания и записи побуждает контроллер 13 столбца считывать данные из выбранных ячеек МС памяти в соответствии с командой считывания.

Контроллер 13 столбцов переносит данные считывания в схему 14 исправления ошибок. Генератор 143 синдрома вычисляет синдром (например, S1, S3, …, Sx) из слова ECC и контроля четности, включенных в данные считывания (этап S12).

Определитель 144 определяет, является ли число ошибочных битов в слове ECC равным нулю, из информации об ошибке, включенной в синдром (этап S13). Результат определения передается в контроллер 31 считывания и записи. Если число ошибочных битов равно нулю, контроллер 31 считывания и записи переносит слово ECC, как оно имеется в схеме 14 исправления ошибок, на контроллер 16 ввода и вывода.

Если число ошибочных битов не равно нулю, определитель 144 определяет, является ли число ошибочных битов в слове ECC равным или меньшим, чем М битов, в соответствии с информацией об ошибке, включенной в синдром (этап S14).

Если число ошибочных битов равно или меньше, чем M битов, то контроллер 31 считывания и записи побуждает декодер 142M ECC выполнять исправление ошибки, имеющей максимум M битов в слове ECC (этап S15). Контроллер 31 считывания и записи переносит данные, для которых было выполнено исправление ошибок в декодере 142M ECC, в контроллер 16 ввода и вывода.

При управлении контроллером 31 считывания и записи, блок DQ ввода и вывода данных принимает слово ECC или данные с исправленной ошибкой из декодера 142M ЕСС и передает слово ECC или данные в контроллер 2 памяти в качестве данных считывания (этап S16).

Когда число ошибочных битов больше, чем M битов, схема 14 исправления ошибок выдает предупреждение вместо выполнения исправления ошибок (этап S17). MRAM 1 передает данные, включающие в себя ошибку, в контроллер 2 памяти.

Контроллер 2 памяти определяет, принято ли предупреждение, или находится ли сигнал относительно предупреждения на уровне ʺHʺ (этап S18). Например, если контроллер 2 памяти не принял предупреждение в течение фиксированного периода после передачи команды считывания (то есть сигнал относительно предупреждения находится на уровне ʺLʺ), то контроллер 2 памяти определяет, что операция считывания завершена.

Когда контроллер 2 памяти принял предупреждение, данные, вызвавшие возникновение предупреждения, могут включать в себя множество ошибок, так что данные как таковые могут быть ненадежными. Контроллер 2 памяти может выдавать, например, команду очистки, чтобы заставить MRAM 1 выполнять операцию очистки (этап S19). Когда операция очистки завершена, контроллер 2 памяти может заставить MRAM 1 снова считывать данные, чтобы подтвердить, уменьшилось ли число ошибочных битов.

Контроллер 2 памяти может реагировать на возникновение предупреждения посредством выполнения операции, отличной от операции очистки. Контроллер 2 памяти может выдавать, например, команду записи, чтобы заставить MRAM 1 выполнить операцию записи (операцию повторной записи). Для выполнения повторной записи необходимо, чтобы данные могли быть извлечены каким-то образом, например, путем сохранения данных, которые должны быть записаны, в контроллере 2 памяти. В качестве альтернативы, контроллер 2 памяти может выдавать, например, команду стирания в соответствии с инструкцией от хост-устройства 3, и побуждает MRAM 1 удалить данные, включающие в себя множество ошибок, или запретить доступ к таким данным. Выполняя любую из этих операций, можно устранить ненадежные данные.

Как показано на фиг. 5, определитель 144 также может определить, является ли число ошибочных битов в слове ECC равным или меньшим, чем N битов, на этапе S14-2, в дополнение к определению ошибки нуля битов на этапе S13 и определению ошибки M битов на этапе S14-1. Таким образом, определитель 144 получает следующие результаты определения (а)-(d) относительно числа ошибочных битов.

(а) Число ошибочных битов=0

(b) 0 < Число ошибочных битов ≤ М битов

(c) М битов < Число ошибочных битов ≤ N битов

(d) N битов < Число ошибочных битов

Если получен результат определения (а) или (b), то ошибки в данных исправляются, и затем данные передаются в контроллер 2 памяти, как описано выше (этап S16).

Если получен результат определения (c) или (d), то в контроллер 2 памяти передается предупреждение, как описано выше (этап S17). После получения предупреждения (этап S18-1) контроллер 2 памяти может реагировать по-разному в зависимости от результата определения. То есть, контроллер 2 памяти может реагировать на результат определения (с), заставляя MRAM 1 выполнять, например, операцию очистки (от этапа S18-2 к этапу S19-1). Контроллер 2 памяти также может реагировать на результат определения (d), заставляя MRAM 1 выполнять, например, перезапись данных (от этапа S18-2 к этапу S19-2).

[Пример операции очистки]

Данные, хранящиеся в ячейках МС памяти, могут перебрасываться в обратное состояние в ответ на непреднамеренное изменение состояния сопротивления элементов MTJ. Такие данные становятся ошибочными. Ввиду данного момента, ошибки в данных могут быть обнаружены с помощью операции очистки, и корректные данные записываются обратно в ячейки МС памяти.

Контроллер 215 контроллера 2 памяти побуждает MRAM 1 выполнять операцию очистки регулярно или нерегулярно. Контроллер 2 памяти может инструктировать MRAM 1 выполнять операцию очистки, когда MRAM 1 переходит в состояние ожидания после того, как, например, прошел фиксированный период времени, или команда считывания или тому подобное была выдана более чем фиксированное число раз. Контроллер 2 памяти может вызывать выполнение операции очистки после того, как в операции считывания было обнаружено число ошибочных битов, превышающее М битов.

MRAM 1 очищает ячейки МС памяти последовательно для каждого блока очистки в соответствии с адресами, управляемыми контроллером 32 очистки, описанным выше. Следовательно, нет необходимости в том, чтобы контроллер 2 памяти указывал адрес ячейки МС памяти при побуждении MRAM 1 выполнять операцию очистки.

Пример операции очистки системы 10 памяти будет описан ниже со ссылкой на фиг. 6. Фиг.6 иллюстрирует поток операции очистки системы памяти в соответствии с настоящим вариантом осуществления. Фиг. 6 в основном иллюстрирует операцию относительно исправления ошибок.

Как показано на фиг. 6, контроллер 2 памяти выдает команду очистки и передает команду очистки в MRAM 1 (этап S21).

Контроллер 16 ввода и вывода MRAM 1 переносит команду очистки в контроллер 15. Команда очистки принимается контроллером 32 очистки контроллера 15. После приема команды очистки, контроллер 32 очистки считывает данные из ячеек МС памяти, которые соответствуют адресу, которым управляет контроллер 32 очистки и для которого должна выполняться операция очистки. То есть, контроллер 32 очистки управляет декодером строк 12 и контроллером 13 столбцов, чтобы считывать данные из выбранных ячеек МС памяти на контроллере 13 столбцов.

Контроллер 13 столбцов переносит данные считывания в схему 14 исправления ошибок. Генератор 143 синдрома вычисляет синдром (например, S1, S3,…, Sx) из слова ECC и контроля четности, включенных в данные считывания (этап S22).

Определитель 144 определяет, является ли число ошибочных битов в слове ECC равным нулю (этап S23). Если число ошибочных битов равно нулю, поток операции очистки переходит к этапу S28.

Если число ошибочных битов не равно нулю, определитель 144 определяет, является ли число ошибочных битов в слове ECC равным или меньшим, чем N битов (этап S24).

Если число ошибочных битов равно или меньше, чем N битов, контроллер 32 очистки побуждает декодер 142N ECC выполнять исправление ошибки, имеющей максимум N битов в слове ECC (этап S25). Контроллер 32 очистки управляется контроллером 31 считывания и записи, чтобы записывать обратно данные с исправленной ошибкой в ячейки МС памяти, которые были целью операции очистки (этап S26).

Операция обратной записи (операция повторной записи) данных в ячейки МС памяти выполняется без приема команды, данных или адреса из контроллера 2 памяти. Остальная часть операции обратной записи данных выполняется аналогично упомянутой выше операции записи. То есть схема 14 исправления ошибок обрабатывает данные с исправленными ошибками в наборы слова ECC и контроля четности, которые затем записываются в ячейки МС памяти с помощью контроллера 32 очистки.

Если число ошибочных битов больше, чем N битов, схема 14 исправления ошибок выдает предупреждение, и контроллер 15 передает предупреждение в контроллер 2 памяти (этап S27).

Контроллер 2 памяти определяет, находится ли предупреждение на уровне ʺHʺ (этап S28). Если предупреждение находится на уровне ʺLʺ, контроллер 2 памяти определяет, что операция очистки завершена.

Если предупреждение находится на уровне ʺHʺ, и, например, контроллер 2 памяти удерживает данные, то контроллер 2 памяти выдает команду записи, чтобы заставить MRAM 1 выполнить операцию записи (этап S29). По завершении операции записи контроллер 2 памяти может снова вызвать выполнение посредством MRAM 1 очистки данных. Контроллер 2 памяти может реагировать на появление предупреждения, выполняя операцию, отличную от записи.

(4) Преимущества настоящего варианта осуществления

Согласно настоящему варианту осуществления, одно или несколько преимуществ могут быть получены на основе следующих признаков (А) или (В).

(A) В соответствии с настоящим вариантом осуществления, схема 14 исправления ошибок включает в себя декодеры 142M, 142N ECC. Когда выполняется очистка данных, в то время как внешний доступ к MRAM 1 не выполняется (то есть, в течение времени ожидания MRA 1), декодер 142N ЕСС исправляет ошибку, имеющую максимум N битов для каждого блока данных, с использованием синдрома. Когда выполняется считывание данных, декодер 142M ЕСС исправляет ошибку, имеющую максимум M битов (M<N) для каждого блока данных, с использованием синдрома.

С помощью признака (A), MRAM 1 может сдерживать число ошибочных битов в данных в пределах требуемого диапазона путем очистки данных. Поэтому надежность данных, хранящихся в ячейках МС памяти, может быть улучшена.

С помощью признака (A), MRAM 1 может выполнять исправление ошибок с использованием высокой исправляющей способности во время очистки. Таким образом, надежность хранимых данных может быть дополнительно улучшена. Хотя для исправления ошибок потребуется больше времени, поскольку исправляющая способность улучшается, очистка выполняется с использованием периода времени, когда MRAM 1 находится в состоянии ожидания. Соответственно, можно поддерживать высокое быстродействие всей системы 10 памяти, включая MRAM 1.

С помощью признака (A), MRAM 1 может быстро передавать данные считывания в контроллер 2 памяти, за счет того, что способность исправления ошибок во время считывания ниже, чем во время очистки. Таким образом, высокое быстродействие всей системы 10 памяти может поддерживаться.

С помощью признака (A), MRAM 1 может обеспечить достаточную надежность считываемых данных, поскольку ошибочные биты исправляются даже во время считывания до тех пор, пока число ошибочных битов не станет равным или меньшим, чем М битов.

(B) В настоящем варианте осуществления, контроль четности и синдром генерируются для обнаружения N-битовой ошибки.

С помощью признака (B), два декодера 142M, 142N ЕСС могут использовать общий контроль четности и синдром. Поэтому схема 14 исправления ошибок может включать в себя упрощенную структуру по сравнению со случаем, когда используются разные типы контроля четности и синдромы.

С помощью признака (B), число битов контроля четности, которые занимают данные, обрабатываемые кодером 141 ECC, может сдерживаться по сравнению со случаем, когда необходимы, например, различные типы контроля четности и синдромы. Это может быть достигнуто, поскольку, если общий контроль четности или подобное не используется, то два типа контроля четности, например, один тип для М-битового исправления и другой тип для N-битового исправления, связываются друг с другом в слово ECC.

С помощью признака (B), исправление ошибки для ошибки, имеющей максимум N битов, может быть выполнено даже во время считывания. Соответственно, данные могут обрабатываться соответствующим образом в зависимости от числа обнаруженных ошибок. Таким образом, надежность всей системы 10 памяти может быть улучшена.

<Второй вариант осуществления>

Настоящий вариант осуществления будет описан со ссылкой на фиг. 7-10.

Настоящий вариант осуществления отличается от вышеупомянутого варианта осуществления тем, что контроллер 22 памяти вместо MRAM 21 включает в себя схему 24 исправления ошибок. Остальные части настоящего варианта осуществления аналогичны вышеупомянутому варианту осуществления, поскольку MRAM 21, контроллер 22 памяти и система памяти, включающая в себя MRAM 21 и контроллер 22 памяти, аналогичны MRAM 1, контроллеру 2 памяти и системе 10 памяти, соответственно, которые были описаны выше.

(1) Пример структуры системы памяти

Пример структуры MRAM 21 и контроллера 22 памяти в соответствии с настоящим вариантом осуществления будет описан со ссылкой на фиг. 7. На фиг.7 схематично показан пример структуры схемы исправления ошибок, включенной в контроллер памяти в соответствии с настоящим вариантом осуществления.

Как показано на фиг. 7, контроллер 22 памяти включает в себя схему 24 исправления ошибок. Схема 24 исправления ошибок включает в себя кодер 241 ECC, декодеры 242M, 242N ECC, генератор 243 синдрома и определитель 244.

Что касается передачи и приема данных, схема 24 исправления ошибок выполняет операцию, отличную от операции схемы 14 исправления ошибок в вышеупомянутом варианте осуществления. Передача и прием данных будут описаны ниже с использованием блок-схемы операции.

Остальные части схемы 24 исправления ошибок и включенные в нее компоненты аналогичны схеме 14 исправления ошибок, описанной выше. То есть, кодер 241 ECC эквивалентен кодеру 141 ЕСС схемы 14 исправления ошибок. Декодеры 242M, 242N ECC эквивалентны декодерам 142M, 142N ЕСС, соответственно. Генератор 243 синдрома эквивалентен генератору 143 синдрома. Определитель 244 соответствует определителю 144.

(2) Пример операции системы памяти

Далее, пример операции системы памяти согласно настоящему варианту осуществления будет описан со ссылкой на фиг. 8-10.

[Пример операции записи]

Сначала будет описан пример операции записи MRAM 21 и контроллера 22 памяти.

Во время операции записи схема 24 исправления ошибок управляется контроллером 215 контроллера 22 памяти для приема и обработки данных записи, прежде чем контроллер 22 памяти передает данные записи в MRAM 21. Обработанные данные передаются в MRAM 21 контроллером 22 памяти и записывается в ячейки МС памяти.

[Пример операции считывания]

Пример операции считывания MRAM 21 и контроллера 22 памяти будет описан со ссылкой на фиг. 8. Фиг.8 иллюстрирует поток операции считывания системы памяти в соответствии с настоящим вариантом осуществления.

Как показано на фиг. 8, контроллер 215 передает команду считывания в MRAM 21 вместе с адресом источника считывания (этап S31).

Контроллер 31 считывания и записи принимает команду считывания для считывания данных из ячеек МС памяти по адресу источника и передает данные как данные считывания в контроллер 22 памяти (этап S32). Данные считывания включают в себя множество наборов слова ECC и контроля четности. Данные считывания передаются к генератору 243 синдрома и декодеру 242M ECC.

Генератор 243 синдрома вычисляет синдром из данных считывания (этап S33) и передает синдром на определитель 244. Определитель 244 определяет, является ли число ошибочных битов в данных считывания равным нулю, и если нет, то определяет, является ли число ошибочных битов равным или меньшим, чем М битов (этапы S34-S35). Результат определения передается в контроллер 215.

Если число ошибочных битов равно нулю, контроллер 215 не выполняет исправление ошибок в декодере 242M ЕСС и не записывает данные обратно в MRAM 1. Поток считывания переходит тогда к этапу S38. На этапе S38 контроллер 215 определяет, выдала ли схема 24 исправления ошибок предупреждение. Если число ошибочных битов равно нулю и предупреждение не выдано, контроллер 215 завершает операцию считывания.

Между тем, если число ошибочных битов больше нуля и равно или меньше, чем М битов, контроллер 215 побуждает декодер 242M ECC выполнять исправление ошибок на данных считывания (этап S36). Если число ошибочных битов больше, чем M битов, схема 24 исправления ошибок выдает предупреждение (этап S37). Этапы S36, S37 переходят к этапу S38.

На этапе S38, когда определено, что предупреждение выдано, контроллер 215 побуждает MRAM 1 выполнять операцию очистки или подобное (этап S39). В качестве альтернативы, контроллер 22 памяти может выполнять различные отклики, как указано в связи с фиг. 4.

Определитель 244 согласно настоящему варианту осуществления может также выполнять определение ошибки из N битов в дополнение к определению ошибки 0 битов и М битов, как показано на фиг. 5.

[Пример операции очистки]

Пример операции очистки MRAM 21 и контроллера 22 памяти будет описан со ссылкой на фиг. 9. Фиг.9 иллюстрирует поток операции очистки системы памяти в соответствии с настоящим вариантом осуществления.

Как показано на фиг. 9, контроллер 215 контроллера 22 памяти передает команду очистки в MRAM 21 (этап S41).

После приема команды очистки, контроллер 32 очистки MRAM 21 управляется контроллером 31 считывания и записи для считывания данных из ячеек МС памяти, расположенных по адресу, хранящемуся в счетчике CN, и передачи данных в контроллер 22 памяти как данных считывания (этап S42). Данные считывания включают в себя множество наборов слова ECC и контроля четности. Данные считывания передаются в генератор 243 синдрома и декодер 242N ECC.

Затем контроллер 22 памяти выполняет этапы S43-S46 или этапы S43-S45, S49 и S50. Этапы S43-S46, S49 и S50 аналогичны этапам S33-S38 на фиг. 8, описанной выше, за исключением того, что число ошибочных битов равно N битов вместо M битов, и декодер 242N ECC вместо декодера 242M ЕСС включен в описание этапов S33-S38 на фиг. 8.

После этапа S46, контроллер 215 передает данные с исправленной ошибкой в MRAM 21 (этап S47). Когда MRAM 21 принимает данные, контроллер 32 очистки обращается к счетчику CN, чтобы узнать адрес ячеек МС памяти, который был целью команды очистки на этапе S41, и записывает полученные данные в ячейки MC памяти по этому адресу (этап S48). Этап S48 переходит к этапу S50.

На этапе S50, если предупреждение не выдано, контроллер 215 определяет, что операция очистки завершена.

Напротив, на этапе S50, если предупреждение выдано, контроллер 215 побуждает MRAM 21 выполнять операцию записи или тому подобное, как на этапе S29 согласно фиг. 6 (этап S51). Альтернативно, контроллер 215 может выполнить отклик, отличный от выполнения записи.

Как описано выше, MRAM 21 не включает в себя функцию обнаружения ошибок и не имеет функции исправления ошибок. Например, во время операций записи, считывания и очистки, MRAM 21 записывает данные, полученные от контроллера 22 памяти, в ячейки МС памяти и передает данные, когда они считываются из ячеек MC памяти, в контроллер 22 памяти,

Такое взаимодействие между MRAM 21 и контроллером 22 памяти будет дополнительно описано ниже.

[Пример последовательности команд в системе памяти]

Пример последовательности команд между MRAM 21 и контроллером памяти 22 в вышеприведенных операциях будет описан со ссылкой на фиг. 10. Фиг. 10 является примером последовательности команд в системе памяти согласно настоящему варианту осуществления. Последовательность команд, показанная на фиг. 10, является примером двух операций считывания и последующей операции очистки. В операции считывания, описанной ниже, предполагается, что определитель 244 выполняет полное определение ошибки 0 битов, M битов и N битов, аналогично примеру, показанному на фиг. 5.

На фиг. 10, командный сигнал CMD передается на контроллер 16 ввода и вывода MRAM 21 из контроллера 22 памяти через командную линию, включенную, например, в соединительную линию 5. Сигнал обнаружения ошибки (> 0 битов), сигнал обнаружения ошибки (> N битов) и сигнал обнаружения ошибки (> М битов) контролируются, например, определителем 244, и к ним обращается контроллер 215. Сигнал обнаружения ошибки (> 0 битов) устанавливается на уровень ʺLʺ, когда обнаруженное число ошибочных битов равно 0 битов, тогда как сигнал устанавливается на уровень ʺHʺ, когда обнаруженное число ошибочных битов превышает 0 битов. Сигнал обнаружения ошибки (> N битов) устанавливается на уровень ʺLʺ, когда обнаруженное число ошибочных битов равно или меньше, чем N битов, тогда как сигнал устанавливается на уровень ʺHʺ, когда обнаруженное число ошибочных битов превышает N битов. Сигнал обнаружения ошибки (> М битов) устанавливается на уровень ʺLʺ, когда обнаруженное число ошибочных битов равно или меньше, чем M битов, тогда как сигнал устанавливается на уровень ʺHʺ, когда обнаруженное число ошибочных битов превышает М битов.

Как показано на фиг. 10, когда начинается первая операция считывания, контроллер 215 передает команду считывания в MRAM 21 по командной линии.

После приема команды считывания контроллер 31 считывания и записи считывает данные из ячеек МС памяти, являющихся целью считывания, и передает данные считывания в контроллер 22 памяти через шину данных, включенную в соединительную линию 5. Данные считывания принимаются генератором 243 синдрома. Генератор 243 синдрома генерирует синдром. Синдром подвергается определению ошибки определителем 244. Определитель 244 использует синдром для определения числа ошибочных битов, включенных в данные считывания.

Что касается данных считывания, полученных из первой операции считывания, определитель 244 определяет, например, что число ошибочных битов равно нулю. Поэтому определитель 244 поддерживает все из сигнала обнаружения ошибки (> 0 битов), сигнала обнаружения ошибки (> М битов) и сигнала обнаружения ошибки (> N битов) на уровне ʺLʺ. Контроллер 215 принимает эти три сигнала обнаружения ошибок и, на основании этого, распознает, что число ошибочных битов равно нулю. Поэтому контроллер 215 не побуждает декодер 242M ECC выполнять исправление ошибок данных.

Затем, когда начинается вторая операция считывания, контроллер 215 передает команду считывания в MRAM 21 по командной линии.

После приема команды считывания, MRAM 21 считывает данные из ячеек МС памяти, являющихся целью считывания, и передает данные считывания в контроллер 22 памяти. Далее, подобно процедурам первой операции считывания, определитель 244 определяет, например, что число ошибочных битов превысило М битов. Затем определитель 244 изменяет состояние сигнала обнаружения ошибки (> 0 битов) и сигнала обнаружения ошибки (> М битов) до уровня ʺНʺ при сохранении состояния сигнала обнаружения ошибки (> N битов) на уровне ʺLʺ и передает эти сигналы в контроллер 215. Контроллер 215 принимает сигнал обнаружения ошибки (> 0 битов) уровня ʺHʺ и сигнал обнаружения ошибки (> М битов) уровня ʺHʺ, на основании которых распознает, что число ошибочных битов превысило М битов. Поскольку обнаруженное число ошибочных битов превысило М битов, контроллер 215 не побуждает декодер 242M ECC выполнять исправление ошибок и выдает предупреждение на хост-устройство 3. В ответ на обнаруженное число ошибочных битов выше M битов, контроллер 215 принимает соответствующие меры по мере необходимости. В примере, показанном на фиг. 10, контроллер 215 побуждает MRAM 21 выполнять операцию очистки.

Когда операция очистки начинается, контроллер 215 передает команду очистки по командной линии в MRAM 21.

После приема команды очистки, контроллер 32 очистки считывает данные из ячеек MC памяти, являющихся целью очистки, и передает данные считывания в контроллер памяти 22 по шине данных. Ячейки MC памяти, являющиеся целью очистки, представляют собой ячейки МС памяти, которые были целью второй операции считывания. Данные, считанные из ячеек памяти, являющихся целью очистки, принимаются схемой 24 исправления ошибок. Схема 24 исправления ошибок определяет число ошибочных битов, включенных в данные считывания, с помощью процедур, аналогичных процедурам первой и второй операций считывания.

Определитель 244 определяет, например, что число ошибочных битов, включенных в данные считывания, не равно нулю и равно или меньше, чем N битов. То есть определяется, что число ошибочных битов находится в пределах исправляемого диапазона с помощью декодера 242N ECC. Определитель 244 изменяет состояние сигнала обнаружения ошибки (> 0 битов) на уровень ʺНʺ. Контроллер 215 принимает сигнал обнаружения ошибки (> 0 битов) уровня ʺHʺ и сигнал обнаружения ошибки (> N битов) уровня ʺLʺ, на основании которых, распознает, что число ошибочных битов равно или меньше, чем N битов. Поэтому контроллер 215 побуждает декодер 242N ECC выполнять исправление ошибок данных.

Контроллер 215 передает данные с исправленными ошибками в MRAM 21 по шине данных. Контроллер 31 считывания и записи записывает исправленные данные в ячейки МС памяти источника. Контроллер 215 не выдает новую команду, такую как команда обратной записи данных. Команда очистки содержит инструкцию для обратной записи данных. Когда MRAM 21 принимает команду очистки без приема других команд, MRAM 21 выполняет обратную запись принятых данных в ячейки МС памяти источника в соответствии с командой очистки.

(3) Преимущества настоящего варианта осуществления

В настоящем варианте осуществления, контроллер 22 памяти включает в себя декодеры 242M, 242N ECC. Это обеспечивает одно или несколько преимуществ, упомянутых ниже, в дополнение к преимуществам вышеупомянутого варианта осуществления.

MRAM 21 может не включать в себя функцию исправления ошибок. Соответственно, пространство в MRAM 21 для функции обнаружения ошибок не потребляется. Поэтому пространство в чипе MRAM 21 может использоваться для других целей, или MRAM 21 может быть меньше.

Способность обработки MRAM 21 не потребляется для исправления ошибок. Способность обработки MRAM 21 может использоваться для других целей или может быть увеличена операционная скорость MRAM 21.

Контроллер 22 памяти включает в себя функцию исправления ошибок. Потребность в уменьшении размера контроллера 22 памяти не настолько строга, чем таковая для MRAM 21. Поэтому относительно легко выделить пространство в чипе контроллера памяти 22 для схемы 24 исправления ошибок.

Контроллер 22 памяти может предусматривать исправление ошибок. Способность обработки контроллера 22 памяти значительно больше, чем способность MRAM 21. Контроллер 22 памяти может, таким образом, выполнять исправление ошибок без существенной потери операционной характеристики контроллера 22 памяти.

<Третий вариант осуществления>

Настоящий вариант осуществления будет описан со ссылкой на фиг. 11-13.

Настоящий вариант отличается от вышеприведенных вариантов осуществления тем, что схема 54 исправления ошибок распределена в MRAM 51 и контроллере 52 памяти. Остальные части настоящего варианта осуществления аналогичны вышеупомянутым вариантам осуществления, поскольку MRAM 51, контроллер памяти 52 и система памяти, включающая в себя MRAM 51 и контроллер 52 памяти, аналогична MRAM 1, контроллеру памяти 2 и системе 10 памяти, соответственно, которые были описаны выше.

(1) Пример структуры системы памяти

Пример структуры MRAM 51 и контроллера 52 памяти в соответствии с настоящим вариантом осуществления будет описан ниже со ссылкой на фиг. 11. На фиг.11 схематично показан пример структуры схемы исправления ошибок, включенной в систему памяти согласно настоящему варианту осуществления.

Как показано на фиг. 11, MRAM 51 включает в себя схему 54M исправления ошибок, которая является частью схемы 54 исправления ошибок. Схема 54M исправления ошибок включает в себя кодер 541 ECC, декодер 542M ECC, генератор 543 синдрома и определитель 544.

Контроллер 52 памяти включает в себя схему 54N исправления ошибок, которая является частью схемы 54 исправления ошибок. Схема 54N исправления ошибок включает в себя декодер 542N ECC.

Что касается передачи и приема данных, схема 54 исправления ошибок выполняет операции, отличные от операций схемы 14 исправления ошибок в вышеупомянутых вариантах осуществления. Передача и прием данных будут описаны ниже с использованием блок-схемы операции.

Остальные части схемы 54 исправления ошибок и включенные в нее компоненты аналогичны таковым для схемы 14 исправления ошибок, описанной выше. То есть, кодер 541 ECC эквивалентен кодеру ECC 141 схемы исправления ошибок 14. Декодеры 542M, 542N ECC эквивалентны декодерам 142M, 142N ЕСС соответственно. Генератор синдрома 543 эквивалентен генератору 143 синдрома. Определитель 544 эквивалентен определителю 144.

(2) Пример операции системы памяти

Пример операции системы памяти согласно настоящему варианту осуществления будет описан ниже со ссылкой на фиг. 12 и 13.

[Пример операции записи]

Схема 54M исправления ошибок в MRAM 51 включает в себя все необходимые компоненты, требуемые для обработки данных записи, для обеспечения исправления ошибок N битов для каждого блока данных. То есть MRAM 51 включает в себя все необходимые функции, требуемые для записи данных, чтобы выполнить обработку записи данных в MRAM 51.

Поток операции записи MRAM 51 и контроллера 52 памяти является таким же, как поток первого варианта осуществления, описанного выше.

[Пример операции считывания]

Схема 54M исправления ошибок в MRAM 51 включает в себя все необходимые компоненты, требуемые для обработки данных считывания для достижения исправления ошибок M битов для каждого блока данных. То есть MRAM 51 включает в себя все необходимые функции, требуемые для считывания данных, чтобы выполнить обработку данных считывания в MRAM 51.

Поток операции считывания MRAM 51 и контроллера 52 памяти идентичен потоку, показанному на фиг. 4 и 5.

[Пример операции очистки]

Необходимая функция для операции очистки данных отдельно предоставляется в MRAM 51 и контроллере 52 памяти.

Пример операции очистки MRAM 51 и контроллера 52 памяти будет описан ниже со ссылкой на фиг. 12. Фиг. 12 иллюстрирует поток операции очистки системы памяти в соответствии с настоящим вариантом осуществления.

Как показано на фиг. 12, контроллер 215 контроллера 52 памяти передает команду очистки в MRAM 51 (этап S61).

После приема команды очистки, контроллер 32 очистки MRAM 51 управляется контроллером 31 считывания и записи для считывания данных из ячеек МС памяти по адресу, хранящемуся в счетчике CN.

Затем схема 54M исправления ошибок выполняет этапы S62-S64 и S68 или этапы S62-S64 и S69. Этапы S62-S64 и S68 аналогичны этапам S22-S24 и S26, соответственно, на фиг. 6. Этап S66, эквивалентный этапу S25 согласно фиг. 6, выполняется декодером 542N ECC посредством управления контроллером 215 контроллера 52 памяти. Поэтому синдром, вычисленный на этапе S62, передается в контроллер 52 памяти вместе с результатом определения ошибки на этапах S63, S64 (этап S65). Кроме того, данные после исправления ошибки на этапе S66 повторно передаются в MRAM 51 (этап S67), и затем выполняется этап S68. Вышеуказанные этапы S62-S64 и S69 аналогичны этапам S22-S24 и S27, соответственно, на фиг. 6.

На этапе S70, если предупреждение не выдано, контроллер 215 определяет, что операция очистки завершена.

Напротив, на этапе S70, если предупреждение выдано, контроллер 215 побуждает MRAM 51 выполнять операцию записи или тому подобное, как на этапе S29 согласно фиг. 6 выше (этап S71). Альтернативно, контроллер 215 может выполнить отклик, отличный от выполнения записи.

Как описано выше, MRAM 51 может автономно обрабатывать во время операций записи и считывания, данные, принятые от контроллера 52 памяти в схеме 54M исправления ошибок самой MRAM 51. В операции очистки, например, MRAM 51 не может выполнить обработку данных, принятых контроллером 52 памяти, в схеме 54M исправления ошибок. MRAM 51 передает синдром, вычисленный из принятых данных, в контроллер 52 памяти, который, в свою очередь, выполняет исправление ошибок.

Такое взаимодействие между MRAM 51 и контроллером 52 памяти будет описано далее с использованием последовательности команд.

[Пример последовательности команд в системе памяти]

Пример последовательности команд между MRAM 51 и контроллером 52 памяти в вышеупомянутых операциях будет описан со ссылкой на фиг. 13. На фиг. 13 показан пример последовательности команд в системе памяти согласно настоящему варианту осуществления. Последовательность команд, показанная на фиг. 13, является примером двух операций считывания и последующей операции очистки. В описанных ниже операциях считывания предполагается, что определитель 544 выполняет полное определение ошибки 0 битов, М битов и N битов, аналогично примеру, показанному на фиг. 5 выше.

Будет приведено описание различий между последовательностью команд согласно настоящему варианту осуществления и примерами согласно фиг. 10, приведенными выше.

Как показано на фиг. 13, первая операция считывания отличается от операции согласно фиг. 10 тем, что синдром, вычисленный генератором 543 синдрома, используется для определения ошибки с помощью определителя 544, а затем данные считывания передаются в контроллер 52 памяти.

Вторая операция считывания отличается от операции, показанной на фиг. 10, тем, что предупреждение передается от контроллера 15 в контроллер 52 памяти в ответ на получение определения ошибки определителем 544.

Операция очистки отличается от таковой согласно фиг. 10 тем, что синдром, вычисленный генератором 543 синдрома в ответ на команду очистки, передается в контроллер 52 памяти вместе с результатом определения ошибки определителем 544.

Кроме того, операция очистки отличается от операции очистки согласно фиг. 10 тем, что синдром, передаваемый в контроллер 52 памяти, корректируется по ошибке декодером 542N ECC, передается в MRAM 51 и записывается обратно в целевые ячейки MC памяти.

Выше был описан пример схемы 54M исправления ошибок MRAM 51, включающей в себя генератор 543 синдрома, но пример не ограничивается этим. В дополнение к генератору 543 синдрома схемы 54M исправления ошибок или вместо него, контроллер 52 памяти может включать в себя генератор синдрома. То есть, как MRAM 51, так и контроллер 52 памяти могут включать в себя генератор синдрома. Таким образом, контроллер 52 памяти может последовательно выполнять исправление ошибок во время очистки, не побуждая MRAM 51 вычислять синдром во время очистки.

Выше был описан пример схемы 54M исправления ошибок в MRAM 51, исполняющей схему исправления ошибок, но пример не ограничивается этим. Например, в дополнение к определителю 544 схемы 54M исправления ошибок или вместо него, схема 54N исправления ошибок контроллера 52 памяти может включать в себя определитель и использует синдром, переданный из MRAM 51, для выполнения исправления ошибок. В этом случае, контроллер 52 памяти может соответствующим образом реагировать на результат определения ошибки путем исправления ошибки, выдачи предупреждения и т.д.

(3) Преимущества настоящего варианта осуществления

В настоящем варианте осуществления, контроллер 52 памяти включает в себя декодер 542N ECC, и MRAM 51 включает в себя декодер 542M ECC. Это дает одно или несколько преимуществ, упомянутых ниже, в дополнение к преимуществам вышеописанных вариантов осуществления.

MRAM 51 может не включать в себя, среди функций исправления N-битовых и M-битовых ошибок, функцию исправления N-битовых ошибок. Декодер 542N ECC, который реализует функцию исправления N-битовых ошибок, должен иметь емкость и занимаемую область, большую, чем область декодера 542M ECC, который реализует функцию исправления M-битовых ошибок. Поскольку MRAM 51 не отвечает за функцию исправления N-битовых ошибок, пространство в чипе MRAM 51 может использоваться для других целей, и MRAM 51 может быть меньше.

MRAM 51 может не включать в себя функцию исправления N-битовых ошибок. Для реализации функции исправления N-битовых ошибок требуется более высокая вычислительная способность, чем для реализации функции исправления M-битовых ошибок. Поскольку MRAM 51 не отвечает за функцию исправления N-битовых ошибок, способность обработки в MRAM 51 может использоваться для других целей, и может быть улучшена операционная скорость MRAM 51.

Контроллер 52 памяти, таким образом, включает в себя декодер 542N ECC. Влияние обеспечения декодера 542N ЕСС в пространстве чипа контроллера 52 памяти может быть на допустимом уровне.

Контроллер 52 памяти может, таким образом, обладать функцией исправления N-битовых ошибок. Влияние выполнения исправления N-битовых ошибок на способность обработки контроллера 52 памяти может быть на допустимом уровне.

Другие варианты осуществления

В вариантах осуществления, описанных выше, было приведено описание примера использования того же синдрома, полученного из того же контроля четности во время исправления ошибок как N-битовых ошибок, так и M-битовых ошибок, но пример не ограничивается этим. Исправление N-битовых ошибок и M-битовых ошибок может соответствовать различным правилам генерации кода с исправлением ошибок, два разных типа контроля четности могут быть конкатенированы в секцию данных (слово ECC), и синдром может вычисляться индивидуально. Во время исправления ошибок для N-битовых ошибок и M-битовых ошибок, различные синдромы вычисляются в соответствии с контролем четности, соответствующим либо N-битовым ошибкам, либо M-битовым ошибкам.

Элемент MTJ, описанный в вышеприведенных вариантах осуществления, может представлять собой перпендикулярно намагниченный элемент MTJ, имеющий перпендикулярную магнитную анизотропию, или горизонтально намагниченный элемент MTJ, имеющий горизонтальную магнитную анизотропию. Элемент MTJ может быть элементом MTJ типа ʺсо свободным низомʺ (с верхними контактами), в котором второй магнитный слой (имеющий переменную ориентацию намагниченности) находится под первым магнитным слоем (имеющим неизменное направление намагниченности). Элемент MTJ также может быть элементом MTJ типа ʺсо свободным верхомʺ (с нижними контактами), в котором второй магнитный слой лежит над первым магнитным слоем.

В вышеприведенных вариантах осуществления было приведено описание примера, в котором устройство памяти представляет собой MRAM, которая использует элементы MTJ в качестве элементов памяти; однако пример не ограничивается этим. Устройство памяти может быть реализовано, например, как резистивная память с произвольным доступом (ReRAM), память с произвольным доступом с изменяемым фазовым состоянием (PRAM или PCRAM) и т.д.

Хотя были описаны некоторые варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема изобретений. Действительно, описанные здесь новые варианты осуществления могут быть воплощены во множестве других форм; кроме того, различные пропуски, замены и изменения в форме описанных здесь способов и систем могут быть сделаны без отклонения от сущности изобретений. Прилагаемые пункты формулы изобретения и их эквиваленты предназначены для охвата таких форм или модификаций, которые находятся в пределах объема и сущности изобретений.

Изобретение относится к области вычислительной техники. Техническим результатом является повышение надежности хранения данных при сохранении высокого быстродействия системы памяти. Раскрыто устройство памяти, содержащее: элементы памяти, которые хранят данные и контроль четности; первый декодер, который, когда выполняется очистка данных, в то время как никакой внешний доступ не осуществляется к устройству памяти, использует синдром, генерируемый из данных и контроля четности, чтобы исправлять ошибку максимум из N битов в блоке данных; и второй декодер, который, когда выполняется считывание данных, использует упомянутый синдром, генерируемый из данных и контроля четности, чтобы исправлять ошибку максимум из М битов в блоке данных, причем М битов представляет число битов, меньшее, чем N битов. 3 н. и 17 з.п. ф-лы, 13 ил.

1. Устройство памяти, содержащее:

элементы памяти, которые хранят данные и контроль четности;

первый декодер, который, когда выполняется очистка данных, в то время как никакой внешний доступ не осуществляется к устройству памяти, использует синдром, генерируемый из данных и контроля четности, чтобы исправлять ошибку максимум из N битов в блоке данных; и

второй декодер, который, когда выполняется считывание данных, использует упомянутый синдром, генерируемый из данных и контроля четности, чтобы исправлять ошибку максимум из М битов в блоке данных, причем М битов представляет число битов, меньшее, чем N битов.

2. Устройство памяти по п. 1, дополнительно содержащее:

кодер, который генерирует контроль четности из данных, которые должны быть записаны в элементах памяти; и

генератор синдрома, который генерирует синдром из данных и контроля четности, при этом

контроль четности и синдром генерируются, чтобы позволить обнаружить ошибку из N битов.

3. Устройство памяти по п. 1, в котором,

когда выполняется очистка данных, данные, в которых исправлена ошибка, записываются в элементы памяти.

4. Устройство памяти по п. 1, в котором,

во время очистки данных, выдается предупреждение, когда число ошибочных битов в блоке данных больше, чем N битов.

5. Устройство памяти по п. 1, в котором,

во время очистки данных, данные, принятые извне, повторно записываются, когда число ошибочных битов в блоке данных больше, чем N битов.

6. Устройство памяти по п. 1, в котором,

во время считывания данных, выдается предупреждение, когда число ошибочных битов в блоке данных больше, чем М битов.

7. Устройство памяти по п. 1, в котором,

во время считывания данных, выполняется очистка данных или данные, принятые извне, повторно записываются, когда число ошибочных битов в блоке данных больше, чем М битов.

8. Устройство памяти по п. 1, в котором,

в ответ на команду очистки, устройство памяти:

считывает данные и контроль четности из элементов памяти,

генерирует синдром из данных и контроля четности, и

использует упомянутый синдром для исправления ошибки данных, и

в ответ на команду считывания, устройство памяти:

считывает данные и контроль четности из элементов памяти,

генерирует синдром из данных и контроля четности,

использует упомянутый синдром для исправления ошибки данных, и

передает данные, в которых исправлена ошибка.

9. Система памяти, содержащая:

устройство памяти, включающее в себя элементы памяти, которые хранят данные и контроль четности;

контроллер памяти, который управляет устройством памяти; и

хост-устройство, которое управляет контроллером памяти, при этом,

во время очистки данных, контроллер памяти

передает команду очистки в устройство памяти для считывания данных и контроля четности из элементов памяти, в то время как никакой внешний доступ не осуществляется к устройству памяти,

генерирует синдром из данных и контроля четности, и

использует упомянутый синдром для исправления ошибки максимум из N битов в блоке данных, и

во время считывания данных, контроллер памяти

передает команду считывания на устройство памяти и считывает данные и контроль четности из элементов памяти,

генерирует синдром из данных и контроля четности, и

использует упомянутый синдром для исправления ошибки максимум из М битов в блоке данных, при этом

М битов представляет число битов, меньшее, чем N битов.

10. Система памяти по п. 9, в которой

контроль четности и синдром генерируются, чтобы позволить обнаруживать ошибку из N битов.

11. Система памяти по п. 9, в которой

контроллер памяти включает в себя

кодер, который генерирует контроль четности,

генератор синдрома, который генерирует упомянутый синдром,

первый декодер, который исправляет ошибку максимум из N битов в блоке данных, и

второй декодер, который исправляет ошибку максимум из М битов в блоке данных.

12. Система памяти по п. 9, в которой,

при очистке данных, контроллер памяти передает данные, в которых ошибка была исправлена, на устройство памяти, и

устройство памяти записывает данные, в которых ошибка была исправлена, в элементы памяти.

13. Система памяти по п. 9, в которой

контроллер памяти выдает предупреждение, когда число ошибочных битов в блоке данных больше, чем N битов, во время очистки данных, или когда число ошибочных битов в блоке данных больше, чем М битов, во время считывания данных.

14. Система памяти по п. 9, в которой,

при очистке данных, контроллер памяти повторно передает данные во время записи вместе с командой записи, когда число ошибочных битов в блоке данных больше, чем N битов, и

во время считывания данных, контроллер памяти передает команду очистки на устройство памяти или повторно передает данные для записи вместе с командой записи, когда число ошибочных битов в блоке данных больше, чем М битов.

15. Система памяти, содержащая:

устройство памяти, включающее в себя элементы памяти, которые хранят данные и контроль четности;

контроллер памяти, который управляет устройством памяти; и

хост-устройство, которое управляет контроллером памяти, при этом,

во время очистки данных, контроллер памяти передает команду очистки на устройство памяти, в то время как никакой внешний доступ не осуществляется к устройству памяти,

в ответ на команду очистки, устройство памяти считывает данные и контроль четности из элементов памяти, генерирует синдром из данных и контроля четности и передает упомянутый синдром в контроллер памяти,

после приема синдрома, контроллер памяти использует упомянутый синдром для исправления ошибки максимум из N битов в блоке данных,

во время считывания данных, контроллер памяти передает команду считывания на устройство памяти,

в ответ на команду считывания, устройство памяти считывает данные и контроль четности из элементов памяти, генерирует синдром из данных и контроля четности, использует упомянутый синдром для исправления ошибки максимум из М битов в блоке данных, передает данные, в которых ошибка была исправлена, в контроллер памяти, причем М битов представляет число битов, меньшее, чем N битов.

16. Система памяти по п. 15, в которой

контроль четности и синдром генерируются, чтобы позволить обнаруживать ошибку из N битов.

17. Система памяти по п. 15, в которой

контроллер памяти включает в себя первый декодер, который исправляет ошибку максимум из N битов в блоке данных, и

устройство памяти включает в себя кодер, который генерирует контроль четности, генератор синдрома, который генерирует упомянутый синдром, и второй декодер, который исправляет ошибку максимум из М битов в блоке данных.

18. Система памяти по п. 15, в которой,

при очистке данных, контроллер памяти передает данные, в которых ошибка была исправлена, в устройство памяти, и

устройство памяти записывает данные, в которых ошибка была исправлена, в элементы памяти.

19. Система памяти по п. 15, в которой,

при очистке данных, контроллер памяти выдает предупреждение, когда число ошибочных битов в блоке данных больше, чем N битов, и

во время считывания данных, устройство памяти выдает предупреждение, когда число ошибочных битов в блоке данных больше, чем М битов.

20. Система памяти по п. 15, в которой,

при очистке данных, контроллер памяти повторно передает данные для записи вместе с командой записи, когда число ошибочных битов в блоке данных больше, чем N битов, и

во время считывания данных, контроллер памяти передает команду очистки в устройство памяти или повторно передает данные для записи вместе с командой записи, когда число ошибочных битов в блоке данных больше, чем М битов.

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| RU 2008111995 A, 10.12.2009. | |||

Авторы

Даты

2019-03-21—Публикация

2015-09-10—Подача