ПЕРЕКРЕСТНАЯ ССЫЛКА НА СВЯЗАННЫЕ ЗАЯВКИ

Настоящая заявка основана на и испрашивает приоритет предшествующей предварительной заявки США № 62/130,490, поданной 9 марта 2015 г., все содержание которой включено в настоящий документ посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Настоящий вариант осуществления относится к полупроводниковому запоминающему устройству.

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

Магниторезистивная память с произвольным доступом (MRAM) представляет собой устройство памяти, в котором ячейка памяти для хранения информации использует магнитный элемент, обладающий магниторезистивным эффектом. MRAM привлекает внимание в качестве устройства памяти следующего поколения, характеризуемого высоким быстродействием, большой емкостью хранения и энергонезависимостью. Между тем, проводятся исследования и разработки по замене динамической памяти с произвольным доступом (DRAM) и статической памяти с произвольным доступом (SRAM) на MRAM. Чтобы снизить затраты на разработку и обеспечить плавное осуществление такой замены, желательно, чтобы MRAM работала в соответствии с теми же спецификациями, что и DRAM и SRAM.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

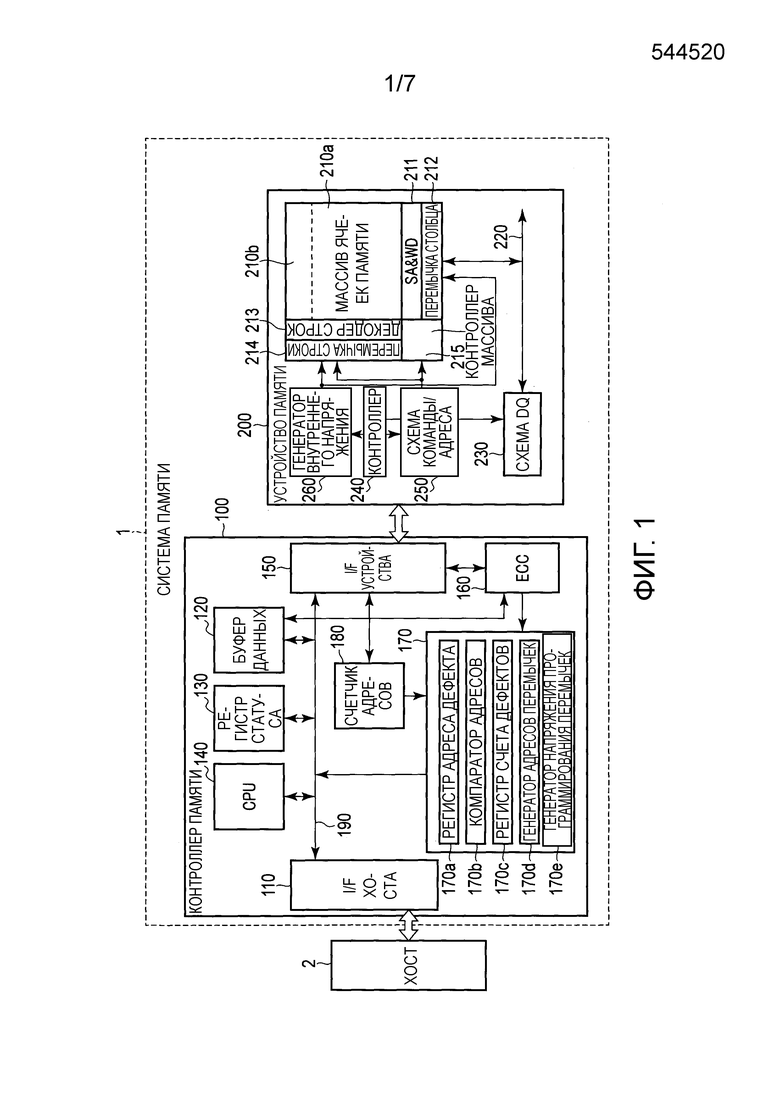

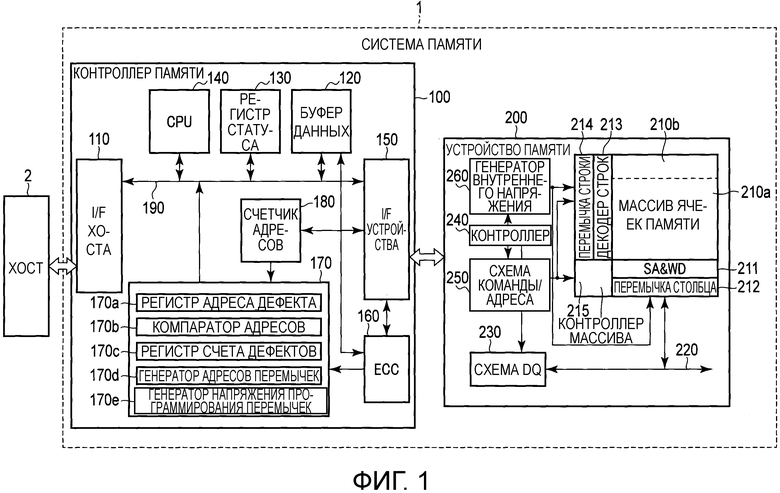

Фиг. 1 - блок-схема, показывающая примерную конфигурацию системы памяти в соответствии с вариантом осуществления.

Фиг. 2 - принципиальная схема, показывающая примерную конфигурацию массива ячеек памяти системы памяти согласно варианту осуществления.

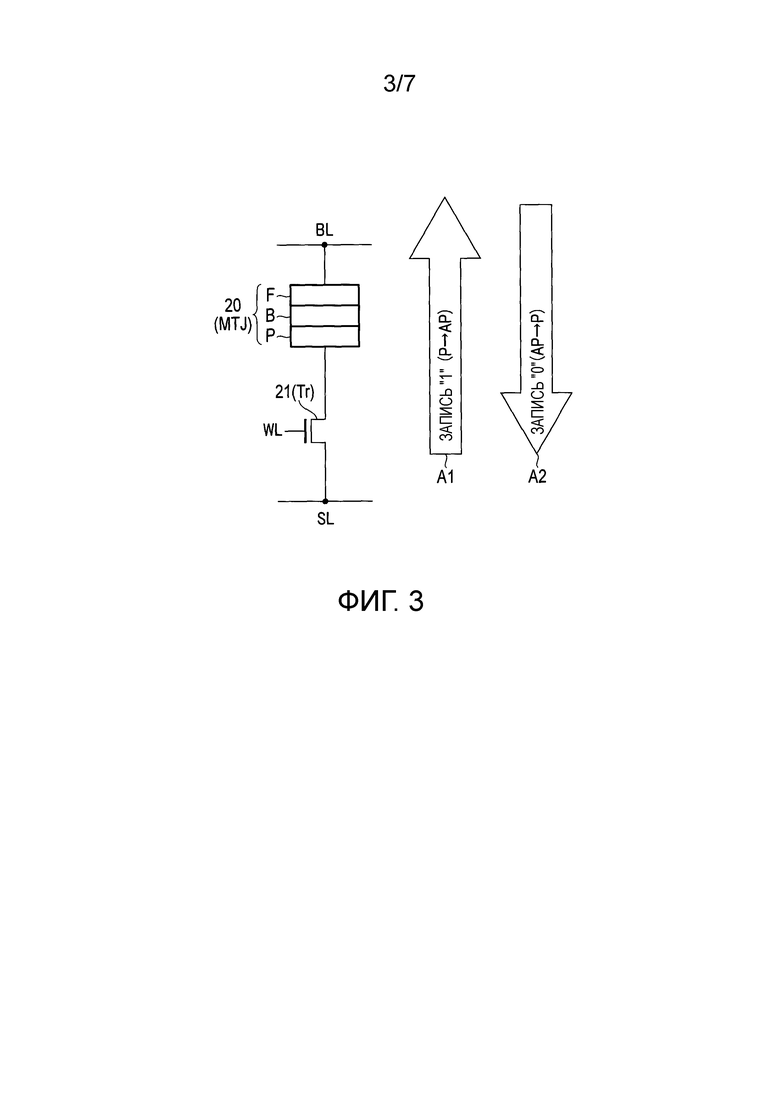

Фиг. 3 иллюстрирует базовую конфигурацию ячейки памяти в системе памяти согласно варианту осуществления.

Фиг. 4 - диаграмма состояний, иллюстрирующая систему памяти согласно варианту осуществления.

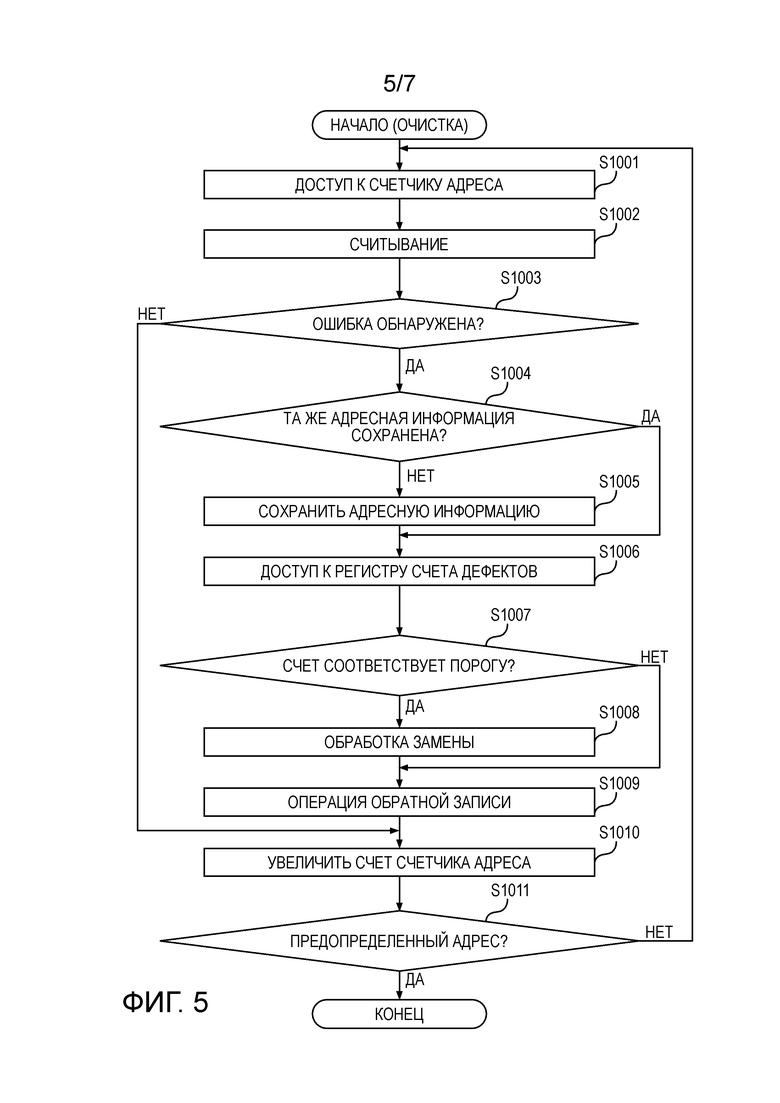

Фиг. 5 - блок-схема последовательности операций, иллюстрирующая операцию очистки системы памяти согласно варианту осуществления.

Фиг. 6 - временная диаграмма сигналов, иллюстрирующая операцию очистки системы памяти согласно варианту осуществления.

Фиг. 7 - временная диаграмма сигналов, иллюстрирующая операцию очистки системы памяти согласно варианту осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

В общем, согласно одному варианту осуществления, система памяти включает в себя:

первую область ячейки памяти, в которой обеспечена первая ячейка памяти;

вторую область ячейки памяти, в которой обеспечена вторая ячейка памяти;

схему ECC, которая исправляет ошибку данных, сохранных первой ячейкой памяти; и

схему управления, которая заменяет первую ячейку памяти второй ячейкой памяти, если число раз, когда ошибка в первой ячейке памяти успешно исправлена, достигает первого значения.

Ниже будет приведено описание вариантов осуществления. В приведенном ниже описании структурные элементы, имеющие по существу одни и те же функции и конфигурации, будут обозначены одинаковыми ссылочными позициями, и повторяющееся описание будет дано только там, где это необходимо. Каждый из вариантов осуществления, описанных ниже, просто показывает примерное устройство и способ, которые реализуют технические идеи вариантов осуществления. Технические идеи вариантов осуществления не ограничиваются материалами, формами, структурами, компоновками и т.д., описанными ниже. Технические идеи вариантов осуществления могут варьироваться в пределах диапазона, определенного в формуле изобретения.

Каждый из функциональных блоков может быть реализован в форме аппаратных средств, программного обеспечения или их комбинации. Чтобы пояснить, что конкретно подразумевается под функциональными блоками, блоки будут объяснены ниже с точки зрения их функций. То, реализованы ли эти функции в виде аппаратных средств или программного обеспечения, является вопросом конкретной реализации или зависит от конструктивных ограничений, налагаемых на систему в целом. Специалисты в данной области техники могут реализовать функции различными способами для каждого из вариантов осуществления, и то, каким образом реализовать функции, находится в пределах диапазона вариантов осуществления.

(Вариант осуществления)

<1> Конфигурация

Настоящий вариант осуществления будет описан со ссылкой на случай, когда MRAM применена для массива ячеек памяти.

<1-1> Конфигурация системы памяти

Схематичное описание будет дано со ссылкой на фиг. 1, иллюстрирующую базовую конфигурацию системы памяти согласно варианту осуществления. Система 1 памяти содержит контроллер 100 памяти и устройство 200 памяти.

<1-2> Конфигурация контроллера памяти

Контроллер 100 памяти согласно варианту осуществления принимает команды от хоста 2. В соответствии с командами, контроллер 100 памяти считывает данные из устройства 200 памяти и записывает данные в устройство 200 памяти.

Контроллер 100 памяти снабжен интерфейсом 110 хоста (I/F хоста), буфером 120 данных, регистром 130 статуса, центральным процессором (CPU) 140, интерфейсом (I/F) 150 устройства, схемой 160 кода с исправлением ошибок (ECC), контроллером 170 перемычек и счетчиком 180 адресов.

Интерфейс 110 хоста соединен с хостом (внешним устройством) 2, таким как персональный компьютер, и дополнительно соединен с шиной 190 контроллера 100 памяти. Через интерфейс 110 хоста данные передаются и принимаются между хостом 2 и системой 1 памяти.

Буфер 120 данных соединен с интерфейсом 110 хоста и далее с шиной 190. Буфер 120 данных принимает, посредством интерфейса 110 хоста, данные, передаваемые от хоста 2 в систему 1 памяти, и временно сохраняет данные. Кроме того, буфер 120 данных временно сохраняет данные, которые должны быть переданы из системы 1 памяти к хосту 2 посредством интерфейса 110 хоста. Буфер 120 данных может быть либо энергозависимой памятью, либо энергонезависимой памятью.

CPU 140 управляет всеми операциями системы 1 памяти. CPU 140 выполняет предопределенную обработку для устройства 200 памяти в соответствии с командами, принятыми, например, от хоста 2.

Регистр 130 статуса является, например, энергозависимой памятью и сохраняет информацию о настройке, команды, исполняемые посредством CPU 140, и сигналы статуса. Регистр 130 статуса может быть либо энергозависимой памятью, либо энергонезависимой памятью.

Интерфейс 150 устройства связывает контроллер 100 памяти и устройство 200 памяти и позволяет передавать и принимать различные виды сигналов между ними. Интерфейс 150 устройства соединен со схемой 160 ECC, счетчиком 180 адресов и шиной 190.

Схема 160 ECC принимает данные записи, полученные от хоста 2, посредством буфера 120 данных. Схема 160 ECC добавляет код с исправлением ошибок к данным записи. Схема 160 ECC подает данные записи, включая добавленный к ним код с исправлением ошибок, в буфер 120 данных или интерфейс 150 устройства.

Схема 160 ECC принимает данные, подаваемые из устройства 200 памяти, посредством интерфейса 150 устройства. Данные представляют собой данные, хранящиеся в группе ячеек памяти массива 210 ячеек памяти. Группа ячеек памяти представляет собой набор ячеек МС памяти и соответствует блоку считывания во время операций считывания. Схема 160 ECC определяет, содержат ли данные, полученные от устройства 200 памяти, ошибку. Если полученные данные содержат ошибку, схема ECC выполняет исправление ошибок для принятых данных, используя код с исправлением ошибок. Схема 160 ECC передает данные, подвергнутые исправлению ошибок, в буфер 120 данных, интерфейс 150 устройства и т.д. Если определено, что данные, считанные из устройства 200 памяти, содержат ошибку, схема 160 ECC подает сигнал уведомления об ошибке ʺErrorʺ на контроллер 170 перемычек. Если определено, что данные, считанные из устройства 200 памяти, не содержат ошибки, схема 160 ECC подает на хост 2 сигнал уведомления ʺNo_Errorʺ.

Контроллер 170 перемычек генерирует информацию адреса избыточности (посредством которой ячейки памяти, используемые для хранения данных, заменяются ячейками избыточности) и сигнал генерации напряжения программирования перемычек в соответствии с числом раз, когда возникает ошибка (в настоящем варианте осуществления, упомянутое число раз равно числу раз, когда ошибка успешно исправлена схемой 160 ECC).

Контроллер 170 перемычек содержит регистр 170a адреса дефекта, компаратор 170b адресов, регистр 170c счета дефектов, генератор 170d адресов перемычек и генератор 170e напряжения программирования перемычек.

Генератор 170a адреса дефекта хранит, в качестве информации об адресе дефекта, адресную информацию, представляющую массив 210 ячеек памяти, в котором ошибка обнаружена схемой 160 ECC. Для простоты, адрес массива 210 ячейки памяти может упоминаться просто как ʺадресʺ в описании настоящего варианта осуществления. ʺАдресʺ является информацией, представляющей, где находится ячейка МС памяти массива 210 ячеек памяти или группа ячеек памяти. Регистр 170a адреса дефекта может хранить множество фрагментов информации об адресе дефекта. Регистр 170a адреса дефекта может быть либо энергозависимой памятью, либо энергонезависимой памятью.

Компаратор 170b адресов сравнивает адрес, который схема 160 ECC определяет как содержащий ошибку, с адресом, сохраненным в регистре 170a адреса дефекта. Более конкретно, компаратор 170b адресов принимает адрес, представляющий местоположение ошибки, от счетчика 180 адресов, если он принимает сигнал уведомления об ошибке ʺErrorʺ из схемы 160 ECC. Затем, компаратор 170b адресов определяет, сохранена ли информация о принятом адресе в регистре 170a адреса дефекта.

Регистр 170c счета дефектов хранит данные, представляющие число раз возникновения ошибки по адресу дефекта, сохраненному в регистре 170a адреса дефекта (упомянутое число раз равно числу раз, когда ошибка успешно исправлена). При обнаружении ошибки схемой 160 ECC, регистр 170c счета дефектов увеличивает число раз повторения ошибки по адресу, соответствующему ошибке. Когда число раз возникновения ошибки (число раз, когда ошибка успешно исправлена) увеличивается и достигает порога, сохраненного в регистре 170c счета дефектов, регистр 170c счета дефектов передает сигнал ʺErr_maxʺ на генератор 170d адреса перемычки и генератор 170e напряжения программирования перемычек. Регистр 170c счета дефектов может быть либо энергозависимой памятью, либо энергонезависимой памятью.

Если число раз возникновения ошибки по дефектному адресу (т.е. число раз, когда ошибка успешно исправлена) достигает порога, генератор 170d адресов перемычек генерирует информацию адреса избыточности, посредством которой ячейка МС памяти, соответствующая дефектному адресу, заменяется ячейкой избыточности. Более конкретно, после приема сигнала ʺErr_maxʺ из регистра 170c счета дефектов, регистр 170d адреса перемычки генерирует адрес перемычки (информацию адреса избыточности) перемычки 212 столбца и/или перемычки 214 строки, так что соответствующий адрес заменяется адресом ячейки избыточности. Генератор 170d адресов перемычек может быть сконфигурирован так, чтобы генерировать адрес или адреса перемычек таким образом, что группа ячеек памяти заменяется группой ячеек избыточности, или одна ячейка памяти заменяется ячейкой избыточности. В связи с настоящим вариантом осуществления, была сделана ссылка на случай, когда система 1 памяти заменяет ячейку памяти ячейкой избыточности.

Если определено, что число раз возникновения ошибки по адресу дефекта, достигло порога, генератор 170e напряжения программирования перемычек генерирует сигнал генерации напряжения программирования перемычек. После приема сигнала генерации напряжения программирования перемычек, генератор 260 внутреннего напряжения устройства 200 памяти генерирует напряжение, на котором выполняется операция программирования перемычек для перемычки 212 столбца и/или перемычки 214 строки.

Контроллер 170 перемычек может содержать контроллер, который управляет регистром 170a адреса дефекта, компаратором 170b адресов, регистром 170c счета дефектов, генератором 170d адресов перемычек и генератором 170e напряжения программирования перемычек.

Счетчик 180 адресов хранит адресную информацию, используемую для операции очистки, упомянутой ниже.

<1-3> Конфигурация устройства памяти

Устройство 200 памяти согласно варианту осуществления содержит массив 210 ячеек памяти (который может упоминаться просто как ʺмассив ячеекʺ), усилитель считывания/формирователь сигналов (драйвер) записи 211, перемычку 212 столбца, декодер 213 строк, перемычку 214 строки, контроллер 215 массива, схему 230 DQ, контроллер 240, схему 250 команды/адреса и генератор 260 внутреннего напряжения.

Массив 210 ячеек памяти представляет собой MRAM, содержащую множество ячеек памяти, расположенных в двумерном матричном шаблоне. Массив 210 ячеек памяти содержит массив 210а обычных ячеек (который может упоминаться как обычная область памяти) и массив 210b ячеек избыточности (который также может упоминаться как область памяти избыточности). Каждый из массива 210a обычных ячеек и массива 210b ячеек избыточности включает в себя множество ячеек МС памяти. Массив 210a обычных ячеек и массив 210b ячеек избыточности являются одинаковыми с точки зрения структуры ячеек МС памяти. Массив 210a обычных ячеек представляет собой основную область памяти, используемую для нормальной операции считывания или нормальной операции записи. Массив ячейки 210b избыточности является областью памяти для устранения дефекта массива 210а обычных ячеек. Например, предположим, что массив 210a обычных ячеек имеет внутренний дефект, и этот дефект обнаруживается в операции тестирования системы 1 памяти, выполняемой перед отправкой. В этом случае ячейка МС памяти, где возникает ошибка, заменяется ячейкой памяти массива 210b ячеек избыточности. Благодаря этой замене, предотвращается использование внутренне дефектной ячейки МС памяти. Как будет описано ниже, замена дефектной ячейки памяти может выполняться в операции очистки, выполняемой после отправки системы 1 памяти. Когда информация об избыточности, соответствующая адресу, подлежащему доступу, сохранена в перемычке 212 столбца и/или перемычке 214 строки, осуществляется доступ к массиву 210b ячеек избыточности. Когда информация об избыточности, соответствующая адресу, подлежащему доступу, не сохранена в перемычке 212 столбца или перемычке 214 строки, осуществляется доступ к массиву 210a обычных ячеек. В спецификации, ячейка МС памяти, обеспеченная в массиве 210a обычных ячеек, также упоминается как обычная ячейка, а ячейка памяти, обеспеченная в массиве 210b ячеек избыточности, также упоминается как массив ячеек избыточности. Конкретная конфигурация массива 210 ячеек памяти будет описана ниже.

Усилитель считывания/драйвер записи (который также упоминается как контроллер битовой линии), 211, расположен так, чтобы продолжаться в направлении битовой линии массива 210 ячеек памяти. Усилитель считывания/драйвер записи, 211, включает в себя усилитель считывания и драйвер записи. Усилитель считывания соединен с битовыми линиями BL и считывает данные из ячейки МС памяти, когда он обнаруживает ток, протекающий через ячейку МС памяти, соединенную с выбранной числовой линией WL. Драйвер записи соединен с битовыми линиями BL и записывает данные в ячейку МС памяти, когда он подает ток в ячейку МС памяти, соединенную с выбранной числовой линией WL. Драйвер 211 считывания/записи управляет битовой линией BL и истоковой линией SL на основе управляющих сигналов, подаваемых от контроллера 215 массива. Обмен данными между усилителем считывания/драйвером записи 211 и внешним терминалом ввода/вывода (также упоминаемым как линия данных) DQ (не показан) выполняется через шину 220 данных и схему 230 DQ.

Перемычка 212 столбца представляет собой электрически программируемое энергонезависимое запоминающее устройство, такое как проводящий мостик или электрическая перемычка, и сохраняет информацию избыточности столбца в массиве 210 ячеек памяти. Перемычка 212 столбца подает, например, информацию избыточности столбца на контроллер 215 массива и усилитель считывания/драйвер записи, 211. Когда перемычка 212 столбца подает информацию избыточности столбца на контроллер 215 массива, контроллер 215 массива осуществляет доступ к соответствующей ячейке избыточности. Информация избыточности столбца включает в себя информацию о паре битовых линий (то есть информацию о битовой линии и истоковой линии), информацию о столбце и т.д. Если дефектная ячейка памяти найдена при тестировании перед отправкой в способе, описанном ниже, информация избыточности столбца сохраняется в перемычке 212 столбца.

Декодер 213 строк расположен, чтобы продолжаться в направлении числовой линии массива 210 ячеек памяти, и соединен с числовыми линиями массива 210 ячеек памяти. Декодер 213 строк декодирует адрес сигнала CAi команды/адреса, подаваемого из схемы 250 команды/адреса, и выбирает числовую линию на основе сигнала выбора числовой линии.

Перемычка 214 строки представляет собой электрически программируемое энергонезависимое запоминающее устройство, такое как проводящий мостик или электрическая перемычка, и сохраняет информацию избыточности строки в массиве 210 ячеек памяти. Перемычка 214 строки подает информацию избыточности строки в декодер 213 строк. Когда перемычка 214 строки подает информацию избыточности строки в декодер 213 строк, декодер 213 строк осуществляет доступ к соответствующей ячейке избыточности. Информация избыточности строки включает в себя информацию о числовой линии, информацию о строке и т.д. Если дефектная ячейка памяти найдена при тестировании перед отправкой в способе, описанном ниже, информация избыточности строки сохраняется в перемычке строки 214.

Перемычка 212 столбца и перемычка 214 строки могут быть предусмотрены как одна перемычка (область хранения). Если информация избыточности столбцов и информация избыточности строк не должны различаться друг от друга, они будут упоминаться просто как информация избыточности.

Контроллер 215 массива функционирует как декодер столбцов и управляет битовыми линиями BL и истоковыми линиями SL.

Схема 230 DQ позволяет обмениваться данными между контроллером 100 памяти и устройством 200 памяти с помощью внешнего терминала DQ ввода/вывода (также упоминаемого как линия данных), который не показан.

Контроллер 240 принимает различные внешние управляющие сигналы (такие как сигнал CS выбора чипа, тактовый сигнал CK, сигнал CKE разрешения тактирования и т.д.), подаваемые посредством интерфейса 150 устройства контроллера 100 памяти. Контроллер 240 управляет схемой 250 команды/адреса и различает адреса и команды друг от друга. Контроллер 240 выполняет общее управление устройством 200 памяти и управляет доступом к массиву 210 ячеек памяти, описанному ниже.

Схема 250 команды/адреса принимает сигнал CAi команды/адреса, подаваемый на нее посредством интерфейса 150 устройства контроллера 100 памяти. Схема 250 команды/адреса переносит сигнал DCAi команды/адреса в декодер 213 строк и контроллер 215 массива.

Генератор 260 внутреннего напряжения генерирует внутреннее электрическое напряжение (например, добавочное напряжение более высокое, чем напряжение питания), необходимое для каждой операции устройства 200 памяти. Управляемый контроллером 240, генератор 260 внутреннего напряжения выполняет операцию повышения напряжения и генерирует требуемое напряжение. После приема сигнала генерации напряжения программирования перемычек, генератор 260 внутреннего напряжения генерирует напряжение, при котором информация избыточности может быть записана в перемычку 212 столбца и перемычку 214 строки.

<1-4> Массив ячеек памяти

Описание будет дано со ссылкой на фиг. 2 конфигурации массива ячеек памяти в соответствии с вариантом осуществления. Как описано выше, массив 210 ячеек памяти содержит множество ячеек памяти, расположенных в двумерном матричном шаблоне. Числовые линии WL, проходящие в направлении строк, и битовые линии BL, проходящие в направлении столбцов, пересекаются друг с другом. Смежные две битовые линии BL образуют пару, и ячейка MC памяти обеспечена на пересечении между числовой линией WL и парой битовых линий (в настоящем варианте осуществления пара битовых линий будет упоминаться как битовая линия BL и истоковая линия SL, для целей описания). Более конкретно, массив 210 ячеек памяти содержит множество числовых линий WL0 до WLi-1, множество битовых линий BL0 до BLj-1 и множество истоковых линий SL0 до SLj-1. Одна из строк массива ячеек памяти соединена с одной числовой линией WL, и один из столбцов массива ячеек памяти соединен с одной парой, образованной одной битовой линией BL и одной истоковой линией SL.

Каждая ячейка MC памяти включает в себя элемент 20 магнитного туннельного перехода (MTJ) и транзистор 21 выбора. Транзистор 21 выбора образован, например, N-канальным MOSFET.

Один конец элемента 20 MTJ соединен с битовой линией BL, а другой его конец соединен со стоком транзистора 21 выбора. Затвор транзистора 21 выбора соединен с числовой линией WL, а его исток соединен с истоковой линией SL.

Массив 210a обычных ячеек и массив 210b ячеек избыточности имеют, по существу, ту же базовую конфигурацию, как описано выше, хотя различия между ними не были упомянуты.

<1-5> Ячейка памяти

Схематичное описание будет дано со ссылкой на фиг. 3 конфигурации ячейки памяти согласно варианту осуществления.

Как показано на фиг. 3, один конец элемента 20 MTJ ячейки MC памяти согласно варианту осуществления соединен с битовой линией BL, а другой конец элемента 20 MTJ соединен с одним путем тока транзистора 21 ячейки. Другой конец транзистора 21 ячейки соединен с истоковой линией SL. Элемент 20 MTJ, использующий туннельный магниторезистивный (TMR) эффект, имеет стековую структуру, включающую в себя два ферромагнитных слоя F, P и один немагнитный слой (пленку изолирования туннеля) B между ферромагнитными слоями F, P. Элемент 20 MTJ сохраняет цифровые данные в использованием изменений в магнитном сопротивлении, вызванных спино-поляризованным туннельным эффектом. Элемент 20 MTJ может быть установлен в состояние низкого сопротивления или состояние высокого сопротивления в соответствии с магнитными ориентациями двух ферромагнитных слоев F и P. Например, когда состояние низкого сопротивления определено как данные ʺ0ʺ, а состояние высокого сопротивления определено как данные ʺ1ʺ, 1-битовые данные могут быть записаны в элементе 20 MTJ. Разумеется, состояние низкого сопротивления может быть определено как данные ʺ1ʺ, а состояние высокого сопротивлением может быть определено как данные ʺ0ʺ.

Например, элемент 20 MTJ сформирован путем укладки фиксированного слоя (закрепленного слоя) P, туннельного барьерного слоя B и слоя записи (свободного слоя) F в упомянутом порядке. Закрепленный слой Р и свободный слой F образованы из ферромагнитного материала, а туннельный барьерный слой В является изолирующей пленкой (например, Al2O3, MgO). Закрепленный слой P представляет собой слой, в котором магнитная ориентация является фиксированной, в то время как свободный слой F представляет собой слой, в котором магнитная ориентация является переменной, и который сохраняет данные с использованием магнитной ориентации.

Когда ток протекает в направлении стрелки A1 в операции записи, магнитная ориентация свободного слоя F становится антипараллельной (состояние AP) относительно магнитной ориентации закрепленного слоя Р. В результате создается состояние высокого сопротивления (данные ʺ1ʺ). Когда ток протекает в направлении стрелки A2 в операции записи, магнитная ориентация свободного слоя F становится параллельной (состояние P) относительно магнитной ориентации закрепленного слоя Р. В результате создается состояние низкого сопротивления (данные ʺ0ʺ). Можно видеть, что различные данные могут быть записаны в элемент MTJ путем изменения направления протекания тока.

<2> Операция

<2-l> Переход состояний

Описание будет дано со ссылкой на фиг. 4 перехода состояний системы памяти согласно варианту осуществления. На фиг. 4, тонкие стрелки указывают, как переходит состояние MRAM, когда команда принимается от хоста 2. На фиг. 4, толстые стрелки показывают, как состояние MRAM переходит автоматически, без какой-либо команды, полученной от хоста 2, в конце предопределенной операции.

[Состояние 1] Включение питания

Как показано на фиг. 4, когда питание подается на систему 1 памяти от хоста 2, система 1 памяти переходит в состояние включения питания (состояние 1).

[Состояние 2] Сброс

Когда команда сброса подается в систему 1 памяти от хоста 2, система 1 памяти переходит в состояние сброса (состояние 2). Хост 2 может подать команду сброса в систему 1 памяти, когда эта система памяти находится либо в состоянии включения питания, либо в состоянии ожидания.

[Состояние 3] Ожидание

После обработки сброса, операция очистки или операция предварительной активации заканчивается, система 1 памяти автоматически переходит в состояние ожидания (состояние 3). В состоянии ожидания система 1 памяти готова к запуску (состояние включения).

[Состояние 4] Очистка

Когда команда очистки подается на систему 1 памяти от хоста 2, система 1 памяти переходит в состояние очистки (состояние 4). Хост 2 может подать команду очистки на систему 1 памяти, когда эта система памяти находится в состоянии ожидания (состояние 3). Подробности операции очистки будут описаны ниже.

[Состояние 5] Активация

Когда команда активации подается на систему 1 памяти от хоста 2, система 1 памяти переходит в активное состояние (состояние 5). Хост 2 может подать команду активации на систему 1 памяти, когда эта система памяти находится в состоянии ожидания (состояние 3). Когда операция считывания/записи или операция считывания/записи регистра режима заканчивается, система памяти автоматически переходит в активное состояние (состояние 5).

[Состояние 6] Считывание/запись

Когда команда считывания/записи (RD/WR) подается на систему 1 памяти из хоста 2, система 1 памяти переходит в состояние считывания/записи (состояние 6). Хост 2 может подавать команду считывания/записи на систему 1 памяти, когда эта система памяти находится либо в активном состоянии (состоянии 5), либо в состоянии считывания/записи (состоянии 6).

[Состояние 7] Считывание/запись регистра режима

Когда команда считывания/записи регистра режима (MRR/MRW) подается на систему 1 памяти из хоста 2, система 1 памяти переходит в состояние считывания/записи регистра режима (состояние 7). Хост 2 может подавать команду считывания/записи регистра режима на систему 1 памяти, когда эта система памяти находится в активном состоянии (состояние 5).

ʺСчитывание регистра режимаʺ является считыванием данных из регистра 130 статуса. ʺЗапись регистра режимаʺ является записью данных в регистр 130 статуса. Регистр 130 статуса хранит данные, представляющие рабочее состояние и т.д. устройства 200 памяти. Например, регистр 130 статуса хранит данные, представляющие тип пакета, длину пакета, период ожидания и т.д.

[Состояние 8] Предактивация

Когда команда предактивации подается на систему 1 памяти от хоста 2, система 1 памяти переходит в состояние предактивации (состояние 8). Хост 2 может подавать команду предактивации на систему 1 памяти, когда эта система памяти находится либо в активном состоянии (состояние 5), либо в состоянии ожидания (состояние 3).

Диаграмма перехода состояний, показанная на фиг. 4, является примером, и переход состояний может выполняться по-другому. Например, команда очистки может быть подана в систему, отличную от системы DDRX или LPDDRx, когда эта система находится в режиме ожидания, и операция очистки может быть выполнена в ответ на это.

<2-2> Операция очистки

Описание будет дано со ссылкой на фиг. 5 операции очистки системы памяти согласно варианту осуществления.

Операция очистки является операцией, которую контроллер 100 памяти выполняет, когда пользователь не выполняет обычную операцию считывания/записи. С помощью операции очистки, ячейки MC памяти матрицы 210a обычных ячеек циклически проверяются, и ошибка данных исправляется.

В операции очистки, если контроллер 100 памяти обнаруживает ошибку, возникающую в данных, хранящихся в предопределенной ячейке МС памяти, контроллер 100 памяти исправляет ошибку и сохраняет корректные данные в ячейке МС памяти. Как описано выше в разделе <l-5>, ток подается в элемент 20 MTJ, когда данные записываются в ячейку МС памяти. Следовательно, элементы MTJ 20 могут ухудшаться со временем в соответствии с увеличением числа раз, когда выполняется операция записи. Например, ячейка МС памяти, которая многократно испытывает ошибку (которая подвергается успешному исправлению ошибок то же самое число раз), скорее всего, будет ячейкой, которая со временем становится дефектной. Даже если корректные данные записываются обратно в такую ячейку MC памяти, они могут быть записаны ненадлежащим образом. Поэтому, ячейка МС памяти, которая испытывает ошибку более чем пороговое число раз (которая подвергается успешному исправлению ошибок то же число раз), рассматривается как вторичная дефектная ячейка. Такую ячейку MC памяти желательно заменить на ячейку MC избыточности. Таким образом, ячейки, которые становятся дефектными со временем, могут быть заменены на ячейки МС избыточности.

Вышеупомянутая операция очистки будет описана более конкретно.

Хост 2 может выдавать команду очистки в систему 1 памяти, когда эта система памяти находится в состоянии ожидания. После приема команды очистки от хоста 2, система 1 памяти запускает операцию очистки.

[Этап S1001]

После получения команды очистки, интерфейс 150 устройства считывает адрес n массива 210 ячеек памяти из счетчика 180 адресов.

[Этап S1002]

Интерфейс 150 устройства выдает адрес n и команду считывания на устройство 200 памяти. Устройство 200 памяти считывает данные из адреса n ячейки памяти на основе принятого адреса n и команды считывания. Затем устройство 200 памяти подает данные d считывания в контроллер 100 памяти через шину 220 данных, схему 230 DQ и линию DQ данных (не показана). В результате, интерфейс 150 устройства принимает данные d посредством линии DQ данных.

[Этап S1003]

Интерфейс 150 устройства подает данные d в схему 160 ECC для обнаружения ошибки данных d. Схема 160 ECC определяет, содержат ли принятые данные d ошибку. Если в данных d обнаружена ошибка, схема 160 ECC выполняет исправление ошибки для данных d с использованием кода с исправлением ошибок.

[Этап S1004]

Если определено, что данные d содержат ошибку (ʺДаʺ на этапе S1003), схема 160 ECC подает сигнал уведомления об ошибке ʺErrorʺ в контроллер 170 перемычек. Компаратор 170b адресов принимает адрес n из счетчика 180 адресов, если он принимает сигнал уведомления об ошибке ʺErrorʺ от схемы 160 ECC.

Затем, компаратор 170b адресов определяет, сохранен ли адрес n в регистре 170a адреса дефекта. Другими словами, компаратор 170b адресов определяет, сохраняет ли регистр 170a адреса дефекта ту же адресную информацию, что и адресная информация (адрес n), соответствующая ошибке.

[Этап S1005]

Если компаратор 170b адресов определяет, что адрес n не сохранен в регистре 170a адреса дефекта (ʺНетʺ на этапе S1004), компаратор 170b адресов сохраняет информацию об адресе n, соответствующем ошибке, в регистре 170a адреса дефекта.

[Этап S1006]

Если компаратор 170b адресов определяет, что адрес n сохранен в регистре 170a адреса дефекта (ʺДаʺ на этапе S1004), регистр 170c счета дефектов увеличивает счет M, соответствующий адресу n, на единицу (счет M: число раз возникновения ошибки или число раз, когда ошибка успешно исправлена).

Если регистр 170a адреса дефекта сохраняет новый адрес n, то соответствующий счет M равен 1 (M=1).

[Этап S1007]

Регистр 170c счета дефектов определяет, достиг ли счет M, соответствующий адресу n, порога Mmax. Этот порог Mmax может быть определен любым желательным способом. Порог Mmax сохраняется, например, в регистре 170c счета дефектов.

[Этап S1008]

Если число раз возникновения ошибки (число раз, когда ошибка успешно исправлена) достигло порога Mmax, ячейка МС памяти, соответствующая адресу n, считается со временем ухудшенной и неспособной хранить точные данные. Поэтому желательно, чтобы такая ячейка памяти не использовалась, и вместо этого следовало бы использовать ячейку МС памяти массива 210b ячейки избыточности. Более конкретное описание будет дано по этому вопросу.

Если регистр 170c счетчика дефектов определяет, что отсчет M, соответствующий адресу n, достиг порога Mmax (ʺДаʺ на этапе S1007), регистр 170c счетчика дефектов подает сигнал ʺErr_maxʺ на генератор 170d адресов перемычек и генератор 170e напряжения программирования перемычек.

После приема сигнала ʺErr_maxʺ, генератор 170d адресов перемычек генерирует адреса перемычек, указывающие перемычку 212 столбца и перемычку 214 строки, на основе адреса n. Генератор 170d адресов перемычек подает сгенерированные адреса перемычек (информацию адресов избыточности) на устройство 200 памяти посредством интерфейса 150 устройства.

После приема сигнала ʺErr_maxʺ, генератор 170e напряжения программирования перемычек генерирует сигнал, который побуждает генератор внутреннего напряжения генерировать электрическое напряжение, используемое для программирования перемычек (а именно, сигнал генерации напряжения программирования перемычек). Генератор 170e напряжения программирования перемычек подает сгенерированный сигнал генерации напряжения программирования перемычек на устройство 200 памяти посредством интерфейса 150 устройства.

После приема адреса перемычки и сигнала генерации напряжения программирования перемычек, контроллер 24 устройства 200 памяти выполняет программирование перемычек для перемычки 212 столбца и перемычки 214 строки. В результате, информация избыточности записывается в перемычку 212 столбца и перемычку 214 строки, тем самым обеспечивая доступ к ячейке МС памяти массива 210b ячеек избыточности, а не к ячейке МС памяти матрицы обычных ячеек, когда следует осуществлять доступ к адресу n.

В результате, ячейка МС памяти матрицы обычных ячеек обрабатывается как ячейка МС памяти, которая не должна использоваться, подобно внутренне дефектной ячейке. Замена адреса n с использованием массива 210b ячеек избыточности, как указано выше, может упоминаться как обработка замены.

Как описано выше, система 1 памяти согласно варианту осуществления позволяет устранить вторичные дефектные ячейки, которые со временем становятся дефектными.

[Этап S1009]

После завершения программирования перемычек на этапе S1008, или если регистр 170c дефекта определяет, что счет M адреса n не достиг порога Mmax (ʺНетʺ на этапе S1007), схема 160 ECC передает данные de c исправленной ошибкой в интерфейс 150 устройства. Интерфейс 150 устройства подает данные de c исправленной ошибкой, адрес n и команду записи на устройство 200 памяти.

После приема команды записи и адреса n, контроллер 240 записывает данные de, принятые через схему 230 DQ, обратно в массив 210 ячеек памяти. В результате, точные данные с исправленной ошибкой записываются в массив 210 ячеек памяти.

Если обработка замены выполнена для адреса n, связанные данные записываются в ячейку МС памяти массива 210b ячеек избыточности.

[Этап S1010]

Если определено, что данные d не содержат ошибки (ʺНетʺ на этапе S1003), схема 160 ECC подает на хост 2 сигнал уведомления ʺNo_Errorʺ.

После того как сигнал уведомления ʺNo_Errorʺ передан на хост 2 или после завершения операции обратной записи на этапе S1009, интерфейс 150 устройства увеличивает отсчет счетчика 180 адреса на один (адрес n=n+1). В результате, интерфейс 150 устройства может получить доступ к следующему адресу для адреса n.

[Этап S1011]

Интерфейс 150 устройства определяет, является ли адрес n, сохраненный в счетчике 180 адресов, предопределенным адресом. Если интерфейс 150 устройства определяет, что адрес n, сохраненный в счетчике 180 адресов, является предопределенным адресом nmax, операция очистки завершается (ʺДаʺ на этапе S1011). По завершении операции очистки, система 1 памяти автоматически переходит в состояние ожидания. Если CPU 140 определяет, что адрес n, сохраненный в счетчике 180 адресов, не является предопределенным адресом nmax (ʺНетʺ на этапе S1011), поток возвращается к этапу S1001.

Адрес nmax может быть определен любым желательным способом. Для определения адреса nmax необходимо определить число адресов, которое запускает обнаружение ошибок в операции очистки. Чем больше число адресов, тем дольше становится время, требуемое для операции очистки. Когда время, требуемое для операции очистки, является переменным, адрес nmax может быть надлежащим образом изменен.

В связи с вышеупомянутым вариантом осуществления, была сделана ссылка на случай, когда операция очистки продолжается до тех пор, пока адрес n не станет равным предопределенному адресу nmax. Однако это не накладывает никаких ограничений.

Например, операция очистки может быть прервана в ответ на запрос пользователя.

Кроме того, операция очистки может быть выполнена для одного адреса путем ввода команды очистки только один раз, вместо выполнения обнаружения ошибки для множества адресов в операции очистки.

<2-3> Конкретный пример операции, которая не вызывает ошибки

Описание будет дано со ссылкой на фиг. 6 конкретного примера операции, которую система памяти согласно варианту осуществления выполняет, когда ошибка не генерируется.

[Время Т0]

Во время T0, система 1 памяти запускает операцию очистки после получения команды очистки от хоста 2 (соответствует этапу S1001).

[Время T1]

Во время T1, данные считываются и подаются из устройства 200 памяти в контроллер 100 памяти посредством линии DQ (не показана) (соответствует этапу S1002).

[Время T2]

Во время T2, данные подаются в схему 160 ECC, и схема 160 ECC запускает операцию обнаружения ошибок (соответствует этапу S1003).

[Время T3]

Если схема 160 ECC определяет, что данные не содержат ошибки, она уведомляет хост 2 во время T3, что ошибки нет (No_Error) (соответствует этапу S1003).

[Время T4]

Во время 4, интерфейс 150 устройства увеличивает адрес счетчика 180 адресов на единицу для определения адреса, для которого выполняется последующее обнаружение ошибки (соответствует этапам S1010 и S1011). Затем интерфейс 150 устройства определяет, является ли адрес n, сохраненный в счетчике 180 адресов, предопределенным.

[Время T5]

Если операция очистки должна выполняться для одного адреса путем ввода команды очистки только один раз, хост 2 становится готовым к приему команды очистки во время T5.

В этом случае период между временем ввода команды очистки и временем, когда может быть введена следующая команда очистки, определяется как tSCRIl. Другими словами, хост 2 может выдать следующую команду очистки в систему 1 памяти, когда период tSCRIl истекает после того, как хост выдает первую команду очистки.

[Время T6 до времени T8]

После того, как хост 2 принимает команду очистки во время Т5, или если адрес счетчика 180 адресов увеличивается на единицу во время Т4, и определяется, что предопределенный адрес еще не достигнут, система 1 памяти выполняет операции, подобные тем, которые выполняются во времена Т1 до Т3.

<2-4> Конкретный пример операции, которая вызывает ошибку

Описание будет дано со ссылкой на фиг. 7 конкретного примера операции, выполняемой, когда генерируется ошибка.

[Время T10 до времени T12]

Система 1 памяти выполняет операции, аналогичные операциям, выполняемым во время T0 до T2.

[Время T13]

При обнаружении ошибки в данных, схема 160 ECC передает сигнал уведомления об ошибке ʺErrorʺ, указывающий на ошибку, на контроллер 170 перемычек (соответствует этапу S1003). Система 1 памяти выполняет операции, аналогичные операциям, выполняемым на этапах S1004-S1007, описанных выше.

[Время T14]

Если число ошибок, возникших в прошлом (число ошибок, которые были успешно исправлены), по отношению к адресу, для которого в текущий момент возникает ошибка, меньше порога, система памяти 1 записывает данные, ошибка в которых исправлена схемой 160 ECC, в массив 210 ячеек памяти во время T14 (соответствует этапу S1009).

[Время T15 до времени T18]

Система 1 памяти выполняет операции, аналогичные тем, которые выполняются во время T4 до T7.

Время tSCRI2, требуемое в случае, когда ошибка возникает и замена не выполняется, является более длительным, чем время tSCRIl, требуемое в случае, когда ошибка не возникает. Это связано с тем, что данные с исправленной ошибкой должны быть записаны в случае, когда ошибка возникает и замена не выполняется.

[Время T19]

Система 1 памяти выполняет операцию, аналогичную выполняемой во время T13.

[Время T20]

Если определено, что число раз возникновения ошибок в прошлом (число раз, когда ошибка была успешно исправлена) по отношению к адресу, для которого в текущий момент возникает ошибка, достигло предопределенного числа раз, схема 170 управления перемычками выдает сигнал ʺErr_maxʺ (соответствует этапу S1007).

[Время T21]

Во время T21, адрес программирования перемычки выдается на основе сигнала ʺErr_maxʺ и адреса, где возникла ошибка (соответствует этапу S1008).

[Время T22]

Во время T22 генерируется сигнал генерации напряжения программирования перемычек на основе сигнала ʺErr_maxʺ (соответствует этапу S1008).

[Время T23]

Во время T23, в устройстве 200 памяти (соответствует этапу S1008) выполняется операция программирования перемычек.

[Время T24]

Система 1 памяти ожидает до конца операции программирования перемычек, а затем выполняет операцию, аналогичную выполняемой во время T14.

[Время T25 и время T26]

Система 1 памяти выполняет операции, аналогичные тем, которые выполняются во времена T4 и T5.

Время tSCRI3, требуемое в случае, когда возникает ошибка и выполняется замена, является более длительным, чем время tSCRI2, требуемое в случае, когда возникает ошибка и замена не выполняется. Это связано с тем, что операция программирования перемычек должна выполняться в случае, когда возникает ошибка и выполняется замена.

<3> Преимущества

Согласно варианту осуществления, описанному выше, система памяти выполняет операцию очистки, если пользователь не запрашивает обычную операцию считывания/записи. В операции очистки, система памяти выполняет проверку ошибок в отношении ячеек МС памяти массива ячеек памяти. Если в данных обнаружена ошибка, информация об адресе, соответствующая ошибке, и число раз возникновения ошибки в прошлом по тому же адресу, сохраняются в контроллере памяти. Если число раз возникновения ошибки в прошлом достигает установленного значения, определенного пользователем, соответствующая ячейка памяти заменяется массивом ячеек избыточности.

Как описано выше, MRAM может со временем ухудшаться и стать неспособной хранить точные данные. Непрерывное использование такой ячейки МС памяти нежелательно с точки зрения надежности системы памяти.

В соответствии с вариантом осуществления, описанным выше, система памяти записывает адрес, где возникает ошибка, и число раз возникновения ошибки (число раз, когда ошибка была успешно исправлена) по тому же адресу. В силу этого, система 1 памяти может обнаруживать ячейку памяти, которая становится неспособной хранить точные данные из-за ухудшения характеристик со временем. Система 1 памяти заменяет ячейку памяти, которая не может хранить точные данные, ячейкой избыточности. Соответственно, система памяти согласно настоящему варианту осуществления является очень надежной в работе.

В соответствии с настоящим вариантом осуществления, дефектная ячейка может быть динамически заменена ячейкой избыточности даже после отправки. Другими словами, массив 210 ячеек памяти, имеющий потенциально дефектную ячейку (т.е. ячейку, имеющую низкое качество), может быть надлежащим образом исправлен. По этой причине, систему памяти не требуется подвергать строгой проверке до ее отправки. В результате электрическое напряжение, воздействующее на систему памяти во время проверки, может быть уменьшено. Соответственно, система памяти не ухудшается до ее фактического использования, и реализуется система памяти, обеспечивающая надежную работу.

(Варианты)

Вышеуказанный вариант осуществления был описан со ссылкой на случай, когда запоминающее устройство представляет собой MRAM. Однако запоминающее устройство может быть реализовано как другой тип памяти с изменяемым сопротивлением, имеющей сходные структурные элементы с теми, которые описаны выше, такой как память с произвольным доступом с изменяемым фазовым состоянием (PCRAM) или резистивная память с произвольным доступом (ReRAM). Кроме того, описанная выше система 1 памяти может быть применима к DRAM вместо MRAM.

В связи с вышеописанным вариантом осуществления, пара битовых линий была описана как имеющая битовую линию BL и истоковую линию SL, для целей описания. Однако пара битовых линий может состоять из первой битовой линии и второй битовой линии.

В системе памяти согласно вышеописанному варианту осуществления, перемычка 212 столбца и перемычка 214 строки используются для доступа к ячейке избыточности, но эта структура является просто примером. Например, одна из перемычки 212 столбца и перемычки 214 строки достаточна для доступа к ячейке избыточности, и в этом случае также может быть выполнена операция, аналогичная описанной выше.

В варианте осуществления, описанном выше, система 1 памяти предназначена для соединения одного устройства 200 памяти с контроллером 100 памяти. Однако это всего лишь пример. Например, система 1 памяти может быть сконструирована для соединения множества устройств 200 памяти с контроллером 100 памяти.

Хотя были описаны некоторые варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема формулы изобретения. Действительно, описанные здесь новые способы и системы могут быть воплощены во множестве других форм; кроме того, различные пропуски, замены и изменения в форме описанных здесь способов и систем могут быть сделаны без отклонения от сущности вариантов осуществления. Прилагаемые пункты формулы изобретения и их эквиваленты предназначены для охвата таких форм или модификаций, которые находятся в пределах объема и сущности вариантов осуществления.

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении надежности работы системы памяти. Система памяти содержит первую область ячейки памяти, где обеспечена первая ячейка памяти, причем первой ячейке памяти назначен адрес; вторую область ячейки памяти, где обеспечена вторая ячейка памяти, причем второй ячейке памяти назначен адрес; схему ECC, которая исправляет ошибку данных, хранящихся в первой ячейке памяти; схему управления, которая заменяет адрес первой ячейки памяти адресом второй ячейки памяти, если число раз исправления ошибки в первой ячейке памяти достигает первого значения; и счетчик адресов, который отсчитывает адрес каждый раз, когда осуществляется доступ к первой области ячейки памяти, причем после приема первой команды схема управления считывает данные из первой ячейки памяти, которой назначен адрес, соответствующий адресу, отсчитанному счетчиком адресов, и сохраняет адрес первой ячейки памяти, где схемой ECC успешно исправлена ошибка. 2 н. и 16 з.п. ф-лы, 7 ил.

1. Система памяти, содержащая:

первую область ячейки памяти, где обеспечена первая ячейка памяти, причем первой ячейке памяти назначен адрес;

вторую область ячейки памяти, где обеспечена вторая ячейка памяти, причем второй ячейке памяти назначен адрес;

схему ECC, которая исправляет ошибку данных, хранящихся в первой ячейке памяти;

схему управления, которая заменяет адрес первой ячейки памяти адресом второй ячейки памяти, если число раз исправления ошибки в первой ячейке памяти достигает первого значения; и

счетчик адресов, который отсчитывает адрес каждый раз, когда осуществляется доступ к первой области ячейки памяти,

причем после приема первой команды схема управления считывает данные из первой ячейки памяти, которой назначен адрес, соответствующий адресу, отсчитанному счетчиком адресов, и сохраняет адрес первой ячейки памяти, где схемой ECC успешно исправлена ошибка.

2. Система памяти по п. 1, в которой схема управления сохранят число раз, когда ошибка успешно исправлена по этому адресу, и определяет, достигает ли число раз исправления ошибки в первой ячейке памяти первого значения.

3. Система памяти по п. 2, дополнительно содержащая третью область памяти, которая хранит первую информацию, используемую для замены первой ячейки памяти второй ячейкой памяти.

4. Система памяти по п. 3, в которой схема управления генерирует адрес третьей области памяти, чтобы заменить первую ячейку памяти второй ячейкой памяти, и дополнительно генерирует электрическое напряжение, при котором данные записываются в третьей области памяти.

5. Система памяти по п. 1, при этом схема ECC выполняет проверку ошибок относительно первой области памяти до тех пор, пока адрес, сохраненный в счетчике адресов, не достигнет первого адреса.

6. Система памяти по п. 1, в которой схема управления определяет, является ли адрес, где возникает ошибка, идентичным адресу, сохраненному в схеме управления, и сохраняет адрес, где возникает ошибка, если адрес идентичен адресу, сохраненному в схеме управления.

7. Система памяти по п. 1, в которой схема управления записывает исправленные данные в тот адрес, где возникает ошибка, если число раз, когда ошибка успешно исправлена в первой ячейке памяти, не достигло первого значения, и записывает исправленные данные во второй ячейке памяти, если число раз, когда ошибка успешно исправлена в первой ячейке памяти, достигло первого значения.

8. Система памяти по п. 3, в которой третья область памяти является энергонезависимой областью.

9. Система памяти по п. 3, в которой третья область памяти образована металлом или полупроводником.

10. Система памяти по п. 3, в которой вторая область памяти является областью избыточности и доступна в соответствии с первой информацией.

11. Система памяти по п. 1, в которой первая ячейка памяти и вторая ячейка памяти включают в себя элемент с изменяемым сопротивлением, способный хранить данные.

12. Система памяти по п. 1, в которой первая область памяти и вторая область памяти выполнены из одной из магниторезистивной памяти с произвольным доступом (MRAM), сегнетоэлектрической памяти с произвольным доступом (FeRaM), памяти с произвольным доступом с изменяемым фазовым состоянием (PCRAM) или резистивной памяти с произвольным доступом (ReRaM).

13. Система памяти по п.1, в которой первая область памяти и вторая область памяти представляют собой DRAM.

14. Система памяти, содержащая:

первую область ячейки памяти, где обеспечена первая ячейка памяти, причем первой ячейке памяти назначен адрес;

вторую область ячейки памяти, где обеспечена вторая ячейка памяти, причем второй ячейке памяти назначен адрес;

схему ECC, которая обнаруживает ошибку данных, хранящихся в первой ячейке памяти;

схему управления, которая заменяет адрес первой ячейки памяти адресом второй ячейки памяти, если число раз возникновения ошибки в первой ячейке памяти достигает первого значения; и

счетчик адресов, который отсчитывает адрес каждый раз, когда осуществляется доступ к первой области ячейки памяти,

причем после приема первой команды схема управления считывает данные из первой ячейки памяти, которой назначен адрес, соответствующий адресу, отсчитанному счетчиком адресов, и сохраняет адрес первой ячейки памяти, где схемой ECC определена ошибка.

15. Система памяти по п. 14, в которой схема управления сохраняет данные о числе раз возникновения ошибки по этому адресу и определяет, достигает ли число раз возникновения ошибки в первой ячейке памяти первого значения.

16. Система памяти по п. 15, дополнительно содержащая третью область памяти, которая хранит первую информацию, используемую для замены первой ячейки памяти второй ячейкой памяти.

17. Система памяти по п. 14, в которой первая ячейка памяти и вторая ячейка памяти содержат элемент с изменяемым сопротивлением, способный хранить данные.

18. Система памяти по п. 14, в которой первая область памяти и вторая область памяти представляют собой DRAM.

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2249262C2 |

Авторы

Даты

2019-03-19—Публикация

2015-09-10—Подача