Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих усилителях с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры).

В структуре аналоговых интерфейсов различного назначения находят широкое применение операционные усилители (ОУ), характеризующиеся двухканальной передачей выходных токов входного дифференциального каскада на вход буферного усилителя [1-10]. Их основное достоинство - исключение нелинейных режимов промежуточного каскада, что способствует повышению быстродействия в схемах с нелинейной коррекцией [7, 8]. Следует отметить, что по такой архитектуре выполняются ОУ как на биполярных [2, 4, 6], так и на полевых [1, 3] транзисторах.

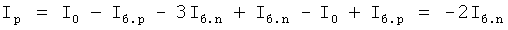

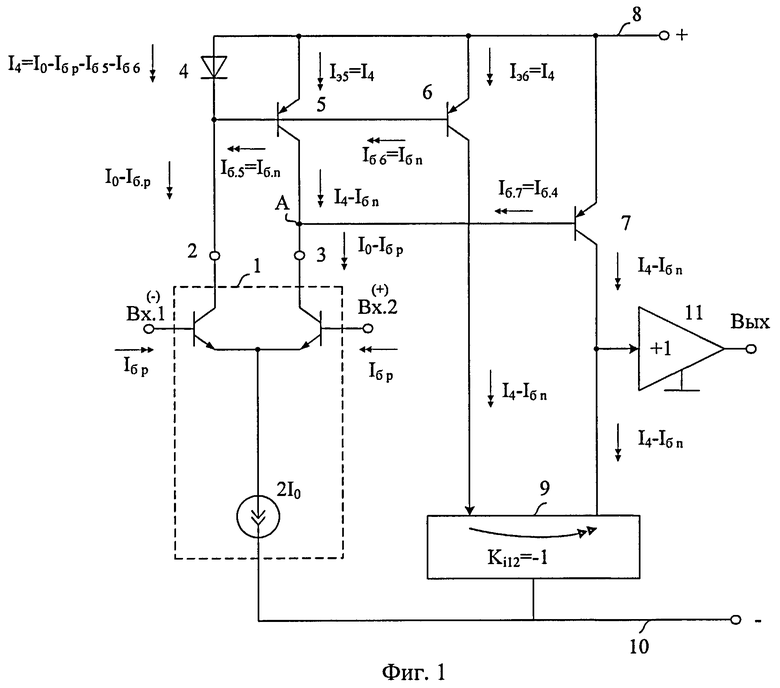

Наиболее близкой по технической сущности к заявляемому устройству является классическая схема ОУ фиг.1, представленная в патенте США №5512857 fig.3, которая стала основой построения различных аналоговых устройств, например [1-10].

Существенный недостаток ОУ-прототипа состоит в повышенном напряжении смещения нуля Uсм, что обусловлено свойствами его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении систематической составляющей напряжения смещения нуля Uсм, т.е. зависящей от схемотехники ОУ.

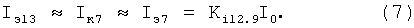

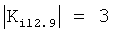

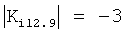

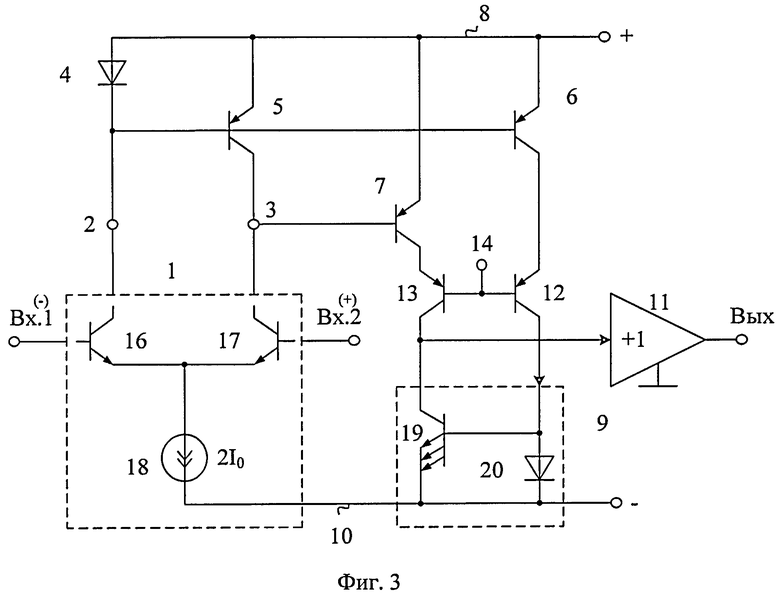

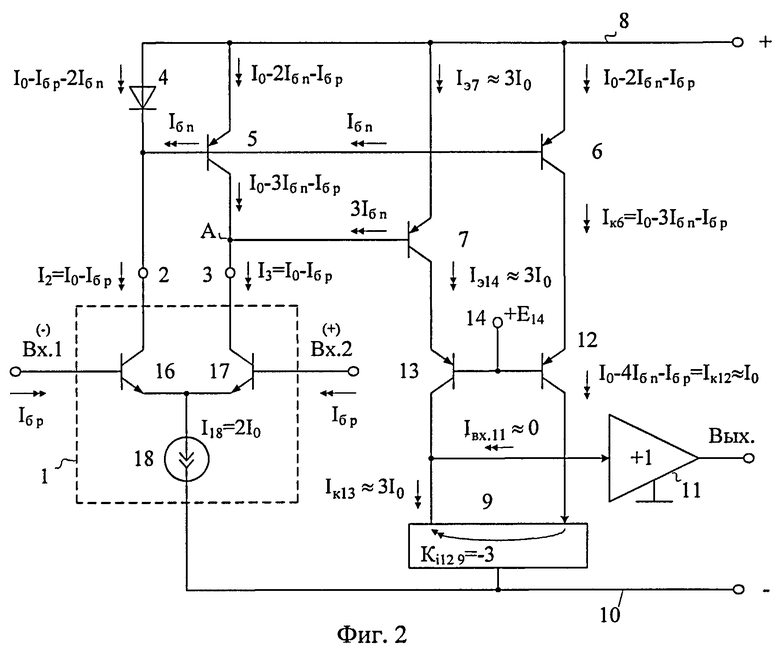

Поставленная цель достигается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1, имеющий первый 2 и второй 3 токовые выходы, p-n переход активной нагрузки 4, связанный первым выводом с базами первого 5 и второго 6 выходных транзисторов и первым 2 токовым выходом входного дифференциального каскада 1, третий 7 выходной транзистор, база которого связана со вторым 3 токовым выходом входного дифференциального каскада 1 и коллектором первого 5 выходного транзистора, первый 8 источник питания, связанный с эмиттерами первого 5, второго 6 и третьего 7 выходных транзисторов и вторым выводом p-n перехода активной нагрузки 4, токовое зеркало 9, согласованное со вторым 10 источником питания, выход которого соединен со входом цепи экстракции выходного сигнала 11, предусмотрены новые элементы и связи - коллектор второго 6 выходного транзистора соединен с эмиттером первого 12 дополнительного транзистора, база первого 12 дополнительного транзистора соединена с базой второго 13 дополнительного транзистора и источником напряжения смещения 14, коллектор первого 12 дополнительного транзистора связан со входом токового зеркала 9, эмиттер второго 13 дополнительного транзистора соединен с коллектором третьего 7 выходного транзистора, а коллектор второго 13 дополнительного транзистора подключен к выходу токового зеркала 9, причем коэффициент передачи по току токового зеркала 9 близок к трем единицам (Ki12.9=-3).

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения. На фиг.3 показана схема фиг.2 с конкретным выполнением токового зеркала 9.

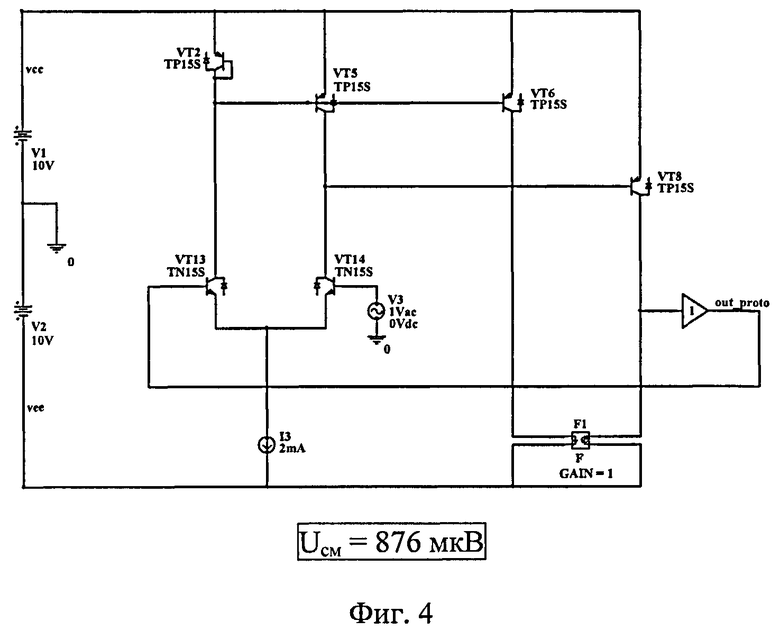

На фиг.4 представлена схема фиг.1 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

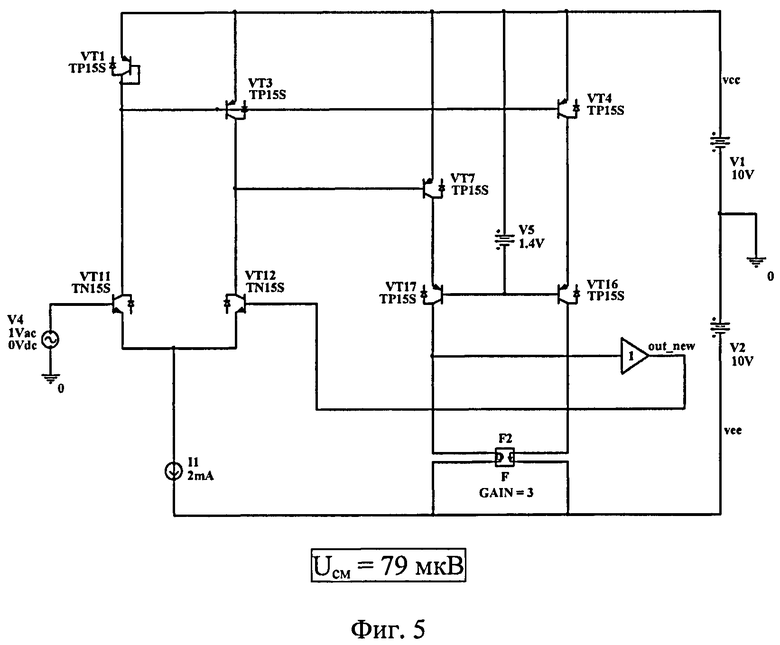

На фиг.5 показана схема фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

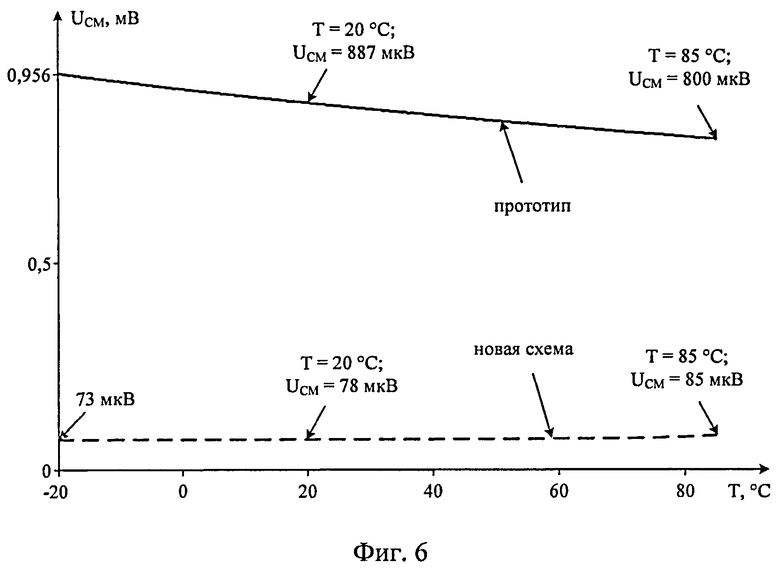

На фиг.6 представлены графики температурной зависимости Uсм ОУ-прототипа (фиг.4) и заявляемого ОУ (фиг.5), полученные в результате моделирования сравниваемых схем.

Операционный усилитель фиг.2 содержит входной дифференциальный каскад 1, имеющий первый 2 и второй 3 токовые выходы, p-n переход активной нагрузки 4, связанный первым выводом с базами первого 5 и второго 6 выходных транзисторов и первым 2 токовым выходом входного дифференциального каскада 1, третий 7 выходной транзистор, база которого связана со вторым 3 токовым выходом входного дифференциального каскада 1 и коллектором первого 5 выходного транзистора, первый 8 источник питания, связанный с эмиттерами первого 5, второго 6 и третьего 7 выходных транзисторов и вторым выводом p-n перехода активной нагрузки 4, токовое зеркало 9, согласованное со вторым 10 источником питания, выход которого соединен со входом цепи экстракции выходного сигнала 11. Коллектор второго 6 выходного транзистора соединен с эмиттером первого 12 дополнительного транзистора, база первого 12 дополнительного транзистора соединена с базой второго 13 дополнительного транзистора и источником напряжения смещения 14, коллектор первого 12 дополнительного транзистора связан со входом токового зеркала 9, эмиттер второго 13 дополнительного транзистора соединен с коллектором третьего 7 выходного транзистора, а коллектор второго 13 дополнительного транзистора подключен к выходу токового зеркала 9, причем коэффициент передачи по току токового зеркала 9 близок к трем единицам (Ki12.9=-3).

На фиг.2, в соответствии с п.1 формулы изобретения, коэффициент передачи по току токового зеркала 9 выбран близким к трем единицам. Входной дифференциальный каскад 1 реализован на базе входных транзисторов 16, 17 и токостабилизирующем двухполюснике 18.

На фиг.3 токовое зеркало 9 реализовано на основе многоэмиттерного транзистора 19 и p-n перехода 20.

К качестве цепи экстракции выходного сигнала 11 может применяться классический буферный усилитель (эмиттерный повторитель).

На фиг.2 и фиг.3, в соответствии с п.2 формулы изобретения, напряжение источника смещения 14 приблизительно на 1, 4 В меньше напряжения первого 8 источника питания.

Рассмотрим работу схемы фиг.2 на постоянном токе.

Если принять, что ток общей эмиттерной цепи I18 входного дифференциального каскада 1 равен 2I0, то токи выходов 2 и 3

где Iб.р - ток базы входных n-p-n транзисторов 16 и 17, образующих входной дифференциальный каскад 1.

С учетом первого закона Кирхгофа, можно найти ток через p-n переход 4:

где Iб.n - ток базы p-n-p транзистора при токе эмиттера I0 (Iб.5=Iб.n, Iб.6=Iб.n).

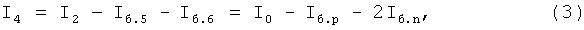

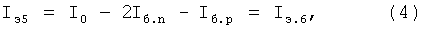

Поэтому эмиттерные токи транзисторов 5, 6, 12, 13 и 7, а также входной (Iвх.9) и выходной (Iвых.9) токи токового зеркала 9

Как следствие, базовый ток транзистора 7:

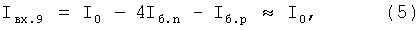

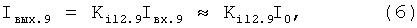

Если выбрать  и учесть, что токи эмиттера Iэi транзисторов 5 и 6 равны току через p-n переход 4, а коэффициент усиления по току базы β транзисторов 6 и 7 одинаковы (β6=β5=β7=β), то из (4)-(8) можно найти, что при нулевом входном напряжении uвх=0 сумма токов в узле «А» близка к нулю

и учесть, что токи эмиттера Iэi транзисторов 5 и 6 равны току через p-n переход 4, а коэффициент усиления по току базы β транзисторов 6 и 7 одинаковы (β6=β5=β7=β), то из (4)-(8) можно найти, что при нулевом входном напряжении uвх=0 сумма токов в узле «А» близка к нулю

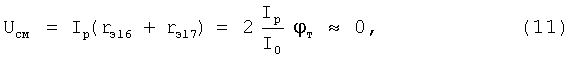

Вследствие воздействия, например, радиации или температуры, токи Iб.7, Iб.5 и Iб.6 изменяются в несколько раз, однако и в этом случае Iр≈0, так как изменения Iб.7, Iб.5, Iб.6 одинаковы. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ОУ фиг.2 в выходной ток узла «А»

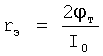

где rэ16=rэ17 - сопротивления эмиттерных переходов входных транзисторов 16 и 17 входного дифференциального каскада 1.

Поэтому для схемы фиг.2

где

;

;

φт - температурный потенциал.

В ДУ-прототипе фиг.1 разностный ток Iр≠0:

или

где βn=30÷100 - коэффициент усиления по току базы p-n-p транзисторов 5, 6, 7.

Как следствие, напряжение смещения нуля

Если β=100, то Uсм≈1 мВ, поэтому здесь систематическая составляющая Uсм получается как минимум на порядок больше (фиг.3, Uсм=876 мкВ), чем в заявляемой схеме (фиг.4, Uсм=79 мкВ). Компьютерное моделирование (фиг.5) подтверждает данные выводы.

Для получения заявляемого положительного эффекта необходимо обеспечить соотношение токов базы транзисторов 7, 6 и 5, равное Iб.7/Iб.6=3, а также Iб.5=Iб.6.

Это условие реализуется за счет выбора коэффициента передачи токового зеркала 9  и введения транзисторов 13 и 12, которые минимизируют влияние неодинаковых напряжений коллектор-база транзисторов 6, 7 и 5 на токи базы Iб.7, Iб.6, Iб.5. Так, например, если транзисторы 13 и 12 исключить из схемы фиг.2 (как на чертеже фиг.1), то при

и введения транзисторов 13 и 12, которые минимизируют влияние неодинаковых напряжений коллектор-база транзисторов 6, 7 и 5 на токи базы Iб.7, Iб.6, Iб.5. Так, например, если транзисторы 13 и 12 исключить из схемы фиг.2 (как на чертеже фиг.1), то при  условие компенсации Uсм не будет выполняться из-за эффекта Эрли.

условие компенсации Uсм не будет выполняться из-за эффекта Эрли.

В заявляемой схеме (п.2 формулы изобретения) за счет рационального выбора напряжения источника смещения 14 транзисторы 5, 6 и 7 работают при идентичных напряжениях коллектор-база, что позволяет обеспечить условия полной компенсации Uсм.

Таким образом, заявляемое устройство имеет существенное преимущество в сравнении с прототипом по статической точности.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6150884.

2. Патент США №5512857, fig.3.

3. Патентная заявка Японии JP 2002/043870.

4. А.св. СССР №614528, фиг.2.

5. Патент Японии JP 7-74554.

6. А.св. СССР №1396242, фиг.1.

7. Операционные усилители с непосредственной связью каскадов [Текст] / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - С.143. - Рис.3-37.

8. Маломощные быстродействующие операционные усилители [Текст] / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М., Югай В. // Активные избирательные системы: Межвузовский научно-технический сборник. - Таганрог: ТРТИ, 1978. - №4.

9. Патент США №3760288.

10. Патент США №6150884, fig.7.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2390921C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390916C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412538C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416155C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2419198C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416152C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416153C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390918C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412537C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих усилителях с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры). Технический результат: уменьшение систематической составляющей напряжения смещения нуля Uсм, т.е. зависящей от схемотехники ОУ. Операционный усилитель с малым напряжением смещения нуля содержит входной дифференциальный каскад (1), имеющий первый (2) и второй (3) токовые выходы, p-n переход активной нагрузки (4), связанный первым выводом с базами первого (5) и второго (6) выходных транзисторов и первым (2) токовым выходом входного дифференциального каскада (1), третий (7) выходной транзистор, база которого связана со вторым (3) токовым выходом входного дифференциального каскада (1) и коллектором первого (5) выходного транзистора, первый (8) источник питания, связанный с эмиттерами первого (5), второго (6) и третьего (7) выходных транзисторов и вторым выводом p-n перехода активной нагрузки (4), токовое зеркало (9), согласованное со вторым (10) источником питания, выход которого соединен со входом цепи экстракции выходного сигнала (11). Коллектор второго (6) выходного транзистора соединен с эмиттером первого (12) дополнительного транзистора, база первого (12) дополнительного транзистора соединена с базой второго (13) дополнительного транзистора и источником напряжения смещения (14), коллектор первого (12) дополнительного транзистора связан со входом токового зеркала (9), эмиттер второго (13) дополнительного транзистора соединен с коллектором третьего (7) выходного транзистора, а коллектор второго (13) дополнительного транзистора подключен к выходу токового зеркала (9), причем коэффициент передачи по току токового зеркала (9) близок к трем единицам (Кi12.9=-3). 1 з.п. ф-лы, 6 ил.

1. Операционный усилитель с малым напряжением смещения нуля, содержащий входной дифференциальный каскад (1), имеющий первый (2) и второй (3) токовые выходы, p-n переход активной нагрузки (4), связанный первым выводом с базами первого (5) и второго (6) выходных транзисторов и первым (2) токовым выходом входного дифференциального каскада (1), третий (7) выходной транзистор, база которого связана со вторым (3) токовым выходом входного дифференциального каскада (1) и коллектором первого (5) выходного транзистора, первый (8) источник питания, связанный с эмиттерами первого (5), второго (6) и третьего (7) выходных транзисторов и вторым выводом p-n перехода активной нагрузки (4), токовое зеркало (9), согласованное со вторым (10) источником питания, выход которого соединен со входом цепи экстракции выходного сигнала (11), отличающийся тем, что коллектор второго (6) выходного транзистора соединен с эмиттером первого (12) дополнительного транзистора, база первого (12) дополнительного транзистора соединена с базой второго (13) дополнительного транзистора и источником напряжения смещения (14), коллектор первого (12) дополнительного транзистора связан со входом токового зеркала (9), эмиттер второго (13) дополнительного транзистора соединен с коллектором третьего (7) выходного транзистора, а коллектор второго (13) дополнительного транзистора подключен к выходу токового зеркала (9), причем коэффициент передачи по току токового зеркала (9) близок к трем единицам (Кi12,9=-3).

2. Операционный усилитель с малым напряжением смещения нуля по п.1, отличающийся тем, что напряжение источника смещения (14) приблизительно на 1,4 В меньше напряжения первого (8) источника питания.

| US 5512857 A, 30.04.1996 | |||

| Операционный усилитель | 1986 |

|

SU1396242A1 |

| Дифференциальный усилитель | 1976 |

|

SU614528A1 |

Авторы

Даты

2011-03-20—Публикация

2010-03-17—Подача