Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях с малыми значениями эдс смещения нуля и его дрейфа в условиях воздействия температуры или радиации).

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ с простейшей архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу устройств.

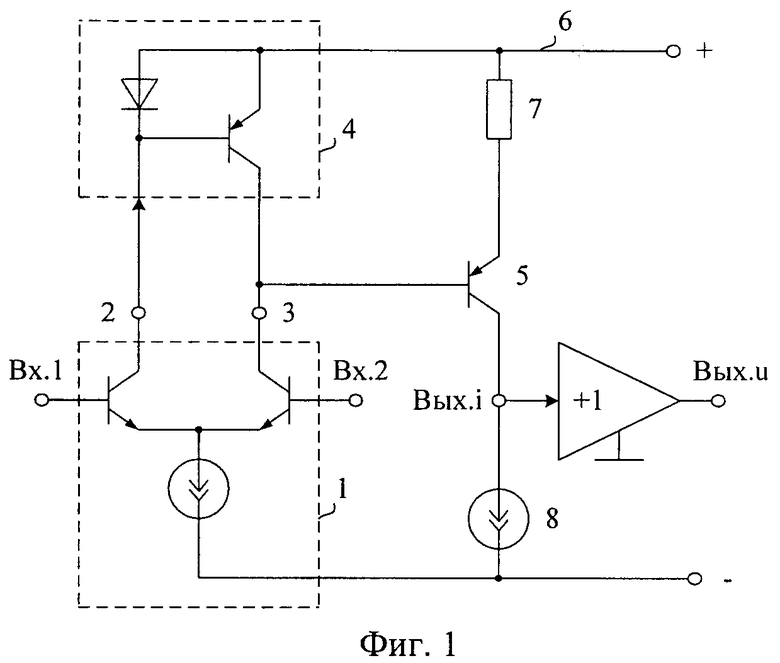

Наиболее близкой по технической сущности к заявляемому ОУ является классическая схема фиг.1 (патент США №4.410.859, fig.1), которая стала основой построения большого числа аналоговых устройств различного назначения, в том числе микросхем (574УД3, 153УД2, 1407УД3, СА3078 и др. [1-13]).

Существенные недостатки известного ОУ фиг.1 состоят в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля Uсм и высокую нестабильность Uсм вследствие воздействия температуры или радиации.

Основная цель предлагаемого изобретения состоит в уменьшении Uсм.

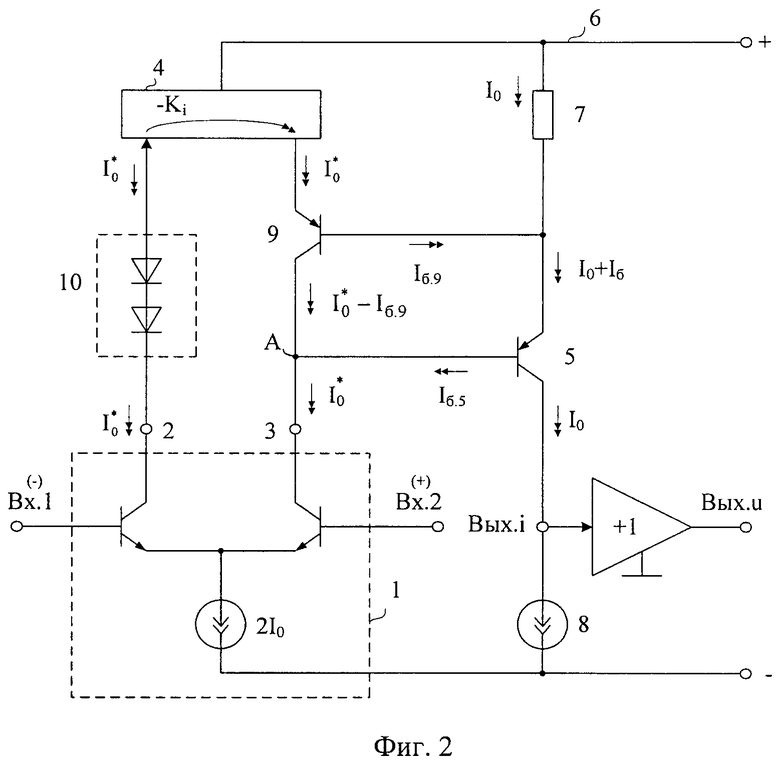

Поставленная цель достигается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, токовое зеркало 4, вход которого связан с первым 2 коллекторным выходом входного дифференциального каскада 1, выходной транзистор 5, база которого связана со вторым 3 коллекторным выходом входного дифференциального каскада 1, эмиттер связан с шиной 6 источника питания через первый 7 вспомогательный резистор, а коллектор соединен с цепью нагрузки 8, предусмотрены новые элементы и связи - в схему введены дополнительный транзистор 9 и цепь смещения потенциала 10, причем эмиттер дополнительного транзистора 9 связан с выходом токового зеркала 4, коллектор - подключен ко второму коллекторному выходу 3 входного дифференциального каскада 1, база - соединена с эмиттером выходного транзистора 5, а вход токового зеркала 4 связан с первым 2 коллекторным выходом входного дифференциального каскада 1 через цепь смещения потенциалов 10.

Схема усилителя-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

На чертеже фиг.3 показана схема ОУ-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.4 показана схема заявляемого устройства в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Прецизионный операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, токовое зеркало 4, вход которого связан с первым 2 коллекторным выходом входного дифференциального каскада 1, выходной транзистор 5, база которого связана со вторым 3 коллекторным выходом входного дифференциального каскада 1, эмиттер связан с шиной 6 источника питания через первый 7 вспомогательный резистор, а коллектор соединен с цепью нагрузки 8. В схему введены дополнительный транзистор 9 и цепь смещения потенциала 10, причем эмиттер дополнительного транзистора 9 связан с выходом токового зеркала 4, коллектор - подключен ко второму коллекторному выходу 3 входного дифференциального каскада 1, база -соединена с эмиттером выходного транзистора 5, а вход токового зеркала 4 связан с первым 2 коллекторным выходом входного дифференциального каскада 1 через цепь смещения потенциалов 10.

В качестве токового зеркала рекомендуется использовать повторители тока Вильсона и другие подсхемы, имеющие малую погрешность передачи входного токового сигнала.

Рассмотрим основные токовые соотношения для схемы фиг.2.

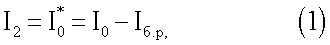

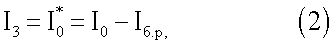

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 1 равен 2I0, то токи выходов 2 и 3

где Iб.р - ток базы входного n-р-n транзистора ДУ1.

Учитывая, что коэффициент передачи по току токового зеркала 4 (например, схемы Вильсона) равен единице (Ki=1), можно найти ток эмиттера (Iэ9) и ток коллектора (Iк9) транзистора 9

где Iб.9 - ток базы транзистора 9.

Следовательно, сумма токов в узле «А»

или

где Iб.5 - ток базы транзистора 5.

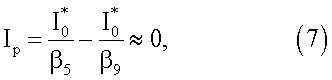

Уравнение (6) можно представить в виде

где β5≈β9=20-50 - коэффициент усиления по току базы транзисторов 5 и 9.

Вследствие воздействия радиации β5 и β9 изменяются в несколько раз, однако и в этом случае Ip≈0.

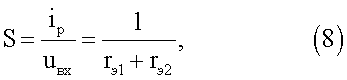

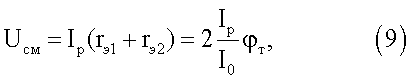

Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного напряжения uвx ДУ фиг.2 в выходной ток узла «А»

где rэ1=rэ2 - сопротивления эмиттерных переходов входных транзисторов дифференциального каскада 1.

Поэтому для схем фиг.2

где φт - температурный потенциал.

В ДУ-прототипе Ip≠0, поэтому здесь систематическая составляющая Uсм получается на порядок больше (фиг.3, Uсм=1,08 мВ), чем в заявляемой схеме (фиг.4, Uсм=86 мкВ).

Таким образом, заявляемое устройство имеет существенное преимущество в сравнении с прототипом.

Источники информации

1. Патент США №4.410.859, fig.1.

2. Патент США №4.721.920.

3. Патент США №4.783.637.

4. А.св. СССР №678639.

5. Патент США №4.560.948.

6. А.св. №1193773.

7. Патент США №4.463.319.

8. Патент W003/063344A1.

9. Патент США №5.343.164.

10. Патент США №4.417.216.

11. Патент США №5.365.191, fig.7.

12. Патент США №4.163.908

13. Патент Японии №54-37561, fig.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402156C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390916C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416151C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402870C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2446555C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412531C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2402151C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412540C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях с малыми значениями эдс смещения нуля и его дрейфа в условиях воздействия температуры и радиации). Технический результат: уменьшение напряжения смещения. Операционный усилитель (ОУ) содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) коллекторными выходами, токовое зеркало (4), вход которого связан с первым (2) коллекторным выходом входного ДК (1), выходной транзистор (Т) (5), база которого связана со вторым (3) коллекторным выходом входного ДК (1), эмиттер - связан с шиной (6) источника питания через первый (7) вспомогательный резистор, а коллектор - соединен с цепью нагрузки (8). В схему введены дополнительный Т (9) и цепь смещения потенциала (10), причем эмиттер дополнительного Т (9) связан с выходом токового зеркала (4), коллектор - подключен ко второму коллекторному выходу (3) входного ДК (1), база - соединена с эмиттером выходного Т (5), а вход токового зеркала (4) связан с первым (2) коллекторным выходом входного ДК (1) через цепь смещения потенциалов (10). 4 ил.

Прецизионный операционный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) коллекторными выходами, токовое зеркало (4), вход которого связан с первым (2) коллекторным выходом входного дифференциального каскада (1), выходной транзистор (5), база которого связана со вторым (3) коллекторным выходом входного дифференциального каскада (1), эмиттер связан с шиной (6) источника питания через первый (7) вспомогательный резистор, а коллектор соединен с цепью нагрузки (8), отличающийся тем, что в схему введен дополнительный транзистор (9) и цепь смещения потенциала (10), причем эмиттер дополнительного транзистора (9) связан с выходом токового зеркала (4), коллектор подключен ко второму коллекторному выходу (3) входного дифференциального каскада (1), база соединена с эмиттером выходного транзистора (5), а вход токового зеркала (4) связан с первым (2) коллекторным выходом входного дифференциального каскада (1) через цепь смещения потенциалов (10).

| US 4410859 A, 18.10.1983 | |||

| RU 2070768 C1, 20.12.1996 | |||

| US 4595883 A, 17.06.1986 | |||

| US 6114904 A, 05.09.2000. |

Авторы

Даты

2010-05-27—Публикация

2009-01-29—Подача