Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах).

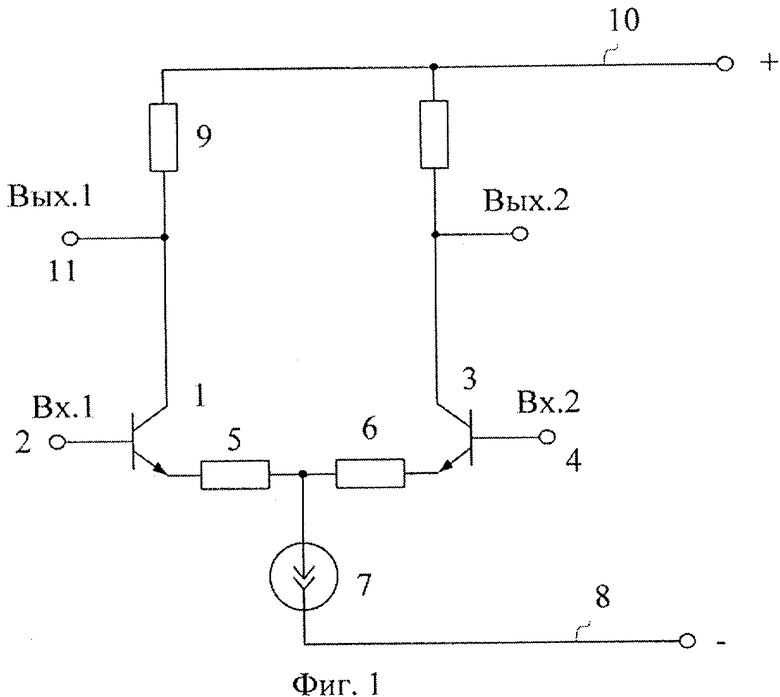

В современной микроэлектронике широко применяются простейшие дифференциальные усилители (ДУ) (фиг.1), которые используются в качестве элементов эмиттерно-связанной логики, драйверов линий связи, элементарных операционных усилителей и фильтров на их основе. Коэффициент усиления по напряжению (Ky) таких ДУ зависит, прежде всего, от сопротивлений резисторов в коллекторной цепи входных транзисторов.

При использовании SiGe технологических процессов напряжение питания ДУ не должно превышать 1,5÷2,5 В, что накладывает существенные ограничения на величину сопротивления коллекторных резисторов, которые не должны превышать единиц килоом.

Наиболее близким по технической сущности к заявляемому устройству является ДУ (фиг.1), рассмотренный в патенте США фирмы Analog Devices № 5.530.444 fig.1. Он содержит первый 1 входной транзистор, база которого соединена с инвертирующим входом 2 устройства, второй 3 входной транзистор, база которого соединена с неинвертирующим входом 4 устройства, первый 5 и второй 6 вспомогательные двухполюсники, первые выводы которых соединены с эмиттерами соответствующих первого 1 и второго 3 входных транзисторов, источник опорного тока 7, первый вывод которого соединен с первым 8 источником напряжения питания, двухполюсник нагрузки 9, включенный между вторым 10 источником напряжения питания и коллектором первого 1 входного транзистора, который соединен с выходом устройства 11.

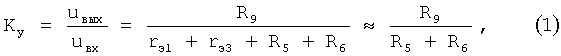

Существенный недостаток известного ДУ фиг.1, который также присутствует в патентах [2-1.7], состоит в том, что при реализации двухполюсника нагрузки 9 в виде низкоомного резистора его коэффициент усиления по напряжению (Ky) получается небольшим. Если учесть сопротивления вспомогательных двухполюсников 5 и 6, то коэффициент усиления по напряжению ДУ-прототипа по основному выходу будет определяться по формуле

где R9 - сопротивление двухполюсника нагрузки 9;

R5, R6 - сопротивления первого 5 и второго 6 вспомогательных двухполюсников;

rэi<<R5=R6 - сопротивление эмиттерного перехода i-го транзистора.

Например, при R9=1 кОм и R5=R6=500 Ом, коэффициент усиления ДУ-прототипа Ky≈1.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления по напряжению при использовании сравнительно низкоомных резисторов нагрузки (например, R9=1÷2 кОм) в условиях технологических ограничений SGB25VD-технологии на напряжения питания (±1,9÷2 В).

Поставленная задача достигается тем, что в дифференциальном усилителе, фиг.1, содержащем первый 1 входной транзистор, база которого соединена с инвертирующим входом 2 устройства, второй 3 входной транзистор, база которого соединена с неинвертирующим входом 4 устройства, первый 5 и второй 6 вспомогательные двухполюсники, первые выводы которых соединены с эмиттерами соответствующих первого 1 и второго 3 входных транзисторов, источник опорного тока 7, первый вывод которого соединен с первым 8 источником напряжения питания, двухполюсник нагрузки 9, включенный между вторым 10 источником напряжения питания и коллектором первого 1 входного транзистора, который соединен с выходом устройства 11, предусмотрены новые элементы и связи - в схему введено токовое зеркало 12 и дополнительный буферный усилитель 13, базовый вход токового зеркала 12 соединен со вторым выводом первого 5 вспомогательного двухполюсника, токовый выход токового зеркала 12 подключен ко второму выводу второго 6 вспомогательного двухполюсника и входу дополнительного буферного усилителя 1.3, причем выход дополнительного буферного усилителя 13 соединен с эмиттерным выходом токового зеркала 12 и вторым выводом источника опорного тока 7, а коллектор второго 3 входного транзистора соединен с выходом 11 устройства.

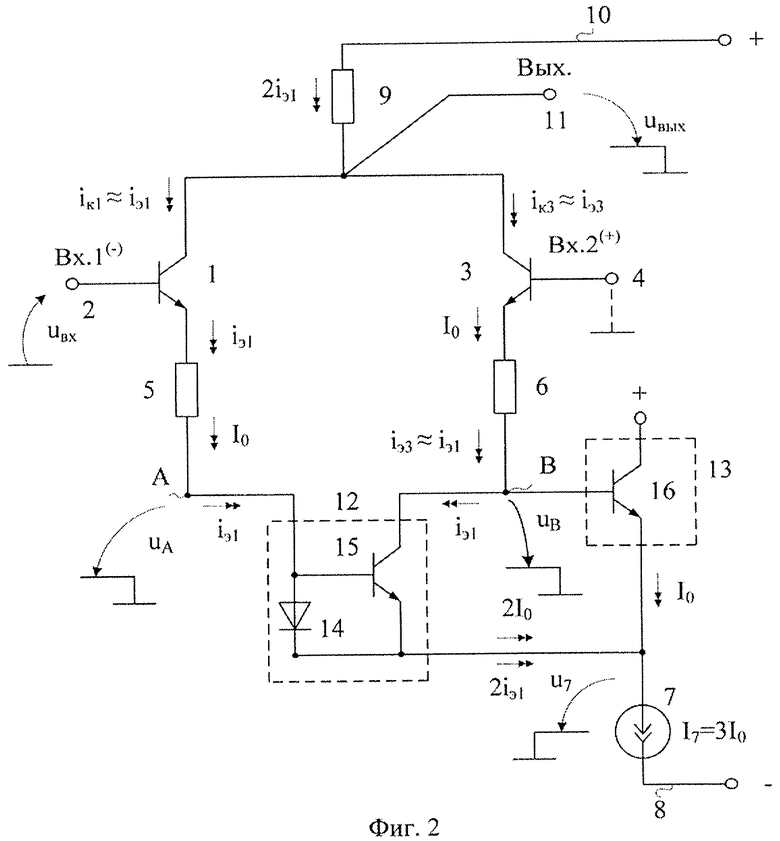

Схема заявляемого устройства, соответствующего п.1, п.2 и п.3 формулы изобретения, показана на фиг.2.

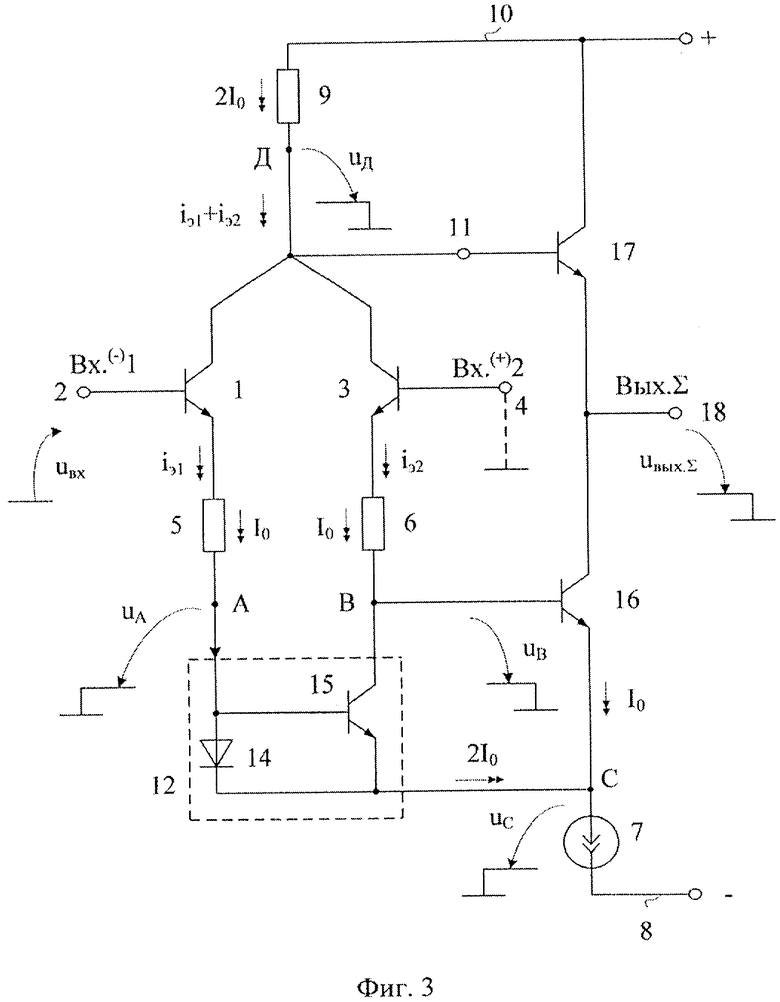

На фиг.3 показана схема ДУ, соответствующая п.4 формулы изобретения.

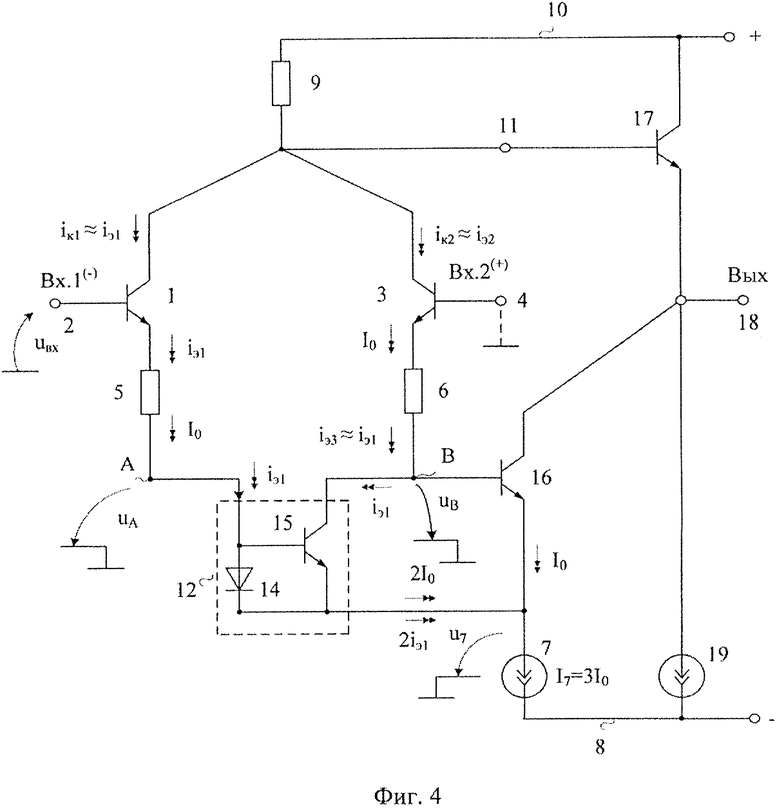

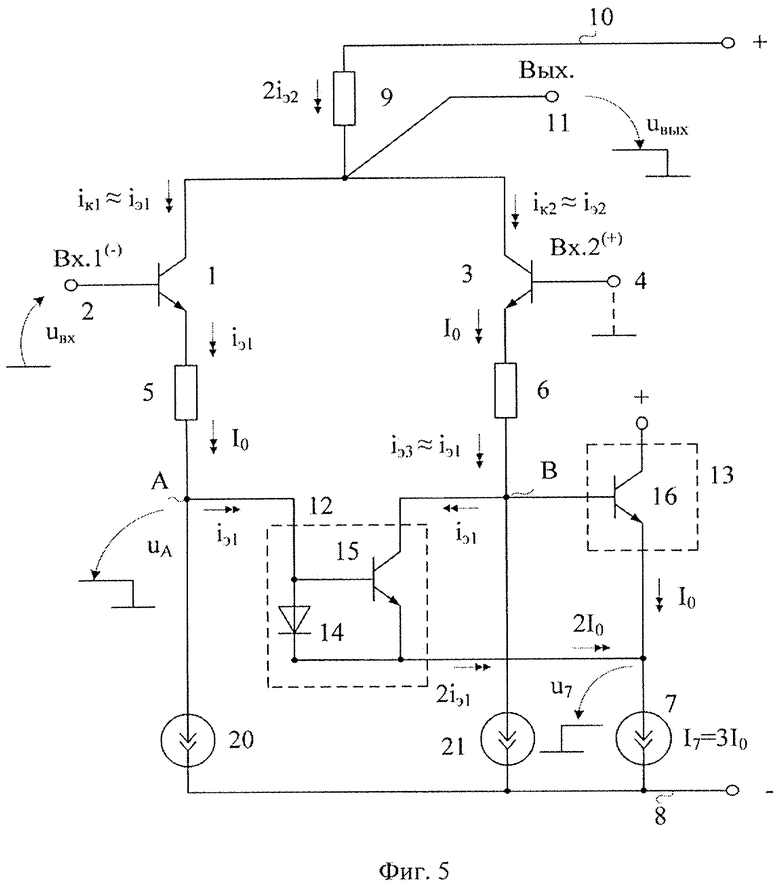

На фиг.4 представлена схема ДУ, соответствующая п.5, а на фиг.5 - п.6 формулы изобретения

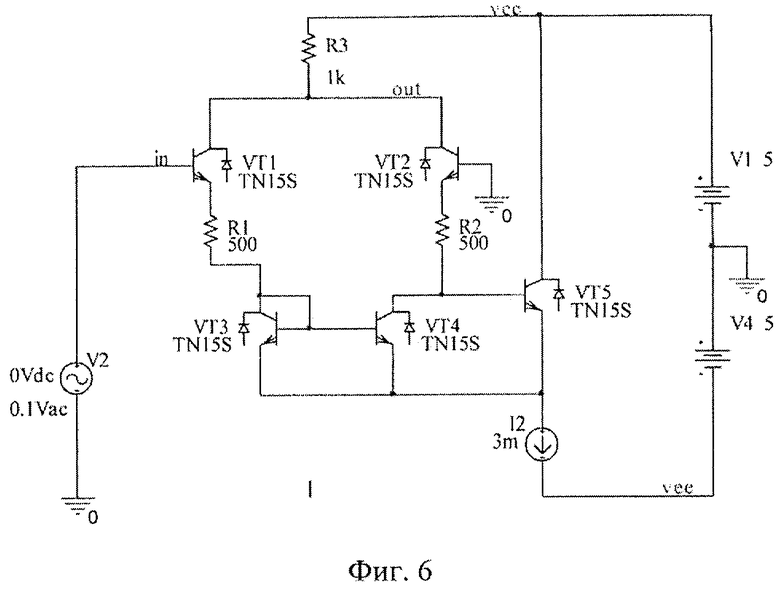

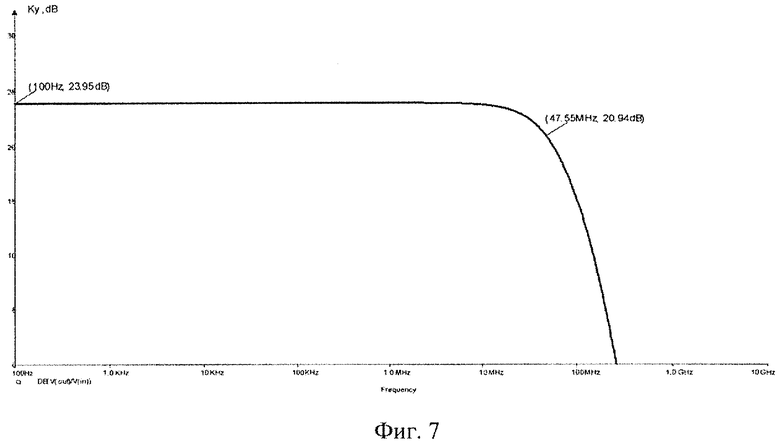

На фиг.6 показана схема ДУ фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.7 - частотная зависимость его коэффициента усиления по напряжению. Данные графики показывают, что, несмотря на применение низкоомной нагрузки (R9=R3=1 кОм), коэффициент усиления по напряжению ДУ (фиг.6) существенно улучшается в сравнении с Ky ДУ-прототипа фиг.1. Это важное достоинство предлагаемого ДУ при его реализации в рамках перспективного технологического процесса SGB25VD.

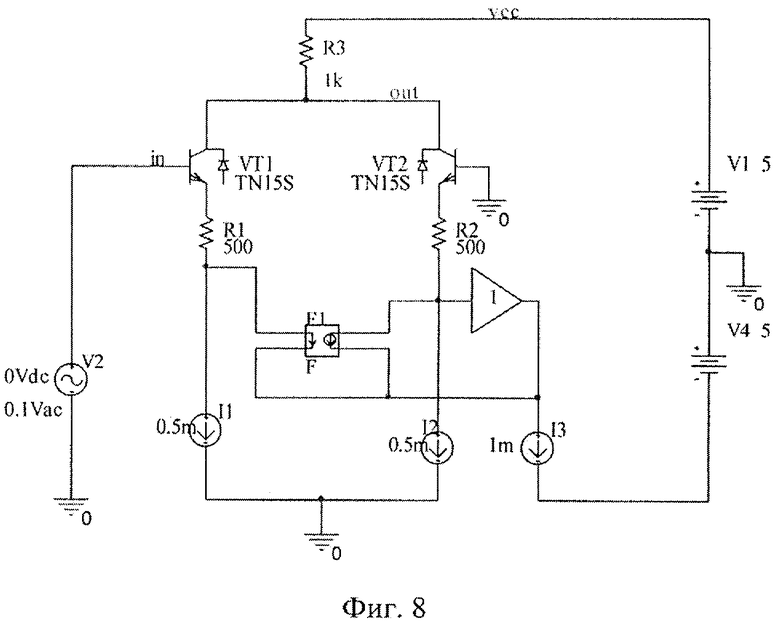

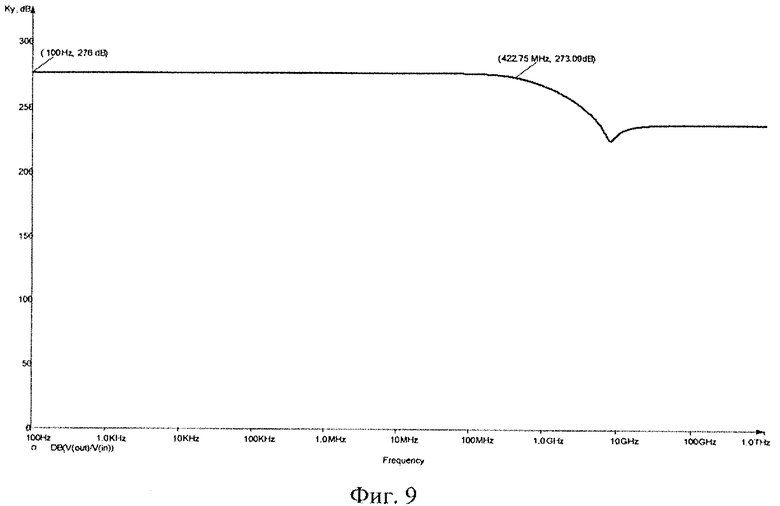

На фиг.8 показана схема ДУ фиг.5 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда токовое зеркало 12 (F1) и буферный усилитель (13) идеальны. На фиг.9 представлена частотная зависимость коэффициента усиления по напряжению ДУ фиг.8. Данные графики показывают, что, несмотря на применение низкоомной нагрузки (R9=1 кОм), коэффициент усиления по напряжению ДУ (фиг.8) улучшается на несколько порядков.

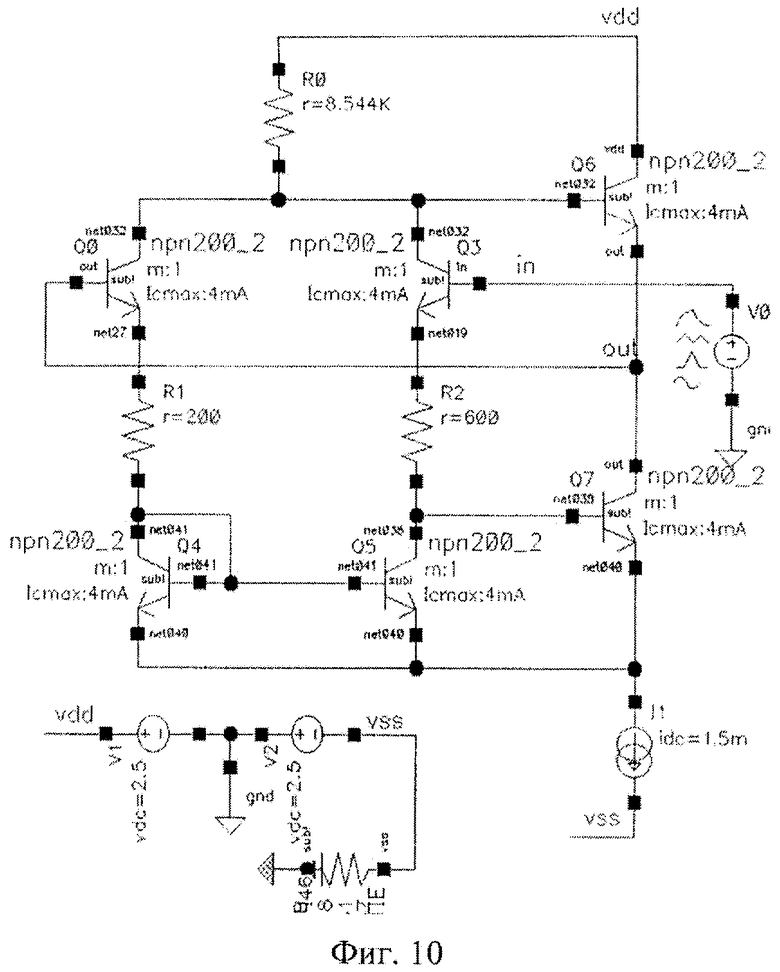

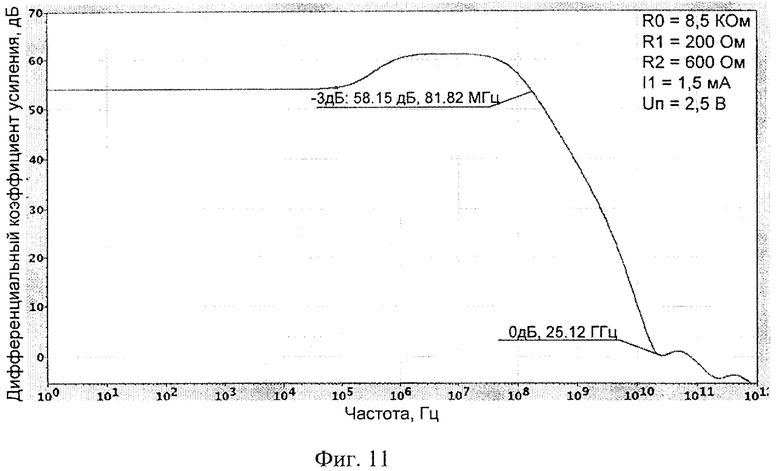

На фиг.10 показана схема ДУ фиг.3 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на фиг.11 - частотная зависимость его коэффициента усиления по напряжению. Данные графики показывают, что, несмотря на применение сравнительно низкоомной нагрузки (R0=8,5 кОм), коэффициент усиления по напряжению предлагаемого ДУ улучшается в сравнении с Ky ДУ фиг.1 на несколько порядков. Это - важное достоинство предлагаемого ДУ при его реализации в рамках технологического процесса SGB25VD.

Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению фиг.2 содержит первый 1 входной транзистор, база которого соединена с инвертирующим входом 2 устройства, второй 3 входной транзистор, база которого соединена с неинвертирующим входом 4 устройства, первый 5 и второй 6 вспомогательные двухполюсники, первые выводы которых соединены с эмиттерами соответствующих первого 1 и второго 3 входных транзисторов, источник опорного тока 7, первый вывод которого соединен с первым 8 источником напряжения питания, двухполюсник нагрузки 9, включенный между вторым 10 источником напряжения питания и коллектором первого 1 входного транзистора, который соединен с выходом устройства 11. В схему введено токовое зеркало 12 и дополнительный буферный усилитель 13, базовый вход токового зеркала 12 соединен со вторым выводом первого 5 вспомогательного двухполюсника, токовый выход токового зеркала 12 подключен ко второму выводу второго 6 вспомогательного двухполюсника и входу дополнительного буферного усилителя 13, причем выход дополнительного буферного усилителя 13 соединен с эмиттерным выходом токового зеркала 12 и вторым выводом источника опорного тока 7, а коллектор второго 3 входного транзистора соединен с выходом 11 устройства.

Кроме этого, на фиг.2 в соответствии с п.2 формулы изобретения токовое зеркало 12 содержит первый 14 p-n переход, первый вывод которого подключен ко входу токового зеркала 12 и базе дополнительного транзистора 1.5, а второй вывод соединен с эмиттером дополнительного транзистора 15 и токовым выходом токового зеркала 12.

Далее, на фиг.2 в соответствии с п.3 формулы изобретения дополнительный буферный усилитель 13 содержит входной транзистор 16, эмиттер которого является выходом дополнительного буферного усилителя 13, а база - его входом.

На фиг.3 в соответствии с п.4 формулы изобретения основной выход (11) устройства соединен с базой дополнительного транзистора (17), эмиттер которого связан с коллектором входного транзистора (16) буферного усилителя (13) и дополнительным выходом устройства (18), а коллектор подключен ко второму (10) источнику напряжения питания.

На фиг.4 в соответствии с п.5 формулы изобретения между дополнительным выходом устройства (18) и первым (8) источником напряжения питания включен симметрирующий двухполюсник (19).

На фиг.5 в соответствии с п.6 формулы изобретения между входом токового зеркала (12) и первым (8) источником напряжения питания включен первый (20) дополнительный двухполюсник, а между токовым выходом токового зеркала (12) и первым (8) источником напряжения питания включен второй (21) дополнительный двухполюсник.

Рассмотрим работу предлагаемого устройства фиг.2.

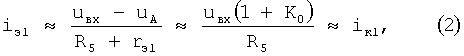

Если на вход 2 ДУ фиг.2 подается положительное приращение напряжения uвх, то это вызывает увеличение эмиттерного и коллекторного токов транзистора 1

где rэ1<<R5=R6 - сопротивление эмиттерного перехода транзистора 1;

R5=R6 - сопротивление двухполюсника 5(6);

K0>>1 - коэффициент передачи по напряжению со входа 2 в цепь эмиттера транзистора 16.

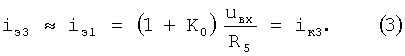

Приращение iэ1 поступает на вход токового зеркала 12, выходной ток которого iвых=iэ1, а затем в двухполюсник 6, эмиттер и далее коллектор транзистора 3:

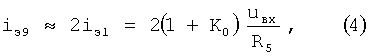

Поэтому через двухполюсник 9 будет протекать переменный ток 19, который создает выходное напряжение uвых:

Следовательно, коэффициент усиления по напряжению ДУ фиг.2

Численные значения K0 определяются различием сопротивлений двухполюсников 5 и 6 друг от друга, а также зависят от «идеальности» токового зеркала 12 и буферного усилителя 13. В практических схемах K0=50÷1000, что дает повышение Ky более чем на порядок. Данные выводы подтверждаются результатами компьютерного моделирования схем фиг.6 (фиг.7), фиг.8 (фиг.9) и фиг.10 (фиг.11).

Анализ графиков фиг.9 показывает, что Ky заявляемого устройства с идеальным токовым зеркалом (Ki=1) и буферным усилителем (Kп=1) может достигать значений более чем 120 дБ (106). В большинстве случаев этого достаточно для его многих применений.

В реальных схемах с типовым токовым зеркалом Ky≈103 (фиг.11). За счет специального построения токового зеркала, например, по схеме Вильсона и более прецизионных буферных усилителей можно получить Ky=104÷105.

Следует отметить, что на основе предлагаемого ДУ легко реализуются операционные усилители с коэффициентом усиления Ky≈103÷106, достаточным для многих применений (фиг.6). При этом все транзисторы ДУ могут иметь один тип проводимости (например, n-p-n), а схема ДУ выполняется с использованием SiGe техпроцессов (SGB25VD), внедряемых на российских предприятиях.

Таким образом, предлагаемое устройство имеет существенные преимущества по сравнению с прототипом.

Библиографический список

1. Патент США № 5.530.444 fig.1.

2. Патент WO 96/21271.

3. Патентная заявка США 2007/0146070 fig.3.

4. Патент WO 2000/038315.

5. Патент ФРГ 2928841 fig.4.

6. Патент Японии JP 55030218.

7. Патент WO 00/13309 fig.2.

8. Патентная заявка США 2009/0295480 fig.3.

9. Патент СА 02072436 fig.2.

10. Патентная заявка США 2005/0225390.

11. Патент США № 4.689.579 fig.6.

12. Патент США 4.703.284.

13. Патент США 4.586.000.

14. Патент США 4.703.284 fig.1.

15. Патент США 4.439.696 fig.2.

16. Патент США 5.115.409 fig.2.

17. Патент США 5.550.512 fig.3.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2463703C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2394362C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2009 |

|

RU2416154C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2419191C1 |

Изобретение относится к радиотехнике и связи для усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах). Технический результат: повышение коэффициента усиления по напряжению при использовании сравнительно низкоомных резисторов нагрузки (например, R9=1÷2 кОм) в условиях технологических ограничений SGB25VD-технологии на напряжения питания (±1,9÷2 В). Дифференциальный усилитель содержит первый (1) входной транзистор (Т), база которого соединена с инвертирующим входом (2) устройства, второй входной Т (3), база которого соединена с неинвертирующим входом (4) устройства, первый (5) и второй (6) вспомогательные двухполюсники (ДП), первые выводы которых соединены с эмиттерами соответствующих Т (1) и Т (3), источник опорного тока (ИОТ) (7), первый вывод которого соединен с первым (8) источником напряжения питания (ИП), ДП нагрузки (9), включенный между вторым (10) ИП и коллектором Т (1), который соединен с выходом устройства (11). В схему введено токовое зеркало (ТЗ) (12) и дополнительный буферный усилитель (БУ) (13), базовый вход ТЗ (12) соединен со вторым выводом ДП (5), токовый выход ТЗ (12) подключен ко второму выводу ДП (6) и входу БУ (13), причем выход БУ (13) соединен с эмиттерным выходом ТЗ (12) и вторым выводом ИОТ (7), а коллектор Т (3) соединен с выходом 11 устройства. 5 з.п. ф-лы, 11 ил.

1. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению, содержащий первый (1) входной транзистор, база которого соединена с инвертирующим входом (2) устройства, второй (3) входной транзистор, база которого соединена с неинвертирующим входом (4) устройства, первый (5) и второй (6) вспомогательные двухполюсники, первые выводы которых соединены с эмиттерами соответствующих первого (1) и второго (3) входных транзисторов, источник опорного тока (7), первый вывод которого соединен с первым (8) источником напряжения питания, двухполюсник нагрузки (9), включенный между вторым (10) источником напряжения питания и коллектором первого (1) входного транзистора, который соединен с выходом устройства (11), отличающийся тем, что в схему введено токовое зеркало (12) и дополнительный буферный усилитель (13), базовый вход токового зеркала (12) соединен со вторым выводом первого (5) вспомогательного двухполюсника, токовый выход токового зеркала (12) подключен ко второму выводу второго (6) вспомогательного двухполюсника и входу дополнительного буферного усилителя (13), причем выход дополнительного буферного усилителя (13) соединен с эмиттерным выходом токового зеркала (12) и вторым выводом источника опорного тока (7), а коллектор второго (3) входного транзистора соединен с выходом (11) устройства.

2. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению по п.1, отличающийся тем, что токовое зеркало (12) содержит первый (14) p-n переход, первый вывод которого подключен ко входу токового зеркала (12) и базе дополнительного транзистора (15), а второй вывод соединен с эмиттером дополнительного транзистора (15) и токовым выходом токового зеркала (12).

3. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению по п.2, отличающийся тем, что дополнительный буферный усилитель (13) содержит входной транзистор (16), эмиттер которого является выходом дополнительного буферного усилителя (13), а база - его входом.

4. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению по п.3, отличающийся тем, что основной выход (11) устройства соединен с базой дополнительного транзистора (17), эмиттер которого связан с коллектором входного транзистора (16) буферного усилителя (13) и дополнительным выходом устройства (18), а коллектор подключен ко второму (10) источнику напряжения питания.

5. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению по п.4, отличающийся тем, что между дополнительным выходом устройства (18) и первым (8) источником напряжения питания включен симметрирующий двухполюсник (19).

6. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению по п.1, отличающийся тем, что между входом токового зеркала (12) и первым (8) источником напряжения питания включен первый (20) дополнительный двухполюсник, а между токовым выходом токового зеркала (12) и первым (8) источником напряжения питания включен второй (21) дополнительный двухполюсник.

| US 5530444 А, 25.06.1996 | |||

| Стабилизатор постоянного напряжения | 1981 |

|

SU987605A1 |

| US 6114904 А, 05.09.2000 | |||

| ОРЛОВ А | |||

| УМЗЧ с однокаскадным усилением напряжения | |||

| - Радио, №12, 1997, с.14, рис.1. | |||

Авторы

Даты

2011-05-20—Публикация

2010-02-04—Подача