Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ и СВЧ-усилителях переменного тока и т.п.).

В современной микроэлектронике находят применение классические усилители переменного тока на основе дифференциальных усилителей (ДУ) с двумя резисторами в коллекторной цепи выходных транзисторов [1-17]. Данная архитектура является основой широкого класса IP-модулей систем связи и является базовой как для существующих, так и для принципиально новых нанотехнологий [10].

Наиболее близким по технической сущности к заявляемому устройству является входной дифференциальный каскад в устройстве по заявке US 2009/0221259 фиг.13.

Существенный недостаток известного ДУ, архитектура которого присутствует также во многих других усилительных каскадах [1-17], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еn≤2,0÷2,5 В), его коэффициент усиления по напряжению (Ку) получается небольшим (Кymax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании и работе с переменными сигналами ВЧ и СВЧ диапазонов.

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первую 4 шину источников питания, связанную с эмиттерной цепью входного дифференциального каскада 1, первый 5 резистор коллекторной нагрузки, первый вывод которого соединен с первым 6 выходом устройства и первым 2 токовым выходом входного дифференциального каскада 1, второй 7 резистор коллекторной нагрузки, первый вывод которого подключен ко второму 8 выходу устройства и второму 3 токовому выходу входного дифференциального каскада 1, вторую 9 шину источников питания, предусмотрены новые элементы и связи - второй вывод первого 5 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через первый 10 дополнительный двухполюсник и через первый 11 корректирующий конденсатор подключен ко входу первого 12 дополнительного инвертирующего повторителя тока, второй вывод второго 7 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через второй 13 дополнительный двухполюсник и через второй 14 корректирующий конденсатор подключен ко входу второго 15 дополнительного инвертирующего повторителя тока, выход первого 12 дополнительного инвертирующего повторителя тока подключен ко второму 3 токовому выходу входного дифференциального каскада 1, выход второго 15 дополнительного инвертирующего повторителя тока подключен к первому 2 токовому выходу входного дифференциального каскада 1, причем общие эмиттерные выходы первого 12 и второго 15 дополнительных инвертирующих повторителей тока связаны с первой 4 шиной источников питания.

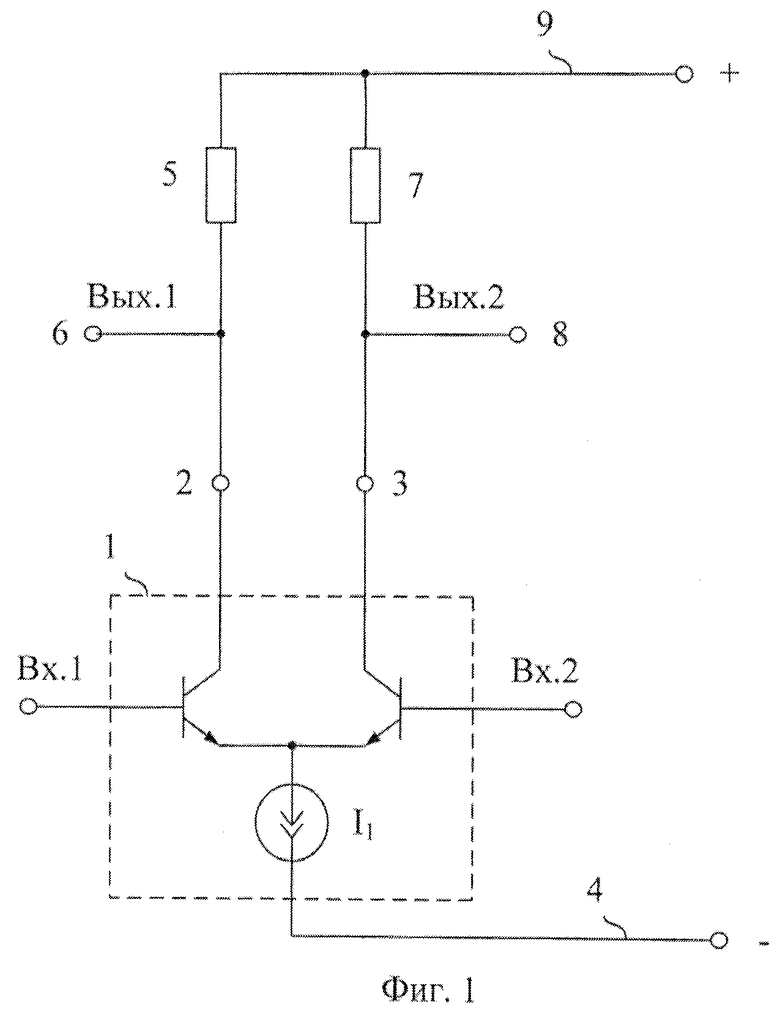

На фиг.1 показана схема ДУ-прототипа.

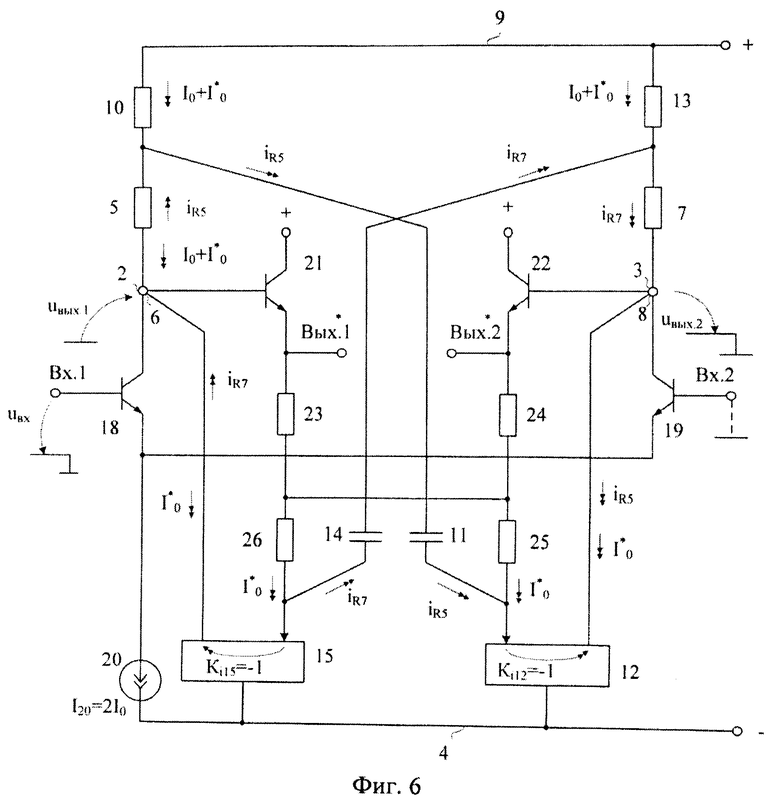

Схема заявляемого устройства, соответствующего п.1 и п.2 формулы изобретения, показана на фиг.2.

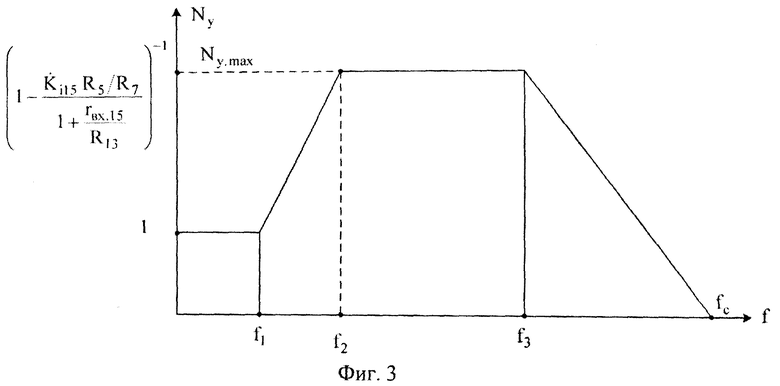

На фиг.3 показан теоретический график зависимости относительного коэффициента усиления Ny ДУ фиг.2 от частоты.

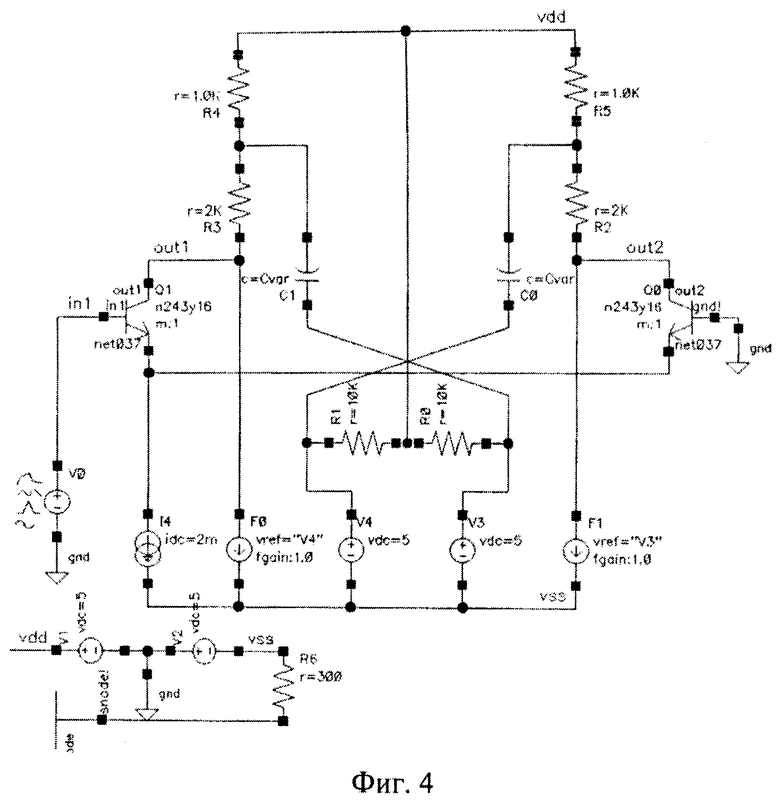

На фиг.4 представлена схема ДУ-прототипа фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW.

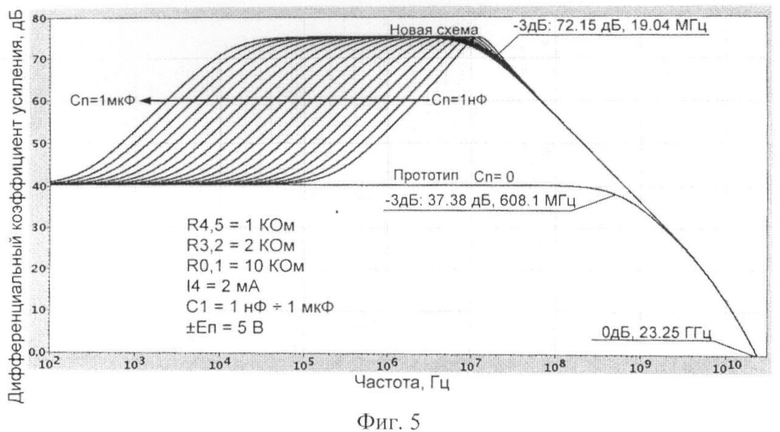

Графики фиг.5 характеризуют частотную зависимость коэффициента

усиления по напряжению (Ку) ДУ фиг, 4 от численных значений емкости, корректирующих конденсаторов С0=C1.

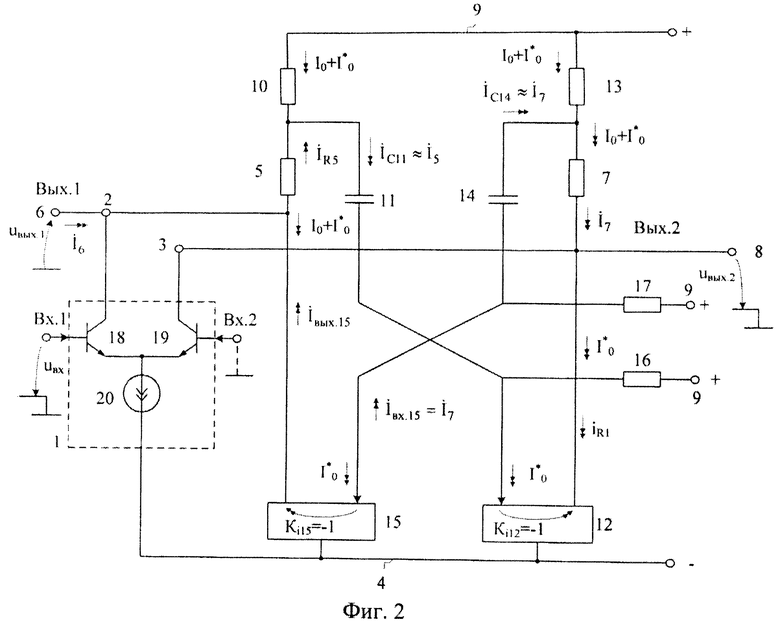

На фиг.6 представлена схема заявляемого ДУ с отрицательной обратной связью по синфазным сигналам в соответствии с п.3 формулы изобретения.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первую 4 шину источников питания, связанную с эмиттерной цепью входного дифференциального каскада 1, первый 5 резистор коллекторной нагрузки, первый вывод которого соединен с первым 6 выходом устройства и первым 2 токовым выходом входного дифференциального каскада 1, второй 7 резистор коллекторной нагрузки, первый вывод которого подключен ко второму 8 выходу устройства и второму 3 токовому выходу входного дифференциального каскада 1, вторую 9 шину источников питания. Второй вывод первого 5 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через первый 10 дополнительный двухполюсник и через первый 11 корректирующий конденсатор подключен ко входу первого 12 дополнительного инвертирующего повторителя тока, второй вывод второго 7 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через второй 13 дополнительный двухполюсник и через второй 14 корректирующий конденсатор подключен ко входу второго 15 дополнительного инвертирующего повторителя тока, выход первого 12 дополнительного инвертирующего повторителя тока подключен ко второму 3 токовому выходу входного дифференциального каскада 1, выход второго 15 дополнительного инвертирующего повторителя тока подключен к первому 2 токовому выходу входного дифференциального каскада 1, причем общие эмиттерные выходы первого 12 и второго 15 дополнительных инвертирующих повторителей тока связаны с первой 4 шиной источников питания.

Кроме этого на фиг.2, в соответствии с п.2 формулы изобретения, вход первого 12 дополнительного инвертирующего повторителя тока соединен со второй 9 шиной источников питания через первый вспомогательный резистор 16, а вход второго 15 дополнительного инвертирующего повторителя тока соединен со второй 9 шиной источников питания через второй вспомогательный резистор 17. В частном случае на фиг.2 входной дифференциальный каскад реализован на входных транзисторах 18, 19 и двухполюснике 20.

На фиг.6, в соответствии с п.3 формулы изобретения, в схему введены первый 21 и второй 22 вспомогательные транзисторы, базы которых соединены с соответствующими первым 2 и вторым 3 токовыми выходами входного дифференциального каскада 1, эмиттеры первого 21 и второго 22 вспомогательных транзисторов связаны друг с другом через последовательно соединенные первый 23 и второй 24 согласующие резисторы, общий узел которых связан со входом первого 12 дополнительного инвертирующего повторителя тока через третий 25 согласующий резистор и четвертый 26 согласующий резистор соединен со входом второго 15 дополнительного инвертирующего повторителя тока.

Статический режим ДУ фиг.2 устанавливается двухполюсником 20, также резисторами 16 и 17, которые задают начальный статический режим первого 12 и второго 15 дополнительных инвертирующих повторителей тока.

Рассмотрим работу ДУ фиг.2 на переменном токе.

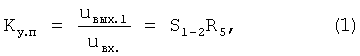

Предельный коэффициент усиления по напряжению входного дифференциального каскада ДУ фиг.2 при емкости конденсатора 11 (С11), равной нулю, и R5>>R10, определяется сопротивлением первого 5 резистора коллекторной нагрузки:

где S1-2=(rэ18+rэ19)-1 - крутизна усиления входного дифференциального каскада 1 в режиме короткого замыкания по его выходу, зависящая от сопротивлений эмиттерных переходов (rэ18, rэ19) транзисторов 18 и 19.

Покажем аналитически, что более высокие значения Ку в диапазоне средних частот, когда влиянием емкостей 11 и 14 на Ку реализуются в схеме фиг.2.

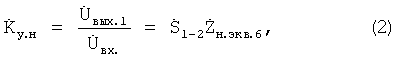

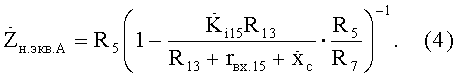

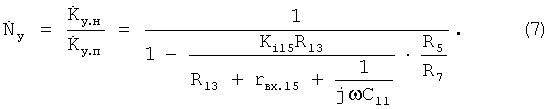

Действительно, комплексный коэффициент передачи по напряжению ДУ фиг.2 определяется по формуле:

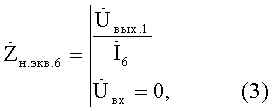

где  - комплекс эквивалентного выходного импеданса в цепи первого (6) выхода устройства;

- комплекс эквивалентного выходного импеданса в цепи первого (6) выхода устройства;

- комплексная крутизна входного дифференциального каскада 1 в режиме короткого замыкания его первого (6) выхода. Комплекс эквивалентной нагрузки

- комплексная крутизна входного дифференциального каскада 1 в режиме короткого замыкания его первого (6) выхода. Комплекс эквивалентной нагрузки  можно найти но формуле:

можно найти но формуле:

где  - выходной ток узла 6;

- выходной ток узла 6;

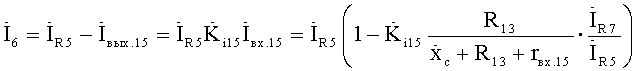

Причем,

,

,

- комплексы входного и выходного токов дополнительного инвертирующего повторителя тока 15;

- комплексы входного и выходного токов дополнительного инвертирующего повторителя тока 15;

- комплексы токов через двухполюсники 7 и 5;

- комплексы токов через двухполюсники 7 и 5;

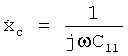

- комплекс импеданса первого 11 корректирующего конденсатора;

- комплекс импеданса первого 11 корректирующего конденсатора;

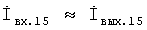

- коэффициент передачи по току второго 15 дополнительного инвертирующего повторителя тока и его входное сопротивление.

- коэффициент передачи по току второго 15 дополнительного инвертирующего повторителя тока и его входное сопротивление.

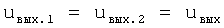

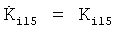

После преобразований последней формулы с учетом равенства

находим, что

находим, что

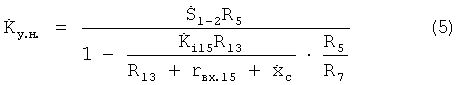

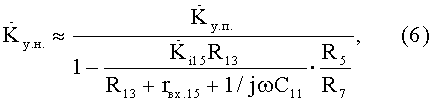

Поэтому комплекс коэффициента усиления по напряжению ДУ фиг.2

или при  :

:

где  - коэффициент усиления ДУ-прототипа (2).

- коэффициент усиления ДУ-прототипа (2).

Таким образом, выигрыш по Кy, который дает схема ДУ фиг.2

Если ω=0, то  В области средних частот, когда можно пренебречь влиянием С11:

В области средних частот, когда можно пренебречь влиянием С11:

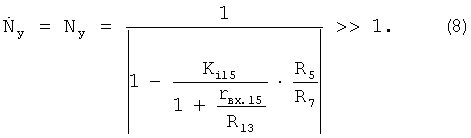

Из уравнения (8) следует ряд важных выводов:

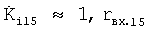

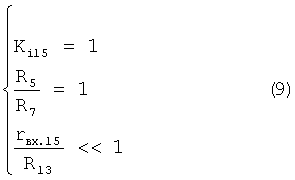

1. Во-первых, эффективность по Ку предлагаемого схемотехнического решения фиг.2 зависит от параметров: Кi15, R5/R7, rвх.15/R13;

2. Во-вторых, для получения максимального выигрыша по Ку необходимо выбирать:

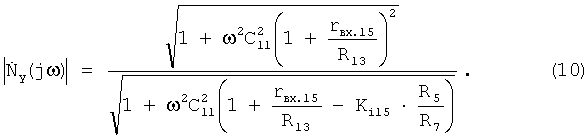

При этом модуль коэффициента  (8) ДУ фиг.2, характеризующего его эффективность:

(8) ДУ фиг.2, характеризующего его эффективность:

График функции  показан на фиг.3. Начиная с частоты f3, эффективность ДУ фиг.2 уменьшается в связи с уменьшением коэффициента Кi15, влиянием емкости коллектор-база транзисторов 18 и 19 и их емкостей на подложку.

показан на фиг.3. Начиная с частоты f3, эффективность ДУ фиг.2 уменьшается в связи с уменьшением коэффициента Кi15, влиянием емкости коллектор-база транзисторов 18 и 19 и их емкостей на подложку.

В схеме ДУ фиг.2 статический режим дополнительных инвертирующих повторителей тока 15 и 16 устанавливается двухполюсниками 16 и 17, которые в ряде случаев могут отсутствовать.

В схеме фиг.6 вводится общая отрицательная обратная связь по синфазному сигналу через дополнительные инвертирующие повторители тока 12 и 15. Кроме этого данная схема имеет низкоомные выходы Вых.1 и Вых. 2, что повышает устойчивость и стабильность статического режима ДУ при изменении параметров элементов.

График фиг.5, полученный в результате моделирования схемы фиг.4, соответствует фиг.3. Он показывает высокое совпадение теоретической (фиг.3) и практических характеристик. При этом выигрыш по Ку в диапазоне средних частот ДУ фиг.4, зависящем от численных значений емкостей коррекции С1=С0, достигает 35 дБ (т.е. почти два порядка).

Заявляемая схема особенно перспективна для использования в микроэлектронных СВЧ устройствах, реализуемых по техпроцессу SG25VD, не содержащем p-n-p транзисторов.

Источники информации

1. Патент США №3.541.464

2. Патентная заявка WO 2004/102789

3. Патент США №5.389.893

4. Патент Японии JP 53-142849

5. А.св. СССР 1102019

6. Патентная заявка WO 2005/077525

7. Патентная заявка США №2006/0181348

8. Патентная заявка WO 2006/077525

9. Патент Англии GB 2419052

10. Патентная заявка США №2008/0290941

11. Патент WO 96/21271

12. Патентная заявка США 2009/0108882 fig.3

13. Патент Японии JP 55030218

14. Патент Англии GB 1350352

15. Патент Японии JP 54-47467

16. Патент Японии JP 55099810

17. Патент ФРГ DE 2821942

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421895C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421892C1 |

| ДВУХКАНАЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2452078C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432667C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2468500C1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2427071C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2005 |

|

RU2282303C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421893C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ и СВЧ-усилителях переменного тока и т.п.). Технический результат: повышение предельных значений коэффициента усиления по напряжению дифференциального усилителя (ДУ) при низковольтном питании и работе с переменными сигналами ВЧ и СВЧ диапазонов. ДУ содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, первую (4) шину источников питания (ИП), связанную с эмиттерной цепью входного ДК (1), первый (5) резистор коллекторной нагрузки, первый вывод которого соединен с первым (6) выходом устройства и первым (2) токовым выходом входного ДК (1), второй (7) резистор коллекторной нагрузки, первый вывод которого подключен ко второму (8) выходу устройства и второму (3) токовому выходу входного ДК (1), вторую (9) шину ИП. Второй вывод первого (5) резистора коллекторной нагрузки соединен со второй (9) шиной ИП через первый (10) дополнительный двухполюсник и через первый (11) корректирующий конденсатор подключен ко входу первого (12) дополнительного инвертирующего повторителя тока (ИПТ), второй вывод второго (7) резистора коллекторной нагрузки соединен со второй (9) шиной ИП через второй (13) дополнительный двухполюсник и через второй (14) корректирующий конденсатор подключен ко входу второго (15) дополнительного ИПТ, выход первого (12) дополнительного ИПТ подключен ко второму (3) токовому выходу входного ДК (1), выход второго (15) дополнительного ИПТ подключен к первому (2) токовому выходу входного ДК (1), причем общие эмиттерные выходы первого (12) и второго (15) дополнительных ИПТ связаны с первой (4) шиной ИП. 2 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первую (4) шину источников питания, связанную с эмиттерной цепью входного дифференциального каскада (1), первый (5) резистор коллекторной нагрузки, первый вывод которого соединен с первым (6) выходом устройства и первым (2) токовым выходом входного дифференциального каскада (1), второй (7) резистор коллекторной нагрузки, первый вывод которого подключен ко второму (8) выходу устройства и второму (3) токовому выходу входного дифференциального каскада (1), вторую (9) шину источников питания, отличающийся тем, что второй вывод первого (5) резистора коллекторной нагрузки соединен со второй (9) шиной источников питания через первый (10) дополнительный двухполюсник и через первый (11) корректирующий конденсатор подключен ко входу первого (12) дополнительного инвертирующего повторителя тока, второй вывод второго (7) резистора коллекторной нагрузки соединен со второй (9) шиной источников питания через второй (13) дополнительный двухполюсник и через второй (14) корректирующий конденсатор подключен ко входу второго (15) дополнительного инвертирующего повторителя тока, выход первого (12) дополнительного инвертирующего повторителя тока подключен ко второму (3) токовому выходу входного дифференциального каскада (1), выход второго (15) дополнительного инвертирующего повторителя тока подключен к первому (2) токовому выходу входного дифференциального каскада (1), причем общие эмиттерные выходы первого (12) и второго (15) дополнительных инвертирующих повторителей тока связаны с первой (4) шиной источников питания.

2. Дифференциальный усилитель по п.1, отличающийся тем, что вход первого (12) дополнительного инвертирующего повторителя тока соединен со второй (9) шиной источников питания через первый вспомогательный резистор (16), а вход второго (15) дополнительного инвертирующего повторителя тока соединен со второй (9) шиной источников питания через второй вспомогательный резистор (17).

3. Дифференциальный усилитель по п.1, отличающийся тем, что в схему введены первый (21) и второй (22) вспомогательные транзисторы, базы которых соединены с соответствующими первым (2) и вторым (3) токовыми выходами входного дифференциального каскада (1), эмиттер первого (21) и второго (22) вспомогательных транзисторов связаны друг с другом через последовательно соединенные первый (23) и второй (24) согласующие резисторы, общий узел которых связан со входом первого (12) дополнительного инвертирующего повторителя тока через третий (25) согласующий резистор, и четвертый (26) согласующий резистор соединен со входом второго (15) дополнительного инвертирующего повторителя тока.

| Колосоуборка | 1923 |

|

SU2009A1 |

| Дифференциальный усилитель | 1982 |

|

SU1102019A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

2011-06-20—Публикация

2010-05-11—Подача