Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ и СВЧ-усилителях, фильтрах, драйверах линий связи и т.п.).

В современной микроэлектронике находят применение классические дифференциальные операционные усилители (ДУ) с двумя резисторами в коллекторной цепи выходных транзисторов [1-17]. Данная архитектура является основой широкого класса IP-модулей систем связи и является базовой как для существующих, так и для принципиально новых технологий [10].

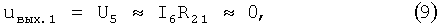

Наиболее близким по технической сущности к заявляемому устройству является дифференциальный усилитель по патенту US 6.285.245, фиг.1.

Существенный недостаток известного ДУ, архитектура которого присутствует также во многих других усилительных каскадах [1-17], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Кy) получается небольшим (Кymax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными. В то же время применение активных нагрузок на p-n-р транзисторах не всегда допускается.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании в рамках техпроцессов SGB25VD.

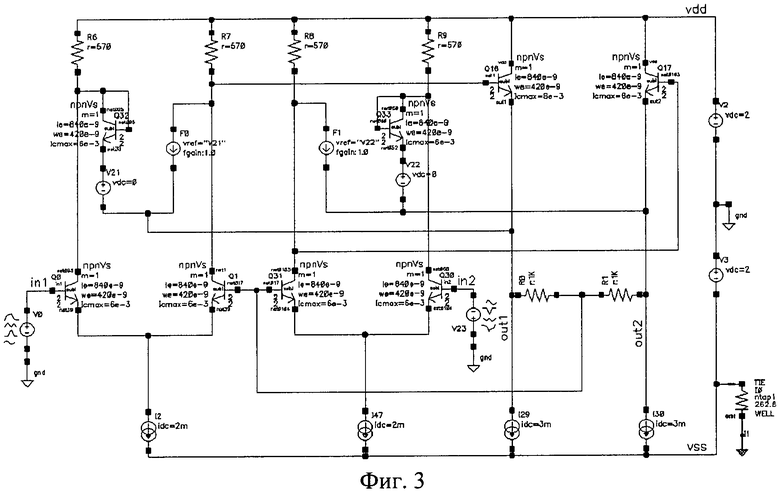

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, первый 3 и второй 4 выходные транзисторы, эмиттеры которых соединены с соответствующими первым 5 и вторым 6 парафазными выходами устройства и через первый 7 и второй 8 токостабилизирующие двухполюсники связаны с шиной первого 9 источника питания, первый 10 резистор коллекторной нагрузки, включенный между базой первого 3 выходного транзистора и шиной второго 11 источника питания, второй 12 резистор коллекторной нагрузки, включенный между базой второго 4 выходного транзистора и шиной второго 11 источника питания, третий 13 токостабилизирующий двухполюсник, включенный между эмиттером первого 1 входного транзистора и шиной первого 9 источника питания, причем коллекторы первого 3 и второго 4 выходных транзисторов соединены с шиной второго 11 источника питания, предусмотрены новые элементы и связи - коллектор первого 1 входного транзистора связан со входом первого 14 дополнительного токового зеркала и через третий 15 резистор коллекторной нагрузки соединен с шиной второго 11 источника питания, причем коллекторный выход первого 14 дополнительного токового зеркала связан с базой первого 3 выходного транзистора, а общий эмиттерный выход первого 14 дополнительного токового зеркала подключен к эмиттеру первого 3 выходного транзистора, коллектор второго 2 входного транзистора связан со входом второго 16 дополнительного токового зеркала и через четвертый 17 резистор коллекторной нагрузки соединен с шиной второго 11 источника питания, причем коллекторный выход второго 16 дополнительного токового зеркала связан с базой второго 4 выходного транзистора, а общий эмиттерный выход второго 16 дополнительного токового зеркала подключен к эмиттеру второго 4 выходного транзистора, эмиттер первого 1 входного транзистора соединен с эмиттером первого 18 дополнительного транзистора, эмиттер второго 2 входного транзистора соединен с эмиттером второго 19 дополнительного транзистора и через четвертый 20 токостабилизирующий двухполюсник соединен с шиной первого 9 источника питания, коллектор первого 18 дополнительного транзистора соединен с базой первого 3 выходного транзистора, коллектор второго 19 дополнительного транзистора соединен с базой второго 4 выходного транзистора, объединенные базы первого 18 и второго 19 дополнительных транзисторов связаны с эмиттером первого 3 выходного транзистора через первый 21 вспомогательный резистор и соединены с эмиттером второго 4 выходного транзистора через второй 22 вспомогательный резистор.

На фиг.1 показана схема ДУ-прототипа.

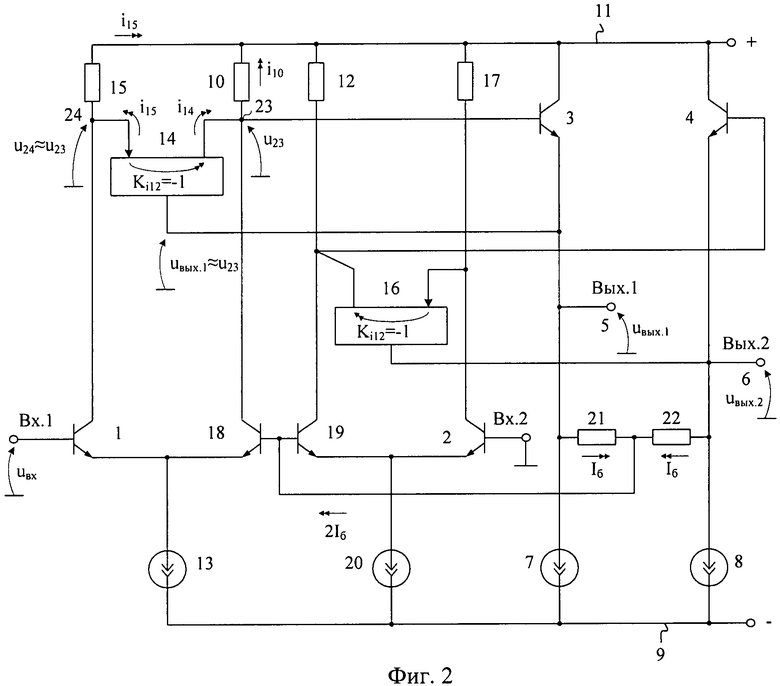

Схема заявляемого устройства, соответствующего формуле изобретения, показана на фиг.2.

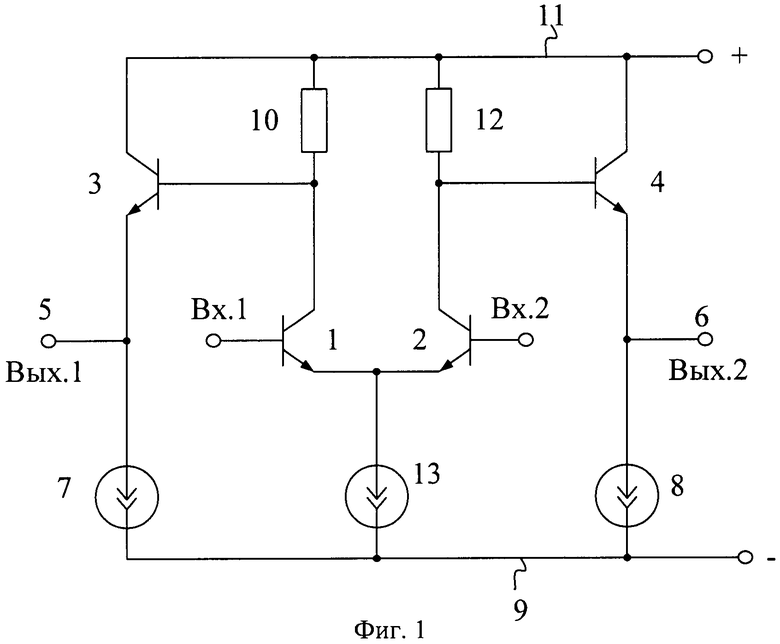

На фиг.3 представлена схема заявляемого ДУ фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных SiGe транзисторов.

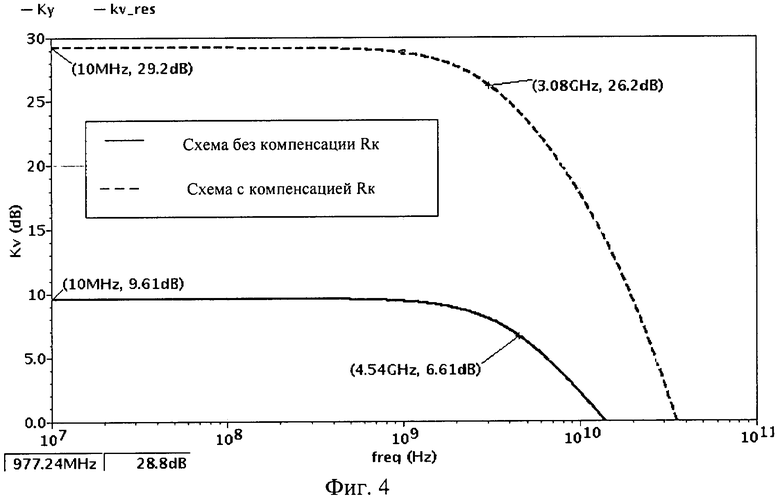

Графики фиг.4 характеризуют частотную зависимость коэффициента усиления по напряжению (Кy) сравниваемых ДУ фиг.1 и фиг.2 при сопротивления резисторов обратной связи (21, 22):R21=R22=R=200 Ом.

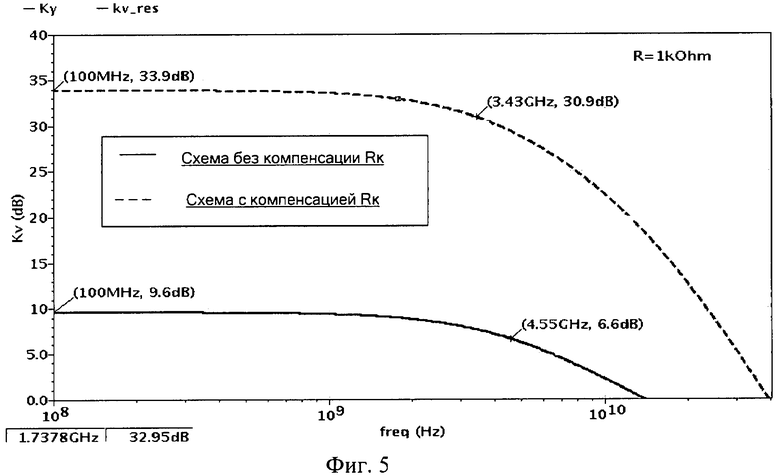

График фиг.5 характеризует частотную зависимость коэффициента усиления разомкнутого ДУ при R21=R22=R=1 кОм.

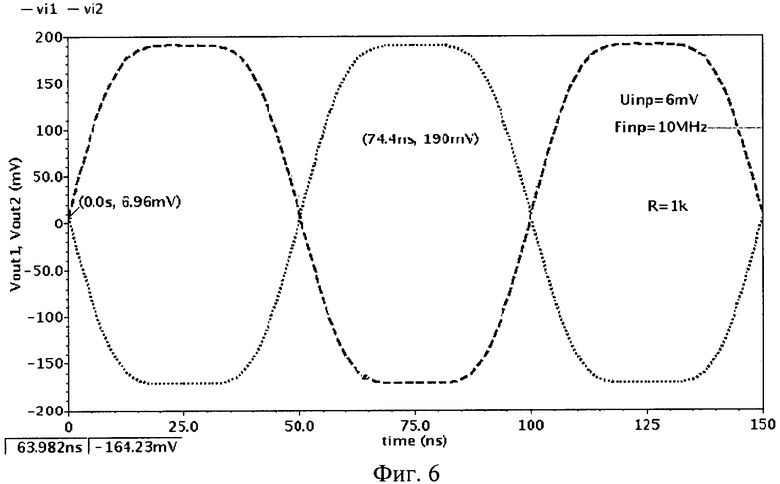

На фиг.6 показана зависимость выходного синусоидального напряжения ДУ фиг.3 при R21=R22=R=1 кОм.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, первый 3 и второй 4 выходные транзисторы, эмиттеры которых соединены с соответствующими первым 5 и вторым 6 парафазными выходами устройства и через первый 7 и второй 8 токостабилизирующие двухполюсники связаны с шиной первого 9 источника питания, первый 10 резистор коллекторной нагрузки, включенный между базой первого 3 выходного транзистора и шиной второго 11 источника питания, второй 12 резистор коллекторной нагрузки, включенный между базой второго 4 выходного транзистора и шиной второго 11 источника питания, третий 13 токостабилизирующий двухполюсник, включенный между эмиттером первого 1 входного транзистора и шиной первого 9 источника питания, причем коллекторы первого 3 и второго 4 выходных транзисторов соединены с шиной второго 11 источника питания, отличается тем, что коллектор первого 1 входного транзистора связан со входом первого 14 дополнительного токового зеркала и через третий 15 резистор коллекторной нагрузки соединен с шиной второго 11 источника питания, причем коллекторный выход первого 14 дополнительного токового зеркала связан с базой первого 3 выходного транзистора, а общий эмиттерный выход первого 14 дополнительного токового зеркала подключен к эмиттеру первого 3 выходного транзистора, коллектор второго 2 входного транзистора связан со входом второго 16 дополнительного токового зеркала и через четвертый 17 резистор коллекторной нагрузки соединен с шиной второго 11 источника питания, причем коллекторный выход второго 16 дополнительного токового зеркала связан с базой второго 4 выходного транзистора, а общий эмиттерный выход второго 16 дополнительного токового зеркала подключен к эмиттеру второго 4 выходного транзистора, эмиттер первого 1 входного транзистора соединен с эмиттером первого 18 дополнительного транзистора, эмиттер второго 2 входного транзистора соединен с эмиттером второго 19 дополнительного транзистора и через четвертый 20 токостабилизирующий двухполюсник соединен с шиной первого 9 источника питания, коллектор первого 18 дополнительного транзистора соединен с базой первого 3 выходного транзистора, коллектор второго 19 дополнительного транзистора соединен с базой второго 4 выходного транзистора, объединенные базы первого 18 и второго 19 дополнительных транзисторов связаны с эмиттером первого 3 выходного транзистора через первый 21 вспомогательный резистор и соединены с эмиттером второго 4 выходного транзистора через второй 22 вспомогательный резистор.

На чертеже фиг.2 для пояснения работы схемы ДУ обозначены узлы 23

и 24.

Рассмотрим работу ДУ фиг.1 и фиг.3 на переменном токе.

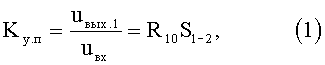

Коэффициент усиления по напряжению ДУ фиг.1 без обратной связи определяется сопротивлением первого 10 двухполюсника коллекторной нагрузки:

где S1-2=(rэ1+rэ2)-1 - крутизна усиления входного каскада, зависящая от сопротивлений эмиттерных переходов (rэ1, rэ2) транзисторов 1 и 2 входного дифференциального каскада.

Покажем аналитически, что более высокие значения Ку.з реализуются в схеме фиг.2.

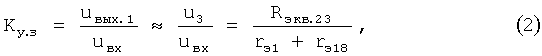

Коэффициент усиления по напряжению ДУ фиг.2 можно найти по формуле

где Rэкв.23 _ эквивалентное сопротивление в узле 23;

u23 - напряжение в узле 23;

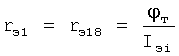

- сопротивления эмиттерных переходов транзисторов

- сопротивления эмиттерных переходов транзисторов

1, 18 при эмиттерном токе Iэi=I0;

φт≈25 мВ - температурный потенциал.

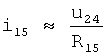

Изменение u23 в узле 23 приводит к появлению токов i10 через двухполюсник коллекторной нагрузки 10 и тока i15 через двухполюсник 15:

,

,

где u24≈uвых1≈u23 - напряжения в узле 24, на выходе ДУ и в узле 23.

Последнее равенство объясняется единичной передачей по напряжению эмиттерного повторителя на транзисторе 3 и свойствами токового зеркала 14.

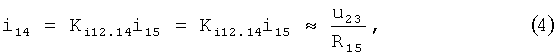

Приращение i15 поступает на вход токового зеркала 9, что создает ток i14 на его выходе:

где Кi12.14≈1 - коэффициент передачи по току дополнительного токового зеркала 14.

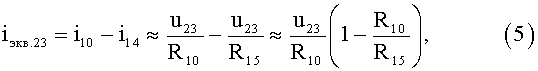

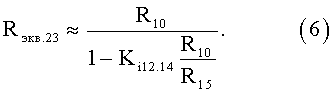

Следовательно, эквивалентное приращение тока в узле 23 (1экв.23) и эквивалентное сопротивление в узле 23:

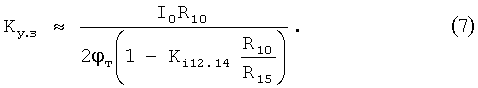

Таким образом, коэффициент усиления по напряжению разомкнутого ДУ фиг.2:

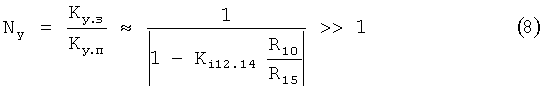

Если выбрать R15=R10, то из (1) и (7) при Кi12.14=0,9-0,99 следует, что в предлагаемом ДУ коэффициент усиления Ку.з повышается в Ny раз, где

Предельные значения Ку.mах в схеме фиг.2 определяются, прежде всего, входным сопротивлением эмиттерного повторителя на транзисторе 3.

Второе «плечо» заявляемого ДУ работает аналогично. Однако вместе с рассмотренным входным каскадом на транзисторах 1, 18 оно образует симметричную схему, в которой обеспечивается нулевой уровень выходного синфазного напряжения:

где Iб - ток базы транзисторов 18, 19.

Таким образом, предлагаемый усилитель имеет повышенный коэффициент усиления по напряжению и малый нулевой уровень выходного синфазного сигнала.

Заявляемая схема с данными свойствами особенно перспективна для использования в микроэлектронных СВЧ-устройствах, реализуемых по техпроцессу SG25VD и др. при низковольтном питании.

Литература

1. Патент США №3.541.464.

2. Патентная заявка WO 2004/102789.

3. Патент США №5.389.893.

4. Патент Японии JP 53-142849.

5. А.св. СССР 1102019.

6. Патентная заявка WO 2005/077525.

7. Патентная заявка США №2006/0181348.

8. Патентная заявка WO 2006/077525.

9. Патент Англии GB 2419052.

10. Патентная заявка США №2008/0290941.

11. Патент WO 96/21271.

12. Патентная заявка США 2009/0108882 fig.3.

13. Патент Японии JP 55030218.

14. Патент Англии GB 1350352.

15. Патент Японии JP 54-47467.

16. Патент Японии JP 55099810.

17. Патент ФРГ DE 2821942.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ЧАСТОТНЫМ ДИАПАЗОНОМ | 2014 |

|

RU2568316C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ И ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2010 |

|

RU2426221C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2419191C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2400924C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ и СВЧ-усилителях, фильтрах, драйверах линий связи и т.п.). Технический результат: повышение предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании в рамках техпроцессов SGB25VD. Дифференциальный операционный усилитель с парафазным выходом содержит первый (1) и второй (2) входные транзисторы, первый (3) и второй (4) выходные транзисторы, эмиттеры которых соединены с соответствующими первым (5) и вторым (6) парафазными выходами устройства и через первый (7) и второй (8) токостабилизирующие двухполюсники связаны с шиной первого (9) источника питания, первый (10) резистор коллекторной нагрузки, включенный между базой первого (3) выходного транзистора и шиной второго (11) источника питания, второй (12) резистор коллекторной нагрузки, включенный между базой второго (4) выходного транзистора и шиной второго (11) источника питания, третий (13) токостабилизирующий двухполюсник, включенный между эмиттером первого (1) входного транзистора и шиной первого (9) источника питания, причем коллекторы первого (3) и второго (4) выходных транзисторов соединены с шиной второго (11) источника питания. Коллектор первого (1) входного транзистора связан со входом первого (14) дополнительного токового зеркала и через третий (15) резистор коллекторной нагрузки соединен с шиной второго (11) источника питания, причем коллекторный выход первого (14) дополнительного токового зеркала связан с базой первого (3) выходного транзистора, а общий эмиттерный выход первого (14) дополнительного токового зеркала подключен к эмиттеру первого (3) выходного транзистора, коллектор второго (2) входного транзистора связан со входом второго (16) дополнительного токового зеркала и через четвертый (17) резистор коллекторной нагрузки соединен с шиной второго (11) источника питания, причем коллекторный выход второго (16) дополнительного токового зеркала связан с базой второго (4) выходного транзистора, а общий эмиттерный выход второго (16) дополнительного токового зеркала подключен к эмиттеру второго (4) выходного транзистора, эмиттер первого (1) входного транзистора соединен с эмиттером первого (18) дополнительного транзистора, эмиттер второго (2) входного транзистора соединен с эмиттером второго (19) дополнительного транзистора и через четвертый (20) токостабилизирующий двухполюсник соединен с шиной первого (9) источника питания, коллектор первого (18) дополнительного транзистора соединен с базой первого (3) выходного транзистора, коллектор второго (19) дополнительного транзистора соединен с базой второго (4) выходного транзистора, объединенные базы первого (18) и второго (19) дополнительных транзисторов связаны с эмиттером первого (3) выходного транзистора через первый (21) вспомогательный резистор и соединены с эмиттером второго (4) выходного транзистора через второй (22) вспомогательный резистор. 6 ил.

Дифференциальный операционный усилитель с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы, первый (3) и второй (4) выходные транзисторы, эмиттеры которых соединены с соответствующими первым (5) и вторым (6) парафазными выходами устройства и через первый (7) и второй (8) токостабилизирующие двухполюсники связаны с шиной первого (9) источника питания, первый (10) резистор коллекторной нагрузки, включенный между базой первого (3) выходного транзистора и шиной второго (11) источника питания, второй (12) резистор коллекторной нагрузки, включенный между базой второго (4) выходного транзистора и шиной второго (11) источника питания, третий (13) токостабилизирующий двухполюсник, включенный между эмиттером первого (1) входного транзистора и шиной первого (9) источника питания, причем коллекторы первого (3) и второго (4) выходных транзисторов соединены с шиной второго (11) источника питания, отличающийся тем, что коллектор первого (1) входного транзистора связан со входом первого (14) дополнительного токового зеркала и через третий (15) резистор коллекторной нагрузки соединен с шиной второго (11) источника питания, причем коллекторный выход первого (14) дополнительного токового зеркала связан с базой первого (3) выходного транзистора, а общий эмиттерный выход первого (14) дополнительного токового зеркала подключен к эмиттеру первого (3) выходного транзистора, коллектор второго (2) входного транзистора связан со входом второго (16) дополнительного токового зеркала и через четвертый (17) резистор коллекторной нагрузки соединен с шиной второго (11) источника питания, причем коллекторный выход второго (16) дополнительного токового зеркала связан с базой второго (4) выходного транзистора, а общий эмиттерный выход второго (16) дополнительного токового зеркала подключен к эмиттеру второго (4) выходного транзистора, эмиттер первого (1) входного транзистора соединен с эмиттером первого (18) дополнительного транзистора, эмиттер второго (2) входного транзистора соединен с эмиттером второго (19) дополнительного транзистора и через четвертый (20) токостабилизирующий двухполюсник соединен с шиной первого (9) источника питания, коллектор первого (18) дополнительного транзистора соединен с базой первого (3) выходного транзистора, коллектор второго (19) дополнительного транзистора соединен с базой второго (4) выходного транзистора, объединенные базы первого (18) и второго (19) дополнительных транзисторов связаны с эмиттером первого (3) выходного транзистора через первый (21) вспомогательный резистор и соединены с эмиттером второго (4) выходного транзистора через второй (22) вспомогательный резистор.

| US 6285245 В1, 04.09.2001 | |||

| Дифференциальный усилитель | 1981 |

|

SU1083341A2 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 5886577 А, 23.03.1999. | |||

Авторы

Даты

2011-10-27—Публикация

2010-10-27—Подача