Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления и преобразования аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, фазорасщепителях сигналов и т.п.).

Широкое применение СВЧ дифференциальных сигналов в современной микроэлектронике позволяет снизить влияние синфазных помех, нелинейных искажений четного порядка, повысить качество обработки сигналов при низких напряжениях питания. Применение дифференциальных сигналов часто сопровождается необходимостью преобразования их в однофазный сигнал и обратно, так как большинство периферийных устройств могут работать лишь с однофазными сигналами. Для выполнения таких преобразований служат специальные симметрирующие устройства - так называемые «балуны» (balanced to unbalanced). Балуны наиболее часто применяются при построении усилителей мощности, смесителей и аналоговых перемножителей сигналов. Заявляемое устройство может быть отнесено к данному классу усилительных каскадов, которые применяются не только в качестве фазорасщепителей сигналов, но и для их усиления.

В настоящее время в ВЧ и СВЧ электронике в структурах квадратурных модуляторов и демодуляторов применяются дифференциальные усилители с парафазным выходом, реализованные на базе классического комплементарного дифференциального каскада с использованием р-n-р входных и n-р-n выходных транзисторов (Патент США №5.521.552 fig.3а, опубл. в 1996 г.; Патент США №4.059.808 fig.1, опубл. в 1977 г.; Патент США №4.176.308 fig.2, опубл. в 1979 г.; Патент США №4.389.579, опубл. в 1983 г.; Патент США №4.536.663, опубл. в 1985 г.; Патент США №4.760.286, опубл. в 1988 г.; Патент США №5.401.995 fig.1, опубл. в 1995 г.; Патент RU 1107279, опубл. в 1984 г.; Патент RU 1283946, опубл. в 1987 г.; Патент ФРГ 2633952 fig.1, опубл. в 1977 г.; Патент США №5.789.949, опубл. в 1998 г.).

Наиболее близким по технической сущности к заявляемому устройству является дифференциальный усилитель переменного тока, фиг.1, рассмотренный в патенте США фирмы Analog Devices №5.521.552 fig.3а, опубл. в 1996 г. Эта же структура присутствует в патентах других производителей микроэлектронных изделий (Патент США №4.059.808 fig.1, опубл. в 1977 г.; Патент США №4.176.308 fig.2, опубл. в 1979 г.; Патент США №4.389.579, опубл. в 1983 г.; Патент США №4.536.663, опубл. в 1985 г.; Патент США №4.760.286, опубл. в 1988 г.; Патент США №5.401.995 fig.1, опубл. в 1995 г.; Патент RU 1107279, опубл. в 1984 г.; Патент RU 1283946, опубл. в 1987 г.; Патент ФРГ 2633952 fig.1, опубл. в 1977 г.; Патент США №5.789.949, опубл. в 1998 г.).

Существенный недостаток известного устройства состоит в том, что на частотах порядка 6-8 ГГц, используемых в системах спутникового телевидения, связи, радионавигации и т.п., он не обеспечивает необходимую фазовую погрешность Δφ преобразования однофазного входного сигнала uвх в два противофазных выходных напряжения u1 (с фазой φ1) и u2 (с фазой φ2=180°+φ1+Δφ). Причем для техпроцесса SGB25VD Δφ=φ2-φ1=8÷10°, что недопустимо для применения известного устройства в квадратурных модуляторах и демодуляторах систем связи нового поколения.

Основная задача предлагаемого изобретения состоит в снижении в 5-10 раз фазовой погрешности преобразования одиночного входного сигнала на частотах до 8 ГГц в два противофазных выходных напряжения.

Поставленная задача решается тем, что в дифференциальном усилителе с первым 1 и вторым 2 парафазными выходами, первым 3 и вторым 4 входами и источником сигнала 5, связанным с первым 3 входом устройства, содержащий первое 6 и второе 7 токовые зеркала, базовые входы которых объединены и подключены к первому 8 токостабилизирующему двухполюснику, коллекторные выходы соединены с соответствующими первым 1 и вторым 2 выходами устройства, а также соответствующими первым и вторым выводами первого 9 и второго 10 резисторов нагрузки, первый 11 и второй 12 входные буферные повторители, входы которых связаны с соответствующими первым 3 и вторым 4 входами устройства, а выходы соединены с соответствующими эмиттерными входами первого 6 и второго 7 токовых зеркал, предусмотрены новые элементы и связи - первый 11 входной буферный повторитель выполнен на первом 13 входном транзисторе, база которого соединена со входом первого 11 входного буферного повторителя, эмиттер - с выходом первого 11 входного буферного повторителя, а коллектор подключен по переменному току ко второму выводу второго 10 резистора нагрузки и через первый 14 дополнительный резистор связан с шиной первого 15(+) источника питания, второй 12 входной буферный повторитель выполнен на втором 16 входном транзисторе, база которого соединена со входом второго 12 входного буферного повторителя, эмиттер - с выходом второго 12 входного буферного повторителя, а коллектор подключен по переменному току ко второму выводу первого 9 резистора нагрузки и через второй 17 дополнительный резистор связан с шиной первого 15(+) источника питания.

На чертеже фиг.1 представлена схема ДУ-прототипа.

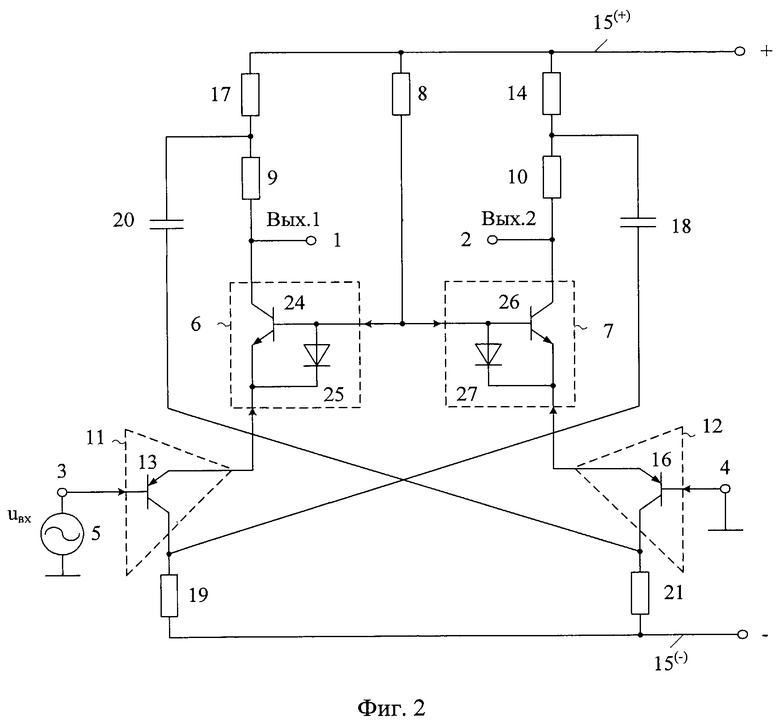

На чертеже фиг.2 представлена схема заявляемого ДУ в соответствии с п.1 и п.2 формулы изобретения.

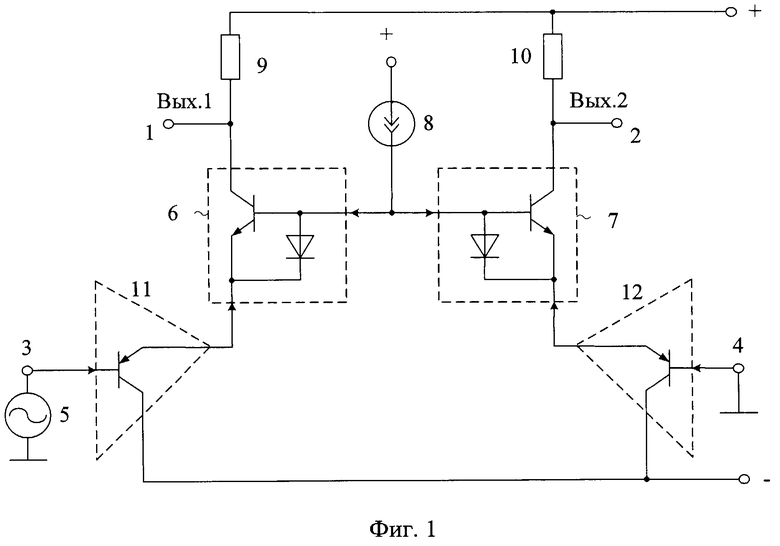

Схема ДУ, соответствующая п.3, п.4 и п.5 формулы изобретения, приведена на чертеже фиг.3.

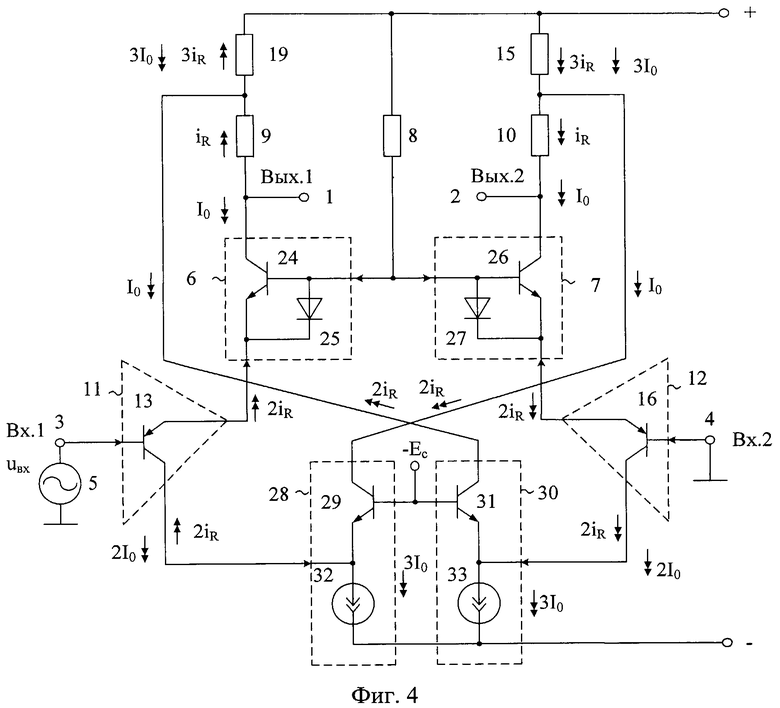

На чертеже фиг.4 показана схема ДУ, соответствующая п.6 формулы изобретения.

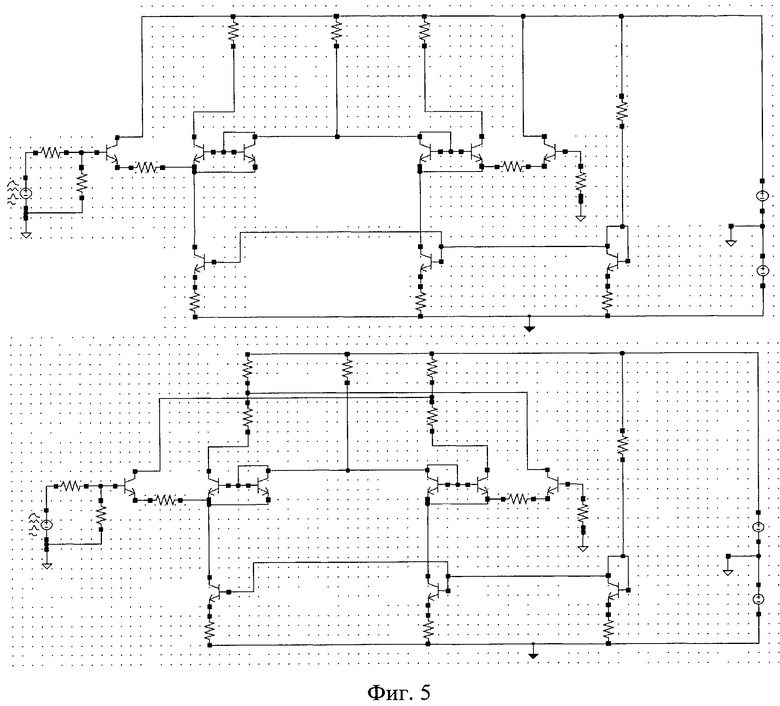

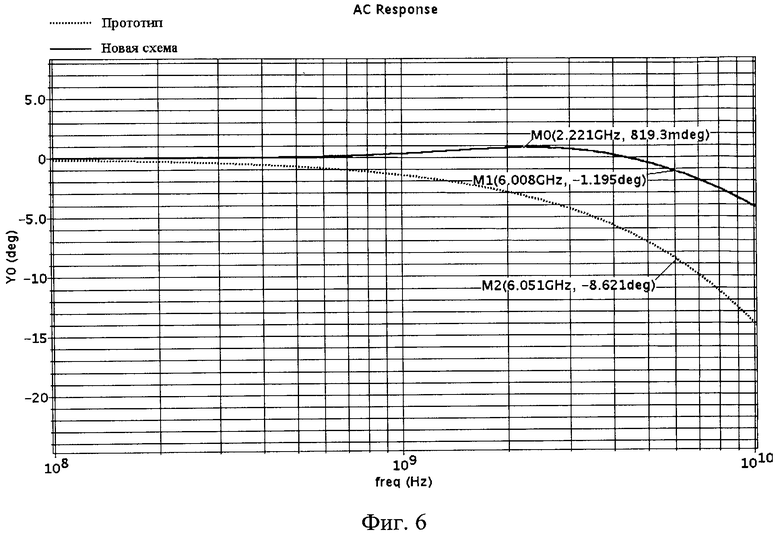

На чертеже фиг.5 показана схема ДУ-аналога (верхний рисунок), не имеющего новых связей в соответствии с п.3 формулы изобретения, и схема ДУ фиг.3 (нижний рисунок) в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на чертеже фиг.6 - зависимость вносимой ДУ фазовой погрешности Δφ между выходами сравниваемых схем от частоты.

Двухканальный дифференциальный усилитель с первым 1 и вторым 2 парафазными выходами, первым 3 и вторым 4 входами и источником сигнала 5, связанным с первым 3 входом устройства, содержит первое 6 и второе 7 токовые зеркала, базовые входы которых объединены и подключены к первому 8 токостабилизирующему двухполюснику, коллекторные выходы соединены с соответствующими первым 1 и вторым 2 выходами устройства, а также соответствующими первым и вторым выводами первого 9 и второго 10 резисторов нагрузки, первый 11 и второй 12 входные буферные повторители, входы которых связаны с соответствующими первым 3 и вторым 4 входами устройства, а выходы соединены с соответствующими эмиттерными входами первого 6 и второго 7 токовых зеркал. Первый 11 входной буферный повторитель выполнен на первом 13 входном транзисторе, база которого соединена со входом первого 11 входного буферного повторителя, эмиттер - с выходом первого 11 входного буферного повторителя, а коллектор подключен по переменному току ко второму выводу второго 10 резистора нагрузки и через первый 14 дополнительный резистор связан с шиной первого 15(+) источника питания, второй 12 входной буферный повторитель выполнен на втором 16 входном транзисторе, база которого соединена со входом второго 12 входного буферного повторителя, эмиттер - с выходом второго 12 входного буферного повторителя, а коллектор подключен по переменному току ко второму выводу первого 9 резистора нагрузки и через второй 17 дополнительный резистор связан с шиной первого 15(+) источника питания.

На чертеже фиг.2, в соответствии с п.2 формулы изобретения, коллектор первого 13 входного транзистора первого 11 входного буферного повторителя подключен ко второму выводу второго 10 резистора нагрузки через первый 18 разделительный конденсатор и связан с шиной второго 15(-) источника питания через первый 19 вспомогательный резистор, а коллектор второго 16 входного транзистора второго 12 входного буферного повторителя подключен ко второму выводу первого 9 резистора нагрузки через второй 20 разделительный конденсатор и связан с шиной второго 15(-) источника питания через второй 21 вспомогательный резистор.

На чертеже фиг.3, в соответствии с п.3 формулы изобретения, эмиттер первого 13 входного транзистора первого 11 входного буферного повторителя соединен со вторым 22 токостабилизирующим двухполюсником, второй вывод которого подключен к шине второго 15(-) источника питания, а коллектор первого 13 входного транзистора первого 11 входного буферного повторителя подключен непосредственно ко второму выводу второго 10 резистора нагрузки, эмиттер второго 16 входного транзистора второго 12 входного буферного повторителя соединен с третьим 23 токостабилизирующим двухполюсником, второй вывод которого соединен с шиной второго 15(-) источника питания, а коллектор второго 16 входного транзистора второго 12 входного буферного повторителя подключен непосредственно ко второму выводу первого 9 резистора нагрузки.

Кроме этого, на чертеже фиг.3, в соответствии с п.4 формулы изобретения, первое 6 токовое зеркало содержит первый 24 выходной транзистор, база которого соединена с базовым входом первого 6 токового зеркала, а коллектор соединен с коллекторным выходом первого 6 токового зеркала, первый 25 дополнительный р-n переход, включенный параллельно эмиттерно-базовому переходу первого выходного 24 транзистора первого 6 токового зеркала, причем эмиттер первого 24 выходного транзистора первого 6 токового зеркала соединен с эмиттерным входом первого 6 токового зеркала, а тип проводимости первого 24 выходного транзистора первого 6 токового зеркала совпадает с типом проводимости первого 13 входного транзистора первого 11 входного буферного повторителя.

Далее, на чертеже фиг.3, в соответствии с п.5 формулы изобретения, второе 7 токовое зеркало содержит второй 26 выходной транзистор, база которого соединена с базовым входом второго 7 токового зеркала, а коллектор соединен с коллекторным выходом второго 7 токового зеркала, второй 27 дополнительный р-n переход, включенный параллельно эмиттерно-базовому переходу второго 26 выходного транзистора второго 7 токового зеркала, причем эмиттер второго 26 выходного транзистора второго 7 токового зеркала соединен с эмиттерным входом второго 7 токового зеркала, а тип проводимости второго 26 выходного транзистора второго 7 токового зеркала совпадает с типом проводимости второго 16 входного транзистора второго 12 входного буферного повторителя.

На чертеже фиг.4, в соответствии с п.6 формулы изобретения, коллектор первого 13 входного транзистора первого 11 входного буферного повторителя подключен ко второму выводу второго 10 резистора нагрузки через первый 28 неинвертирующий повторитель тока с включением его входного транзистора 29 по схеме с общей базой, а коллектор второго 16 входного транзистора второго 12 входного буферного повторителя подключен ко второму выводу первого 9 резистора нагрузки через второй 30 неинвертирующий повторитель тока с включением его входного транзистора 31 по схеме с общей базой, причем входные транзисторы 29 и 31 первого 28 и второго 30 неинвертирующих повторителей тока отличаются от входных транзисторов 13 и 16 первого 11 и второго 12 входных буферных повторителей типом проводимости.

Рассмотрим работу ДУ фиг.3.

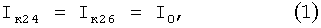

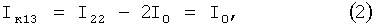

Статический режим схемы фиг.3 устанавливается двухполюсником 8 (I8=2I0). При этом коллекторные токи транзисторов 24, 26, 16 и 13 будут равны

Положительное приращение ВЧ-сигнала uвх=u5 нa входе Вх.1 вызывает уменьшение тока эмиттерного входа токового зеркала 6 и увеличение тока эмиттерного входа токового зеркала 7:

где

где rэ13, rэ16 - сопротивление эмиттерных переходов транзисторов 13 и 16;

rэ6, rэ7 - эквивалентные дифференциальные сопротивления токовых зеркал 6 и 7 по эмиттерным входам.

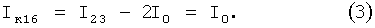

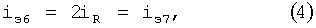

При этом в двухполюсниках 9 и 10 создаются противофазные приращения токов iк24=iR, iк26=iR. Кроме этого, коллекторные токи транзисторов 13 и 16 также изменяются на величину:

В результате в резисторе 14 протекают переменные токи i14=3iR, создаваемые, с одной стороны, дополнительным параллельным каналом на основе транзистора 13 буферного повторителя 11, а с другой стороны, - основным каналом, включающим буферный усилитель 11, токовое зеркало 6 и выходной транзистор 26 токового зеркала 7.

В схеме фиг.3 дополнительный ВЧ-канал передачи входного напряжения ux=u5 через коллекторную цепь транзистора 13 корректирует фазовую погрешность основного канала, который образован токовыми зеркалами 6 и 7. Действительно, паразитная емкость на подложку C22 двухполюсника 22 шунтирует основной канал передачи ux, что вносит отрицательный фазовый сдвиг в основном канале с повышением частоты. Однако для дополнительного ВЧ-канала данная емкость С22 вносит фазовый сдвиг на выходе 2 другого знака, что расширяет диапазон рабочих частот, в пределах которого паразитная фазовая погрешность между выходами ДУ минимальна (Δφ=0÷1°).

Наличие резисторов нагрузки 9 и 10, «изолирующих» выходы Вых.1 и Вых.2 от коллекторов транзисторов 13 и 16, имеющих собственные емкости на подложку, позволяет получить эффект фазовой коррекции без существенных изменений амплитудно-частотных характеристик коэффициента усиления по напряжению основного канала.

Схема фиг.4 реализуется на элементах техпроцесса SG25H2 и не содержит разделительных конденсаторов. Более высокочастотные каскодные каналы передачи токов 2iR на транзисторах 29 и 31 расширяют частотный диапазон и минимизируют эквивалентную входную емкость ДУ, связанную с эффектом Миллера.

Данные теоретические выводы соответствуют результатам компьютерного моделирования схемы фиг.3, представленным графиками фиг.6.

Таким образом, построение заявляемого устройства по двухканальной схеме обеспечивает более высокую крутизну преобразования входного сигнала в выходные противофазные напряжения u1 и u2 и, как показывает эксперимент, в 8 раз уменьшает фазовую погрешность Δφ между выходными напряжениями u1 и u2 на частоте 6 ГГц.

В связи с высокими точностными параметрами по фазовому сдвигу Δφ предлагаемое техническое решение вошло в состав СФ-блоков СВЧ-систем связи нового поколения, выпуск которых намечен в 2011-2012 гг.

Таким образом, заявляемое устройство выполняет функции СВЧ-усилителя и фазорасщепителя, обеспечивающего высококачественное преобразование в диапазоне частот до 6-8 ГГц однофазного сигнала в два противофазных.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.521.552 fig.3а

2. Патент США №4.059.808 fig.1

3. Патент США №4.176.308 fig.2

4. Патент США №4.389.579

5. Патент США №4.536.663

6. Патент США №4.760.286

7. Патент США №5.401.995 fig.1

8. Патент RU 1107279

9. Патент RU 1283946

10. Патент ФРГ 2633952 fig.1

11. Патент США №5.789.949

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411635C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2419191C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2408975C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления и преобразования аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, СВЧ-усилителях, фазорасщепителях сигналов и т.п.). Технический результат заключается в снижении в 5-10 раз фазовой погрешности преобразования одиночного входного сигнала на частотах до 8 ГГц в два противофазных выходных напряжения. Двухканальный дифференциальный усилитель содержит первое и второе токовые зеркала, первый токостабилизирующий двухполюсник, первый и второй резисторы нагрузки, первый и второй входные буферные повторители, первый и второй дополнительные резисторы. 5 з.п. ф-лы, 6 ил.

1. Двухканальный дифференциальный усилитель с первым (1) и вторым (2) парафазными выходами, первым (3) и вторым (4) входами и источником сигнала (5), связанным с первым (3) входом устройства, содержащий первое (6) и второе (7) токовые зеркала, базовые входы которых объединены и подключены к первому (8) токостабилизирующему двухполюснику, коллекторные выходы соединены с соответствующими первым (1) и вторым (2) выходами устройства, а также соответствующими первым и вторым выводами первого (9) и второго (10) резисторов нагрузки, первый (11) и второй (12) входные буферные повторители, входы которых связаны с соответствующими первым (3) и вторым (4) входами устройства, а выходы соединены с соответствующими эмиттерными входами первого (6) и второго (7) токовых зеркал, отличающийся тем, что первый (11) входной буферный повторитель выполнен на первом (13) входном транзисторе, база которого соединена со входом первого (11) входного буферного повторителя, эмиттер - с выходом первого (11) входного буферного повторителя, а коллектор подключен по переменному току ко второму выводу второго (10) резистора нагрузки и через первый (14) дополнительный резистор связан с шиной первого (15(+)) источника питания, второй (12) входной буферный повторитель выполнен на втором (16) входном транзисторе, база которого соединена со входом второго (12) входного буферного повторителя, эмиттер - с выходом второго (12) входного буферного повторителя, а коллектор подключен по переменному току ко второму выводу первого (9) резистора нагрузки и через второй (17) дополнительный резистор связан с шиной первого (15(+)) источника питания.

2. Двухканальный дифференциальный усилитель по п.1, отличающийся тем, что коллектор первого (13) входного транзистора первого (11) входного буферного повторителя подключен ко второму выводу второго (10) резистора нагрузки через первый (18) разделительный конденсатор и связан с шиной второго (15) источника питания через первый (19) вспомогательный резистор, а коллектор второго (16) входного транзистора второго (12) входного буферного повторителя подключен ко второму выводу первого (9) резистора нагрузки через второй (20) разделительный конденсатор и связан с шиной второго (15(-)) источника питания через второй (21) вспомогательный резистор.

3. Двухканальный дифференциальный усилитель по п.1, отличающийся тем, что эмиттер первого (13) входного транзистора первого (11) входного буферного повторителя соединен со вторым (22) токостабилизирующим двухполюсником, второй вывод которого подключен к шине второго (15(-)) источника питания, а коллектор первого (13) входного транзистора первого (11) входного буферного повторителя подключен непосредственно ко второму выводу второго (10) резистора нагрузки, эмиттер второго (16) входного транзистора второго (12) входного буферного повторителя соединен с третьим (23) токостабилизирующим двухполюсником, второй вывод которого соединен с шиной второго (15(-)) источника питания, а коллектор второго (16) входного транзистора второго (12) входного буферного повторителя подключен непосредственно ко второму выводу первого (9) резистора нагрузки.

4. Двухканальный дифференциальный усилитель по п.3, отличающийся тем, что первое (6) токовое зеркало содержит первый (24) выходной транзистор, база которого соединена с базовым входом первого (6) токового зеркала, а коллектор соединен с коллекторным выходом первого (6) токового зеркала, первый (25) дополнительный р-n переход, включенный параллельно эмиттерно-базовому переходу первого выходного (24) транзистора первого (6) токового зеркала, причем эмиттер первого (24) выходного транзистора первого (6) токового зеркала соединен с эмиттерным входом первого (6) токового зеркала, а тип проводимости первого (24) выходного транзистора первого (6) токового зеркала совпадает с типом проводимости первого (13) входного транзистора первого (11) входного буферного повторителя.

5. Двухканальный дифференциальный усилитель по п.3, отличающийся тем, что второе (7) токовое зеркало содержит второй (26) выходной транзистор, база которого соединена с базовым входом второго (7) токового зеркала, а коллектор соединен с коллекторным выходом второго (7) токового зеркала, второй (27) дополнительный р-n переход, включенный параллельно эмиттерно-базовому переходу второго (26) выходного транзистора второго (7) токового зеркала, причем эмиттер второго (26) выходного транзистора второго (7) токового зеркала соединен с эмиттерным входом второго (7) токового зеркала, а тип проводимости второго (26) выходного транзистора второго (7) токового зеркала совпадает с типом проводимости второго (16) входного транзистора второго (12) входного буферного повторителя.

6. Двухканальный дифференциальный усилитель по п.1, отличающийся тем, что коллектор первого (13) входного транзистора первого (11) входного буферного повторителя подключен ко второму выводу второго (10) резистора нагрузки через первый (28) неинвертирующий повторитель тока с включением его входного транзистора (29) по схеме с общей базой, а коллектор второго (16) входного транзистора второго (12) входного буферного повторителя подключен ко второму выводу первого (9) резистора нагрузки через второй (30) неинвертирующий повторитель тока с включением его входного транзистора (31) по схеме с общей базой, причем входные транзисторы (29) и (31) первого (28) и второго (30) неинвертирующих повторителей тока отличаются от входных транзисторов (13) и (16) первого (11) и второго (12) входных буферных повторителей типом проводимости.

| US 5521552 А, 28.05.1996 | |||

| US 4059808 А, 22.11.1977 | |||

| ДВУХКАНАЛЬНЫЙ УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2009 |

|

RU2394364C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2413356C1 |

Авторы

Даты

2012-05-27—Публикация

2011-04-13—Подача