Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления больших импульсных сигналов в структуре аналоговых микросхем различного функционального назначения (быстродействующих операционных усилителей, непрерывных стабилизаторов напряжения, перемножителей сигналов и т.д.).

Известны дифференциальные усилители (ДУ) на основе дифференциальных каскадов с расширенным диапазоном активной работы, которые стали основой построения ряда современных быстродействующих операционных усилителей [1, 2, 3, 4]. Расширение диапазона активной работы в этих схемах (напряжения ограничения Uгр проходной характеристики iвых=f(uвх) [3]) обеспечивается нелинейным параллельным каналом, который находится в выключенном состоянии при малых сигналах (uвх<Uгр≈50 мВ) и, наоборот, входит в активный режим при перегрузке базового дифференциального каскада (при uвх>Uгр). Проблема расширения диапазона активной работы ДУ (увеличения Uгр) при сохранении высокой температурной стабильности статического режима ДУ и малой зоне нечувствительности Uп на его проходной характеристике iвых=f(uвх) относится к числу одной из проблем, которая не решается в рамках традиционных технических решений.

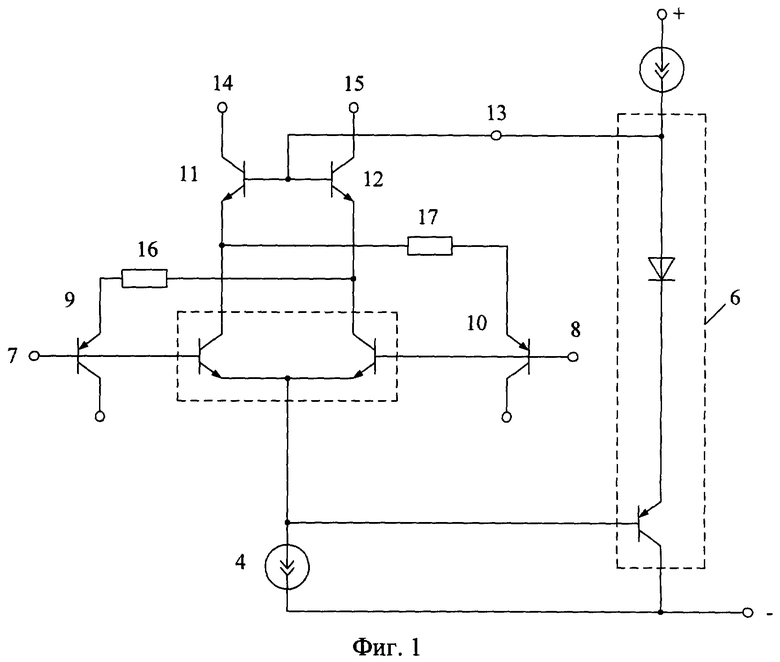

Ближайшим прототипом, схема которого приведена в нескольких работах [1-4], является каскадный дифференциальный усилитель с нелинейным параллельным каналом (фиг.1) [Полонников Д.Е. Операционные усилители: принципы построения, теория, схемотехника. - М: Энергоатомиздат 1983., стр.-117, рис.3.28б], содержащий входной дифференциальный каскад на первом и втором входных транзисторах, эмиттеры которых связаны с источником опорного тока и входом повторителя напряжения, базы соединены с входами дифференциального усилителя и базами соответствующих первого и второго вспомогательных транзисторов, а коллекторы подключены к эмиттерам первого и второго выходных транзисторов, причем базы первого и второго выходных транзисторов соединены с выходом повторителя напряжения, коллекторы - с первым и вторым токовыми выходами дифференциального усилителя, а эмиттеры первого и второго вспомогательных транзисторов соединены с первыми выводами первого и второго вспомогательных резисторов, вторые выводы которых соединены с эмиттерами выходных транзисторов.

Существенный недостаток известного ДУ состоит в том, что он имеет большую зону нечувствительности на проходной характеристике (iвых=f(uвх)), что не позволяет обеспечить высокое быстродействие операционных усилителей на его основе при средних амплитудах входного сигнала. Как показано в работе [3, стр.75, рис.2.22], наличие зоны нечувствительности, которая измеряется пороговым напряжением Uп, отрицательно сказывается на максимальной скорости нарастания выходного напряжения и времени установления переходного процесса для большого сигнала.

Рассмотрим недостатки ДУ-прототипа более подробно.

В рамках известных технических решений возможны два основных варианта обеспечения статического режима нелинейного параллельного канала:

1. Параллельный канал (транзисторы параллельного канала) при uвх=0 находится в выключенном состоянии, его выходные статические токи (токи коллектора транзисторов) и их температурные изменения близки к нулю (измеряются долями микроампер). Т.е. при таком статическом режиме схема известного ДУ имеет наилучшие значения показателей, характеризующих составляющую эдс смещения нуля от параллельного канала, дрейф эдс смещения нуля от параллельного канала, входные токи и дрейф входных токов от параллельного канала, а также ослабление входных синфазных сигналов, обусловленное параллельным каналом. Однако при работе в этом режиме параллельный канал имеет большую зону нечувствительности на характеристике передачи тока iвых=f(uвх), которая обусловлена физическими свойствами биполярного транзистора (как известно, эмиттерный ток транзистора достигает микроамперных значений только при Uэб>0,5 В). Таким образом, в рассматриваемом случае известный ДУ имеет наилучшие статические параметры, но характеризуется большой зоной нечувствительности на проходной характеристике iвых=f(uвх) (Uп=0,4-0,6 B).

2. Во втором случае за счет введения специальных цепей смещения статического уровня в параллельный канал можно перевести его транзисторы в активный режим и тем самым убрать зону нечувствительности на характеристике iвых=f(uвх). Это благоприятно скажется на быстродействии операционного усилителя с таким входным каскадом, особенно при малых напряжениях питания (1,5-2,5 В). Однако транзисторы параллельного канала, переведенные в активный режим для уменьшения зоны нечувствительности, создадут дополнительную температурную нестабильность статического режима всего ДУ, ухудшат его ослабление синфазных сигналов, входные сопротивления для дифференциальных и синфазных сигналов и т.п.

Таким образом, в рамках известных технических решений можно иметь либо предельно высокие значения статических параметров ДУ, но большую зону нечувствительности, либо малую зону нечувствительности, но повышенную температурную нестабильность и неудовлетворительные статические параметры, а также более низкие значения коэффициента ослабления синфазного сигнала, коэффициента подавления помехи по питанию и т.д. Иными словами, в известных ДУ невозможно одновременно обеспечить два режима:

- выключенное состояние транзисторов параллельного канала (токи эмиттера его транзисторов, близкие к нулю) при uвх=0;

- малую зону нечувствительности или ее полное отсутствие, т.е. линейную проходную характеристику (не имеющую изломов в области средних входных напряжений).

Основная цель предлагаемого изобретения состоит в повышении линейности проходной характеристики в широком диапазоне входных сигналов при сохранении высокой стабильности статического режима. При этом высокая стабильность статического режима обеспечивается полностью выключенным состоянием транзисторов параллельного канала, а исключение зоны нечувствительности - за счет новых элементов и связей между ними.

Поставленная цель достигается тем, что в дифференциальном усилителе (фиг.1), содержащем входной дифференциальный каскад на первом и втором входных транзисторах, эмиттеры которых связаны с источником опорного тока и входом повторителя напряжения, базы соединены с входами дифференциального усилителя и базами соответствующих первого и второго вспомогательных транзисторов, а коллекторы подключены к эмиттерам первого и второго выходных транзисторов, причем базы первого и второго выходных транзисторов соединены с выходом повторителя напряжения, коллекторы - с первым и вторым токовыми выходами дифференциального усилителя, а эмиттеры первого и второго вспомогательных транзисторов, соединены с первыми выводами первого и второго вспомогательных резисторов, дополнительно вводятся новые элементы и связи: первый и второй дополнительные транзисторы, эмиттеры которых соединены с вторыми выводами соответствующих первого и второго вспомогательных резисторов, базы связаны с соответствующими коллекторами первого и второго входных транзисторов.

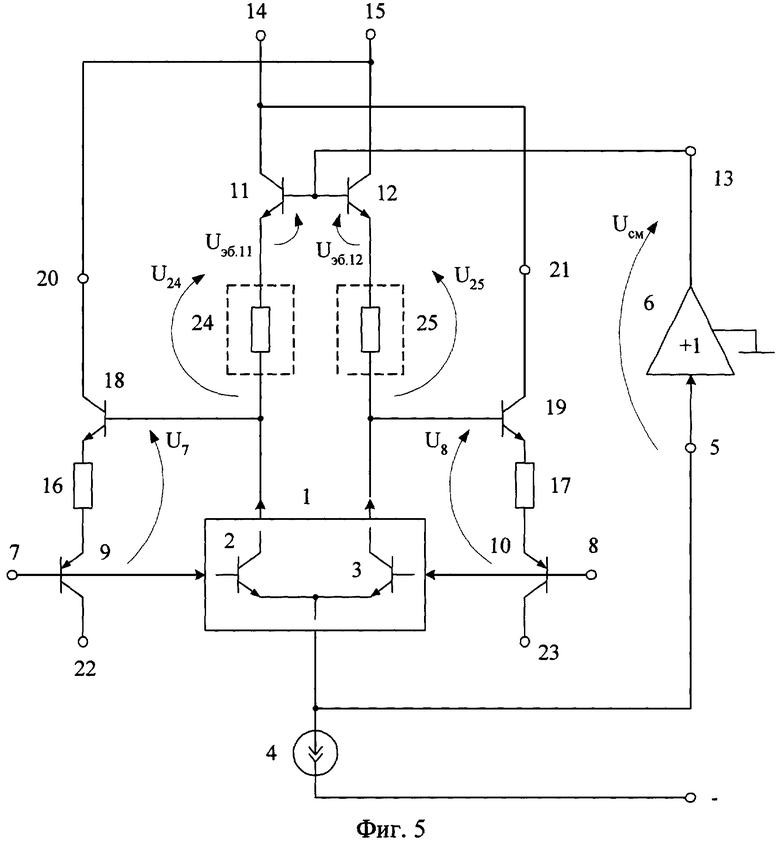

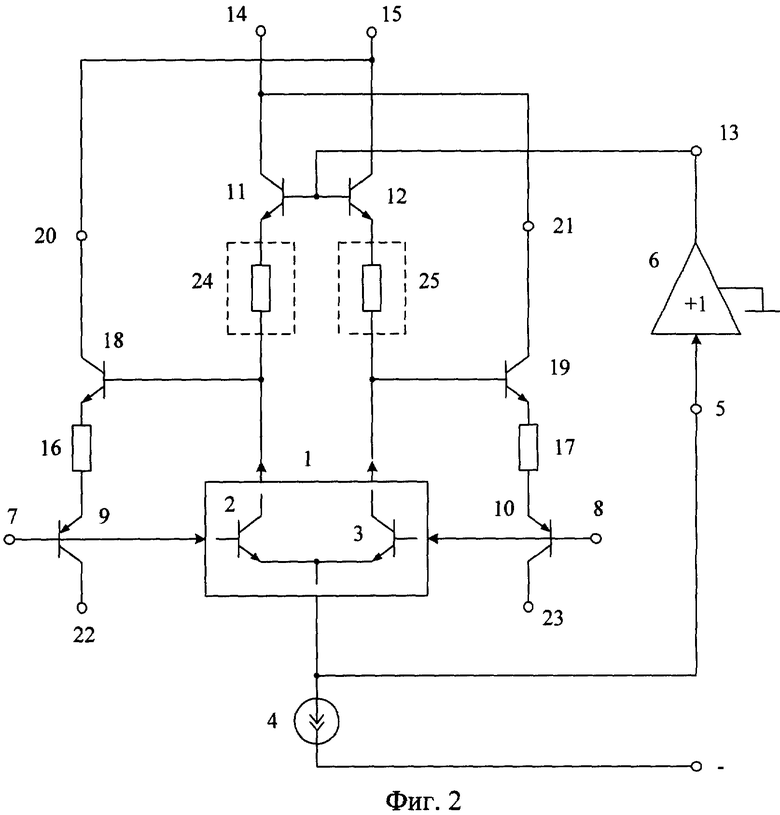

Дифференциальный усилитель по п.1 формулы изобретения (фиг.2) содержит входной дифференциальный каскад 1 на первом 2 и втором 3 входных транзисторах, эмиттеры которых связаны с источником опорного тока 4 и входом 5 повторителя напряжения 6, базы соединены с входами дифференциального усилителя 7 и 8 и базами соответствующих первого 9 и второго 10 вспомогательных транзисторов, а коллекторы подключены к эмиттерам первого 11 и второго 12 выходных транзисторов, причем базы первого 11 и второго 12 выходных транзисторов соединены с выходом 13 повторителя напряжения 6, коллекторы - с первым 14 и вторым 15 токовыми выходами дифференциального усилителя, а эмиттеры первого 9 и второго 10 вспомогательных транзисторов соединены с первыми выводами первого 16 и второго 17 вспомогательных резисторов. В соответствии с п.1 формулы изобретения в схему введены первый 18 и второй 19 дополнительные транзисторы, эмиттеры которых соединены с вторыми выводами соответствующих первого 16 и второго 17 вспомогательных резисторов, базы связаны с соответствующими коллекторами первого 2 и второго 3 входных транзисторов дифференциального каскада 1. Коллекторы транзисторов 18 и 19, а также транзисторов 9 и 10, выполняют функции соответствующих токовых выходов 20, 21 и 22, 23 параллельного канала, обеспечивающего усиление больших амплитуд входного сигнала.

В соответствии с п.2 формулы изобретения (фиг.2) коллекторы первого 2 и второго 3 входных транзисторов подключены к эмиттерам первого 11 и второго 12 выходных транзисторов через дополнительные двухполюсники 24 и 25.

В качестве дополнительных двухполюсников 24 и 25 авторы рекомендуют использовать резисторы, диоды, а также параллельное включение диодов и резисторов. Диодно-резистивное построение двухполюсников предотвращает насыщение транзисторов 2 и 3.

В соответствии с п.3 формулы изобретения (фиг.2) коллектор первого дополнительного транзистора 18 соединен с коллектором второго выходного транзистора 12 и вторым токовым выходом 15 дифференциального усилителя, а коллектор второго дополнительного транзистора 19 соединен с коллектором первого выходного транзистора 11 и первым токовым выходом 14 дифференциального усилителя.

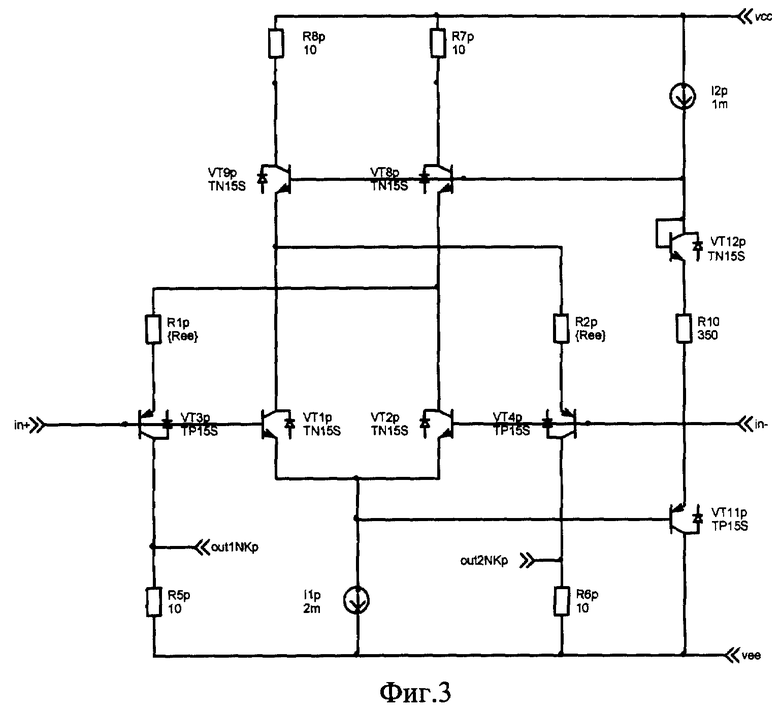

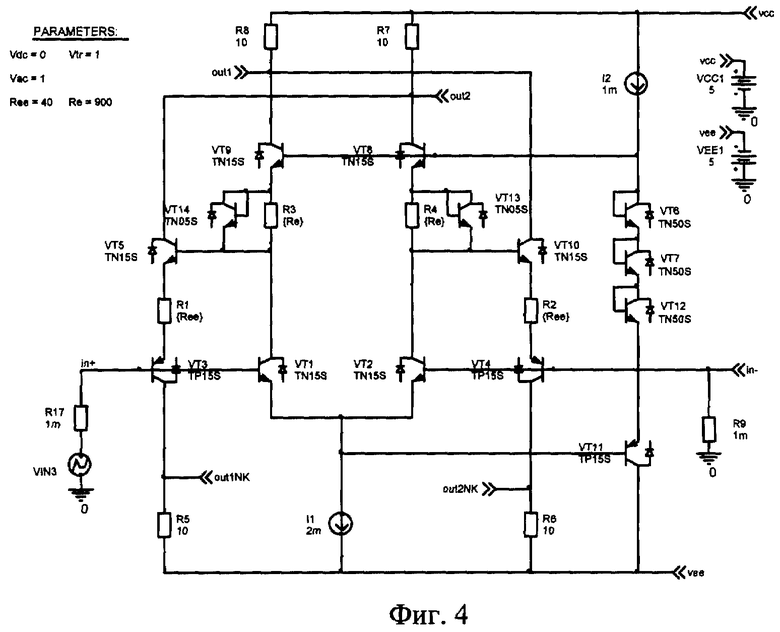

На фиг.3 приведена карта статического режима ДУ-прототипа полученного в среде PSpice, а на фиг.4 - заявляемого ДУ.

На фиг.5 показана схема, поясняющая работу заявляемого ДУ.

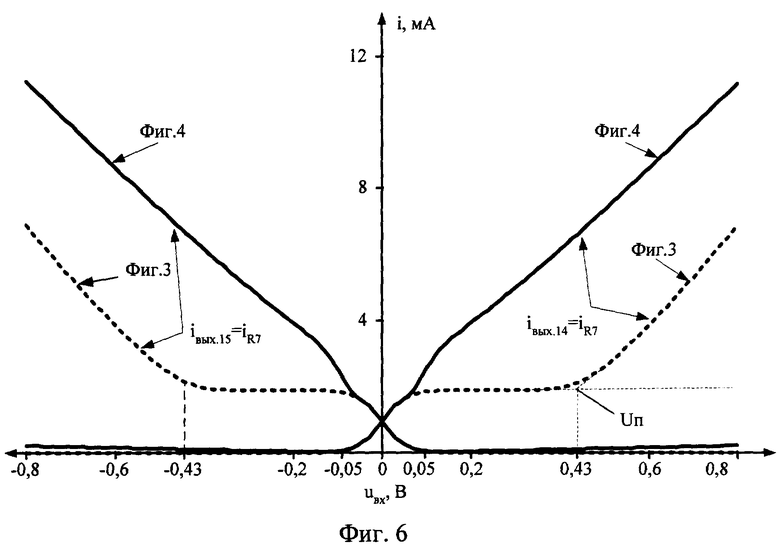

Графики фиг.6 иллюстрируют зависимости выходных токов заявляемого (фиг.4) и известного (фиг.3) ДУ (токов выходов 14 и 15 в зависимости от входного напряжения ДУ), которые показывают, что при чрезвычайно малых статических токах параллельного канала (≈0.1 мкА, см. фиг.3, фиг.4) схема фиг.4 не имеет излома проходной характеристики, которая присутствует у ДУ фиг.3 (Uп≈400÷450 мВ).

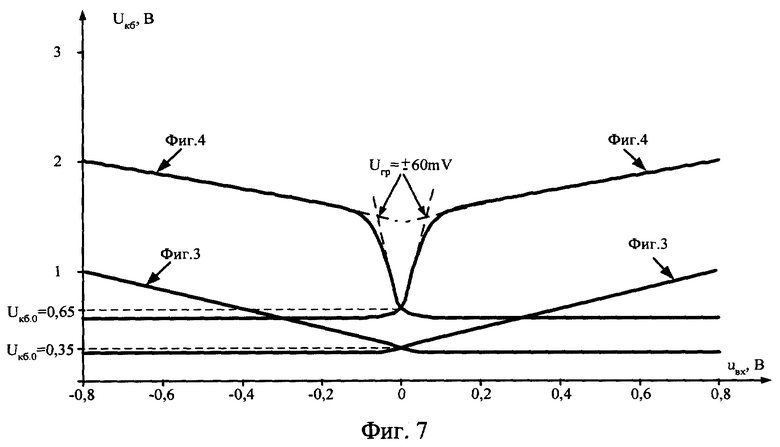

На фиг.7 приведены графики зависимости напряжений коллектор-база входных транзисторов 2 и 3 от напряжения между входами ДУ фиг.3 и ДУ фиг.4. Эти графики позволяют пояснить работу заявляемого устройства.

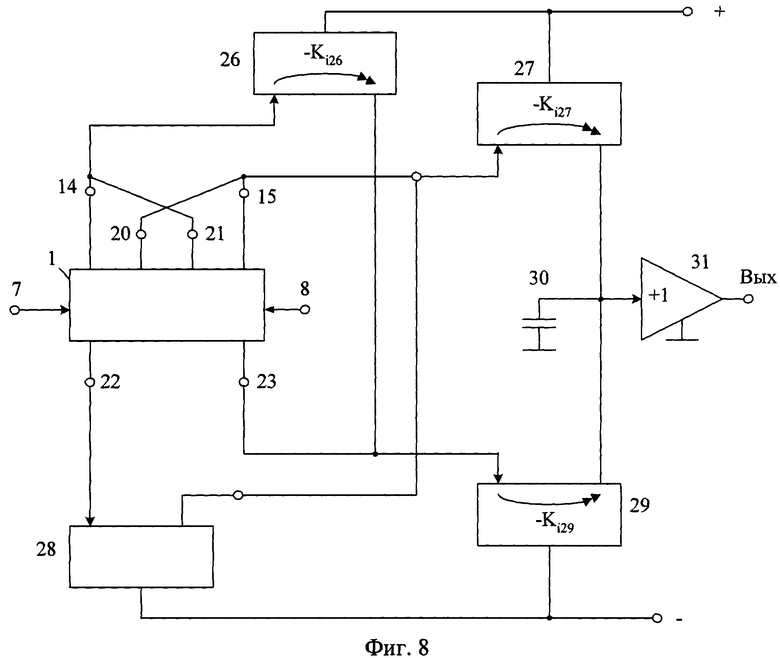

На фиг.8 показана архитектура быстродействующего операционного усилителя на основе заявляемого ДУ в соответствии с п.4 формулы изобретения. В нем первый токовый выход 14 дифференциального усилителя 1 соединен с входом первого 26 дополнительного инвертирующего усилителя тока, второй токовый выход 15 соединен с входом второго 27 дополнительного инвертирующего усилителя тока, коллектор первого вспомогательного транзистора 22 соединен с входом третьего 28 дополнительного усилителя тока, коллектор второго вспомогательного транзистора 23 связан с входом четвертого 29 дополнительного инвертирующего усилителя тока, причем выход первого 26 дополнительного инвертирующего усилителя тока соединен с входом четвертого 29 дополнительного инвертирующего усилителя тока, выход третьего 28 дополнительного инвертирующего усилителя тока соединен с входом второго 27 дополнительного инвертирующего усилителя тока, а выход второго 27 дополнительного инвертирующего усилителя тока соединен с выходом четвертого 29 дополнительного инвертирующего усилителя тока, корректирующим конденсатором 30 и входом выходного буферного усилителя 31.

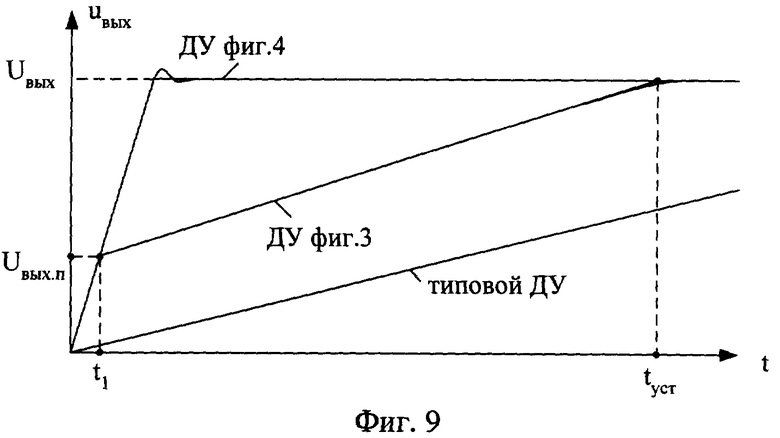

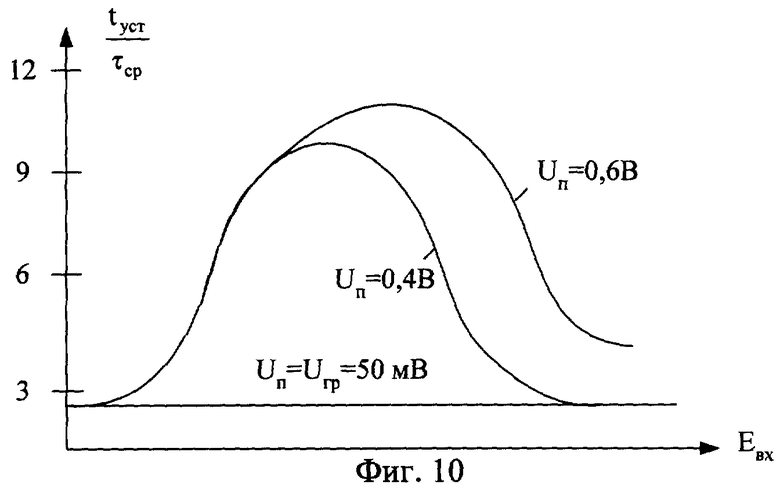

Временная зависимость выходного напряжения типового операционного усилителя (при 100% обратной связи и импульсном входном сигнале большой амплитуды) с предлагаемым (фиг.4) и известным ДУ (прототипом, фиг.3) показана на фиг.9. В соответствии с [3, стр.75, рис.2-22, сплошные линии] влияние зоны нечувствительности на время установления переходного процесса показано на фиг.10, где τср=1/2πf1, f1 - частота единичного усиления разомкнутого ОУ.

Работу схемы фиг.2 рассмотрим для случая, когда в качестве двухполюсников 24 и 25 применяются резисторы (фиг.5).

Режим транзисторов 9, 18 и 10, 19 устанавливается (как и в ДУ-прототипе) повторителем напряжения 6 (разностью напряжений между его входом 5 и выходом 13 Uсм), а также падением напряжения на резисторах 24 (25), которое зависит от коллекторных токов транзисторов 2 и 3 и, следовательно, от входного сигнала Uвх. Именно эта зависимость создает необходимые условия для достижения положительного эффекта - исключения зоны нечувствительности Uп на эквивалентной проходной характеристике.

При нулевом входном сигнале uвх=0 напряжения Uкб.2=Uкб.3, определяющие состояние транзисторов 9 и 18 (11 и 10), выбираются за счет Uсм такими, чтобы транзисторы 9 и 18, 10 и 9 находились в надежно запертом состоянии во всем температурном диапазоне. Как показано на фиг.7 для этого необходимо иметь Uкб=0,65 В. Тогда токи коллекторов транзисторов 9 и 18 (10 и 9) будут составлять величины порядка 0,02 мкА. То есть их влиянием на статику базового каскада можно пренебречь.

Если на вход 7 подать отрицательное входное напряжение относительно входа 8, то ток коллектора транзистора 2 каскада 1 начнет уменьшаться, а ток коллектора транзистора 3 увеличиваться. Как следствие, падение напряжения на резисторе 24 уменьшится почти до нуля уже при uвх=50-60 мВ. Поэтому увеличится (на величину падения напряжения на резисторе 24) эквивалентное напряжение смещения эмиттерно-базовых переходов транзисторов 18, 9 и 10, 19, определяющее их режим. То есть введение двухполюсников 24, 25 создает условия для «быстрого» отпирания транзисторов 9, 18 и 10, 19, которое происходит уже при uвх=50-60 мВ. В дальнейшем напряжение между базами транзисторов 9 и 18 (19 и 10) (равное напряжению коллектор-база транзисторов 2 и 3) и, следовательно, их коллекторные токи будут линейно зависеть от Uвх (фиг.7).

Из графиков фиг.6 карт статического режима фиг.3 и фиг.4 следует, что за счет введения новых связей предлагаемый усилитель имеет более высокую линейность проходной характеристики - у него отсутствует зона нечувствительности Uп при сохранении на том же уровне, что и у прототипа, температурной стабильности статического режима.

Источники информации

1. Полонников Д.Е. Операционные усилители: принципы построения, теория, схемотехника, - М.: Энергоатомиздат, 1983, стр. 117, рис.3.28б.

2. Ю.С.Ежков. Справочник по схемотехнике усилителей. Изд. 2-е. М.: РадиоСофт, 2002. - С.84, рис.5.16.

3. Операционные усилители с непосредственной связью каскадов/ Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - С.107, табл.3.2, схема №2.

4. Прокопенко Н.Н. Дифференциальный операционный усилитель с повышенным быстродействием/ Приборы и техника эксперимента. - №2. - М., 1978 г. - С.153.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2255416C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2006 |

|

RU2307459C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2015 |

|

RU2621289C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2310268C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2280318C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292636C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

Изобретение относится к радиотехнике для использования в микроэлектронных усилителях и преобразователях аналоговых сигналов. Технический результат заключается в уменьшении зоны нечувствительности проходной характеристики при сохранении на высоком уровне статической точности. Дифференциальный усилитель содержит входной дифференциальный каскад (1) на входных транзисторах (Т) (2, 3), эмиттеры которых связаны с источником опорного тока (4) и через повторитель напряжения (6) с базами выходных Т (11, 12), эмиттеры которых соединены с коллекторами входных Т (2, 3), базы которых соединены с базами соответствующих вспомогательных Т (9, 10), эмиттеры которых через введенные дополнительные Т (18, 19) соединены с токовыми выходами (14, 15) выходных Т (11, 12), базы Т (18, 19) соединены с коллекторами Т (2, 3), причем коллекторы Т (18, 19) и (9, 10) выполняют функции соответствующих токовых выходов (20, 21 и 22, 23) параллельного канала, обеспечивающего усиление больших амплитуд входного сигнала. 3 з.п. ф-лы, 10 ил.

| ПОЛОННИКОВ Д.Е | |||

| Операционные усилители: приниципы построения, теория, схемотехника, Москва, Энергоатомиздат, 1983, с.117, рис.3.28б | |||

| Усилитель | 1988 |

|

SU1580527A1 |

| Усилитель | 1988 |

|

SU1656669A1 |

| US 6281752 А, 28.08.2001. | |||

Авторы

Даты

2006-08-20—Публикация

2005-01-28—Подача