Область техники, к которой относится изобретение

Настоящее изобретение относится к передаче данных. Более конкретно, настоящее изобретение относится к способу и устройству для эффективной обработки принимаемого сигнала в системе связи.

Уровень техники

В типичной цифровой системе связи данные обрабатываются в передающем устройстве, модулируются, согласуются и передаются в приемное устройство. Обработка данных может включать в себя, например, форматирование данных с преобразованием их в некоторый конкретный формат кадра, кодирование форматированных данных для обеспечения обнаружения и исправления ошибок в приемном устройстве, разделение кодированных данных по каналам (т.е. маскирование), расширение данных, разделенных по каналам, в пределах системы, ширины полосы и т.п. Как правило, обработка данных определяется, в частности, реализуемой системой или реализуемым стандартом.

В приемном устройстве происходит прием, согласование, демодуляция и цифровая обработка принимаемого сигнала для восстановления переданных данных. Обработка в приемном устройстве является дополняющей по отношению к той, которая проведена в передающем устройстве, и может включать в себя, например, сжатие принимаемых выборок, демаскирование сжатых выборок для формирования демаскированных символов, декодирование демаскированных символов, и т.п. Вследствие многолучевого распространения и других явлений передаваемый сигнал может достигать приемного устройства по многочисленным каналам сигнала. Для обеспечения улучшенной рабочей характеристики приемное устройство в типичном случае выполнено с возможностью обработки многочисленных (и имеющих самый высокий уровень (наиболее резко выраженных)) копий принимаемого сигнала.

Для проведения требуемой обработки сигнала некоторые обычные приемные устройства выполнены с некоторым количеством элементов для обработки, каждый из которых специально разработан и выделен для выполнения некоторой конкретной функции. Например, приемное устройство может быть оснащено элементом искателя и некоторым количеством элементов для обработки данных. Элемент искателя осуществляет поиск принимаемого сигнала с целью определения сильных (резко выраженных) копий сигнала и для обработки конкретных копий сигнала, имеющих достаточный уровень сигнала, предоставляются элементы для обработки данных. Реализация многочисленных параллельных элементов для обработки приводит к увеличению сложности и стоимости схем. Элементы для обработки в типичном случае имеют фиксированные конструкции и в них, как правило, не предусмотрена возможность программирования (т.е. обработки принимаемого сигнала с применением разных наборов значений параметров для выполнения, например, обработки с использованием пилот-сигнала, поисков сигнала и демодуляции данных). Более того, количество копий сигнала, которые можно обработать, ограничено количеством реализуемых элементов для обработки.

Для уменьшения сложности некоторые другие приемные устройства оснащены некоторым количеством параллельных блоков для предварительной обработки, подключенных к процессору общего канала передачи данных. Каждый блок предварительной обработки выполняет частичную обработку (например, сжатие и маскирование) выделенной копии сигнала. Затем процессор общего канала передачи данных проводит остальную обработку (например, демодуляцию пилот-сигналом, вычисление энергии и т.д.) частично обработанных данных. И опять, ограниченное количество копий сигнала, которые можно обработать, определяют на основании количества реализуемых блоков предварительной обработки, а программирование, как правило, не предусматривается.

Применительно к терминалу пользователя нужно отметить, что способность обрабатывать многочисленные копии принимаемого сигнала может обеспечить улучшенную рабочую характеристику. Применительно к базовой станции нужно отметить, что в типичном случае многочисленным пользователям требуется одновременная обработка многочисленных копий сигнала, что дополнительно обосновывает необходимость эффективных способов обработки сигналов. Способность обрабатывать сигналы для многочисленных пользователей с помощью малого количества элементов для обработки сигналов экономически и технически желательна по многим причинам, например, таким как повышенная плотность компоновки плат, меньшее количество компонентов, сниженные затраты и т.п. Возможность программирования в элементах для обработки сигналов также желательна в системах связи, которые могут передавать данные, используя различные значения параметров (например, различные коды разделения по каналам, имеющие разную длину), в зависимости от различных факторов, например, таких как скорость передачи данных.

Как можно заметить, способы, которые могут обеспечить эффективную обработку принимаемого сигнала в системе связи, весьма желательны.

Сущность изобретения

В настоящем изобретении предложена изящная конструкция демодулятора, имеющая многочисленные преимущества над обычными конструкциями. В соответствии с некоторыми аспектами изобретения предложен блок обработки данных для проведения многих сопровождаемых интенсивными вычислениями операций и предложен контроллер для решения остальных задач, необходимых для обработки (например, демодуляции) принимаемого сигнала. Эта архитектура обеспечивает контроллеру возможность управлять обработкой многих копий сигнала и поддерживать многих пользователей одновременно. В некоторых конструкциях можно предусмотреть микроконтроллер для осуществления «микроуправления» блоком обработки данных и освобождения контроллера от некоторых обязанностей по управлению, связанных с установлением последовательности выполнения команд низкого уровня (упорядочения на низком уровне) блока обработки данных. Эти различные признаки позволяют разработать упрощенную конструкцию, обладающую улучшенной рабочей характеристикой по сравнению с обычными конструкциями.

Блок обработки данных и контроллер могут быть выполнены с возможностью работы с сигналами синхронизации обработки, которые могут быть асинхронными по отношению к частоте следования принимаемых выборок и в типичном случае поступают значительно чаще упомянутых выборок. Более частое поступление сигналов синхронизации обеспечивает обработку большего количества копий принимаемого сигнала без дополнительного увеличения сложности схем, а также обеспечивает увеличение производительности обработки пропорционально частоте сигналов синхронизации. Блок обработки данных также может быть выполнен с обеспечением возможности обработки данных на основании программируемых значений параметров, что обеспечивает повышенную гибкость и расширенные функциональные возможности. Например, программируемыми могут быть сделаны интервал времени поиска, коды разделения по каналам (например, коды Уолша), временной сдвиг и другие параметры. Блок обработки данных также может быть выполнен с возможностью объединения элементов для обработки с целью уменьшения сложности и стоимости схем.

В одном варианте осуществления изобретения предложено приемное устройство для использования либо в терминале пользователя, либо на базовой станции системы радиосвязи (например, системы множественного доступа с кодовым разделением каналов (системы CDMA (МДКР))). Приемное устройство включает в себя первый буфер, подключенный к блоку обработки данных. Этот первый буфер получает и сохраняет выборки в цифровой форме и передаваемые с некоторой конкретной частотой следования выборок (а также может хранить псевдослучайные выборки (PN выборки), используемые для сжатия цифровых выборок). Блок обработки данных извлекает сегменты цифровых выборок из первого буфера и обрабатывает выбранные сегменты с помощью некоторого конкретного набора значений параметров. Работа блока обработки данных основана на сигналах синхронизации обработки, имеющих частоту, которая выше (например, в десять и более раз выше) частоты следования элементарных посылок. Многочисленные копии принимаемого сигнала можно обрабатывать, извлекая и обрабатывая многочисленные сегменты цифровых выборок из первого буфера.

В типичном случае приемное устройство также включает в себя приемник и контроллер. Приемник принимает и обрабатывает передаваемый сигнал для выдачи цифровых выборок. Контроллер распределяет задачи для блока обработки данных и обрабатывает информацию сигнализации, поступающую из блока обработки данных.

Блок обработки данных может быть выполнен таким образом, что будет включать в себя коррелятор, блок демодуляции и объединения символов, первый накапливающий сумматор и второй буфер или некоторую их совокупность. Коррелятор сжимает выбранные сегменты цифровых выборок с помощью соответствующих сегментов псевдослучайных (PN) сжимающих последовательностей для получения коррелированных выборок. Блок демодуляции и объединения символов принимает и дополнительно обрабатывает коррелированные выборки для получения обработанных символов. Второй буфер сохраняет обработанные символы и может быть выполнен с возможностью обращенного перемежения обработанных символов. Имея такую конструкцию, второй буфер может быть разделен на две и более секций, при этом в одной секции будут храниться обработанные символы для текущего пакета, а в еще одной секции будут храниться обработанные символы для предыдущего обработанного пакета. Символы для текущего пакета могут обрабатываться в то время, когда символы для предыдущего пакета выдаются в элемент для последующей обработки сигнала.

Коррелятор может быть выполнен таким образом, что будет включать в себя блок сжатия, второй накапливающий сумматор (выборок) и интерполятор или некоторую их совокупность. Блок сжатия включает в себя группу из К блоков умножения, которые одновременно сжимают группы, содержащие до К комплексных цифровых выборок. Накапливающий сумматор выборок включает в себя группу из К сумматоров, подключенных к группе из К блоков умножения, причем каждый сумматор получает и объединяет выборки из соответствующей группы блоков умножения. Интерполятор получает и интерполирует сжатые выборки для формирования интерполированных выборок.

Блок демодуляции и объединения символов может быть выполнен таким образом, что будет включать в себя демаскирующий элемент, блок демодуляции пилот-сигналом и третий накапливающий сумматор (символов) или некоторую их совокупность. Демаскирующий элемент принимает коррелированные выборки и демаскирует их с помощью одного или нескольких каналообразующих кодов для получения демаскированных символов. Коды разделения по каналам могут быть кодами Уолша, имеющими длину, которая является программируемой и определяется значениями параметров. Блок демодуляции пилот-сигналом демодулирует демаскированные символы с помощью символов пилот-сигнала для получения демодулированных символов. А накапливающий сумматор символов суммирует с накоплением демодулированные символы из многочисленных копий сигнала для получения обработанных символов.

Демаскирующий элемент может быть реализован в виде элемента быстрого преобразования Адамара (FHT (БПА)), имеющего L каскадов, и может быть выполнен таким образом, что будет выбирать и обрабатывать синфазные и квадратурные коррелированные выборки на протяжении чередующихся циклов синхронизации. Элемент БПА может быть выполнен с возможностью демаскирования с помощью одного или нескольких символов Уолша, имеющих (программируемую) длину 1, 2, 4, 8, 16, 32, 64 или 128 или какую-нибудь другую длину.

Первый накапливающий сумматор получает и обрабатывает коррелированные выборки для выдачи накопленных результатов. Первый накапливающий сумматор может быть выполнен с возможностью суммирования с накоплением коррелированных выборок на протяжении некоторого программируемого промежутка времени для получения оценок пилот-сигнала. Первый накапливающий сумматор может включать в себя некоторое количество суммирующих с накоплением элементов, причем каждый суммирующий с накоплением элемент предназначен для получения контрольной оценки сигнала при некотором конкретном временном сдвиге.

Частота следования выборок может быть асинхронной по отношению к сигналу синхронизации обработки. В таком случае контроллер может быть выполнен с возможностью реализации контура синхронизации с задержкой, который отслеживает частоту следования элементарных посылок цифровых выборок, и выдает значение сброса, которое используется для формирования сигнала, впоследствии используемого для записи пакетов цифровых выборок, в первый буфер, начиная с предназначенных для этого ячеек.

Контроллер может быть выполнен с возможностью поддержания синхронизации конечного автомата для каждой обрабатываемой копии сигнала. Синхронизацию каждого конечного автомата можно поддерживать с использованием «зашитых» программ процессора цифровых сигналов (DSP), и он может включать в себя контур слежения за временем, используемый для (1) слежения за продвижением обрабатываемой копии сигнала и (2) формирования временного сдвига, соответствующего копии сигнала. Этот временной сдвиг можно использовать для того, чтобы извлечь из первого буфера надлежащий сегмент выборок для обработки. Контроллер также может принимать тактирующий сигнал, который может использоваться для инициирования обработки сегментов выборок. Этот тактирующий сигнал можно генерировать на основе значения сравнения, выдаваемого контроллером.

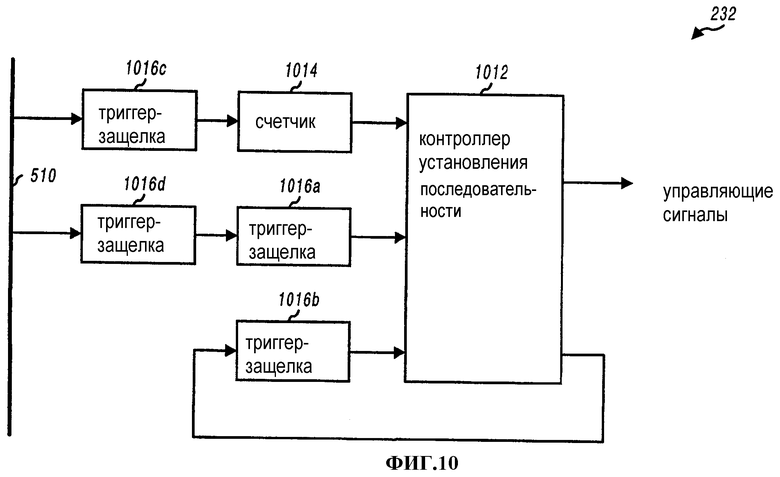

Приемное устройство также может включать в себя микроконтроллер, который получает задачи, поставленные контроллером, и генерирует группу управляющих сигналов для руководства работой элементов в приемном устройстве. Микроконтроллер может задавать конечный автомат задачи для каждой обрабатываемой задачи и может включать в себя контроллер установления последовательности, который принимает один или несколько сигналов индикаторов и поставленные задачи и генерирует группу управляющих сигналов.

В другом варианте осуществления изобретения предложен способ обработки принимаемого сигнала в системе радиосвязи. В соответствии с этим способом, передаваемый сигнал принимают, обрабатывают и преобразуют в цифровую форму для получения цифровых выборок, при некоторой конкретной частоте следования выборок. Затем выборки в цифровой форме, буферизуют в первом буфере, а сегменты цифровых выборок, извлекают из первого буфера и обрабатывают, используя первый конкретный набор значений параметров, некоторые из которых могут быть программируемыми. Обработку проводят на основании сигнала синхронизации обработки, имеющего частоту, которая выше частоты следования выборок.

Обработка может включать в себя некоторую совокупность последовательно осуществляемых (1) сжатия извлеченных выбранных сегментов цифровых выборок с помощью соответствующих сегментов псевдослучайных сжимающих последовательностей для получения коррелированных выборок, (2) демаскирования коррелированных выборок с помощью одного или нескольких каналообразующих кодов для получения демаскированных символов, (3) демодуляции демаскированных символов с помощью символов пилот-сигнала для получения демодулированных символов и (4) суммирования с накоплением демодулированных символов из многочисленных копий сигнала для получения обработанных символов.

Краткое описание чертежей

Признаки, характерные особенности и преимущества настоящего изобретения станут более очевидными после рассмотрения подробного описания, приводимого ниже со ссылками на чертежи, на которых одинаковые позиции обозначают одинаковые элементы на всех чертежах, и при этом:

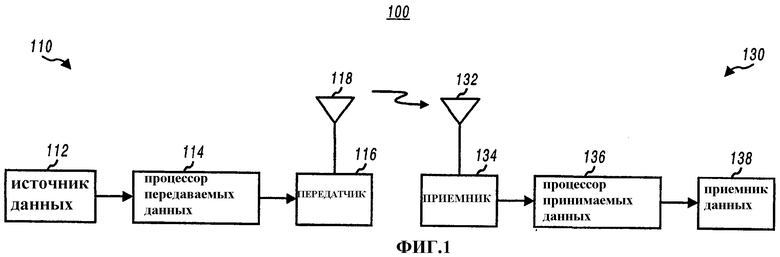

на фиг.1 представлена упрощенная блок-схема системы связи;

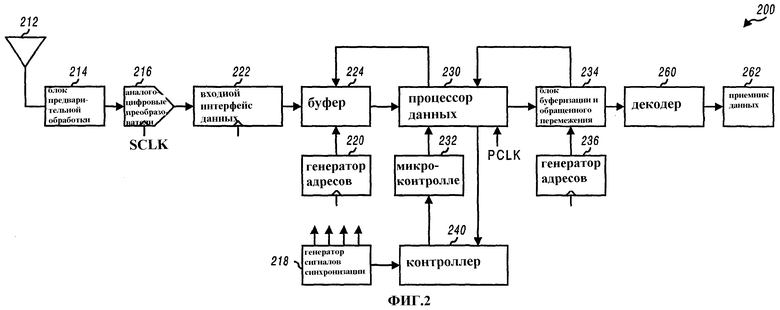

на фиг.2 представлена блок-схема конкретного варианта осуществления приемного устройства, предназначенного для приема и обработки модулированного сигнала;

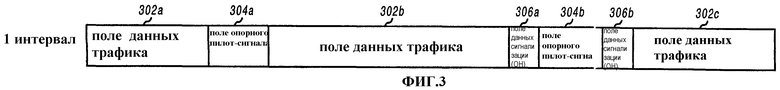

на фиг.3 представлена диаграмма формата кадра данных для передачи по прямой линии связи в соответствии с системой множественного доступа с кодовым разделением каналов (CDMA (МДКР)) с высокой скоростью передачи данных (HDR (ВСПД)) (системой МДКР ВСПД);

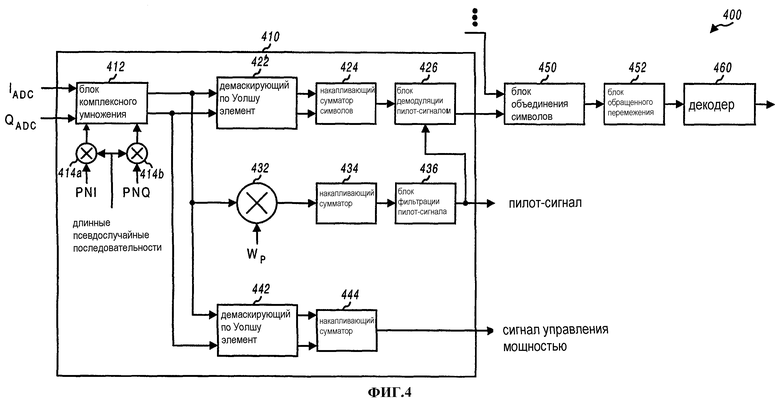

на фиг.4 представлена блок-схема варианта осуществления блока обработки принимаемых данных, который может быть использован для обработки передачи данных по прямой линии связи в системе МДКР ВСПД;

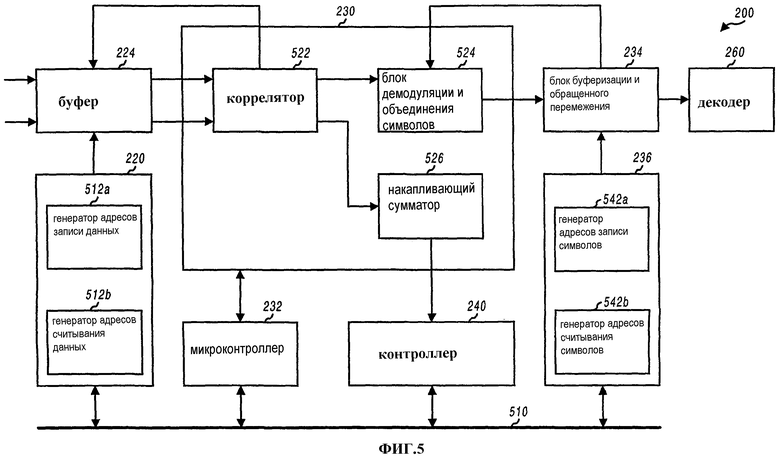

на фиг.5 представлена блок-схема конкретного варианта осуществления блока обработки данных согласно изобретению;

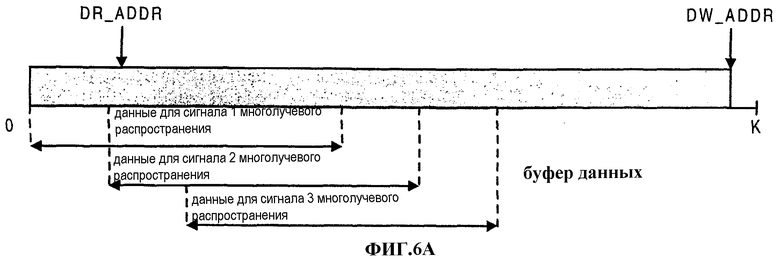

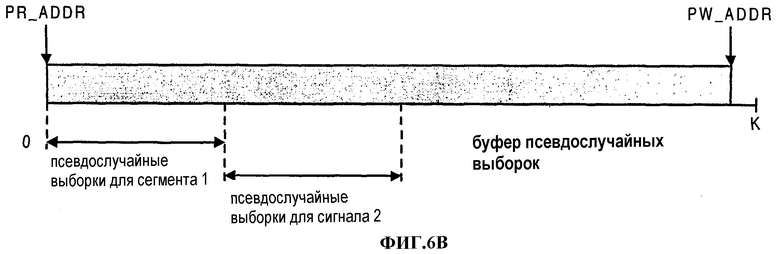

на фиг.6А и 6В представлены диаграммы, иллюстрирующие запись выборок данных в буфер и считывание выборок данных из буфера, а также запись псевдослучайных выборок в буфер и считывание псевдослучайных выборок из буфера соответственно;

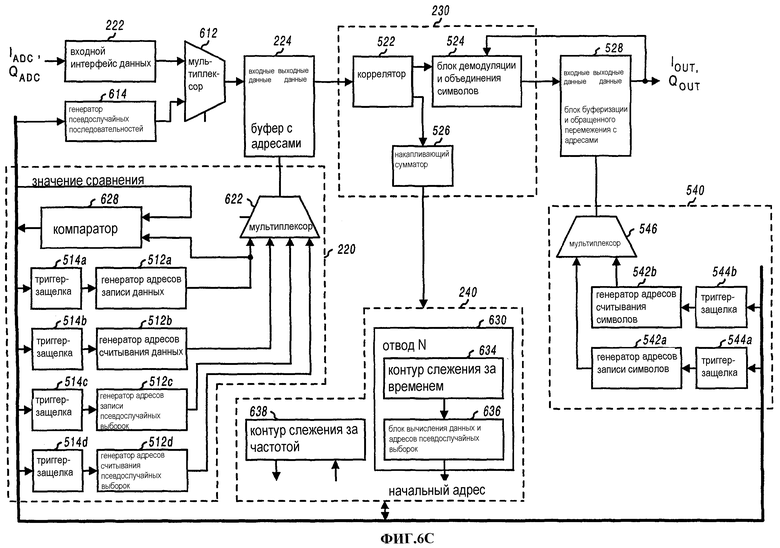

на фиг.6С представлена блок-схема конкретного варианта осуществления буферизации данных для конструкции приемного устройства, показанной на фиг.2 и 5;

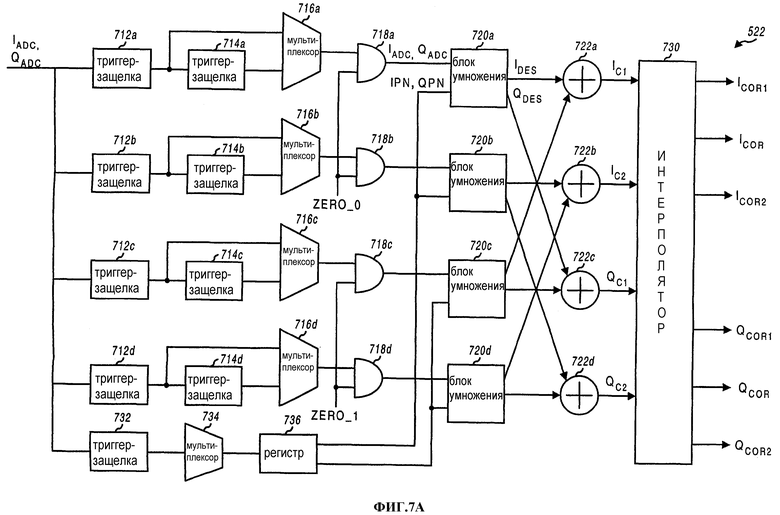

на фиг.7А представлена блок-схема конкретного варианта осуществления коррелятора в блоке обработки данных, показанном на фиг.5;

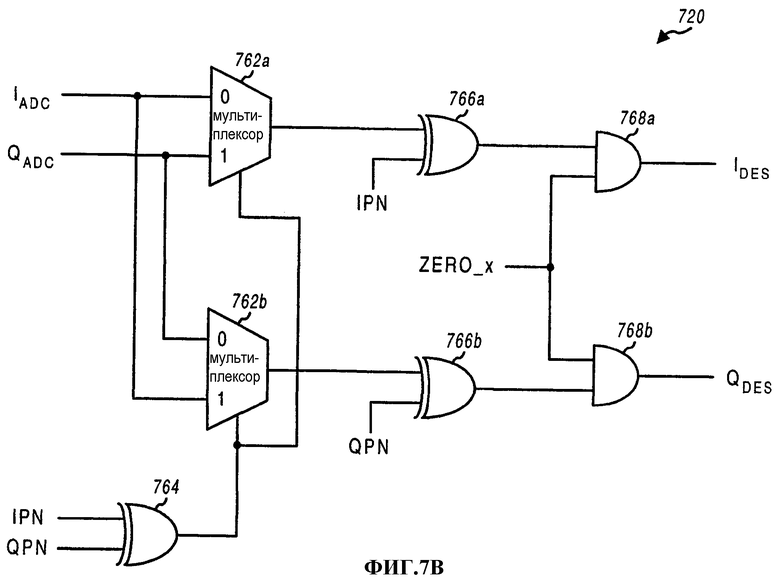

на фиг.7В представлена блок-схема конкретного варианта осуществления блока умножения, который может выполнять комплексное сжатие;

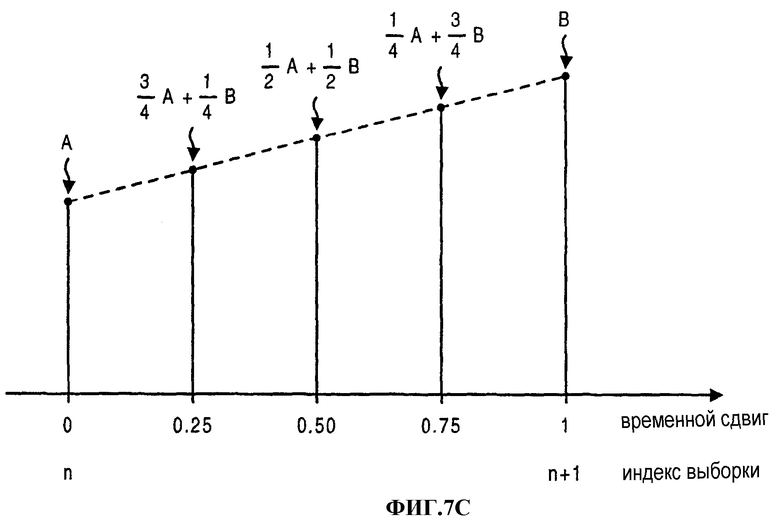

на фиг.7С представлена диаграмма, которая иллюстрирует линейную интерполяцию;

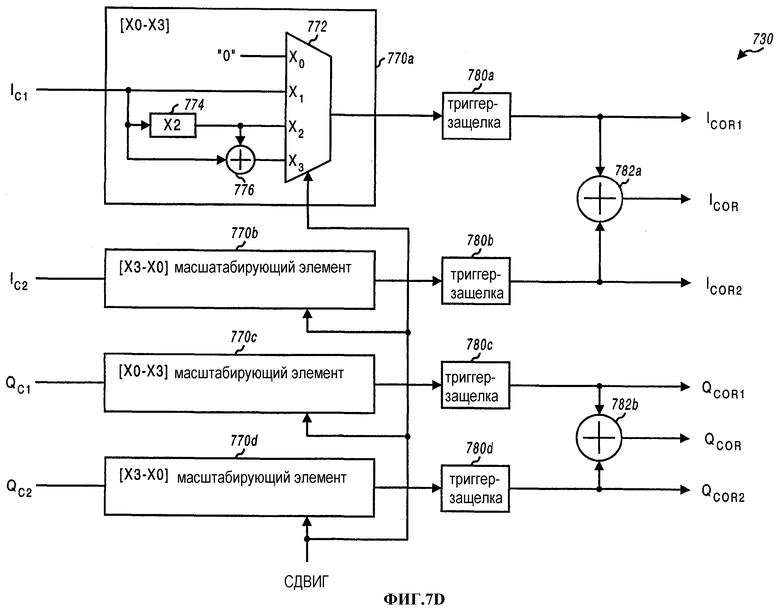

на фиг.7D представлена блок-схема конкретного варианта осуществления интерполятора;

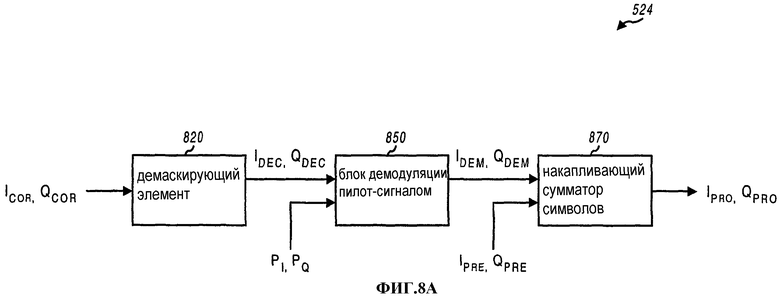

на фиг.8А представлена блок-схема конкретного варианта осуществления блока демодуляции и объединения символов в блоке обработки данных, показанном на фиг.5;

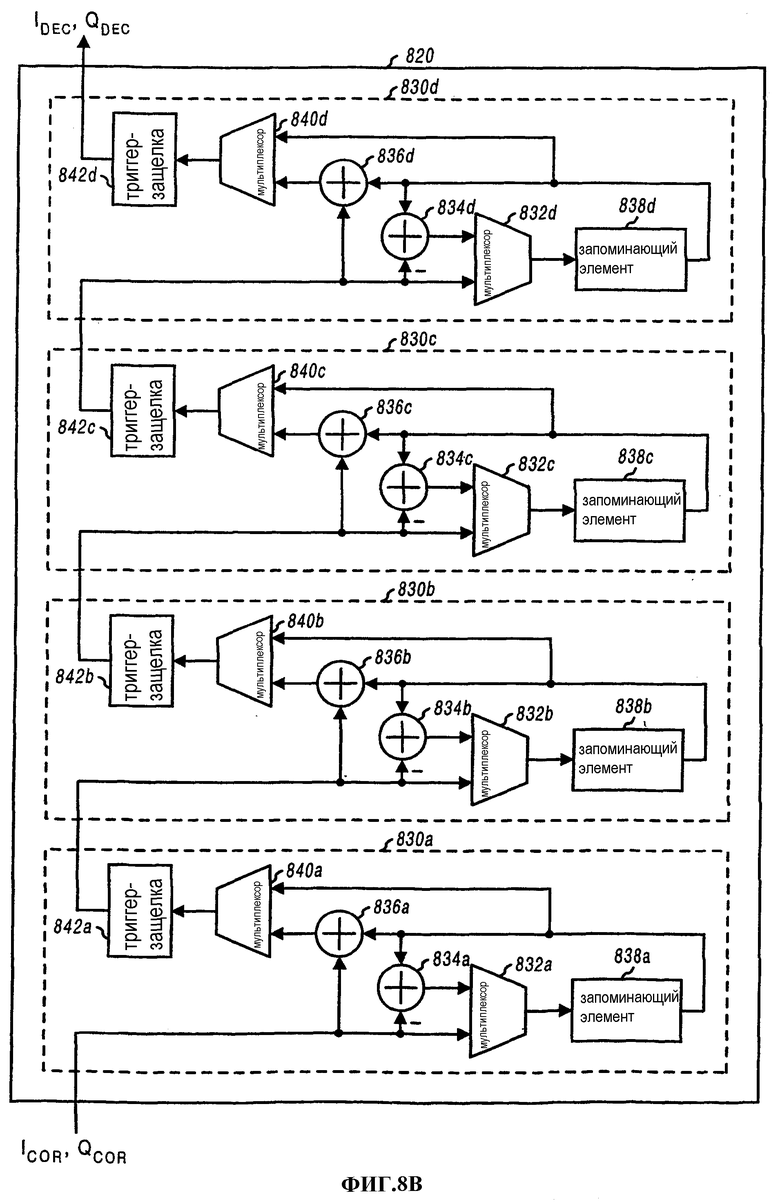

на фиг.8В представлена блок-схема конкретного варианта осуществления элемента быстрого преобразования Адамара (БПА);

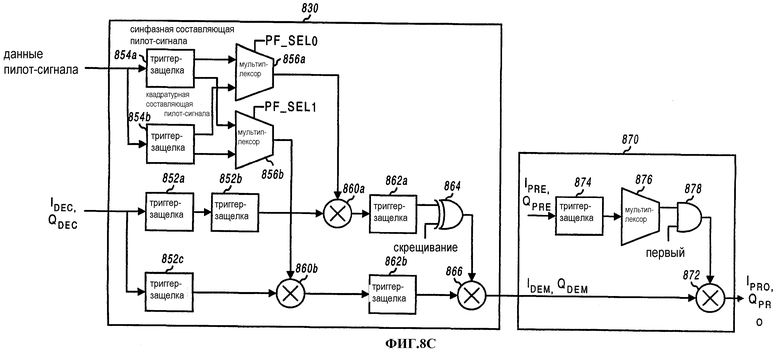

на фиг.8С представлена блок-схема конкретного варианта осуществления блока демодуляции пилот-сигналом;

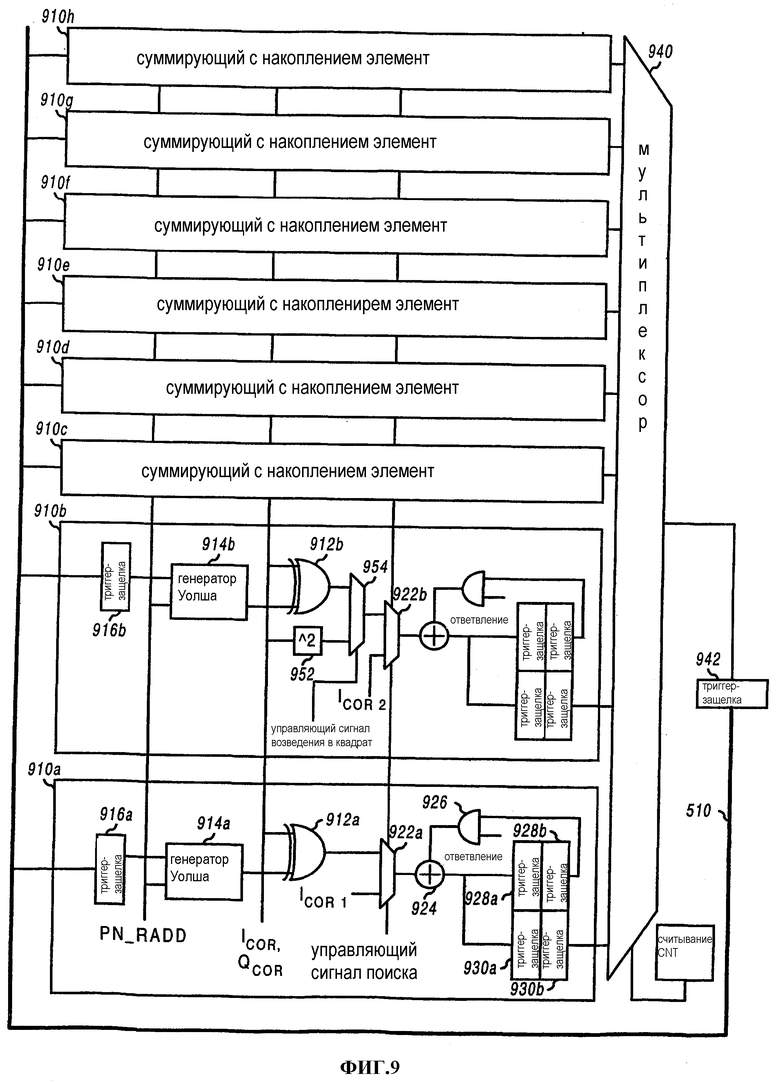

на фиг.9 представлена блок-схема конкретного варианта осуществления накапливающего сумматора для обработки данных трафика, опорного пилот-сигнала и других данных сигнализации;

на фиг.10 представлена блок-схема конкретного варианта осуществления микроконтроллера, который может быть использован для управления работой элементов приемного устройства, и

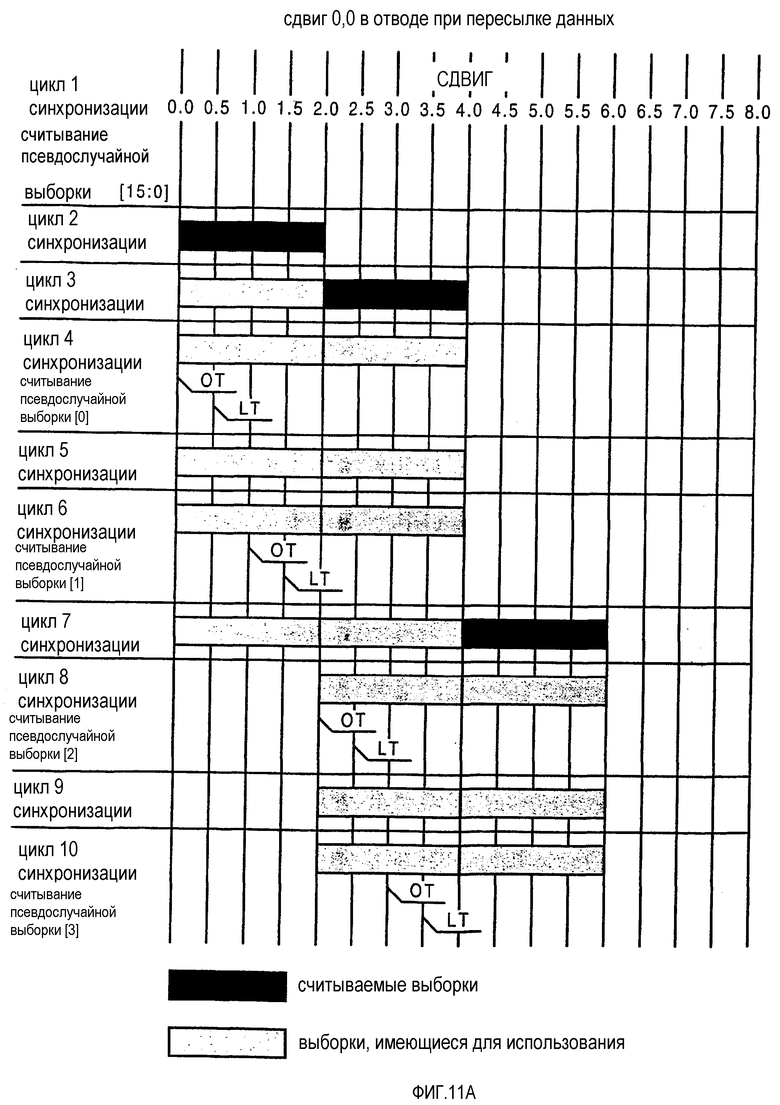

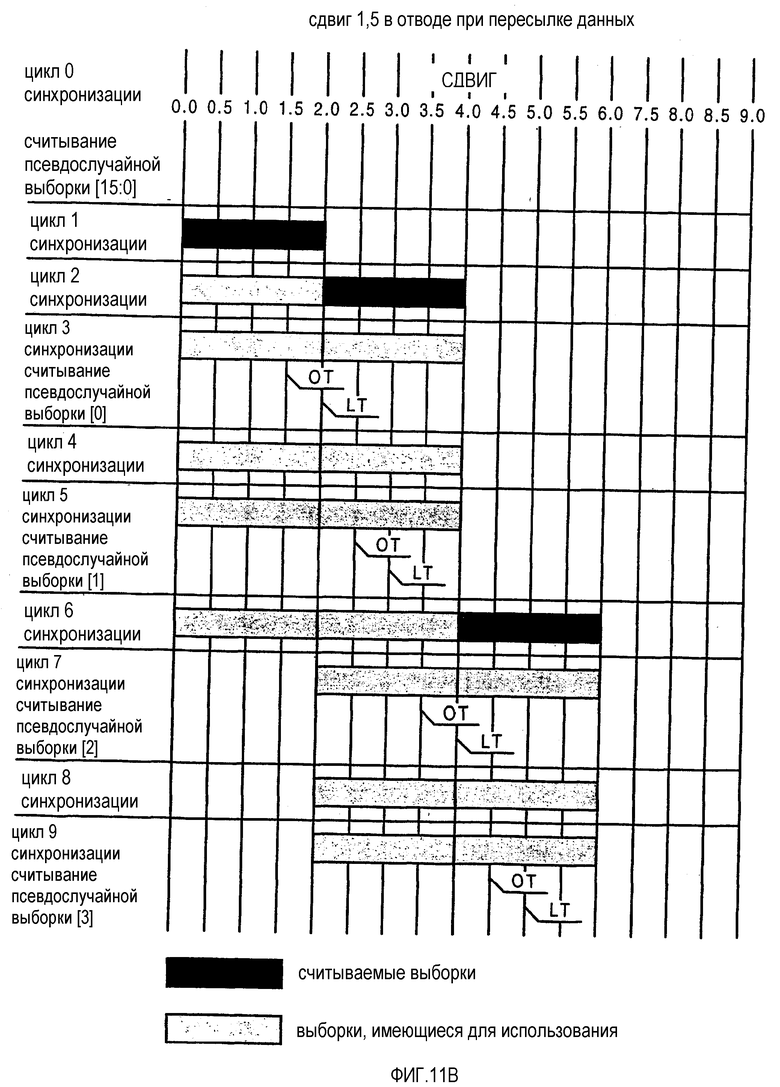

на фиг.11А и 11В представлены временные диаграммы обработки выборок данных блоком обработки данных при временных сдвигах, равных нулю и 1,5, соответственно.

Подробное описание конкретных вариантов осуществления

На фиг.1 представлена упрощенная блок-схема варианта осуществления обработки сигналов при передаче сигналов в системе 100 связи. В передающем устройстве 110 данные посылаются, как правило, в виде пакетов из источника 112 данных в блок обработки 114 передаваемых (TX) данных, который форматирует, кодирует и обрабатывает эти данные для формирования сигналов основной полосы частот. Затем сигналы основной полосы частот подаются в передатчик (TMTR) 116, подвергаются квадратурной модуляции, фильтрации, усилению и преобразованию с повышением частоты для формирования модулированного сигнала, который передается через антенну 118 в один или несколько приемных устройств.

В приемном устройстве 130 происходит прием передаваемого сигнала с помощью антенны 132 и выдача его в приемник (RCVR) 134. В приемнике 134 принимаемый сигнал усиливается, фильтруется, подвергается преобразованию с понижением частоты, квадратурной демодуляции с переводом в основную полосу частот, а также преобразованию в цифровую форму для получения синфазной (I) и квадратурной (Q) выборок. Эти выборки выдаются в блок обработки 136 принимаемых (RX) данных, где декодируются и обрабатываются для восстановления переданных данных. Декодирование и обработка в приемном устройстве 130 осуществляются способом, который является дополняющим по отношению к кодированию и обработке, проведенным в передающем устройстве 110. Затем восстановленные данные выдаются в приемник 138 данных.

Вышеописанная обработка сигналов поддерживает передачи пакетных данных, сообщений, видеоинформации, речевой информации, а также связь, обуславливающую другие типы передачи, в одном направлении. Однако обработка сигнала, проходящего в другом направлении, не показана на фиг.1 лишь для упрощения изображения.

Система 100 связи может быть системой множественного доступа с кодовым разделением каналов (МДКР), которая поддерживает передачу речевой информации и данных между пользователями по наземной линии связи. Использование методов MДКР в системе связи множественного доступа описано в патенте США № 4901307 под названием “SPREAD SPECTRUM MULTIPLE ACCESS COMMUNICATION SYSTEM USING SATELLITE OR TERRESTRIAL REPEATERS” («Система связи множественного доступа с расширенным спектром сигналов, в которой используются спутниковые или наземные ретрансляторы»), в патенте США № 5103459 под названием “SYSTEM AND METHOD FOR GENERATING WAVEFORMS IN A CDMA CELLULAR TELEPHONE SYSTEM” («Система и способ формирования сигналов в телефонной сотовой системе МДКР»). Еще одна специальная система МДКР описана в патенте США № 6574211 под названием “METHOD AND APPARATUS FOR HIGH RATE PACKED DATA TRANSMISSION” («Способ и устройство для высокоскоростной передачи пакетированных данных»), заявка на который подана 3 ноября 1997 г.

Системы МДКР обычно выполнены с обеспечением соответствия одному или более таких стандартов, как “TIA/EIA/IS-95-A Mobile Station-Base Station Compatibility Standard for Dual-Mode Wideband Spread Spectrum Cellular System” (Версия А Временного стандарта 1995 г., выпущенная под эгидой Ассоциации электронной промышленности и Ассоциации предприятий связи США под названием «Стандарт совместимости подвижных станций и базовых станций для двухрежимной широкополосной сотовой системы передачи сигналов с расширенным спектром») (в нижеследующем тексте именуется стандартом IS-95-А), “TIA/EIA/IS-98 Recommended Minimum Standard for Dual-Mode Wideband Spread Spectrum Cellular System” (Временный стандарт 1998 г., выпущенный под эгидой Ассоциации электронной промышленности и Ассоциации предприятий связи США под названием «Рекомендуемый стандарт минимальных требований к подвижной станции двухрежимной широкополосной сотовой системы передачи сигналов с расширенным спектром») (в нижеследующем тексте именуется стандартом IS-98), стандарт, предложенный консорциумом под названием “3rd Generation Partnership Project” (3GPP) («Проект сотрудничества в создании средств связи 3-го поколения» (ПСвСС3П)), см. документы №№ 3G TS 25.211, 3G TS 25.212, 3G TS 25.213 и 3G TS 25.214 (в нижеследующем тексте именуется стандартом широкополосного множественного доступа с кодовым разделением каналов (W-CDMA (Ш-МДКР)), и “TR-45.5 Physical Layer Standard for cdma2000 Spread Spectrum Systems” (версия TR-45.5 «Стандарта физического уровня для систем с расширенным спектром формата cdma2000) (в нижеследующем тексте именуется стандартом CDMA-2000). Следует учесть, что непрерывно разрабатываются и предлагаются к применению новые стандарты МДКР. Эти стандарты МДКР упоминаются в данном описании для справок.

На фиг.2 представлена блок схема конкретного варианта осуществления приемного устройства 200, пригодного для приема и обработки модулированного сигнала. Приемное устройство 200 представляет собой конкретный вариант осуществления приемного устройства 130, показанного на фиг.1. Модулированный сигнал принимается с помощью антенны 212 и выдается в блок 214 предварительной обработки. В блоке предварительной обработки принимаемый сигнал усиливается, фильтруется, подвергается преобразованию с понижением частоты и квадратурной демодуляции для получения сигналов основной полосы частот. Затем сигналы основной полосы частот преобразуются в цифровую форму одним или несколькими аналого-цифровыми преобразователями (ADP (АЦП)) с помощью сигнала синхронизации выборок, (SCLK (СВЫБ)) для формирования синфазных (IADC) и квадратурных (QADC) выборок, которые выдаются в схему 222 интерфейса данных. Блок 214 предварительной обработки и аналого-цифровые преобразователи 216 могут быть реализованы в приемнике 134, показанном на фиг.1.

В зависимости от конкретной конструкции приемного устройства 200, аналого-цифровые преобразователи 216 могут выдавать IADC и QADC выборки с высокой частотой следования выборок и в соответствии с сигналами, получаемыми с одной или нескольких антенн. Схема 222 интерфейса данных может децимировать (т.е. удалять) ненужные выборки, а также располагать (т.е. сортировать) выборки, соответствующие каждой антенне, и собирать выборки в слова, подходящие для эффективного хранения их в буфере 224. В одном конкретном варианте осуществления, каждое слово содержит 32 бита данных, а каждая IADC и QADC выборка содержит 4 бита данных, при этом в каждое слово помещаются четыре пары IADC и QADC выборок. Можно также использовать слова другой ширины (например, имеющие ширину 16 бит, 64 бита, 128 бит и т.п.), что также находится в рамках объема притязаний изобретения. Когда имеется слово для хранения, генератор 220 адресов генерирует адрес записи данных, DW_ADDR (АДР_ЗД), и в ячейку буфера 224, указываемую генерируемым адресом, записывается слово.

Затем блок 230 обработки данных извлекает выборки из буфера 224, обрабатывает извлеченные выборки под руководством контроллера 240 и выдает обработанные символы в блок 234 буферизации и обращенного перемежения. Блок 230 обработки данных может последовательно извлекать символы из блока 234 буферизации и обращенного перемежения и суммировать с накоплением символы из многочисленных копий сигнала для получения накопленных символов, которые затем выдаются обратно в блок 234 буферизации и обращенного перемежения. Когда имеется демодулированный символ, подлежащий извлечению из блока 234 буферизации и обращенного перемежения, генератор 236 адресов генерирует адрес считывания данных, SR_ADDR (АДР_СД), который используется для выдачи символа в декодер 260. Блок 230 обработки данных может также выдавать обработанные данные сигнализации непосредственно в контроллер 240. Декодер 260 декодирует демодулированные символы в соответствии с алгоритмом декодирования, который является дополняющим относительно алгоритма кодирования, используемого в передающем устройстве, и выдает декодированные данные в приемник 262 данных.

Блок 230 обработки данных в типичном случае включает в себя коррелятор, накапливающий сумматор, блок демодуляции (умножения) и объединения символов, или некоторую их совокупность, в зависимости от конкретной конструкции блока обработки данных. Блок 230 обработки данных выполняет многие из функций, необходимых для демодуляции принимаемых выборок. Блок обработки данных может быть выполнен с возможностью выдачи демодулированных сигналов непосредственно в декодер 260 с целью декодирования, а обработанных данных сигнализации - в контроллер 240 для дополнительной обработки. Такие обработанные данные сигнализации могут включать в себя, например, накопленные суммы символов опорного пилот-сигнала и управления скоростью передачи данных (DRC (УСПД)) для обработки сигналов обратной линии связи, а также символы управления мощностью для обработки сигналов прямой линии связи.

Контроллер 240 может быть предназначен для выполнения различных функций, например, таких как фильтрация пилот-сигнала, обнаружение синхронизации отводов многоотводного приемника (кейк-приемника), слежение за временем для каждой обрабатываемой копии сигнала, поддержание временного сдвига отводов многоотводного приемника, слежение за частотой (в случае прямой линии связи при обработке удаленным терминалом) или некоторой их совокупности. Контроллер 240 также руководит работой блока 230 обработки данных и блока 234 буферизации и обращенного перемежения, обеспечивая выполнение ими требуемых функций.

В некоторых конструкциях предусмотрен микроконтроллер 232, который руководит работой блока 230 обработки данных. В таких конструкциях микроконтроллер 232 получает директивы или команды из контроллера 240 для решения конкретных задач (например, для осуществления корреляции применительно к одному или нескольким предназначенным для этого отводам многоотводного приемника). Кроме того, микроконтроллер 232 руководит работой блока 230 обработки данных и других блоков (например, буфера 224, блока 234 буферизации и обращенного перемежения), обеспечивая решение ими соответствующих задач. Микроконтроллер 232 может уменьшить объем контроля, требуемый контроллером 240, а также объем взаимодействия между контроллером 240 и другими элементами. Таким образом, микроконтроллер 232 может освободить контроллер 240 от выполнения некоторых функций и обеспечить поддержку им дополнительных каналов и/или пользователей.

Для конструкции, показанной на фиг.2, количество пользователей, которые могут быть поддержаны, в общем случае возрастает пропорционально частотам сигналов синхронизации, выдаваемых в блок 230 обработки данных и контроллер 240. Эти две разновидности сигналов синхронизации независимы, и в зависимости от их конкретных частот один из сигналов синхронизации в типичном случае ограничивает количество копий сигнала и пользователей, которые можно поддерживать.

Генератор 218 сигналов синхронизации генерирует сигналы SCLK синхронизации выборок для аналого-цифровых преобразователей 216 и другие сигналы синхронизации для других элементов приемного устройства 200. В одном конкретном варианте осуществления генератор 218 сигналов синхронизации включает в себя независимый источник сигналов синхронизации, который генерирует главный сигнал синхронизации, и один или несколько счетчиков сигналов синхронизации в реальном масштабе времени (и/или схему фазовой автоподстройки частоты), которые генерируют другие сигналы синхронизации, используемые элементами, находящимися в приемном устройстве 200. Независимый источник сигналов синхронизации может быть реализован в виде кварцевого генератора, управляемого напряжением, или генератора какого-либо иного типа. Счетчики сигналов синхронизации в реальном масштабе времени срабатывают по главному сигналу синхронизации и генерируют сигналы синхронизации на более низких частотах, но являющиеся синхронными с главным сигналом синхронизации. Такие сигналы синхронизации включают в себя сигнал SCLK синхронизации выборок для аналого-цифровых преобразователей, сигнал PCLK (СИНПРД) синхронизации для блока обработки данных, сигналы синхронизации для генераторов 220 и 236 адресов и т.п. В одном конкретном варианте осуществления сигнал SCLK синхронизации выборок получается из главного сигнала синхронизации и имеет частоту, которая близка к частоте следования элементарных посылок принимаемого сигнала (но не обязательно подвергнута фазовой автоподстройке на эту частоту).

В одном конкретном варианте осуществления генератор 220 адресов включает в себя генератор адресов записи данных, который генерирует адрес записи данных, DW_ADDR, и генератор адресов считывания данных, который генерирует адрес считывания данных, DS_ADDR. Генератор 220 адресов может дополнительно включать в себя генераторы адресов для других данных (псевдослучайных последовательностей), которые могут храниться в буфере 224. В одном конкретном варианте осуществления генератор 236 адресов включает в себя генератор адресов записи символов, который генерирует адрес записи символа, SW_ADDRESS (АДРЕС_ЗС), и генератор адресов считывания символов, который генерирует адрес считывания символа, SR_ADDRESS (АДРЕС_СС). Генераторы 220 и 236 адресов подробнее описаны ниже.

Теперь будет приведено более подробное описание реализации и работы приемного устройства 200.

В соответствии с изобретением разработаны блок 230 обработки данных и контроллер 240, обладающие совокупностью признаков, которая обеспечивает улучшенную рабочую характеристику и повышенную эффективность по сравнению с обычными блоками для обработки данных. Некоторые из этих признаков кратко описаны ниже.

Во-первых, блок 230 обработки данных выполняет многие требующие интенсивных вычислений операции и поэтому обеспечивает контроллеру 240 возможность поддержки многих пользователей одновременно. Блок 230 обработки данных может быть выполнен с возможностью проведения требуемой обработки принимаемых данных и выдачи демодулированных символов непосредственно в декодер 260. Таким образом, контроллер 240 может быть освобожден от интенсивной обработки данных (например, от вычисления скалярных произведений), необходимость выполнения которой в обычных конструкциях, как правило, приравнивается к необходимости иметь более сложный контроллер и традиционно мешает такому контроллеру одновременно поддерживать значительное количество пользователей или обрабатывать значительное количество копий сигнала. Кроме того, микроконтроллер 232 может быть выполнен с возможностью осуществления «микро-управления» блоком 230 обработки данных и освобождения контроллера 240 от некоторых «суетных» обязанностей по управлению.

Во-вторых, и блок 230 обработки данных, и контроллер 240 могут срабатывать по сигналу синхронизации, который может быть асинхронным относительно частоты следования выборок, с которой поступают выборки, хранящиеся в буфере 224, и может поступать значительно чаще них. Например, частота следования выборок может быть выбрана вдвое превышающей частоту следования элементарных посылок принимаемого сигнала (т.е. fSAM = 2,4 миллиона выборок в секунду), а сигнал PCLK синхронизации может быть выбран имеющим частоту, которая более чем на порядок превышает величину частоты выборок (например, fPCLK = 50 МГц). Если блок 230 обработки данных и контроллер 240 используются для терминала пользователя, то чаще идущие сигналы синхронизации обеспечивают обработку большего количества копий принимаемого сигнала. В этом случае блок 230 обработки данных и контроллер 240 можно использовать для реализации и поддержки большего количества отводов многоотводного приемника без дополнительного усложнения схем. А если блок 230 обработки данных и контроллер 240 используются на базовой станции, то чаще идущие сигналы синхронизации обеспечивают обработку принимаемых сигналов от большего количества пользователей и/или обработку большего количества копий принимаемых сигналов.

В третьих, и блок 230 обработки данных, и контроллер 240 могут быть выполнены с обеспечением возможности обработки данных на основании программируемых значений параметров. Например, контроллер 240 может выбирать то количество выборок, которое накоплено во время операции поиска, и выдавать это количество в блок 230 обработки данных. В качестве еще одного примера отметим, что блоку 230 обработки данных можно придать конфигурацию, обеспечивающую демаскирование выборок с помощью одного или нескольких каналообразующих кодов, имеющих программируемую длину. В отличие от этого обычные конструкции принимающих устройств, как правило, включают в себя специализированные элементы аппаратного обеспечения, которые решают специальный набор задач при незначительном уровне программируемости или при отсутствии таковой. Признак программируемости согласно изобретению может обеспечить улучшенную рабочую характеристику по сравнению с обычными конструкциями.

В четвертых, блок 230 обработки данных и контроллер 240 могут быть выполнены таким образом, что имеющиеся в них средства обработки обеспечат меньшую сложность схем и меньшие затраты. Каждый из блока 230 обработки данных и контроллера 240 в типичном случае включает в себя группу элементов для обработки, которая выполняет различные необходимые функции (например, сжатие, демаскирование, суммирование с накоплением и демодуляцию пилот-сигналом - в случае блока 230 обработки данных, и демаскирование с помощью пилот-сигнала и слежение за временем - в случае контроллера 240). В решении некоторой конкретной задачи на сегменте выборок участвуют только те элементы для обработки, которые необходимы для решения этой задачи, а остальные элементы могут быть отключены или переведены в режим резервирования. Для дополнительного улучшения рабочей характеристики элементы для обработки, находящиеся как в блоке 230 обработки данных, так и в контроллере 240, как правило, не дублируются, за исключением случаев, когда желательна параллельная обработка. В отличие от этого конструкции обычных приемных устройств, как правило, предусматривают дублирование многих функций, которое может привести к повышению сложности схем и увеличению затрат.

Блок 230 обработки данных может быть выполнен с возможностью обработки передачи данных в соответствии с различными стандартами и системами МДКР. Для ясности теперь изобретение будет описано применительно к системе, сущность которой раскрыта в вышеупомянутом патенте США № 6574211 и именуемой в нижеследующем тексте системой множественного доступа с кодовым разделением каналов с высокой скоростью передачи данных (системой МДКР ВСПД).

На фиг.3 представлена диаграмма формата кадра данных для передачи по прямой линии связи в соответствии с системой МДКР ВСПД. В прямой линии связи - применительно к данным трафика, опорного пилот-сигнала и данным сигнализации - осуществляется мультиплексирование с разделением времени в кадре и передача с базовой станции в конкретный терминал пользователя. Каждый кадр охватывает единицу времени, называемую интервалом (например, имеющим величину 1,67 для конкретной конструкции системы ВСПД). Каждый интервал включает в себя поля 302а, 302b и 302с данных трафика, поля 304а и 304b опорного пилот-сигнала и поля 306а и 306b данных сигнализации, т.е. служебных данных (обозначенные символами ОН). Поля 302 данных трафика и поля 304 опорного пилот-сигнала используются для передачи данных трафика и опорного пилот-сигнала соответственно. Поля 306 данных сигнализации используются для посылки информации сигнализации, например, такой как указатели активности прямой линии связи (обозначаемые символами FAC), указатели занятости обратной линии связи, команды управления мощностью обратной линии связи и т.п. Указатели FAC указывают, есть ли на базовой станции данные для посылки на протяжении конкретного количества интервалов в будущем. Указатели занятости обратной линии связи указывают, достигнут ли предел пропускной способности обратной линии связи базовой станции. А команды управления мощностью предписывают передающим терминалам пользователей увеличить или уменьшить их мощность передачи.

В соответствии с системой МДКР ВСПД перед передачей данные трафика маскируются кодами Уолша, соответствующими каналам, используемым для передачи данных, а данные управления мощностью для каждого терминала пользователя маскируются кодами Уолша, присвоенными этому терминалу пользователя. Опорный пилот-сигнал, замаскированные данные трафика и данные управления мощностью затем расширяются с помощью комплексной псевдослучайной расширяющей последовательности, генерируемой путем умножения коротких псевдослучайных расширяющих последовательностей, присваиваемых конкретной передающей базовой станции, на длинную псевдослучайную последовательность, присваиваемую терминалу пользователя.

На фиг.4 представлена блок-схема конкретного варианта осуществления блока обработки 400 принимаемых данных, который может быть использован для обработки передачи данных по прямой линии связи в системе МДКР ВСПД. Преобразованные в цифровую форму IADC и QADC выборки из приемника выдаются в некоторое количество корреляторов 410 данных (для простоты на фиг.4 показан лишь один из них). Вследствие многолучевого распространения и других явлений передаваемый сигнал может достигать приемного устройства по многочисленным каналам сигнала. Для обеспечения улучшенной рабочей характеристики приемное устройство в типичном случае выполнено с возможностью обработки многочисленных (и имеющих самый высокий уровень (т.е. наиболее резко выраженных)) копий принимаемого сигнала. В случае обычной конструкции предусматривается некоторое количество корреляторов 410 данных, причем каждый коррелятор 410 данных обычно именуют отводом многоотводного приемника. Каждый коррелятор 410 данных может предоставляться для обработки конкретной копии принимаемого сигнала.

В корреляторе 410 данных IADC и QADC выборки выдаются в блок комплексного умножения, который также принимает комплексную псевдослучайную сжимающую последовательность из блоков 414а и 414b умножения. Эту комплексную псевдослучайную сжимающую последовательность генерируют, умножая короткую псевдослучайную синфазную (PNI) и длинную псевдослучайную квадратурную (PNQ) последовательности, соответствующие базовой станции, из которой принимается сигнал, на длинную псевдослучайную последовательность, присвоенную приемному устройству 400. Эти псевдослучайные последовательности имеют временные сдвиги, соответствующие конкретной копии сигнала, обрабатываемой коррелятором 410 данных.

Блок 412 умножения выполняет комплексное умножение комплексных IADC и QADC выборок на комплексную псевдослучайную сжимающую последовательность и выдает комплексные сжатые синфазную и квадратурную (IDES и QDES) выборки в демаскирующие по Уолшу элементы 422 и 442. Сжатые IDES выборки также выдаются в демаскирующий по Уолшу элемент 432.

Демаскирующий по Уолшу элемент 422 демаскирует сжатые IDES и QDES выборки с помощью кодов Уолша, использовавшихся для маскирования данных на базовой станции, и генерирует некоторое количество потоков демаскированных выборок, по одному потоку для каждого канала, используемого для передачи данных. После этого потоки выборок выдаются в накапливающий сумматор 424 символов, который суммирует с накоплением выборки в каждом потоке на основании скорости передачи данных в канале, используемом для передачи потока. Для каждого потока накапливающий сумматор 424 суммирует с накоплением некоторое количество демаскированных выборок для формирования демаскированного символа. Демаскированные символы затем выдаются в блок 426 демодуляции пилот-сигналом.

Демаскирующий по Уолшу элемент 432 демаскирует сжатые IDES выборки с помощью конкретного кода Уолша, WF (например, кода Уолша, равного 0), используемого для маскирования опорного пилот-сигнала на базовой станции. Демаскированные выборки пилот-сигнала затем выдаются в накапливающий сумматор 434 и суммируются с накоплением в течение некоторого конкретного промежутка времени (например, равного длительности опорного пилот-сигнала или периоду опорного пилот-сигнала) для формирования символа пилот-сигнала. Затем символы пилот-сигнала выдаются в фильтр 436 пилот-сигнала и используются для формирования восстановленного пилот-сигнала. Восстановленный пилот-сигнал содержит оценочные или прогнозируемые пилот-сигналы для промежутков времени, проходящих между опорными пилот-сигналами, и выдается в блок 426 демодуляции пилот-сигналом.

Блок 426 демодуляции пилот-сигналом осуществляет когерентную демодуляцию демаскированных символов данных, поступающих из накапливающего сумматора 424, с помощью символов пилот-сигнала, поступающих из фильтра 436 пилот-сигнала, и выдает демодулированные символы данных в блок 450 объединения символов. Когерентная демодуляция осуществляется путем вычисления скалярного произведения и векторного произведения демаскированных символов данных на символы пилот-сигнала, как описано ниже. Скалярное и векторное произведения, по существу, отображают фазовую демодуляцию данных и дополнительное масштабирование получаемого результата по относительному уровню восстановленного пилот-сигнала. Масштабирование с помощью контрольных сигналов приводит к эффективному «взвешиванию» вкладов различных копий принимаемого сигнала в соответствии с качеством этих копий принимаемого сигнала при эффективном объединении. Таким образом, скалярное и векторное произведения играют двойственную роль таких характеристик когерентного многоотводного приемника, как проецирование фаз и взвешивание сигнала.

Блок 450 объединения символов принимает демодулированные символы данных из каждого выделенного коррелятора 410 данных, когерентно объединяет эти символы и выдает восстановленные символы данных в блок 452 обращенного перемежения. Блок 452 обращенного перемежения переупорядочивает эти символы способом, который является дополняющим применительно к тому способу, который реализован на базовой станции. Символы данных из блока 452 обратного перемежения затем декодируются декодером 460 и выдаются в приемник данных.

Конструкция и работа многоотводного приемника для системы МДКР подробнее описана в патенте США № 5764687 под названием “MOBILE DEMODULATOR ARCHITECTURE FOR A SPREAD SPECTRUM MULTIPLE ACCESS COMMUNICATION SYSTEM” («Архитектура демодулятора подвижной станции для системы связи множественного доступа с расширенным спектром сигналов»), а также в патенте США № 5490165 под названием “DEMODULATION ELEMENT ASSIGNMENT IN A SYSTEM CAPABLE OF RECEIVING MULTIPLE SIGNALS” («Выделение демодулирующего элемента в системе, способной принимать многочисленные сигналы»). Скалярное произведение несущей пилот-сигнала и (оптимальное) взвешивание каналов отводов многоотводного приемника подробнее описаны в патенте США № 5506865 под названием “PILOT CARRIER DOT PRODUCT CICRUIT” («Схема для вычисления скалярного произведения несущей пилот-сигнала).

В системе МДКР ВСПД, данные управления мощностью для конкретного терминала пользователя маскируются конкретным кодом Уолша, присвоенным этому терминалу и передаваемым в каждом интервале. Таким образом, в корреляторе 410 данных сжатые IDES и QDES выборки демаскируются демаскирующим по Уолшу элементом 442 с помощью присвоенного кода Уолша. Демаскированные выборки сигнала управления мощностью затем выдаются в накапливающий сумматор 444 и суммируются с накоплением на протяжении длительности посылки сигнала управления мощностью для формирования бита управления мощностью для обрабатываемой копии сигнала. Биты управления мощностью из всех выделяемых корреляторов данных 410 можно когерентно объединить (для простоты это не показано на фиг.4) для формирования объединенного бита управления мощностью, который затем используется для регулирования мощности передачи терминала пользователя.

На фиг.5 представлена блок-схема конкретного варианта осуществления блока 230 обработки данных, который выполнен с возможностью обработки передач данных по прямой и обратной линиям связи для различных систем МДКР. Например, блоку 230 обработки данных можно придать конфигурацию, обеспечивающую проведение обработки сигналов с использованием опорного пилот-сигнала для когерентной демодуляции при передаче данных по прямой линии связи в системе МДКР ВСПД, как описано выше на фиг.4.

Возвращаясь к фиг.2, отмечаем, что IADC и QADC выборки из аналого-цифровых преобразователей 216 форматируются входным интерфейсом 222 данных и сохраняются в буфере 224. В одном варианте осуществления буфер 224 реализован в виде кольцевого двумерного буфера, имеющего размер, выбранный на основании ряда факторов, например, таких как частота следования выборок на входе, частота следования выборок на выходе и т.п. Буфер 224 выполнен с возможностью хранения выборок данных, принимаемых за конкретный период времени (например, на протяжении двух кадров выборок или какого-либо иного периода). Этот период времени выбирают достаточно большим, чтобы обеспечить сбор достаточного количества данных для всех обрабатываемых каналов сигнала, но достаточно малым, чтобы предотвратить запись новых выборок поверх старых, необработанных выборок. Период времени, в течение которого осуществляется сбор и сохранение выборок, может быть программируемым.

В одном варианте осуществления для стирания данных, записанных в буфер 224, каждая строка буфера имеет ширину, которая совпадает с шириной выходного слова входного интерфейса 222 данных (составляющей, например, 32 бита). Когда слово становится доступным для записи в буфер 224, генератор 512а адресов записи данных генерирует адрес записи данных, DW_ADDR, соответствующий следующей имеющейся строке в буфере 224. Потом в строку буфера 224, указываемую генерируемым адресом, записывается слово. После этого хранимые выборки оказываются доступными для их извлечения и обработки блоком 230 обработки данных.

Блоку 230 обработки данных может быть предписана обработка выборок в соответствии с конкретным набором значений параметров. Для обработки данных трафика блок 230 обработки данных может выполнять команды, обеспечивающие: (1) сжатие и демаскирование конкретной копии принимаемого сигнала с конкретным временным сдвигом; (2) осуществление демодуляции декодированных демаскированных символов пилот-сигналом и (3) когерентное объединение демодулированных символов, соответствующих различным копиям сигнала, и т.п. Для обработки данных сигнализации (например, пилот-сигнала и сигнала управления мощностью) блок 230 обработки данных может выполнять команды, обеспечивающие: (1) сжатие и/или демаскирование конкретной копии принимаемого сигнала; (2) суммирование с накоплением демаскированных выборок за некоторый конкретный промежуток времени; (3) объединение накопленных символов из различных копий сигнала и т.п. Блок 230 обработки данных также можно эксплуатировать с целью поиска имеющих высокий уровень копий принимаемого сигнала. Блок 230 обработки данных также может быть выполнен с возможностью и может эксплуатироваться для выполнения обработки различных сигналов, в зависимости от конкретного стандарта или системы МДКР, а также конкретной поддерживаемой передачи данных (по прямой или обратной линии связи).

Блок 234 буферизации и обращенного перемежения обеспечивает сохранение обработанных символов, поступающих из блока 230 обработки данных. Когда некоторый символ обрабатывается блоком 230 обработки данных и становится доступным для записи в блок 234 буферизации и обращенного перемежения, генератор 542а адресов записи символов генерирует адрес записи символа, SW_ADDR, соответствующий надлежащей ячейке в блоке 234 буферизации и обращенного перемежения, указываемой генерируемым адресом записи символа. После этого сохраненные символы могут быть возвращены в блок 230 обработки данных для дальнейшей обработки (например, суммирования с накоплением обработанных символов для другой копии сигнала). Таким образом, блок 234 буферизации и обращенного перемежения сохраняет результаты демодуляции пилот-сигналом для первой копии сигнала, а также сохраняет результаты накопления при демодуляции пилот-сигналом для последующих копий сигнала.

За счет формирования надлежащих адресов считывания и записи символов блок 234 буферизации и обращенного перемежения можно использовать для переупорядочения символов в соответствии с конкретным алгоритмом обращенного перемежения. Когда символы готовы к выдаче в декодер 260, контроллер 240 инициирует процесс считывания в подходящий момент времени. Тогда генератор 542b адресов символов генерирует надлежащие адреса считывания для достижения требуемого обращенного перемежения символов. Подвергнутые обращенному перемежению (т.е. демодулированные) символы выдаются в декодер 260 для декодирования.

В варианте осуществления, показанном на фиг.5, синфазные и квадратурные выборки из буфера 224 выдаются в коррелятор 522 в блоке 230 обработки данных. Коррелятор 522 также получает комплексную псевдослучайную сжимающую последовательность, которую также можно хранить в буфере 224 или генерировать с помощью псевдослучайного генератора псевдослучайных последовательностей (не показанного на фиг.5). Для обработки данных трафика коррелятор 522 сжимает синфазные и квадратурные выборки с помощью комплексной псевдослучайной сжимающей последовательности для получения сжатых выборок. Таким образом, коррелятор 522 выполняет ту функцию сжатия, которую выполняет блок 412 комплексного умножения, показанный на фиг.4. Коррелятор 522 также может быть предназначен для выполнения других функций, например, таких как суммирование с накоплением многочисленных сжатых выборок на протяжении каждого промежутка длительности элементарной посылки, интерполяция сжатых выборок и т.п. Сжатые выборки выдаются в блок 524 демодуляции и объединения символов.

Блоку 524 демодуляции и объединения символов можно придать конфигурацию, обеспечивающую демаскирование, когерентную демодуляцию пилот-сигналом, объединение символов для многочисленных копий сигнала, суммирование с накоплением символов применительно к повторяющимся символам в пакете или выполнение некоторой совокупности перечисленных операций. Для демаскирования блок 524 демодуляции и объединения символов получает сжатые выборки из коррелятора 522 и выполняет демаскирование с помощью набора символов Уолша. В одном конкретном варианте осуществления длина символов Уолша является программируемой и может быть выбрана равной 1, 2, 4, 8, 16 или эта длина может быть равной какому-либо другому значению (например, 32, 64, 128 и т.п.).

Для когерентной демодуляции блок 524 демодуляции и объединения символов получает и когерентно демодулирует демаскированные символы данных с помощью восстановленных символов пилот-сигнала для формирования демодулированных символов, которые сохраняются в блоке 234 буферизации и обращенного перемежения. Для объединения символов блок 524 демодуляции и объединения символов получает и объединяет демодулированные символы, соответствующие различным копиям сигнала, для формирования восстановленных символов, которые опять сохраняются в блоке 524 демодуляции и объединения символов. Таким образом, блок 524 демодуляции и объединения символов может выполнять те функции, которые выполняют коррелятор 410 данных и блок 450 объединения символов, показанные на фиг.4.

Блок 234 буферизации и обращенного перемежения хранит промежуточные и конечные результаты накопления символов. Обработанные символы из блока 524 демодуляции и объединения символов записываются в ячейки блока 234 буферизации и обращенного перемежения, указываемые генератором 542 адресов записи символов, находящимся в генераторе 236 адресов. Сохраняемые символы извлекаются из ячеек блока 234 буферизации и обращенного перемежения, указываемых генератором 542b адресов считывания символов. За счет формирования надлежащих адресов считывания символов блок 234 буферизации и обращенного перемежения можно использовать с целью выполнения обращенного перемежения символов способом, который является дополняющим относительно способа, который реализован в передающем устройстве. Символы, извлекаемые из блока 234 буферизации и обращенного перемежения, представляют собой демодулированные символы, которые выдаются в декодер 260.

Для обработки данных сигнализации коррелятору 522 можно придать конфигурацию, обеспечивающую сжатие синфазных и квадратурных выборок с помощью комплексной псевдослучайной сжимающей последовательности, а также выдачу сжатых выборок в накапливающий сумматор 526. Накапливающему сумматору 526 можно придать конфигурацию, обеспечивающую демаскирование сжатых выборок с помощью одного или нескольких кодов Уолша, суммирование с накоплением сжатых или демаскированных выборок за некоторый конкретный период времени (например, за период опорного пилот-сигнала) и выдачу восстановленных данных (например, данных пилот-сигнала или управления мощностью) в контроллер 240. Накапливающему сумматору 526 также можно придать конфигурацию, обеспечивающую выдачу обработанных символов, используемых для поиска имеющих высокий уровень копий принимаемого сигнала при различных временных сдвигах, как описано ниже.

В одном варианте осуществления контроллер 240 обрабатывает символы пилот-сигнала, поступающие от накапливающего сумматора 526 и генерирует восстановленный пилот-сигнал, который используется для когерентной демодуляции символов данных. В других вариантах осуществления блок обработки пилот-сигнала может быть реализован в блоке 230 обработки данных для фильтрации символов пилот-сигнала и генерации восстановленного пилот-сигнала. Для обработки опорного пилот-сигнала могут быть предусмотрены и другие разработки, находящиеся в рамках объема притязаний данного изобретения.

В конкретном варианте осуществления, показанном на фиг.5, шина 510 данных взаимосвязывает различные элементы приемного устройства 200, такие как генератор 220 адресов, блок 230 обработки данных, микроконтроллер 232 и контроллер 240. Шина 510 данных поддерживает эффективную передачу данных и другой информации между элементами, подключенными к этой шине данных. Например, контроллер 240 может использовать шину 510 данных для постановки задач микроконтроллеру 232 и для посылки обработанных символов пилот-сигнала в блок 230 обработки данных. Могут быть предусмотрены и другие механизмы взаимосвязи элементов приемного устройства 200, также находящиеся в рамках объема притязаний изобретения.

На фиг.6А представлена диаграмма, иллюстрирующая запись выборок данных в буфер 224 и считывание выборок данных из этого буфера. В типичной цифровой системе связи данные подразделяются на пакеты и обрабатываются в этих пакетах, которые затем передаются в кадрах, имеющих некоторую конкретную длительность во времени. Например, в системе МДКР ВСПД данные передаются в пакетах, каждый из которых передается на протяжении одного или нескольких интервалов. Каждый интервал представляет собой некоторую долю кадра и (в системе ВСПД) включает в себя 2048 элементарных посылок, каждая из которых имеет период ТС, который связан с общей шириной полосы системы (например, соотношением ТС = 1/(ширина полосы)).

В одном варианте осуществления получаемые выборки записываются в буфер 224, начиная с предназначенного адреса, который может быть выбран произвольно (например, этот адрес может быть нулевым, как показано на фиг.6А). В одном варианте осуществления инициализация указания предназначенного адреса указателем адреса записи данных происходит при наступлении события сброса (этим событием может быть, например увеличение мощности), а выборки записываются в буфер 224, начиная с ячейки, указываемой упомянутым указателем. Таким образом, между указателем адреса записи и фактической границей кадра, передаваемого через радиоинтерфейс и представляемого выборками, имеется некоторый произвольный сдвиг, называемый также фазовым сдвигом. Граница кадра может соответствовать любому адресу в буфере 224. В процессе приема этот сдвиг вычисляется контроллером 240. Последующие извлечения данных компенсируются этим вычисленным сдвигом - его прибавляют к указателю адреса считывания.

Генератор адресов записи данных генерирует адрес записи данных, DW_ADDR, который указывает следующую доступную ячейку в буфере 224. В одном варианте осуществления выборки записываются в последовательные ячейки буфера 224, а адрес записи данных, DW_ADDR, получает приращение после каждой операции записи. В одном варианте осуществления буфер 224 реализуется в виде кольцевого буфера с циклическим возвратом от конца к началу. За счет выбора размера буфера 224 равным степени двойки можно использовать двоичный счетчик для выдачи требуемого адреса записи (или считывания). Этот счетчик, естественно, совершает циклический возврат от конца к началу и сбрасывается в нуль, когда при подсчете достигается конец буфера 224.

После сохранения достаточного количества выборок в буфере 224 можно извлечь и обработать некоторый конкретный сегмент выборок из этого буфера. Такой сегмент может включать в себя выборки данных для всего пакета или части пакета. В одном конкретном варианте осуществления каждый сегмент выборок данных соответствует отдельному опорному пилот-сигналу, а размер сегмента ограничен продолжительностью времени, в течение которого канал является когерентным на протяжении опорного пилот-сигнала. В одном варианте осуществления в качестве части обработки пилот-сигнала в контроллере 240 вектор пилот-сигнала, соответствующий опорному пилот-сигналу, претерпевает фазовый сдвиг, соответствующий оценке ошибки по частоте, для формирования оценок пилот-сигнала, которые затем выдаются в блок 230 обработки данных для демодуляции пилот-сигналом. Таким образом, контроллер 240 осуществляет выборку опорного пилот-сигнала в начале сегмента и использует контрольный опорный сигнал для формирования оценок пилот-сигнала на протяжении длительности сегмента. Фазовая ошибка в оценках пилот-сигнала накапливается на протяжении длины сегмента, и таким образом длина сегмента ограничивается для уменьшения накопленной фазовой ошибки в оценках пилот-сигнала. При наличии подобной конструкции не нужно иметь специализированный сложный блок умножения частоты следования элементарных посылок для циклического сдвига самих выборок, что могло бы увеличить сложность блока обработки данных.

Сегменты выборок данных, соответствующие различным копиям сигнала (или сигналам многолучевого распространения), можно обрабатывать последовательно. Например, выборки, соответствующие первому сигналу многолучевого распространения, имеющему нулевой временной сдвиг, можно извлекать из буфера 224 и обрабатывать с помощью блока 230 обработки данных. По завершении обработки первого сигнала многолучевого распространения можно извлечь из буфера 224 и обработать другой сегмент выборок (например, соответствующий второму сигналу многолучевого распространения). Для каждого обрабатываемого сегмента в генератор адресов считывания данных загружен начальный адрес, в котором учитывается (1) произвольный сдвиг между выравниванием выборок при нулевом сдвиге и указателем адреса записи, (2) адрес сегмента относительно начала пакета и (3) временной сдвиг, связанный с обрабатываемым конкретным сигналом многолучевого распространения.

На фиг.6В представлена диаграмма, иллюстрирующая запись псевдослучайных выборок в буфер 224 и считывание псевдослучайных выборок из этого буфера. В одном конкретном варианте осуществления комплексные псевдослучайные выборки, используемые для сжатия получаемых выборок, вычисляются генератором псевдослучайных последовательностей и сохраняются в части буфера 224. И опять, псевдослучайные выборки могут сохраняться по предназначенному адресу. После этого можно извлекать некоторый сегмент псевдослучайных выборок из буфера 224 и использовать для сжатия соответствующего сегмента выборок данных.

Генератор адресов записи псевдослучайных выборок используется для формирования адреса записи псевдослучайной выборки, PW_ADDR, необходимого для считывания сегмента псевдослучайных выборок. Для каждого обрабатываемого сегмента данных, который требует псевдослучайных выборок, в генератор адреса считывания псевдослучайной выборки загружается адрес первой псевдослучайной выборки в сегменте. Каждый из генераторов адресов записи и считывания псевдослучайных выборок соответственно получает приращение после каждой операции записи или считывания псевдослучайных выборок.

Количество псевдослучайных выборок, сохраняемых в буфере 224, может быть установлено на основе ряда факторов и может быть равно количеству сохраняемых выборок данных. Например, можно сохранять два интервала псевдослучайных выборок для двух интервалов выборок данных. Количество сохраняемых псевдослучайных выборок также может зависеть, например, от размера буфера 224, поддерживаемой величины компенсации фазового сдвига сигналов многолучевого распространения и т.п.

На фиг.6С представлена блок-схема конкретного варианта осуществления буферизации данных для конструкции приемного устройства, показанной на фиг.2 и 5. IADC и QADC выборки из аналого-цифровых преобразователей поступают на входной интерфейс 222 данных, который удаляет избыточные выборки, упаковывает выборки в слова и выдает эти слова в мультиплексор 612. Генератор 614 псевдослучайных последовательностей получает псевдослучайную (PN) маску из шины 510 данных, генерирует часть каждой из синфазной псевдослучайной (IPN) и квадратурной псевдослучайной (QPN) последовательностей, используемых для сжатия выборок данных, и выдает генерируемые синфазные псевдослучайные и квадратурные псевдослучайные выборки (в виде слов) в мультиплексор 612. Мультиплексор 612 выдает каждое извлекаемое слово, состоящее либо из выборок данных, либо из псевдослучайных выборок, в ячейку буфера 224, указываемую адресом записи, выдаваемым генератором 220 адресов.

На фиг.6С также показана блок-схема конкретного варианта осуществления генератора 220 адресов, используемого для формирования адресов для буфера 224. Генератор 220 адресов включает в себя генератор 512а адресов записи данных, генератор 512b адресов считывания данных, генератор 512с адресов записи псевдослучайных выборок и генератор 512d адресов считывания псевдослучайных выборок, подключенные к регистрам-фиксаторам 514а, 514b, 514с и 514d соответственно. Генераторы 512а-512d адресов также подключены к мультиплексору 622, который выбирает генерируемый адрес из одного из генераторов 512 адресов и выдает выбранный адрес в буфер 224.

В каждом регистре-фиксаторе 514 хранится некоторое значение, указывающее первый адрес, генерируемый генератором 512 адресов для обрабатываемого сегмента. Например, для считывания некоторого конкретного сегмента данных из буфера 224 адрес первой выборки данных в сегменте выдается в регистр-фиксатор 514b в подходящий момент времени. Генератор 512b адресов считывания данных загружает значение, хранящееся в регистре-фиксаторе 514b, и использует это значение в качестве начального адреса. Последующие адреса считывания данных можно генерировать, например, путем придания приращений счетчику, находящемуся в генераторе 512b адресов считывания данных.

Как описано выше, выборки данных можно сохранять в буфере 224, начиная с некоторой произвольно назначенной ячейки буфера (например, нулевой). Кроме того, буфер 224 выполнен с возможностью хранения некоторого конкретного количества выборок. В одном варианте осуществления буфер 224 имеет размер, равный степени двойки. Вследствие этого можно использовать двоичный счетчик для формирования адреса записи (или считывания) для буфера 224. Этот двоичный счетчик обычно осуществляет циклический возврат к нулю, когда достигается конец буфера.

В одном варианте осуществления, поскольку выборки данных записываются в буфер 224 в последовательном порядке, генератор 512b адресов считывания данных также можно использовать в качестве счетчика выборок, который подсчитывает количество выборок, сохраняемых в буфере 224. Адрес записи данных из генератора 512а адресов выдается в компаратор 628 и сравнивается со значением сравнения, выдаваемым контроллером 240. Это значение сравнения указывает, что сохраняется некоторое конкретное количество выборок (например, один пакет), о котором следовало бы уведомить контроллер 240. Если адрес записи данных равен значению сравнения, то компаратор 628 выдает тактирующий сигнал, отражающий это условие. Этот тактирующий сигнал используется контроллером 240 для инициирования обработки сохраненных выборок.

На фиг.6С также показан конкретный вариант осуществления временной обработки для каждого выделенного сигнала многолучевого распространения. В одном конкретном варианте осуществления контроллер 240 поддерживает синхронизацию конечного автомата 630 для каждого обрабатываемого сигнала многолучевого распространения (например, получаемого с отвода многоотводного приемника). Хотя на фиг.6С это условно показано в виде блока, синхронизация каждого конечного автомата 630 в типичном случае реализуется и поддерживается посредством «зашитых программ» цифровой обработки сигналов. Блок 230 обработки данных может быть настроен на выполнение некоторой части обработки сигнала с целью поиска среди выборок данных тех копий принимаемого сигнала, которые имеют наиболее высокий уровень (например, путем корреляции некоторого сегмента псевдослучайных выборок с некоторым количеством сегментов выборок данных при различных временных сдвигах). Каждый пик корреляции соответствует имеющей высокий уровень (т.е. резко выраженной) копии сигнала. Если пик корреляции превышает некоторый конкретный порог, то контроллер 240 задает новую синхронизацию конечного автомата 630 для сигнала многолучевого распространения, соответствующего пику корреляции. Затем определяется временной сдвиг, соответствующий выделенному сигналу многолучевого распространения, и используется для формирования адреса с целью считывания выборок из буфера 224.

В одном варианте осуществления каждый синхронизированный конечный автомат 630 включает в себя контур 634 слежения за временем, который отслеживает перемещение сигнала многолучевого распространения. Слежение за временем может быть достигнуто путем обработки выборок (например, в соответствии с опорным пилот-сигналом) при сдвигах на +1/2 и -1/2 элементарной посылки, определения разности между накопленными значениями пилот-сигнала при сдвигах на +1/2 и -1/2 элементарной посылки и фильтрации значения разности для формирования некоторого коэффициента коррекции. Таким образом, при движении сигнала многолучевого распространения со временем контур 634 слежения за временем определяет величину перемещения и, соответственно, обновляет временной сдвиг с учетом коэффициента коррекции. Временной сдвиг выдается в блок 636 вычисления данных и адресов псевдослучайных выборок и используется для вычисления начального адреса каждого обрабатываемого сегмента данных. Вычисленный начальный адрес затем выдается в регистр-фиксатор 514b по шине 510 данных в подходящий момент времени.

Как отмечалось выше, выборки сохраняются в буфере 224, начиная с некоторой предназначенной ячейки в памяти, в произвольный момент времени. В результате начальные выборки для каждой копии сигнала, подлежащей обработке, могут соответствовать какой-либо ячейке в буфере 224. В одном конкретном варианте осуществления контур 634 слежения за временем используется для определения начального местоположения принимаемого пакета данных для каждой обрабатываемой копии сигнала. Контур 634 слежения за временем обрабатывает получаемые выборки, чтобы определить конкретный временной сдвиг для копии принимаемого сигнала. Этот временной сдвиг затем используется для формирования начального адреса для каждого сегмента обрабатываемых выборок.

Конечные автоматы 630 могут быть реализованы с помощью контроллера 240, в котором используются «зашитые» программы цифровой обработки сигналов и имеется базовый набор элементов для обработки. Например, единственный контур 634 слежения за временем и единственный блок 636 вычисления данных и адресов псевдослучайных выборок могут быть мультиплексированными с разделением времени и использоваться для реализации всех проиллюстрированных конечных автоматов 630. Контроллер 240 может поддерживать отдельный регистр для хранения временного сдвига, связанного с каждым проиллюстрированным конечным автоматом 630.

В одном варианте осуществления для обработки прямой линии связи в удаленном терминале контроллер 240 также поддерживает контур 638 слежения за частотой, который задает частоту источника сигналов синхронизации равной частоте следования (скорости передачи) данных, применяемой для выборок данных. Контур слежения за частотой может быть выполнен с возможностью определения величины циклического фазового сдвига опорных пилот-сигналов, использования информации о фазах, чтобы определить, является частота следования синхронизирующих импульсов выше или ниже частоты следования элементарных посылок, и соответствующего регулирования частоты источника синхронизирующих импульсов. Если частота синхронизирующих импульсов фиксируется равной частоте следования элементарных посылок, то для каждого кадра выдается некоторое конкретное количество выборок (например, 2048). Таким образом, когда частота фиксирована, можно интерпретировать прием некоторого кадра выборок подсчетом количества выборок, записываемых в буфер 224.

На фиг.6С также показана блок-схема конкретного варианта осуществления генератора 236 адресов, используемого для формирования адресов для блока 234 буферизации и обращенного перемежения. Генератор 236 адресов включает в себя генератор 542а адресов записи символов и генератор 542b адресов считывания символов, подключенных к регистрам-фиксаторам 544а и 544b соответственно. Генераторы 542а и 542b адресов также подключены к мультиплексору 546, который выбирает формированный адрес из генераторов 542а и 542b адресов и выдает выбранный адрес в блок 234 буферизации и обращенного перемежения.

В каждом регистре-фиксаторе 544 хранится некоторое значение, указывающее первый адрес, генерируемый генератором 542 адресов для обрабатываемого сегмента. Начальные значения, выдаваемые в регистры-фиксаторы 514, в общем случае связаны со значениями, выдаваемыми в регистры-фиксаторы 544, но выдаются они с учетом различных факторов, например, таких как задержка обработки в блоке 230 обработки данных. Генератор 542а адресов считывания символов загружает значение, хранящееся в регистре-фиксаторе 544а, и использует это загруженное значение в качестве начального адреса. Последующие адреса считывания символов можно генерировать, например, путем придания приращений счетчику, находящемуся в генераторе 542а адресов считывания символов.

В одном варианте осуществления блок 234 буферизации и обращенного перемежения используется для хранения промежуточных и конечных результатов суммирования с накоплением символов для многочисленных сигналов многолучевого распространения. Сначала производится обработка выборок для некоторого конкретного сигнала многолучевого распространения, а получаемые символы сохраняются в конкретных ячейках блока 234 буферизации и обращенного перемежения. Чтобы упростить адресацию, символы для некоторого конкретного сигнала многолучевого распространения (например, первого из обрабатываемых) можно сохранять в блоке 234 буферизации и обращенного перемежения, начиная с некоторой предназначенной ячейки (например, имеющей нулевой адрес NS, и т.п.). Для каждого последующего сигнала многолучевого распространения, демодулированные символы для такого сигнала многолучевого распространения можно объединять с соответствующими сохраненными символами для ранее обработанных сигналов многолучевого распространения. Эти объединенные символы потом снова сохраняют в тех же ячейках в блоке 234 буферизации и обращенного перемежения. Таким образом, символы для многочисленных обрабатываемых сигналов многолучевого распространения объединяются «на месте» с соответствующими ранее накопленными символами. Когда нужно объединить символы для многочисленных сигналов многолучевого распространения, генератор 236 адресов генерирует надлежащие адреса считывания и записи символов, определяемые значениями, хранящимися в регистрах-фиксаторах 544а и 544b.

Во многих системах связи, включая систему МДКР ВСПД, перемежение используется для обеспечения временного разнесения в передаваемых данных. Перемежение уменьшает вероятность приема цепочки последовательных ошибок, вызываемых, например, импульсным шумом. В приемном устройстве происходит переупорядочение принимаемых символов. Это переупорядочение может обеспечить эффективное расширение цепочки символов, принимаемых с ошибками, на весь кадр, что может увеличить вероятность правильного декодирования принимаемых символов. Перемежение осуществляется в передающем устройстве, так что временное разнесение достигается раньше декодирования в приемном устройстве.

В одном варианте осуществления блок 234 буферизации и обращенного перемежения также используется для обеспечения обращенного перемежения обрабатываемых символов. В одном варианте осуществления обрабатываемые символы записываются в блок 234 буферизации и обращенного перемежения в последовательном порядке, а считываются в псевдослучайном, но детерминистском порядке, определяемом конкретным реализуемым алгоритмом перемежения. Поскольку символы считываются не в последовательном порядке, блок 234 буферизации и обращенного перемежения сначала заполняется символами, соответствующими продолжительности осуществления перемежения. Например, в системе МДКР ВСПД перемежение осуществляется на протяжении каждого кадра данных. Таким образом, в приемном устройстве весь кадр символов обрабатывается и сохраняется в блоке 234 буферизации и обращенного перемежения. После обработки всего кадра символы для этого кадра считываются в последующий декодер. В одном конкретном варианте осуществления текущий кадр обрабатывается и сохраняется в одной секции блока 234 буферизации и обращенного перемежения, а ранее обработанный кадр может быть извлечен из другой секции блока 234 буферизации и обращенного перемежения.

Генератор 542b адресов считывания символов включает в себя схемы, необходимые для формирования надлежащих адресов символов, выдаваемых в блок 524 демодуляции и объединения символов, чтобы осуществить накопление символов, а затем символы выдаются в последующий декодер 260 для декодирования. Адреса считывания символов для упомянутых двух «пунктов назначения» можно генерировать путем мультиплексирования с разделением времени. Например, символы можно выдавать в блок 524 демодуляции и объединения символов и декодер 260 на протяжении чередующихся циклов считывания. В альтернативном варианте можно выдавать группу символов в блок 524 демодуляции и объединения символов, а затем выдавать группу символов в декодер 260.

На фиг.7А представлена блок-схема конкретного варианта осуществления коррелятора 522 в блоке 230 обработки данных. В одном варианте осуществления коррелятор 522 выполнен с возможностью поддержки некоторого количества функций, включая, например, сжатие выборок данных с помощью комплексных псевдослучайных сжимающих последовательностей, накопление многочисленных сжатых выборок для каждого периода следования элементарной посылки, а также интерполяцию. Для достижения улучшенной рабочей характеристики коррелятор 522 может быть выполнен с возможностью работы с несколькими комплексными выборками одновременно (например, их количество может достигать четырех). Для коррелятора 522 могут быть реализованы другие конструкции и функции, которые находятся в рамках объема притязаний изобретения.

В одном варианте осуществления для каждого цикла считывания данных из буфера 224 извлекаются четыре пары преобразованных в цифровую форму синфазных и квадратурных выборок IADC и QADC из аналого-цифровых преобразователей (т.е. четыре комплексных выборки данных), которые фиксируются регистрами-фиксаторами 712а-712d. В следующем цикле считывания данных выборки из регистров-фиксаторов 712а-712d также фиксируются регистрами-фиксаторами 714а-714d соответственно и следующие четыре пары преобразованных в цифровую форму синфазных и квадратурных выборок IADC и QADC из аналого-цифровых преобразователей фиксируются регистрами-фиксаторами 712а-712d. В одном конкретном варианте осуществления по две выборки данных выдаются в течение каждого периода следования элементарной посылки (то есть получается период двойной выборки), а двойная фиксация регистрами-фиксаторами 712 и 714 обеспечивает обработку либо своевременной (OT) выборки, либо запаздывающей (LT) выборки каждой элементарной посылки.

Мультиплексоры 716а-716d также получают зафиксированные выборки из регистров-фиксаторов 712а-712d соответственно и зафиксированные выборки из регистров-фиксаторов 714а-714d соответственно. Каждый мультиплексор 716 выдает одну из полученных выборок, в зависимости от того, какая выборка - своевременная или запаздывающая - подлежит обработке, в соответствующий из логических элементов «И», обозначенных позицией 718. Логические элементы «И», обозначенные позициями 718а и 718b, также получают управляющий сигнал ZERO_0, а логические элементы «И», обозначенные позициями 718с и 718d, также получают управляющий сигнал ZERO_1. Каждый из логических элементов 718 «И» выдает либо полученную выборку, либо нулевое значение («0») в соответствующий блок 720 умножения, в зависимости от управляющего сигнала ZERO_х.

В одном конкретном варианте осуществления буфер 224 также предназначен и применяется для хранения синфазных псевдослучайных и квадратурных псевдослучайных последовательностей, используемых для сжатия выборок данных. В одном конкретном варианте осуществления на протяжении каждого цикла считывания псевдослучайных выборок имеющий длину 16 элементарных посылок сегмент комплексной псевдослучайной сжимающей последовательности, соответствующий обрабатываемым выборкам данных, извлекается из буфера 224, фиксируется регистром-фиксатором 732 и выдается в мультиплексор 734. Мультиплексор 734 выбирает часть (например, часть, содержащую 2 элементарные посылки) зафиксированного сегмента комплексной псевдослучайной последовательности и выдает выбранную часть в регистр 736 циклического сдвига. Затем этот регистр 736 выдает надлежащие синфазные псевдослучайные и квадратурные псевдослучайные выборки в каждый из блоков 718а-718d умножения.