ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится, в общем, к процессорам и, в частности, к системе и способу отладки кода на процессоре посредством схемы отладки, которые включают в себя рассмотрение режима обработки набора команд процессора.

УРОВЕНЬ ТЕХНИКИ

Современные процессоры являются чрезвычайно сложными системами. Большинство современных процессоров используют конвейерную архитектуру, где последовательные команды, каждая из которых имеет множество этапов исполнения, совмещаются при выполнении. Множество процессоров, известных как "суперскалярные" процессоры, включают два или более отдельных конвейера для параллельного выполнения команд. Чтобы избежать остановов в конвейере из-за команд ветвления, большинство процессоров использует различные формы предсказания переходов со спекулятивной выборкой и выполнением команд при принятии предсказанных переходов. Чтобы улучшить производительность, множество современных процессоров отделяют логические адреса регистра от соответствующих физических регистров памяти, что известно как переименование регистров. Чтобы предоставить программам иллюзию неограниченной и быстродействующей памяти, множество процессоров выполняют код в виртуальном адресном пространстве, транслируя адреса в одно или более физических адресных пространств, когда данные проходят через иерархию памяти (например, регистр, кэш, оперативная память). При такой сложности выполнение кода в рамках современного процессора очень трудно точно проследить и проверить правильность выбора. В частности, аномальные ситуации могут быть очень сложны в отладке.

Кроме того, само программное обеспечение, которое выполняется на современных процессорах, чрезвычайно сложно. С появлением архитектур процессоров с сокращенным набором команд (RISC) большая часть вычислительной и логической сложности вычисления перемещена от команд процессора к оптимизирующим компиляторам. Таким образом, компиляторы создают сложные операции из относительно маленького набора команд процессора, каждая из которых оптимизирована для определенной, конкретной функции. Это приводит к более длинной и сложной последовательности команд, включающих, например, логические, арифметические, загрузочные/сохраняющие операции и операции ветвления для данной вычислительной задачи. Такой сложный код может быть сложным в отладке, когда ошибки вызывают аномальное поведение программы.

Чтобы содействовать задаче подчинения отладки сложного кода, выполняющегося на сложном процессоре, во многие процессоры встроены инструменты отладки. Они могут включать в себя компараторы адреса и данных для того, чтобы идентифицировать определенные команды и/или шаблоны данных. Отладчики могут дополнительно включать в себя компараторы адресного интервала так, чтобы отладка или отслеживание могли быть ограничены предопределенными кодовыми сегментами. Другие инструменты отладки могут включать в себя счетчики, задатчики последовательности и т.п., чтобы предоставить гибкость в определении условий, которые определяют точки останова и/или отслеживают инициирующие механизмы. Трассировочная информация может быть предоставлена вне кристалла, например через выделенную шину, или может быть сохранена в выделенном на кристалле буфере. Точки остановов могут инициировать один или более внешних сигналов, например, таких, чтобы вызвать срабатывание и/или запуск логического анализатора или подсвечивание светодиода; могут вызвать исключительную ситуацию, выполнение кода ветвления к подпрограмме отладки; или могут просто остановить выполнение, позволяя производить просмотр содержимого регистров и кэшей. Эти инструменты отладки, которые не используются во время нормальной работы процессора, встроены в схемы процессора таким образом, чтобы минимизировать воздействие на производительность процессора и потребляемую мощность.

Программисты могут явно установить надлежащий режим обработки набора команд в программном обеспечении до выполнения команд согласно релевантному кодированию набора команд. Однако неправильное программное обеспечение может время от времени выполнять переход к специфическому адресу команды, который был предназначен для выполнения в одном режиме обработки набора команд, в то время как процессор находится фактически в некотором другом режиме обработки набора команд. В таком случае процессор может попытаться выполнить команду по этому адресу, используя неподходящее декодирование набора команд, приводящее к неправильным результатам.

Например, некоторые версии архитектуры семейства процессоров ARM содержат по меньшей мере два набора команд режимов обработки: 32-разрядный режим ARM и 16-разрядный режим "Thumb". В таблице 1 представлен фрагмент кода команд ARM:

Режим ARM кодирования команд

В таблице 2 представлен тот же самый код, интерпретированный в режиме "Thumb":

Кодирование команды в режима "Thumb"

Отметим, в частности, команды перехода в 96F2, 96FA и 96FE. Ввиду ошибочного перехода может быть трудно установить место, в котором ошибка вызвала код ARM Таблицы 1, чтобы быть интерпретированной в режиме "Thumb", как в таблице 2, и, следовательно, отладить ошибку. Эта трудность возникает, потому что схемы отладки, известные из предшествующего уровня техники, не включают в себя режим обработки набора команд процессора как входные данные для логики, которая вызывает точки останова, инициализирует трассировки и тому подобное.

Большинство процессоров, которые поддерживают два или более "режимов" обработки, как, например, привилегированные (супервизора) и непривилегированные (пользовательские) режимы, или реальные и защищенные режимы, переключаются между режимами посредством вызова исключительной ситуации и выполнения перехода к подпрограмме переключения режимов. Эта операция легко обнаруживается, используя инструменты отладки, известные из предшествующего уровня техники, и программное обеспечение, посредством установки точки останова или начала трассировки на адрес команды подпрограммы переключения режимов. Переключение режимов обработки набора команд процессором без получения исключительной ситуации является одним примером поведения кода, который является трудным в диагностике с помощью инструментов отладки, известных из уровня техники, которые не включают в себя режим обработки набора команд процессором в качестве рассмотрения при вызове точек остановов, инициализации трассировки и т.п.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Технический результат, на достижение которого направлено настоящее изобретение, заключается в повышении эффективности отладки команд в процессоре посредством использования режима обработки набора команд процессора.

Согласно одному или более варианту осуществления схема отладки в процессоре, выполняющем два или более наборов команд, идентифицирует адрес, по которому процессор переключается из одного режима обработки набора команд на другой режим обработки набора команд, и выводит предупреждение или указатель (индикацию) переключения режима. Предупреждение или индикация могут содержать сигнал точки останова, который останавливает выполнение и/или является выходным сигналом в качестве внешнего сигнала процессора. Адрес команды, по которому процессор переключает режим обработки набора команд, может быть дополнительно выведен. Альтернативно, предупреждение или индикация могут включать в себя начало или окончание трассировочной операции, вызов исключительной ситуации или любую другую известную функцию отладчика.

Один вариант осуществления относится к способу отладки программного кода, содержащего множество команд, на процессоре, имеющем по меньшей мере два различных режима обработки набора команд. Целевой режим обработки набора команд принимается до выполнения любых команд кода. Команды кода выполняются, и для каждой выполняемой команды текущий режим обработки набора команд процессора сравнивается с целевым набором команд режима обработки. Предупреждение инициируется, если текущий режим обработки набора команд процессора соответствует целевому режиму обработки набора команд.

Другой вариант осуществления относится к способу выполнения программного обеспечения на процессоре, имеющем по меньшей мере первый и второй режимы обработки набора команд. Адрес, по которому процессор переключает первый режим обработки набора команд на второй режим обработки набора команд, идентифицируется, и предупреждение инициируется в ответ на идентификацию.

Еще один вариант осуществления относится к процессору, выполненному с возможностью выполнения команд согласно двум или более кодированиям набора команд, причем каждый - в отличных режимах обработки наборов команд. Процессор включает в себя индикатор текущего режима обработки набора команд и местоположение хранения данных для сохранения индикатора целевого режима обработки набора команд. Процессор также включает в себя исполнительный блок, выполненный с возможностью осуществлять команды согласно текущему режиму обработки набора команд, и схему сравнения, выполненную с возможностью сравнивать текущий режим обработки набора команд с целевым режимом обработки набора команд при выполнении каждой команды, и вывода индикации, если текущий режим обработки набора команд соответствует целевому режиму обработки набора команд.

Еще один вариант осуществления относится к процессору, выполненному с возможностью осуществления двух или более кодирований набора команд, причем каждый - в отличном режиме обработки набора команд. Процессор включает в себя схему сравнения, выполненную с возможностью обнаруживать изменение в режиме обработки набора команд и выводить индикацию относительно изменения режима обработки набора команд, и адрес команды, по которому это изменение происходит, в ответ на обнаружение.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 является функциональной блок-схемой процессора.

Фиг.2 является функциональной блок-схемой конвейера процессора, включая схему отладки.

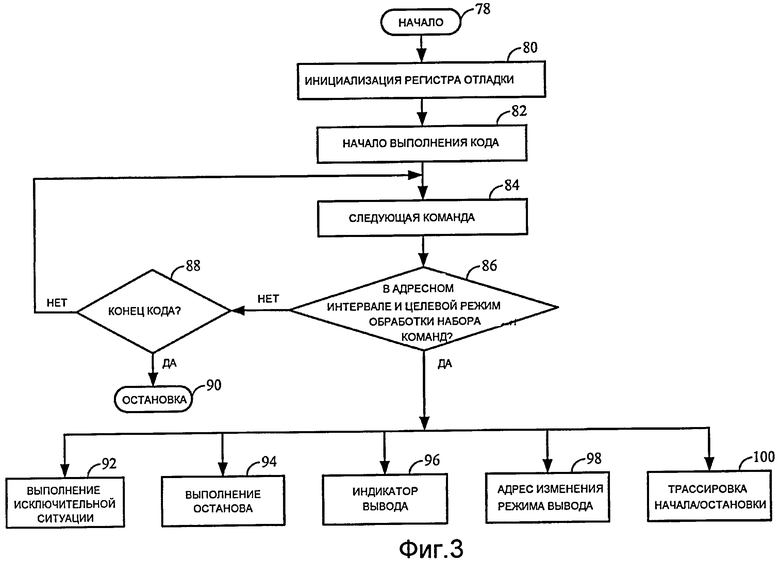

Фиг.3 является блок-схемой последовательности операций процесса диагностики/отладки.

ПОДРОБНОЕ ОПИСАНИЕ

Фиг.1 иллюстрирует функциональную блок-схему процессора 10. Процессор 10 выполняет команды в конвейере 12 выполнения команды согласно логике 14 управления. Логика 14 управления поддерживает счетчик 15 программы (PC), и устанавливает и очищает биты в одном или более регистрах 16 состояния для указания, например, текущего режима обработки набора команд, информации относительно результатов арифметических операций и логических сравнений (нуль, перенос, равно, не равно) и т.п. В некоторых вариантах осуществления конвейер 12 может быть суперскалярной конструкцией с множественными параллельными конвейерами. Конвейер 12 может также называться как исполнительный блок. Файл 20 регистров общего назначения (GPR) предоставляет регистры, доступные конвейеру 12, и представляет собой вершину иерархии памяти.

Процессор 10, который выполняет команды по меньшей мере из двух наборов команд в различных режимах обработки набора команд, дополнительно включает в себя схему 18 отладки, выполненную с возможностью сравнивать, при выполнении каждой команды, по меньшей мере заранее определенный целевой режим обработки набора команд и текущий режим обработки набора команд и предоставлять индикацию соответствия между двумя режимами. Схема 18 отладки описана более подробно ниже.

Конвейер 12 осуществляет выборку команд из кэша 26 команд (I-кэш) с трансляцией адреса памяти и разрешениями, управляемыми буфером предыстории трансляции команд (ITLB) 28. К данным обращаются из кэша 30 данных (D-кэш) с трансляцией адреса памяти и разрешениями, управляемыми основным буфером предыстории трансляции 32 (TLB). В различных вариантах осуществления ITLB 28 может включать в себя копию части TLB 32. Альтернативно, ITLB 28 и TLB 32 могут быть интегрированы. Точно также в различных вариантах осуществления процессора 10, I-кэш 26 и D-кэш 30 могут быть интегрированы или объединены. Промахи в I-кэше 26 и/или D-кэше 30 вызывают обращение к основной памяти (вне кристалла) 38, 40 с помощью интерфейса 34 памяти. Интерфейс 34 памяти может быть основным входом в шинное соединение 42, реализующее совместно используемую шину для одного или более устройств 38, 40 памяти. Дополнительные основные устройства (не показанные) могут дополнительно подключиться к шинному соединению 42.

Процессор 10 может включать в себя интерфейс 44 ввода/вывода (I/O), который может быть ведущим устройством на периферийной шине, через которую интерфейс 44 I/O может обратиться к различным периферийным устройствам 48, 50. Для специалистов в данной области техники понятно, что возможны многочисленные изменения процессора 10. Например, процессор 10 может включать в себя кэш второго уровня (L2) для одного или для обоих I- и D-кэшей 26, 30. Кроме того, один или более функциональных блоков, изображенных в процессоре 10, могут быть не включены в конкретный вариант осуществления. Другие функциональные блоки, которые могут постоянно находиться в процессоре 10, например, контроллер JTAG, предварительный декодер команд, целевой кэш адреса перехода и т.п., не относятся к описанию настоящего изобретения и исключены для ясности.

Фиг.2 иллюстрирует функциональную блок-схему одного варианта осуществления схемы 18 отладки. Схема 18 отладки включает в себя регистр 52 целевого режима обработки набора команд, регистр 54 адреса начала адресного интервала и регистр 56 адреса конца адресного интервала. Регистры 52, 54, 56 загружаются программистами с помощью диагностического программного обеспечения до операции диагностики/отладки. Значение, записанное в регистр 52 целевого режима обработки набора команд, сравнивается с текущим режимом обработки набора команд процессора во время выполнения каждой команды для инициирования точки останова, трассировочной функции или другого предупреждения. Значения регистров 54, 56 начального и конечного адреса являются началом и концом, соответственно, целевого адресного интервала, по которому схема 18 отладки должна контролировать соответствие между текущим и целевым режимом обработки набора команд.

Для специалистов в данной области техники понятно, что схема 18 отладки может включать в себя дополнительные настраиваемые параметры и дополнительные функциональные блоки, разрешающие точки останова, трассировки и т.п. для инициирования в широком спектре условий. Эти блоки не отражены на фиг.2 для ясности, но вообще могут включать в себя все параметры схемы отладки и функциональные возможности, известные из уровня техники.

До выполнения диагностики/отладки программист загружает регистры 54, 56 начального и конечного адреса, чтобы определить целевую область адреса, которая может колебаться от одного адреса до всего адресного интервала тестируемого кода. В других вариантах осуществления множество регистров начального и конечного адреса могут быть предоставлены, чтобы определить множество целевых адресных интервалов. Программист дополнительно загружает регистр 52 целевого режима обработки набора команд. Например, в случае процессора ARM, выполняющего код полностью в режиме ARM, программист может загрузить регистр 52 значением, указывающим режим "Thumb", устанавливать точки останова, побуждающие схему 18 отладки остановить выполнение, например, если процессор 10 выполняет команду в пределах адресного интервала, определенного регистрами 54, 56 в режиме "Thumb".

Во время операции диагностики/отладки значение, сохраненное в регистре 52 целевого режима обработки набора команд, сравнивается с битом регистра состояния, указывающим текущий режим обработки набора команд процессора 10 в логике сравнения, таком как вентиль 58 AND. Например, в процессоре 10 ARM бит 5 из регистра 16 состояния текущей программы (CPSR) может быть проверен. Выходной сигнал 60 из логики 58 сравнения будет установлен, только когда текущий режим обработки набора команд процессора 10 сопоставляется с режимом обработки набора команд, указанным регистром 52 целевого режима обработки набора команд.

В вариантах осуществления, где процессор 10 выполняет команды из более чем двух наборов команд в различных режимах обработки набора команд, регистр 52 целевого режима обработки набора команд и биты индикатора режима CPSR (или другой регистр состояния) 16 будут включать многобитовые значения, и логика 58 сравнения может включать в себя дополнительные схемы, например, декодеры. В различных вариантах осуществления другие индикации относительно текущего режима обработки набора команд используются вместо CPSR 16, например, выходной сигнал логики декодирования команд.

Одновременно, текущее значение PC 15 сравнивается с регистрами 54, 56 адресного интервала в логике 68 сравнения адреса. Выходной сигнал 70 из логики 68 сравнения адреса устанавливается всякий раз, когда текущее значение PC 15 находится в пределах целевого адресного интервала. В различных вариантах осуществления индикации относительно "текущего" адреса команды могут отличаться от PC 15, как требуется или задано. Например, схема 68 сравнения адреса может сравнивать адреса команд на этапе (каскаде) декодирования в конвейере 12, каскаде выполнения, или любом другом каскаде конвейера. Кроме того, может использоваться другой динамический адрес, как, например, адрес последней команды в конвейере 12, для фиксации выполнения.

Выходной сигнал 70 из логики 68 сравнения адреса объединяется посредством операции AND с выходным сигналом 60 из логики 58 сравнения индикатора режима обработки набора команд в AND вентиле 72 для формирования выходного сигнала 20, указывающего соответствие в данный период времени между текущим и целевым режимом обработки набора команд, происходящее в пределах целевого адресного интервала. В одном варианте осуществления выходной сигнал 20 предоставляется как выходной сигнал процессора (см. фиг.1). Этот выходной сигнал 20 может побуждать и/или инициировать логический анализатор, подсветить светодиод или вызвать некоторое другое действие или сигнал тревоги. В одном варианте осуществления, как изображено на фиг.1, выходной сигнал 20 индикатора о соответствии режима обработки набора команд может являться входящим сигналом на контроллер 14 для остановки выполнения процессором 10.

В одном варианте осуществления выходной сигнал 20 индикатора о соответствии режима обработки набора команд может инициализировать или останавливать операцию трассировки команды, с трассировочной информацией, направляемой к выходным контактам процессора 10 или сохраняемой в находящемся на кристалле буфере трассировки (не показан). В одном варианте осуществления, как показано на фиг.2, выходной сигнал 20 индикатора о соответствии режима обработки набора команд может переключать регистр 74 адреса соответствия режима обработки набора команд, фиксируя значение PC 15, и, следовательно, адрес команды, при которой соответствие может быть обнаружено между текущим и целевым режимом обработки набора команд. Это может быть особенно важным в обнаружении смены одного режима обработки набора команд на другой. Выходной сигнал 76 из этого регистра 74 может быть направлен к выводам процессора 10 для внешнего просмотра.

В одном варианте осуществления выходной сигнал 20 индикатора о соответствии режима обработки набора команд может вызывать исключительную ситуацию, выполнение кода ветвления к предопределенной подпрограмме. Эта подпрограмма соответствия режима набора команд может, например, считывать регистр 74 адреса соответствия режима обработки набора команд. В общем, выходной сигнал 20 индикатора о соответствии режима обработки набора команд может запускать любую известную операцию отладки, как требуется или задано.

Фиг.3 иллюстрирует способ отладки кода согласно одному или более вариантам осуществления настоящего изобретения. Начиная с этапа 78, программист инициализирует регистры схемы отладки (этап 80). Это может содержать, например, загрузку регистра 52 целевого режима обработки набора команд и установку целевого адресного интервала посредством загрузки регистра 54 начального адреса и регистра 56 конечного адреса. Дополнительные регистры схемы отладки (не показаны) могут быть инициализированы, как требуется или задано.

Далее программист начинает выполнение кода, который должен быть отлажен (этап 82), последовательно выбирая и выполняя следующую команду (этап 84) в последовательности кода. Независимо от адреса, если текущий режим обработки набора команд процессора 10 не соответствует таковому, установленному программистом в регистре 52 целевого режима обработки набора команд (этап 86), то следующая команда выбирается и выполняется (этап 84) до окончания кода, подлежащего отладке (этап 88), при котором способ останавливается на этапе 90.

Если при выполнении команды (этап 84) адрес команды находится в пределах предопределенного адресного интервала, и текущий режим обработки набора команд соответствует установленному программистом в регистре 52 целевого режима обработки набора команд (этап 86), то схема отладки устанавливает выходной сигнал 20 и может выбрать любое число действий, как определено программистом.

Например, выходной сигнал 20 схемы отладки может побудить процессор 10 принимать исключительную ситуацию, выполнение кода ветвления к подпрограмме соответствия режима обработки набора команд (этап 92). Выходной сигнал 20 схемы отладки может побудить контроллер 14 конвейера останавливать выполнение (этап 94), разрешая программисту проверить содержимое различных регистров, строк кэша и т.п. Схема 18 отладки может установить выходной сигнал 20 внешне (этап 96), который может использоваться для задания или запуска логического анализатора, подсвечивания светодиода или т.п. Схема 18 отладки может дополнительно выводить адрес соответствия режима обработки набора команд для внешнего просмотра (этап 98). Схема 18 отладки может начинать или заканчивать трассировочную операцию (этап 100). Несмотря на то, что схема 18 отладки изображена как альтернатива, в данном варианте осуществления она может выполнить два или более этапов 92-96. В общем, схема 18 отладки может предпринять любое действие, известное в предшествующем уровне техники, которое выгодно для отладки кода на процессоре 10, после обнаружения соответствия между текущим режимом обработки набора команд и целевым режимом обработки набора команд.

Термин "набор команд", как используется здесь, относится к набору кодов, посредством которого данные команд (например, содержимое строки I-кэша) интерпретируются процессором 10 как выполнимые команды. Термин "режим обработки набора команд" относится к идентифицируемому режиму работы процессора 10, в котором данные команд интерпретируются согласно определенному кодированию набора команд. В частности, "режим обработки набора команд" отличается от известных "режимов" обработки процессором, например, разрешениями (например, режим супервизора и пользовательский), адресацией памяти (например, реальный и защищенный режим) и т.п.

Хотя настоящее изобретение было описано здесь относительно конкретных признаков, аспектов и вариантов осуществления, очевидно, что многочисленные изменения, модификации и другие варианты осуществления возможны в пределах широкой области применения настоящего изобретения, и, соответственно, все изменения, модификации и воплощения должны попадать в рамки изобретения. Поэтому настоящие варианты осуществления должны быть рассмотрены во всех аспектах как иллюстративные и без ограничений и должны содержать все изменения, находящиеся в пределах объема и формы эквивалентов приложенной формулы изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДРЕСАЦИЯ РЕГИСТРОВ В УСТРОЙСТВЕ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2193228C2 |

| ВЫБОРКА КОМАНД ПО УКАЗАНИЮ В СРЕДСТВЕ СБОРА СВЕДЕНИЙ О ХОДЕ ВЫЧИСЛЕНИЙ | 2013 |

|

RU2585982C2 |

| УПРАВЛЕНИЕ В РЕЖИМЕ НИЗКИХ ПРИВИЛЕГИЙ РАБОТОЙ СРЕДСТВА СБОРА СВЕДЕНИЙ О ХОДЕ ВЫЧИСЛЕНИЙ | 2013 |

|

RU2585969C2 |

| ЗАПОМИНАНИЕ ОПЕРАНДОВ СТЕКА В РЕГИСТРЕ | 2001 |

|

RU2271565C2 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОТВРАЩЕНИЯ НЕСАНКЦИОНИРОВАННОГО ПЕРЕМЕЩЕНИЯ СТЕКА | 2014 |

|

RU2629442C2 |

| СБОР СВЕДЕНИЙ О ХОДЕ ВЫЧИСЛЕНИЙ | 2013 |

|

RU2585968C2 |

| РЕЖИМ СЛЕЖЕНИЯ В УСТРОЙСТВЕ ОБРАБОТКИ В СИСТЕМАХ ТРАССИРОВКИ КОМАНД | 2013 |

|

RU2635044C2 |

| СРЕДСТВО ДЛЯ УСТАНОВКИ КЛЮЧА БЕЗ ПЕРЕВОДА В ПАССИВНОЕ СОСТОЯНИЕ | 2010 |

|

RU2542953C2 |

| Связанное с выбранными архитектурными функциями администрирование обработки | 2015 |

|

RU2665243C2 |

| РАСШИРЕНИЕ СОГЛАСУЮЩЕГО ПРОТОКОЛА ДЛЯ ИНДИКАЦИИ СОСТОЯНИЯ ТРАНЗАКЦИИ | 2015 |

|

RU2665306C2 |

Изобретения относятся к системам и способам отладки кода на процессоре посредством схемы отладки. Техническим результатом является повышение эффективности отладки команд в процессоре. Процессор в одном из вариантов содержит индикатор текущего режима обработки набора команд, место хранения данных, выполненное с возможностью хранить индикатор целевого режима обработки набора команд, исполнительный блок, выполненный с возможностью выполнения команд согласно текущему режиму обработки набора команд, и схему сравнения, выполненную с возможностью сравнивать текущий режим обработки набора команд и целевой режим обработки набора команд при выполнении каждой команды и выводить индикацию, если текущий режим обработки набора команд соответствует целевому режиму обработки набора команд. 4 н. и 24 з.п. ф-лы, 3 ил., 2 табл.

1. Способ отладки кода программного обеспечения, содержащего множество команд на процессоре, имеющем по меньшей мере два различных режима обработки набора команд, содержащий этапы, на которых:

принимают целевой режим обработки набора команд до выполнения любых команд кода;

выполняют команды кода и для каждой выполненной команды сравнивают текущий режим обработки набора команд процессора с целевым режимом обработки набора команд; и

формируют предупреждение, если текущий режим обработки набора команд процессора соответствует целевому режиму обработки набора команд.

2. Способ по п.1, в котором предупреждение содержит остановку выполнения команды.

3. Способ по п.1, в котором предупреждение содержит управление трассировочной операцией.

4. Способ по п.1, в котором предупреждение содержит вызов исключительной ситуации.

5. Способ по п.1, в котором предупреждение содержит выведение сигнала, указывающего о соответствии между текущим режимом обработки набора команд процессора и целевым режимом обработки набора команд.

6. Способ по п.1, в котором предупреждение содержит выведение адреса команды, для которой текущий режим обработки набора команд процессора соответствует целевому режиму обработки набора команд.

7. Способ по п.1, дополнительно содержащий этапы, на которых:

принимают целевой адресный интервал до выполнения любых команд кода;

для каждой выполненной команды сравнивают текущий адрес команды с целевым адресным интервалом; и

формируют предупреждение, только если текущий режим обработки набора команд процессора соответствует целевому режиму обработки набора команд, и текущий адрес команды находится в пределах целевого адресного интервала.

8. Способ выполнения программного обеспечения на процессоре, имеющем по меньшей мере первый и второй режимы обработки набора команд, содержащий этапы, на которых:

идентифицируют адрес, по которому процессор переключает первый режим обработки набора команд на второй режим обработки набора команд; и

формируют предупреждение в ответ на идентификацию.

9. Способ по п.8, в котором предупреждение содержит остановку выполнения команды.

10. Способ по п.8, в котором предупреждение содержит управление трассировочной операцией.

11. Способ по п.8, в котором предупреждение содержит вызов исключительной ситуации.

12. Способ по п.8, в котором предупреждение содержит выведение индикатора сигнала, указывающего об изменении режима обработки набора команд.

13. Способ по п.8, в котором предупреждение содержит выведение адреса идентифицированной команды.

14. Способ по п.8, в котором идентифицирование адреса, по которому процессор переключает первый режим обработки набора команд на второй режим обработки набора команд, содержит идентифицирование адреса, только если он находится в пределах предопределенного адресного интервала.

15. Процессор, выполненный с возможностью выполнять команды согласно двум или более кодированиям набора команд, каждый - в отличном режиме обработки набора команд, содержащий:

индикатор текущего режима обработки набора команд;

место хранения данных, выполненное с возможностью хранить индикатор целевого режима обработки набора команд;

исполнительный блок, выполненный с возможностью выполнения команд согласно текущему режиму обработки набора команд; и

схему сравнения, выполненную с возможностью сравнивать текущий режим обработки набора команд и целевой режим обработки набора команд при выполнении каждой команды и выводить индикацию, если текущий режим обработки набора команд соответствует целевому режиму обработки набора команд.

16. Процессор по п.15, в котором индикация содержит сигнал, служащий для остановки выполнения команды.

17. Процессор по п.15, в котором индикация содержит сигнал, служащий для управления трассировочной операцией.

18. Процессор по п.15, в котором индикация содержит сигнал, служащий для вызова исключительной ситуации.

19. Процессор по п.15, в котором индикация содержит сигнал, указывающий, что текущий режим обработки набора команд соответствует целевому режиму обработки набора команд.

20. Процессор по п.15, в котором индикация содержит адрес выполняемой команды, когда соответствие обнаружено между текущим режимом обработки набора команд и целевым режимом обработки набора команд.

21. Процессор по п.15, дополнительно содержащий местоположение хранения данных, выполненное с возможностью хранения целевого адресного интервала, и причем схема сравнения выполнена с возможностью выводить индикацию, только если текущий режим обработки набора команд соответствует целевому режиму обработки набора команд, и адрес команды, которая выполняется в текущий момент, находится в пределах целевого адресного интервала.

22. Процессор, выполненный с возможностью выполнять два или более кодирований набора команд, каждый - в отличном режиме обработки набора команд, содержащий:

схему сравнения, выполненную с возможностью обнаруживать изменение в режиме обработки набора команд и выводить индикацию относительно изменения режима обработки набора команд, и адрес команды, в которой происходит изменение, в ответ на обнаружение.

23. Процессор по п.22, в котором индикация содержит сигнал, служащий для остановки выполнения команды.

24. Процессор по п.22, в котором индикация содержит сигнал, служащий для управления трассировочной операцией.

25. Процессор по п.22, в котором индикация содержит сигнал, служащий для вызова исключительной ситуации.

26. Процессор по п.22, в котором индикация содержит сигнал, указывающий изменения в режиме обработки набора команд.

27. Процессор по п.22, в котором индикация содержит измененный адрес режима обработки набора команд.

28. Процессор по п.22, в котором схема сравнения обнаруживает изменение в режиме обработки набора команд, только когда адрес команды, по которому происходит изменение, находится в пределах предопределенного адресного интервала.

| US 5680620 А, 21.10.1997 | |||

| УСТРОЙСТВО УПРАВЛЕНИЯ ГЕНЕРАТОРАМИ ГАЗОВОГО ПОТОКА НА ВЗЛЕТНО-ПОСАДОЧНОЙ ПОЛОСЕ | 2008 |

|

RU2374694C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| СПОСОБ КОНТРОЛЯ ВЫПОЛНЕНИЯ КОМПЬЮТЕРНЫХ ПРОГРАММ В СООТВЕТСТВИИ С ИХ НАЗНАЧЕНИЕМ | 1998 |

|

RU2220443C2 |

Авторы

Даты

2011-09-20—Публикация

2007-08-03—Подача