Область техники, к которой относится изобретения

Варианты настоящего изобретения относятся в общем случае к процессорным устройствам и, более конкретно, относятся к режиму слежения в процессорных устройствах в системе трассировки команд.

Уровень техники

Система трассировки команд (instruction tracing system (ITS)) представляет собой средство трассировки, формирующее трассу потока управления выполнением программы. Трасса передается на выход в форме пакетов переменного размера. Декодер может использовать эти пакеты вместе с байтами ассоциированных команд для восстановления потока исполнения отслеживаемой программы.

Краткое описание чертежей

Настоящее изобретение будет более полно понятно из приведенного ниже описания и из прилагаемых чертежей различных вариантов изобретения. Эти чертежи, однако, следует рассматривать не как ограничение изобретения конкретными вариантами, а только как средство для лучшего разъяснения и понимания.

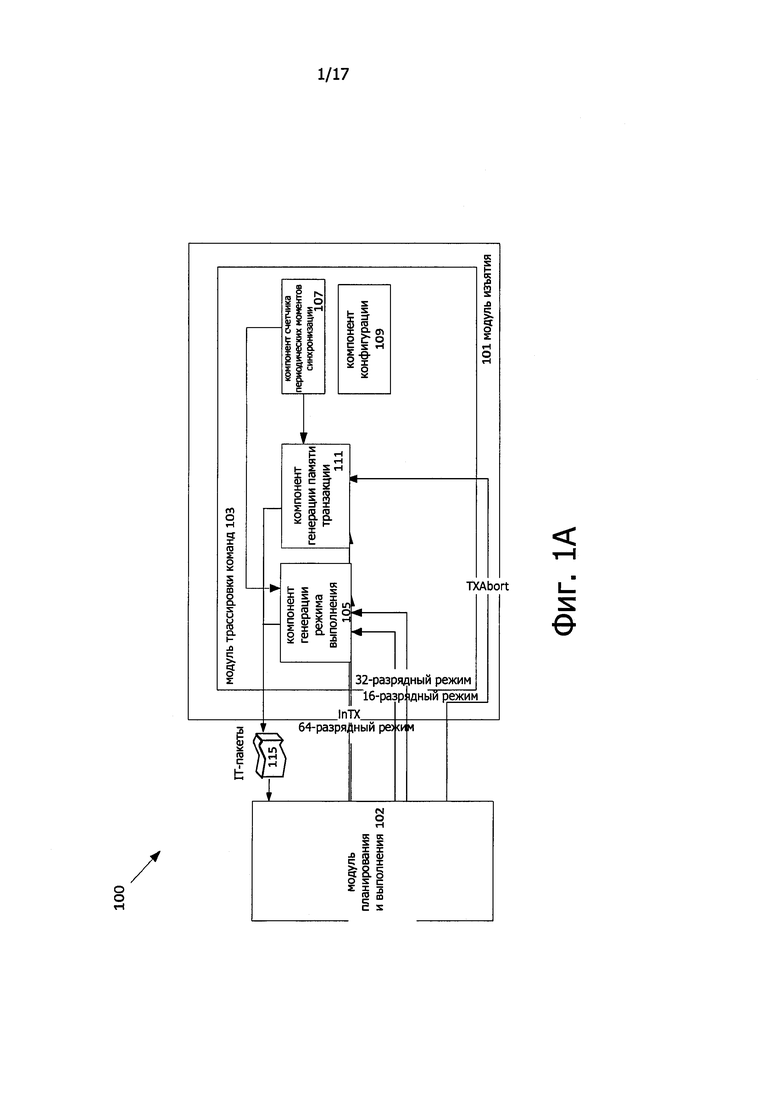

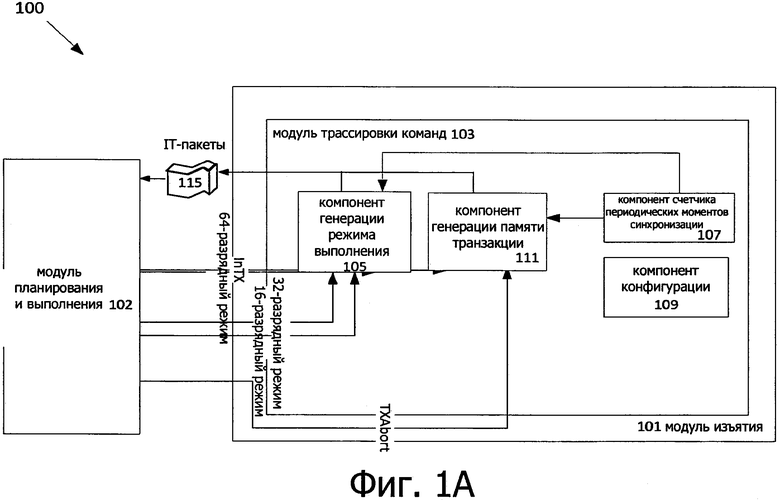

Фиг. 1А иллюстрирует пример архитектуры системы трассировки команд (instruction tracing system (ITS)) в процессорном устройстве, в соответствии с которой могут работать варианты настоящего изобретения.

Фиг. 1В иллюстрирует таблицу примеров последовательности команд, выполняемой системой ITS, и пакетов трассировки команд (instruction tracing (IT)), генерируемых системой ITS для отслеживания режима выполнения программы в трассе команд.

Фиг. 1С иллюстрирует таблицу примеров последовательности команд, выполняемой системой ITS, и IT-пакетов, генерируемых системой ITS для отслеживания режима выполнения операций памяти транзакций в трассе команд.

Фиг. 2А представляет блок-схему, иллюстрирующую пример конвейера с выполнением команд по порядку, а также пример конвейера с внеочередной выдачей/выполнением команд и переименованием регистров согласно рассматриваемым вариантам.

Фиг. 2В представляет блок-схему, иллюстрирующую пример архитектуры ядра с выполнением команд по порядку, а также пример архитектуры ядра с внеочередной выдачей/выполнением команд и переименованием регистров для включения в состав процессора согласно рассматриваемым вариантам.

Фиг. 3 представляет логическую схему, иллюстрирующую пример способа прослеживания режима выполнения в трассе команд в системе ITS.

Фиг. 4 представляет логическую схему, иллюстрирующую пример способа прослеживания выполнения операций памяти транзакций в трассе команд в системе ITS.

Фиг. 5 представляет блок-схему, иллюстрирующую процессор согласно одному из вариантов.

Фиг. 6А иллюстрирует пример альтернативной архитектуры, в соответствии с которой могут работать варианты настоящего изобретения.

Фиг. 6В показывает схематичное представление системы, в соответствии с которой варианты настоящего изобретения могут работать, быть инсталлированы, интегрированы или конфигурированы.

Фиг 7 иллюстрирует блок-схему компьютерной системы согласно одному из вариантов.

Фиг. 8 представляет блок-схему системы на кристалле (system on chip (SoC)) согласно одному из вариантов настоящего изобретения.

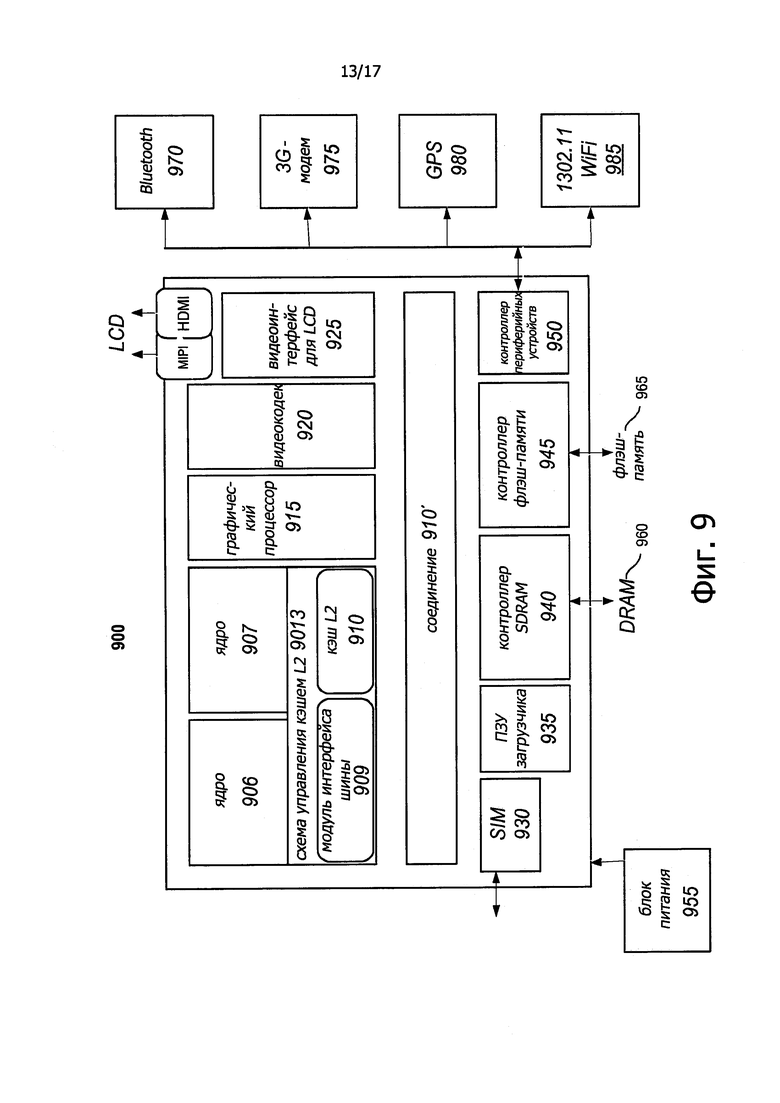

Фиг. 9 представляет блок-схему одного из вариантов системы на кристалле (SOC).

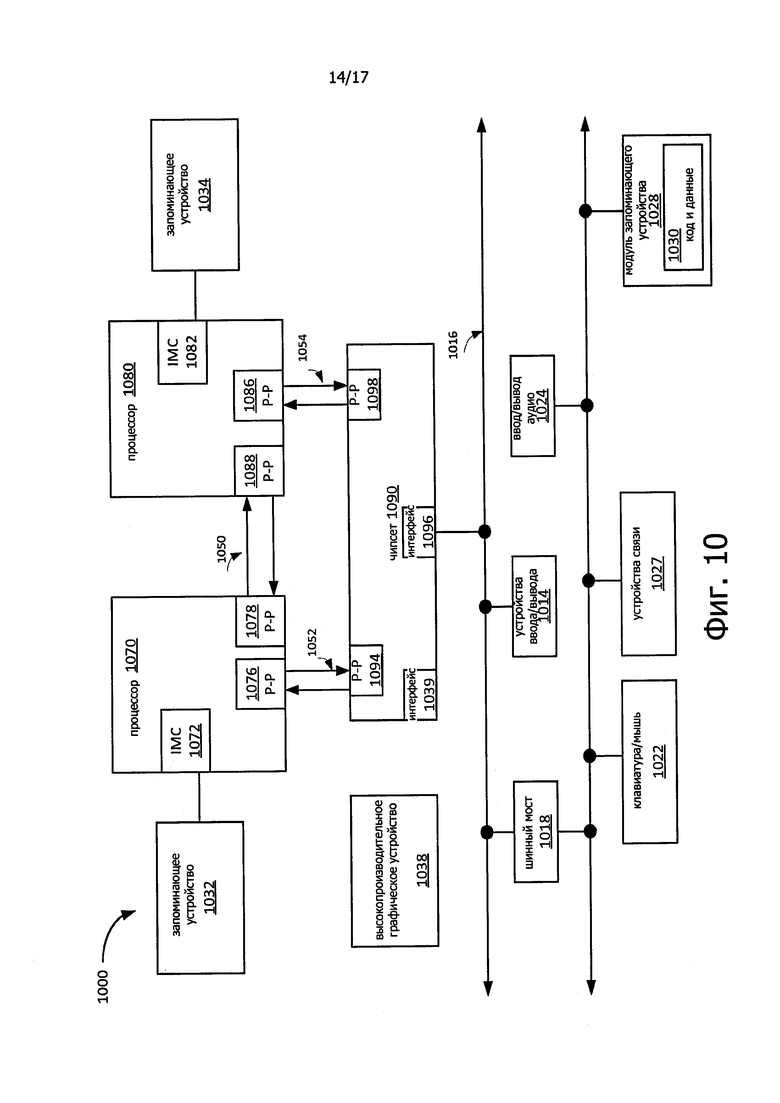

Фиг. 10 иллюстрирует блок-схему компьютерной системы согласно одному из вариантов.

Фиг. 11 иллюстрирует блок-схему компьютерной системы согласно одному из вариантов.

Фиг. 12 иллюстрирует блок-схему планшетного вычислительного устройства, смартфона или другого мобильного устройства, в котором использованы соединители интерфейса сенсорного экрана.

Фиг. 13 иллюстрирует схематичное представление машины в форме примера компьютерной системы, где может выполняться набор команд, в соответствии с которыми машина может осуществлять один или несколько рассматриваемых здесь способов.

Подробное описание

Здесь рассмотрены варианты режима слежения в процессорных устройствах в системе трассировки команд (instruction tracing (IT)). Режим слежения предоставляет информацию, позволяющую отладить исполняемое программное обеспечение в процессе трассировки команд. В одном из вариантов эта информация содержит индикацию события в выполняемой программе, которое изменило режим выполнения в процессорном устройстве, включая индикацию измененного режима. В другом варианте эта информация содержит изменение состояния операции трансакции с памятью в этом процессорном устройстве.

В IT-системе IT-пакеты указывают поток управления программы, выполняемой процессорным устройством. В таком случае IT-пакеты могут показывать информацию о разрешении для всех трассируемых ветвей и событий, так что при соединении с информацией об исходных командах можно воспроизвести поток управления программы. Для отслеживания режима выполнения IT-пакетов декодер должен знать состояние режима выполнения для каждой команды в трассе. Режим выполнения диктует, каким образом процессор интерпретирует байты команд, и может быть изменен программой в любой момент. Поэтому осведомленность о режиме выполнения позволяет декодеру правильно интерпретировать байты команд на основе двоичных файлов программы. Прослеживая и сохраняя трассу режима выполнения в процессоре для каждой команды, декодер может точно дезассемблировать байты команды для получения такой же самой команды, которую выполнял процессор, с целью воспроизведения точного потока управления.

В одном из вариантов предложен IT-модуль для генерации пакета режима выполнения (execution mode (ЕМ)), представленного двухбитовой структурой в пакете в выходном журнале (логе), генерируемом этим IT-модулем. Такой ЕМ-пакет создает индикацию текущего режима выполнения в процессорном устройстве и может быть сформирован каждый раз, когда режим выполнения изменяется. Этот ЕМ-пакет должен тогда указывать величину нового режима выполнения в процессоре.

Применительно к ЕМ-пакетам указанный IT-модуль может использовать компонент счетчика периодических моментов синхронизации из состава процессора, чтобы определить, когда передавать на выход ЕМ-пакеты, указывающие текущий режим выполнения в процессоре. В одном из вариантов ЕМ-пакеты указывают событие в программе, которое изменяет режим выполнения в процессоре, а также дают индикацию измененного режима. В одном из вариантов IT-модуль может содержать компонент для генератора режима выполнения, который генерирует ЕМ-пакеты, содержащие двухбитовую структуру. Этот ЕМ-пакет может предоставлять индикацию изменения в режиме выполнения в процессоре для команды, отслеживаемой IT-модулем. Например, различные сочетания битов в двухбитовой структуре представляют разные режимы выполнения в процессоре. В одном из вариантов компонент генератора режима выполнения также генерирует пакет указателя команды режима выполнения (execution mode instruction pointer (EMIP)) вместе с ЕМ-пакетом. Этот EMIP-пакет содержит указатель команды (instruction pointer (IP)), соответствующей первой команде, выполняемой в измененном режиме выполнения, ассоциированном с ЕМ-пакетом. В одном из вариантов указатель IP обозначает адрес выполнения в начале трассы команд.

Для правильного декодирования трассы IT-декодер, который принимает выходной IT-журнал, должен знать режим выполнения для каждой команды в трассе. Таким образом, для точного декодирования команд из статических двоичных файлов IT-декодер должен знать первоначальный режим и начальный указатель команды (IP), соответствующий началу журнала трассировки. Затем декодер переходит к «прогулке» по двоичному изображению, декодируя команды и определяя их результат (выход) на основе IT-журнала. Когда программа выполняет операцию изменения режима, измененный режим необходимо сообщить IT-декодеру. Процессор начинает применять информацию измененного режима к процессу декодирования записанных в процессоре команд в двоичной форме и, аналогично, декодер обязан также применить эту информацию режима к декодированию команд, хранящихся в статических двоичных файлах. Если процессор и декодер становятся несинхронизированными один с другим с точки зрения информации режима, эти процессор и декодер могут интерпретировать байты команд по-разному и, вследствие этого выполнять и просматривать разные команды, соответственно. В таком случае, IT-журнал, генерируемый процессором, скорее всего, будет несогласован с интерпретацией байтов команд, осуществляемой декодером, что вероятно приведет к ошибкам и сбоям процесса декодирования. Наконец, поскольку иногда бывает желательно начать декодирование с середины выходного журнала, IT-модуль может периодически вставлять индикатор состояния режимы и указатель IP в выходной журнал для создания дополнительных жизнеспособных начальных точек декодирования.

Как обсуждается выше, IT-пакеты служат индикаторами потока управления программы. Эти IT-пакеты используются декодером для реконструкции потока выполнения трассируемой программы. Во избежание сбоев декодера из-за передачи пакетов для команд, которые реально не «завершили» (не зафиксировали) свое состояние, генерация пакетов происходит в периоды «изъятия». Это позволяет избежать генерации пакетов для спекулятивных операций (операций по предположению), которые могут быть отброшены процессорным устройством, такие как команды, выполняемые по пути, соответствующему неверному предположению. Благодаря операциям памяти транзакций (transactional memory (ТМХ)) команды теперь изымаются спекулятивно, так что их результаты (состояние регистров, записи в памяти и т.п.) завершаются (фиксируются) только в более поздний момент. В ходе транзакции команды изымаются обычным путем, но состояние фиксируется только в том случае, когда транзакция завершается фиксацией. Если транзакция отбрасывается, все изменения состояния, произведенные спекулятивными (по предположению) командами, включая уже изъятые команды, «откатываются» назад. В такой ситуации полезно предоставить IT-декодеру информацию о том, какие команды зафиксировали (завершили) свое состояние, а какие не зафиксировали свое состояние, и о ТМХ-командах, ассоциированных с этими состояниями.

В одном из вариантов IT-модуль может также генерировать пакеты памяти транзакций (ТМХ), представленные двухбитовой структурой указания режима в пакете в выходном журнале, генерируемом IT-модулем. Один бит может указывать, находится ли ТМХ-транзакция в процессе выполнения, так что изъятия команд (и пакеты, ассоциированные с этими командами) являются спекулятивными. В одном из вариантов этот бит следует задать, когда транзакция начинается, и сбрасывать, когда эта транзакция завершается или фиксируется. Другой бит может указывать, что произошло отбрасывание команды, так что все состояния, модифицированные спекулятивными ТМХ-командами, следует «откатить» назад.

В одном из вариантов настоящего изобретения IT-модуль может содержать компонент генератора памяти транзакций, который генерирует пакеты памяти транзакций (ТМХ) на основе двухбитовых структур указания режима, которые указывают начальную точку транзакции ТМХ и все точки, где происходило изменение состояния, в выходном IT-журнале. В одном из вариантов такая точка изменения состояния указывает, что произошло состояние отбрасывания в ТМХ-операции. Это состояние отбрасывания означает, что команды между начальной точкой ТМХ-операции и точкой отбрасывания не зафиксировали свое состояние. Ранее, декодер мог не знать, что команды выполняются спекулятивно, в рамках транзакции, и, если транзакция была отброшена, что результаты следует откатить назад. В такой ситуации, не зная об изменении в состоянии ТМХ-операции, процессор может неправильно представить поток выполнения в процессоре и обновления состояния процессора. Более того, состояние отбрасывания в ТМХ-операции может вызвать переход потока управления. В такой ситуации, если не иметь индикации об отбрасывании ТМХ-операции, включая указатели команд (IT) источника и адресата этого события отбрасывания, декодер может оказаться несинхронизированным с реальным потоком управления выполнением, вследствие чего генерируемые пакеты IT-журнала могут оказаться несогласованными с тем, как декодер выполняет трассировку.

В другом варианте процессор может исключать пакеты, генерируемые отброшенными и потому незафиксированными спекулятивно выполненными командами. Однако для процессора может быть затруднительно сохранять выходные пакеты в буфере, если только процессор не отбрасывает или не фиксирует ТМХ-область команд. В альтернативном варианте процессор может попытаться создать резервную копию указателя записи в выходном журнале трассировки, удаляя, таким образом, эти пакеты из журнала трассировки. Но это может быть затруднительно в случае больших ТМХ-областей с большим числом пакетов, где системный компонент периодически архивирует выходной журнал пакетов на энергонезависимом носителе для хранения информации, так что начальная точка отбрасываемой области уже была архивирована. Наконец, для отладчика может оказаться полезным и ценным проанализировать поток выполнения в отбрасываемой области, что поможет определить причины отбрасывания.

Аналогично ЕМ-пакетам декодеру желательно определить ТМХ-состояние процессора в момент начала трассировки. Столкнувшись с ТМХ-состоянием отбрасывания, декодер может засомневаться, не «видел» ли он начальное ТМХ-состояние. В таком случае декодер может не знать, какие выполненные и обработанные пакетированные результаты нужно исключить вследствие отбрасывания. Также аналогично ЕМ-пакетам, ТМХ-пакеты могут быть вставлены в выходной журнал в качестве ТМХ-событий, происходящих во время выполнения в процессоре. И наконец, аналогично ЕМ-пакетам, IT-модуль может вставить информацию ТМХ-состояния как часть периодических моментов синхронизации для создания дополнительных стартовых точек декодера, которые содержат все состояния процессора, необходимые для декодирования выходного журнала.

Следует отметить, что другие типы информации о режимах процессора могут обрабатываться аналогично в том смысле, что пакеты состояния в выходном журнале записывают в начале трассы и затем в периодические моменты синхронизации, равно как пакеты событий, указывающие на изменения режима, вставляют в выходной журнал в моменты времени, когда происходят соответствующие события. Информация о режиме может содержать информацию, необходимую для правильного декодирования двоичного кода, и может содержать информацию, полезную, чтобы охарактеризовать поведение различных компонентов. Такая информация о режимах содержит, не ограничиваясь, правила упорядочения памяти, указание строгого или приблизительного следования правилам IEEE округления чисел с плавающей запятой, указатель на основание таблицы страниц, частоту процессора, частоту системы, базовый (начальный) адрес сегмента кода, базовый адрес сегмента данных, указатель на основание структуры управления виртуальной машиной, напряжение питания процессора, состояние питания процессора, состояние питания системы, сведения о снижении питания/выключении компонентов и т.п.

В последующем описании приведены многочисленные конкретные подробности (например, различные варианты реализации логических IT-устройств, форматы IT-пакетов, подробности секционирования аппаратуры/встроенного программного обеспечения, подробности секционирования/интеграции логических устройств, конфигурации процессора, подробности микро-архитектуры, последовательности операций, типы и взаимоотношения компонентов системы и т.п.). Однако понятно, что варианты настоящего изобретения могут быть осуществлены на практике и без этих конкретных подробностей. В других случаях хорошо известные схемы, структуры и способы не были показаны подробно, чтобы не затемнять понимание настоящего изобретения.

Фиг. 1А иллюстрирует пример архитектуры 100 процессорного устройства согласно тому, какие варианты могут работать с использованием IT-архитектуры, генерирующей пакеты 115 трассировки команд (instruction trace (IT)). В одном из вариантов устройство обработки представляет собой центральный процессор (CPU).

Более конкретно, модуль 101 изъятия содержит IT-модуль 103, который принимает информацию от модуля 102 планирования и исполнения и пакетирует эту информацию (например, значение текущего режима выполнения, ассоциированное с командами в трассе) для вывода в форме IT-пакетов 115, передаваемых в модуль 102 планирования и выполнения. Указанный IT-модуль 103 может содержать компонент 105 генератора режима выполнения (EMGC), который принимает значения текущего режима выполнения от модуля 102 планирования и выполнения. Как обсуждается выше, совокупность значений режима выполнения может содержать, не ограничиваясь, 8-разрядный режим, 16-разрядный режим, 32-разрядный режим, 48-разрядный режим и 64-разрядный режим. В одном из вариантов компонент EMGC 105 выделяет значения текущего режима выполнения из сигнала от модуля 102 планирования и выполнения. В других вариантах компонент EMGC 105 принимает значения текущего режима выполнения от модуля 102 планирования и исполнения по запросу. В следующих вариантах компонент EMGC 105 автоматически принимает значения текущего режима выполнения от модуля 102 планирования и выполнения.

Указанный IT-модуль 103 может также содержать компонент 107 счетчика периодических моментов синхронизации, соединенный с компонентом EMGC 105. Этот компонент 107 счетчика периодических моментов синхронизации передает компоненту EMGC 105 командный сигнал для записи ЕМ-пакета, в качестве периодического обновления состояния режима, в поток выходных IT-пакетов 115. Как обсуждается выше, ЕМ-пакет несет информацию о текущем режиме выполнения в процессоре, включая индикацию любых изменений режима выполнения в процессоре. В одном из вариантов компонент EMGC реализован в виде последовательности выполняемых команд или микроопераций (также называемых μops), которые выполняет машина для генерации ЕМ-пакетов.

В одном из вариантов ЕМ-пакет содержит двухбитовую структуру из журнала пакетов, которая указывает текущий режим выполнения в процессоре для IT-пакетов 115. Варианты настоящего изобретения двухбитовыми структурами не ограничиваются, так что ЕМ-пакет может содержать структуры, имеющие больше двух битов или меньше двух битов в зависимости от конкретного варианта архитектуры. В одном из вариантов такая двухбитовая структура может отражать величины архитектурных битов. Например, когда величины обоих битов в двухбитовой структуре равны нулю, это может обозначать значение режима выполнения, соответствующее 16-разрядному режиму. В другом примере, когда один бит в двухбитовой структуре равен нулю, а другой бит равен единице, это может обозначать значение режима выполнения, соответствующее 32-разрядному режиму или 64-разрядному режиму в зависимости от архитектуры процессорного устройства.

Например, компонент EMGC 105 может принять индикацию 16-разрядного режима в качестве значения текущего режима выполнения от модуля 102 планирования и выполнения и позднее этот компонент может принять индикацию 32-разрядного режима в качестве значения текущего режима выполнения от этого модуля 102 планирования и выполнения. После приема индикации 32-разрядного режима компонент EMGC 105 распознает изменение значения текущего режима выполнения и генерирует ЕМ-пакет, которые задает момент изменения значения режима выполнения для ассоциированного IT-пакета 115.

Указанный IT-модуль 103 может также содержать компонент 109 конфигурации, соединенный с компонентом EMGC 105. Этот компонент 109 конфигурации позволяет программе конфигурировать частоту периодических моментов синхронизации под управлением компонента 107 счетчика периодических моментов синхронизации и может также позволить программе конфигурировать включение/исключение конкретных ЕМ-пакетов в IT-пакетах 115.

Компонент EMGC 105 генерирует также пакет указателя команд режима выполнения (EMIP), ассоциированный с ЕМ-пакетом в составе IT-пакетов 115. В одном из вариантов EMIP-пакет следует за ассоциированным с ним ЕМ-пакетом. Этот EMIP-пакет содержит указатель IP для первой команды, выполняемой в измененном режиме выполнения.

Используя принимаемые ЕМ-пакеты и EMIP-пакеты, декодер может знать, когда изменяется режим выполнения для команды в трассе. Кроме того, декодер может точно знать, в каком месте двоичного кода происходит изменение режима, чтобы правильно дизассемблировать байты команды. В результате поток команд в трассе совпадает с потоком выполнения в процессоре.

В одном из вариантов декодер может пытаться узнать, какой был режим выполнения в начале трассировки, т.е. до первого изменения режима выполнения. Компонент EMGC 105 передает ЕМ-пакет в последовательности пакетов состояния. Эти пакеты состояния передают информацию о текущем состоянии процессорного устройства. В таком ситуации информацию о текущем режиме выполнения в ЕМ-пакете передают пакеты состояния. Поскольку декодер начинает декодирование с пакета состояния, он точно декодирует пакеты состояния в начале трассы. Введение последовательности пакетов состояния в периодические точки в выходном журнале создает дополнительные моменты, когда декодер может начать декодирование.

В одном из вариантов последовательность IT-пакетов 115 в журнале пакетов в выходном потоке, может содержать, не ограничиваясь, граничный пакет, после чего следуют разнообразные пакеты состояния, среди которых могут быть ЕМ-пакет и EMIP-пакет, и далее - конечный пакет состояния. Эта последовательность может повторяться в другой точке в журнале пакетов в выходном потоке. За граничным пакетом в журнале пакетов следует первый байт другого пакета, так что этот байт служит стартовой точкой декодирования пакетов. В одном из вариантов конечный пакет состояния служит индикатором конца последовательности пакетов состояния. Пакет вне области пакетов, ограниченной с одной стороны граничным пакетом и с другой стороны конечным пакетом состояния, являются пакетами событий, которые вставляют в выходной журнал в точке изменения режима.

Фиг. 1В иллюстрирует таблицу IT-пакетов 115, генерируемых IT-модулем 103, когда трассировка активизирована, в ходе потока 116 выполнения, например. Как показано, пока процессор выполняет программную последовательность, в журнал пакетов вводят IT-пакеты 115, генерируемые IT-модулем 103. В качестве примера, совокупность IT-пакетов 115 содержит граничный пакет 120, за который следуют пакеты 121 состояния и следующий за ними ЕМ-пакет 122, имеющий 32-разрядный режим выполнения. В такой ситуации трассировка активизирована в 32-разрядном режиме. За ЕМ-пакетом 122 следует EMIP-пакет 123, которые предоставляет указатель IT 32-разрядного режима выполнения в выходной журнал. За EMIP-пакетом 123 следует другая группа пакетов 124 состояния, за которыми следует конечный пакет 125 состояния.

В этом примере посреди потока управления может произойти изменение режима выполнения в потоке 116 выполнения. Это изменение в режиме выполнения представлено в совокупности пакетов 126 событий в выходном журнале пакетов 115, что вызывает генерацию другого ЕМ-пакета 127 с измененным режимом выполнения в выходном журнале пакетов 115. В приведенном примере, в потоке выполнения происходит изменение режима выполнения от 32-разрядного режима к 64-разрядному режиму. Кроме того, указатель IP этого изменения режима выполнения представлен в выходном журнале посредством EMIP-пакета 128, который следует сразу же после ЕМ-пакета 127. За EMIP-пакетом 128 следует группа пакетов 129 событий.

В одном из примеров в потоке 116 выполнения создана периодическая точка синхронизации, генерирующая другой граничный пакет 130, за которым следует группа пакетов 131 состояния, и после этого пакета следует ЕМ-пакет, имеющий 64-разрядный режим выполнения. В такой ситуации активизирована трассировка в 64-разрядном режиме. За ЕМ-пакетом 132 следует EMIP-пакет 133, представляющий указатель IP 64-разрядного режима выполнения в выходном журнале. За этим EMIP-пакетом следует другая группа пакетом 134 состояния, за которой следует конечный 135 пакет состояния.

Возвращаясь к Фиг. 1А, как обсуждается выше, IT-модуль 103 принимает информацию от модуля 102 планирования и управления и пакетирует эту информацию для передачи на выход IT-пакетов 115. В одном из вариантов эта информация содержит указание состояния транзакции в процессоре. Такое ТМХ-состояние может, не ограничиваясь, представлять собой «Начало транзакции», «Завершение (фиксация) транзакции» и «Отбрасывание транзакции». Указанный IT-модуль 103 может содержать компонент 111 генератора памяти транзакции (transactional memory generation component (TMXGC)), который принимает указание ТМХ-состояния от модуля 102 планирования и выполнения. В одном из вариантов компонент TMXGC 111 выделяет информацию о ТМХ-состоянии из сигнала от модуля 102 планирования и выполнения. В другом варианте компонент TMXGC 111 принимает информацию о ТМХ-состоянии от модуля 102 планирования и выполнения по запросу. В следующих вариантах компонент TMXGC 111 автоматически получает информацию о ТМХ-состоянии от модуля 102 планирования и выполнения.

Компонент 107 счетчика периодических моментов синхронизации в составе IT-модуля 103 также связан с компонентом TMXGC 111, который в свою очередь генерирует пакеты памяти транзакций (ТМХ) для вставки в совокупность пакетов состояния, генерируемых в периодические моменты синхронизации в совокупности IT-пакетов 115. Этот компонент 107 счетчика периодических моментов синхронизации передает командный сигнал компоненту TMXGC 111 для генерации ТМХ-пакетов в качестве части периодических пакетов состояния, записываемых в потоке выходных IT-пакетов. В одном из вариантов компонент TMXGC реализован в виде последовательности выполняемых команд или микроопераций (также называемых μops), которые выполняет машина для генерации ТМХ-пакетов. Как обсуждается выше, ТМХ-пакет представляет собой двухбитовую структуру указания режима в журнале пакетов. Эта двухбитовая структура указания режима может обозначать момент изменения ТМХ-состояния для IT-пакета 115. Варианты настоящего изобретения не ограничиваются двухбитовой структурой указания режима, так что ТМХ-пакет может содержать структуры, имеющие больше двух битов или меньше двух битов в зависимости от используемого варианта архитектуры.

Компонент 109 конфигурации в составе IT-модуля также связан с компонентом TMXGC 111. Этот компонент 109 конфигурации позволяет программе конфигурировать частоту периодических моментов синхронизации, которой управляет компонент 107 счетчика периодических моментов синхронизации, и может также позволить программе конфигурировать включение/исключение конкретных ТМХ-пакетов в совокупность IT-пакетов 115.

В одном из вариантов двухбитовая структура указания режима в ТМХ-пакете содержит бит индикации режима InTX и бит индикации режима TXAbort. Бит режима InTX обозначает, что процессор выполняет транзакцию и, следовательно, изменение этого бита обозначает начало или конец ТМХ-операции. В одном из примеров бит режима InTX может быть установлен (например, сделан равным 1), когда ТМХ-операция начинается, и сброшен или очищен (например, сделан равным 0), когда эта ТМХ-операция завершена (зафиксирована) или отброшена. Бит режима TXAbort предоставляет IT-декодеру извещение, соответствующая ТМХ-операция была отброшена. Это извещение об отбрасывании информирует IT-декодер, что все пакеты между моментом установления бита режима InTX и моментом установления бита режима TXAbort представляют команды, которые не зафиксировали свое состояние. В одном из вариантов IT-декодер отбрасывает все команды, ассоциированные с этими пакетами. В одном из вариантов декодер маркирует эти пакеты, чтобы позднее использовать команды, ассоциированные с этими пакетами. В одном из примеров бит режима TXAbort может быть установлен (например, сделан равным 1), когда бит режима InTX изменяется от 1 к 0 в момент отбрасывания.

В одном из примеров, когда процессор выполняет ТМХ-команду «Начало транзакции», компонент TMXGC 111 генерирует ТМХ-пакет, в котором бит режима InTX установлен равным 1, а бит режима TXAbort установлен равным 0, что обозначает начало транзакции, т.е. ТМХВ. В другом примере, когда процессор выполняет ТМХ-команду «Завершение (фиксация) транзакции», компонент TMXGC 111 генерирует ТМХ-пакет, в котором бит режима InTX установлен равным 0 и бит режима TXAbort установлен равным 0, что указывает на завершение (фиксацию) транзакции, т.е. ТМХС. В следующем пример, когда компонент TMXGC 111 принимает индикацию отбрасывания транзакции, этот компонент TMXGC 111 генерирует ТМХ-пакет, в котором бит режима InTX установлен равным 0, а бит режима TXAbort установлен равным 1, что обозначает отбрасывание транзакции, т.е. ТМХА.

В одном из вариантов компонент TMGC 111 также генерирует пакет указателя исходной команды памяти транзакции (source transactional memory instruction pointer (STMXIP)) и или пакет указателя целевой команды транзакции (target transactional memory instruction pointer (TTMXIP)), ассоциированные с каждым ТМХ-пакетом в совокупности IT-пакетов 115. Указанный STMXIP-пакет предоставляет указатель IP команды, ассоциированной с изменением ТМХ-состояния. В одном из вариантов STMXIP-пакет генерируют вместе с ТМХВ-пакетом для предоставления указателя IP ассоциированной команды в начале ТМХ-операции. В другом варианте STMXIP-пакет генерируют вместе с ТМХА-пакетом для предоставления указателя IP ассоциированной команды при отбрасывании ТМХ-операции. В следующем варианте STMXIP-пакет генерируют вместе с ТМХС-пакетом для предоставления указателя IP ассоциированной команды при завершении (фиксации) ТМХ-операции.

Указанный TTMXIP-пакет предоставляет указатель IP следующей команды, которую нужно выполнить при отбрасывании ТМХ-операции, что требуется, если операция отбрасывания вызывает переход потока управления. В таком случае декодер может знать, где начинается ТМХ-операция, где эта операция отбрасывается, где она завершается (фиксируется) и откуда продолжается выполнение после какого-либо отбрасывания. В одном из вариантов декодер может отбрасывать байты команд для всех пакетов между началом ТМХ-операции и моментом отбрасывания ТМХ-операции. В другом варианте декодер может маркировать байты команд для всех пакетов между началом ТМХ-операции и отбрасыванием этой ТМХ-операции.

Как обсуждается выше, декодер начинает декодирование с пакетов состояния, так что эти пакеты состояния предоставляют информацию о текущем состоянии процессорного устройства. Компонент TMXGC 111 передает ТМХ-пакет в последовательности пакетов состояния. За граничным пакетом в журнале пакетов всегда следует первый байт какого-либо пакета, так что этот байт служит стартовой точкой декодирования пакетов. В такой ситуации IT-декодер может искать этот граничный пакет и точно декодировать пакеты состояния после граничного пакета. Благодаря вставке ТМХ-пакета среди пакетов состояния, следующих сразу же после граничного пакета, декодеру обеспечено знание состояния транзакции от стартовой точки декодирования.

Фиг. 1С иллюстрирует таблицу примеров IT-пакетов 115, генерируемых IT-модулем 103, когда активизирована трассировка в процессе потока 118 выполнения, например. Как показано, когда трассировка активизирована во время выполнения последовательности 118 команд компонент TMGC 111 генерирует журнал пакетов на основе IT-пакетов 115. Совокупность IT-пакетов 115 содержит граничный пакет 140, за которым следует группа пакетов 141 состояния, и за ними следует ТМХ-пакет 142. Этот ТМХ-пакет 142 может содержать описанную выше двухбитовую структуру указания режима, которая содержит бит режима InTX и бит режима TXAbort. Бит режима InTX предоставляет декодеру извещение о начале ТМХ-операции, а бит режима TXAbort предоставляет извещение, что ТМХ-операция отброшена. В этом примере двухбитовая структура указания режима в составе ТМХ-пакетов 142 содержит бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 0. В таком случае поток 118 выполнения не находится в транзакции. Пакет 143 указателя исходной команды памяти транзакций (STMXIP) генерируют после ТМХ-пакета 142. Указанный STMXIP-пакет 143 предоставляет указатель IP ассоциированной команды из состава ТМХ-операции. В одном из вариантов STMXIP-пакет 143 может быть сформирован перед ТМХ-пакетом 142. За этим STMXIP-пакетом 143 следует группа пакетов 144 состояния и конечный 145 пакет состояния.

В одном из примеров посреди потока управления начинается ТМХ-операция в потоке 118 выполнения. Начало этой ТМХ-операции представлено группой пакетов 146 событий в выходном журнале пакетов 115, которые вызывают генерацию пакета начала транзакции ТМХ (ТМХВ) 147 в качестве ТМХ-пакета в начале ТМХ-операции. Этот ТМХВ-пакет 147 может представлять собой описанную выше двухбитовую структуру указания режима, которая содержит бит режима InTX и бит режима TXAbort. Бит режима InTX предоставляет декодеру извещение о начале ТМХ-операции, а бит режима TXAbort предоставляет извещение, что ТМХ-операция отброшена. Например, когда ТМХВ-пакет 147 указывает появление ТМХ-команды «Начало транзакции», двухбитовая структура указания режима в составе ТМХВ-пакета 147 может содержать бит режима InTX, установленный равным 1, и бит режима TXAbort, установленный равным 0. После ТМХВ-пакета 147 генерируют первый пакет указателя исходной команды памяти транзакций (STMXIP) 148. Этот первый STMXIP-пакет 148 предоставляет указатель IP ассоциированной команды в начале ТМХ-операции. В одном из вариантов первый STMXIP-пакет 148 может быть сформирован прежде ТМХВ-пакета 147.

В одном из примеров ТМХ-операция отбрасывает поток выполнения, что представлено ТМХ-пакетом 150 отбрасывания (ТМХА) в качестве ТМХ-пакета. Этот ТМХА-пакет 150 может также следовать за двухбитовой структурой указания режима, описанной выше. Например, когда ТМХА-пакет 150 указывает появление отбрасывания транзакции, тогда двухбитовая структура указания режима в составе ТМХА-пакета 150 может содержать бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 1. Второй STMXIP-пакет 151 генерируют после ТМХА-пакета 150. Этот второй STMXIP-пакет 151 предоставляет указатель IP ассоциированной команды, которая должна быть выполнена при отбрасывании ТМХ-операции. В одном из вариантов второй STMXIP-пакет 151 может быть сформирован перед ТМХА-пакетом 150. За вторым STMXIP-пакетом 151 следует пакет 152 указателя целевой команды памяти транзакций (TTMXIP), который предоставляет указатель IP следующей команды, которая должна быть выполнена после отбрасывания ТМХ-операции. В одном из вариантов TTMXIP-пакет 152 генерируют перед ТМХА-пакетом 150. За TTMXIP-пакетом 152 может следовать другая группа пакетов 153 событий.

В этом примере в потоке 118 выполнения создают периодическую точку синхронизации, генерирующую другой граничный пакет 154, за которым следует группа пакетов 155 состояния, после чего следует другой ТМХ-пакет 156. Аналогично описанному выше, двухбитовая структура указания режима в составе ТМХ-пакета 156 содержит бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 0. Другой STMXIP-пакет 157 генерируют после ТМХ-пакета 156. В одном из вариантов этот STMXIP-пакет 157 может быть сформирован прежде ТМХ-пакета 156. За этим STMXIP-пакетом 157 следует другая группа пакетов 158 состояния и конечный пакет 159 состояния.

Хотя это и не показано, результатом ТМХ-команд может быть также завершение (фиксация) ТМХ-операции, куда входит также генерация пакета завершения (фиксации) ТМХ-операции (ТМХС). При использовании двухбитовой структуры указания режима этот ТМХС-пакет содержать бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 0.

Возвращаясь к Фиг. 1А, в одном из вариантов пользователь может пожелать трассировать команды, выполняемые в конкретном диапазоне указателей IP. В этом сценарии компонент TMXGC 111 может генерировать и передавать на выход ТМХ-пакеты на основе команд, которые как попадают в конкретный диапазон указателей IP, так и находятся вне этого диапазона указателей IP. Однако компонент TMXGC 111 не должен генерировать и передавать на выход STMXIP-пакет и TTMXIP-пакет, ассоциированные с ТМХ-пакетом, если указатель IP находится вне указанного конкретного диапазона указателей IP. В результате декодер имеет возможность должным образом обрабатывать пакеты, генерируемые либо ТМХ-операциями, начинающимися в этой области указателей IP, но заканчивающимися вне этой области указателей IP, либо ТМХ-операциями, начинающимися вне указанной области указателей IP, но заканчивающимися в этой области указателей IP.

Фиг. 2А представляет блок-схему, иллюстрирующую конвейер с выполнением операций по порядку, а также пример конвейера с внеочередной выдачей/выполнением команд и ступенью переименования регистров в процессоре, отслеживающем режим выполнения и выполнение операций памяти транзакций в системе трассировки команд согласно по меньшей мере одному из вариантов настоящего изобретения. Фиг. 2В представляет блок-схему, иллюстрирующую пример архитектуры ядра с выполнением команд по порядку, а также пример архитектуры ядра с внеочередной выдачей/выполнением команд и логическим устройством переименования регистров для включения в состав процессора согласно по меньшей мере одному из вариантов настоящего изобретения. Прямоугольники из сплошных линий на Фиг. 2А иллюстрируют конвейер с выполнением команд по порядку, тогда как прямоугольники из штриховых линий иллюстрируют конвейер с внеочередной выдачей/выполнением команд и переименованием регистров. Аналогично прямоугольники из сплошных линий на Фиг. 2В иллюстрируют архитектуру логического устройства с выполнением команд по порядку, тогда как прямоугольники из штриховых линий иллюстрируют логическое устройство с переименованием регистров и логическое устройство с внеочередной выдачей/выполнением команд.

Как показано на Фиг. 2А, процессорный конвейер 200 содержит ступень 202 выборки, ступень 204 декодирования длины, ступень 206 декодирования, ступень 208 распределения, ступень 210 переименования, ступень 212 планирования (также известную как ступень диспетчирования и выдачи), ступень 214 чтения регистров/чтения памяти, ступень 216 выполнения, ступень 218 обратной записи/записи в память, ступень 222 обработки исключений и ступень 224 завершения (фиксации). В некоторых вариантах ступени выполняют в другом порядке и разные ступени могут рассматриваться по порядку или вне очереди.

Как показано на Фиг. 2В, стрелки обозначают связь между двумя или более модулями, а направление стрелок указывает направление потоков данных между этими модулями. На Фиг. 2В показано процессорное ядро 290, содержащее входной блок 230, соединенный с модулем 250 механизма выполнения, причем и входной блок, и модуль механизма исполнения связаны с модулем 70 памяти.

Ядро 290 может представлять собой ядро с сокращенным набором команд (RISC), ядро с полным набором команд (CISC), ядро с очень длинным командным словом (VLIW), либо ядро гибридного или альтернативного типа. В качестве еще одной опции ядро 290 может представлять ядро специального назначения, такое как, например, сетевое ядро или ядро связи, механизм сжатия данных, графическое ядро или другое подобное ядро.

Входной блок 230 содержит модуль 232 прогнозирования ветвления, соединенный с модулем 234 кэша команд, который связан с буфером 236 динамической трансляции (translation lookaside buffer (TLB)) команд. Этот буфер соединен с модулем 238 выборки команд, который соединен с модулем 240 декодера. Модуль декодера или декодер может декодировать команды и генерировать на выходе одну или несколько микроопераций, входных точек микрокода, микрокоманд, других команд или других сигналов управления, декодированных из исходных команд, или отражающих исходные команды другим способом, или полученных из исходных команд. Декодер может быть реализован с использованием разнообразных механизмов. К примерам таких разнообразных механизмов относятся, не ограничиваясь этим, преобразовательные таблицы, аппаратные схемы, программируемые логические матрицы (PLA), постоянные запоминающие устройства (ПЗУ (ROM)) микрокода и т.п. Модуль 234 кэша команд связан с модулем 276 кэша уровня 2 (L2) в составе модуля 270 памяти. Модуль 240 декодера соединен с модулем 252 распределения/переименования в составе модуля 250 механизма выполнения.

Модуль 250 механизма выполнения содержит модуль 252 переименования/распределения, соединенный с модулем 254 изъятия и группой из одного или нескольких модулей 256 планировщиков. Модуль 254 изъятия может содержать компонент 203 для трассировки команд в реальном времени с целью генерации ITS-пакетов. Эти модули 256 планировщиков представляют какое-то число различных планировщиков, включая станции резервирования, центральное окно команд и т.п. Модули 256 планировщиков соединены с модулями 258 физических регистровых файлов. Каждый из модулей 258 физических регистровых файлов представляет собой один или несколько физических регистровых файлов, так что разные файлы сохраняют данные одного или нескольких различных типов, таких как скалярные целочисленные данные, скалярные данные с плавающей запятой, упакованные целочисленные данные, упакованные данные с плавающей запятой, векторные целочисленные данные, векторные данные с плавающей запятой и т.п., данные состояния (например, указатель команды, иными словами, адрес следующей команды, которую нужно выполнить) и т.д. На модули 258 физических регистровых файлов наложен модуль 254 изъятия для иллюстрации различных способов, какими может осуществляться переименование регистров и внеочередное (не по порядку) выполнение (например, с использованием буферов переупорядочения и регистровых файлов изъятия; с использованием файлов будущего, буферов истории и регистровых файлов изъятия; с использованием карт регистров и пула регистров; и т.п.).

В общем случае архитектурные регистры видимы извне процессора или с точки зрения программиста. При этом понятие регистров не ограничивается каким-либо известным конкретным типом схем. Здесь подходят регистры различных типов, если они способны сохранять и предоставлять данные, как описано здесь. К примерам подходящих регистров относятся, не ограничиваясь, выделенные физические регистры, динамически назначаемые физические регистры с использованием переименования регистров, сочетания выделенных и динамически назначаемых физических регистров и т.п. Модуль 254 изъятия и модули 258 физических регистровых файлов соединены с исполнительными кластерами 260. Исполнительный кластер 260 содержит один или несколько исполнительных модулей 262 и группу из одного или нескольких модулей 264 доступа к памяти. Исполнительные модули 262 могут осуществлять разнообразные операции (например, сдвиги, суммирование, вычитание, умножение) и над различными типами данных (например, над скалярными данными с плавающей запятой, упакованными целочисленными данными, упакованными данными с плавающей запятой, векторными целочисленными данным, векторными данными с плавающей запятой).

Тогда как некоторые варианты могут содержать ряд исполнительных модулей, выделенных для конкретных функций или групп функций, другие варианты могут содержать только один исполнительный модуль или несколько исполнительных модулей, где все модули выполняют все функции. Модули 256 планировщиков, модули 258 физических регистровых файлов и исполнительные кластеры 260, показаны для варианта с несколькими такими модулями, поскольку некоторые варианты создают раздельные конвейеры для некоторых типов данных/операций (например, конвейер для скалярных целочисленных данных, конвейер для скалярных данных с плавающей запятой/упакованных скалярных целочисленных данных/упакованных данных с плавающей запятой/векторных целочисленных данных/векторных данных с плавающей запятой и/или конвейер доступа к памяти, так что каждый из этих конвейеров имеет собственный модуль планировщика, модуль физических регистровых файлов и/или исполнительный кластер - и в случае отдельного конвейера для доступа к памяти реализуются некоторые варианты, в которых исполнительный кластер этого конвейера имеет модули 264 для доступа к памяти). Следует также понимать, что в случае использования раздельных конвейеров, один или несколько из этих конвейеров могут служить для внеочередного выпуска/выполнения, а остальные - для работы по порядку.

Группа модулей 264 доступа к памяти соединена с модулем памяти 270, содержащим модуль 272 буфера данных TLB, соединенный с модулем 274 кэша данных, связанным с модулем 276 кэша уровня 2 (L2). В примере одного из вариантов модули 264 доступа к памяти могут содержать модуль загрузки, модуль сохранения адреса и модуль сохранения данных, каждый из которых соединен с модулем 272 буфера данных TLB в составе модуля 270 памяти. Модуль 276 кэша L2 соединен с одним или несколькими другими уровнями кэша и в конечном итоге с главной памятью.

В качестве примера, архитектура с переименованием регистров и ядром для внеочередного выпуска/выполнения может реализовать конвейер 200 следующим образом: 1) модуль 238 выборки команд реализует ступени 202 и 204 выборки и декодирования длины; 2) модуль 240 декодера реализует ступень 206 декодирования; 3) модуль 252 переименования/распределения реализует ступень 208 распределения и ступень 210 переименования; 4) модули 256 планировщиков реализуют ступень 212 планирования; 5) модули 258 регистровых файлов и модуль 270 памяти реализуют ступень 214 чтения регистров/чтения памяти; исполнительный кластер 260 реализует ступень выполнения 116; 6) модуль 270 памяти и модули 258 физических регистровых файлов реализуют ступень 218 обратной записи/записи в память; 7) различные модули могут участвовать в реализации ступени 222 обработки исключений; а модуль 254 изъятия и модули 258 физических регистровых файлов реализуют ступень 224 завершения (фиксации).

Ядро 290 может поддерживать один или несколько наборов команд (например, набор команд х86 (с некоторыми расширениями, которые были добавлены в более новых версиях); набор команд MIPS, разработанный компанией MTPS Technologies из Солнечной долины, Калифорния (MIPS Technologies, Sunnyvale, СА); набор команд ARM (с дополнительными расширениями, такими как NEON), разработанный компанией ARM Holdings of Sunnyvale, СА).

Следует понимать, что ядро может поддерживать многопоточность (выполнение двух или более параллельных наборов операций или потоков) и может делать это различными способами, включая многопоточность с разделением времени, одновременную многопоточность (где одно физическое ядро создает свое логическое ядро для каждого из потоков, которые должно выполнять это физическое ядро одновременно в многопоточном режиме), или их сочетание (например, выборка и декодирование в режиме разделения времени и затем одновременная многопоточность в соответствии с технологией Intel® Hyperthreading).

Хотя переименование регистров описано в контексте внеочередного выполнения, следует понимать, что переименование регистров может быть использовано также в архитектуре с выполнением команд по порядку. Тогда как иллюстрируемый вариант процессора также содержит раздельные модули 234/274 кэшей данных и совместно используемый модуль 276 кэша L2, альтернативные варианты могут иметь один внутренний кэш и для команд, и для данных, такой как, например, внутренний кэш Уровня 1 (L1), или многоуровневый внутренний кэш. В некоторых вариантах система может содержать сочетание внутреннего кэша и внешнего кэша, находящегося вне ядра и/или процессора. В качестве альтернативы весь кэш может быть внешним относительно ядра и/или процессора.

На Фиг. 3 представлена логическая схема, иллюстрирующая пример способа 300 для отслеживания режима выполнения посредством системы трассировки команд. Способ 300 может быть осуществлен посредством процессорного логического устройства, которое может представлять собой аппаратуру (например, схемы, специализированные логические устройства, программируемые логические устройства, микрокоды и т.п.). Представленная на чертеже нумерация блоков служит только для ясности и никак не имеет целью предписывать порядок операций, в которых могут участвовать различные блоки. В одном из вариантов способ 300 осуществляется IT-модулем 103, рассмотренным применительно к Фиг. 1А.

Начиная с блока 301, IT-модуль отслеживает режим выполнения для каждой команды в трассе. Например, компонент EMGC 105 отслеживает режим выполнения, осуществляемый модулем 102 планирования и выполнения. Этот режим выполнения задает текущее значение режима выполнения в процессорном устройстве. Режим выполнения может представлять собой, не ограничиваясь этим, 8-разрядный режим, 16-разрядный режим, 32-разрядный режим, 48-разрядный режим или 64-разрядный режим. В блоке 303 определяют, произошло ли изменение режима выполнения для рассматриваемой команды в трассе. Если в блоке 303 определено, что режим выполнения не изменился, способ переходит к блоку 305, где определяют, нужно ли генерировать периодический пакет состояния. Если в блоке 305 определено, что периодический пакет состояния генерировать не нужно, повторяют блок 301. В одном из вариантов, когда именно генерировать периодический пакет состояния, определяет компонент 107 счетчика периодических моментов синхронизации. Если в блоке 305 определено, что периодический пакет состояния генерировать нужно, способ переходит к блоку 307, где компонент EMGC 105 генерирует и передает на выход пакет режима выполнения (ЕМ). Как обсуждается выше, такой ЕМ-пакет предоставляет информацию о текущем режиме выполнения в процессорном устройстве.

Однако если в блоке 303 определено, что режим выполнения изменился, тогда способ переходит к блоку 307, где компонент EMGC 105 генерирует и передает на выход пакет режима выполнения (ЕМ) в составе IT-пакетов. Как обсуждается выше, этот ЕМ-пакет предоставляет также индикацию события в программе, которое изменило режим выполнения, и индикацию измененного режима выполнения. В одном из вариантов ЕМ-пакет представляет собой двухбитовую структуру в журнале пакетов в составе IT-модуля, которая служит точкой изменения режима выполнения для IT-пакета 115. В блоке 309 компонент EMGC 105 генерирует и передает на выход EMIP-пакет, ассоциированный с указанным ЕМ-пакетом в совокупности IT-пакетов. В одном из вариантов EMIP-пакет следует за ЕМ-пакетом. Как обсуждается выше, этот EMIP-пакет содержит указатель IP первой команды, которая выполняется в состоянии измененного режима выполнения.

На Фиг. 4 представлена логическая схема, иллюстрирующая пример способа 400 для отслеживания выполнения операций памяти транзакций посредством системы трассировки команд. Способ 400 может быть осуществлен посредством процессорного логического устройства, которое может содержать оборудование (например, схемы, специализированные логические устройства, программируемые логические устройства, микрокоды и т.п.). Представленная на чертеже нумерация блоков служит только для ясности и никак не имеет целью предписывать порядок операций, в которых могут участвовать различные блоки. В одном из вариантов способ 400 осуществляется IT-модулем 103, рассмотренным применительно к Фиг. 1А.

Начиная с блока 401, IT-модуль 103 отслеживает состояние памяти транзакций (ТМХ) для каждой команды в трассе. Например, компонент TMXGC 111 отслеживает состояние ТМХ-операции, осуществляемой модулем 102 планирования и выполнения. В блоке 403 определяют, является ли состояние ТМХ-операции для рассматриваемой команды в трассе состоянием «Отброшено». Если в блоке 403 определено что состояние этой ТМХ-операции не является состоянием «Отброшено», тогда в блоке 405 определяют, является ли состояние рассматриваемой ТМХ-операции состоянием «Завершено» (фиксировано). Если в блоке 405 определено, что состояние ТМХ-операции является состоянием «Завершено» (фиксировано), тогда в блоке 406 генерируют сообщение о завершении (фиксации) ТМХ-операции (ТМХС) в виде ТМХС-пакета и передают на выход в составе совокупности IT-пакетов 115 в выходном потоке. Компонент TMXGC 111 генерирует этот ТМХС-пакет, который обозначает завершение (фиксацию) ТМХ-операции. Например, этот ТМХС-пакет представляет собой сообщение о «Завершении транзакции» в виде ТМХ-команды, где бит режима InTX установлен равным 0 и бит режима TXAbort установлен равным 0. В блоке 407 генерируют пакет указателя исходной команды памяти транзакций (STMXIP), ассоциированный с ТМХС-пакетом. Этот STMXIP-пакет предоставляет указатель IP источника, ассоциированного с ТМХ-командами. В качестве примера STMXIP-пакет предоставляет указатель ГР ассоциированной командой при завершении (фиксации) ТМХ-операции. В одном из вариантов STMXIP-пакет может быть сформирован перед ТМХС-пакетом.

Если в блоке 405 определено, что состояние ТМХ-операции не является состоянием «Завершено» (фиксировано), способ переходит к блоку 408, где определяют, является ли состояние этой ТМХ-операции состоянием «Начало». Если в блоке 408 определено, что состояние ТМХ-операции является состоянием «Начало», тогда в блоке 409 генерируют сообщение о начале ТМХ-операции (ТМХВ) в виде ТМХ-пакета. Компонент TMXGC 111 генерирует этот ТМХВ-пакет, обозначающий начало ТМХ-операции. Этот ТМХ-пакет содержит двухбитовую структуру указания режима, имеющую бит режима InTX и бит режима TXAbort. Бит режима InTX предоставляет декодеру извещение о начале ТМХ-операции, а бит режима TXAbort предоставляет извещение, что ТМХ-операция была отброшена. Например, ТМХВ-пакет представляет собой сообщение о «Начале транзакции», в виде ТМХ-команды, где бит режима InTX установлен равным 1, а бит режима TXAbort установлен равным 0. В блоке 411 генерируют пакет указателя исходной команды памяти транзакций (STMXIP), ассоциированный с ТМХВ-пакетом. Этот STMXIP-пакет предоставляет указатель IP источника, ассоциированный с ТМХ-командами. В качестве примера, STMXIP-пакет предоставляет указатель IP ассоциированный с началом ТМХ-операции. В одном из вариантов STMXIP-пакет может быть сформирован перед ТМХВ-пакетом.

Если в блоке 408 определено, что состояние ТМХ-операции не является состоянием «Начало», тогда изменений состояния ТМХ-операций нет, а в блоке 413 определяют, следует ли формировать периодический пакет состояния. Как указано выше, пакет состояния предоставляет текущую информацию о состоянии процессора. Если в блоке 413 определено, что периодический пакет состояния генерировать не нужно, повторяют блок 401. В одном из вариантов компонент 107 счетчика периодических моментов синхронизации определяет, когда именно нужно генерировать периодический пакет состояния. Если в блоке 413 определено, что периодический пакет состояния генерировать нужно, способ переходит к блоку 415, где компонент TMXGC 111 генерирует и передает на выход ТМХ-пакет. Как обсуждается выше, ТМХ-пакет содержит двухбитовую структуру указания режима, имеющую бит режима InTX и бит режима TXAbort. В этом примере, ТМХ-пакет, в котором бит режима InTX установлен равным 0 и бит режима TXAbort установлен равным 0, указывает, что поток выполнения не осуществляет транзакцию. В блоке 416 генерируют STMXIP-пакет, ассоциированный с ТМХ-пакетом. Как обсуждается выше, этот STMXIP-пакет предоставляет указатель IP источника, ассоциированного с ТМХ-командами. В одном из вариантов STMXIP-пакет может быть сформирован перед ТМХ-пакетом.

Возвращаясь к блоку 403, если определено, что состояние ТМХ-операции является состоянием «Отброшено», способ переходит к блоку 417, где генерируют ТМХ-пакет «Отброшено» (ТМХА) в качестве ТМХ-пакета посредством компонента TMXGC 111. Как обсуждается выше, ТМХА-пакет предоставляет индикацию завершения в качестве состояния ТМХ-операции. Например, ТМХА-пакет является сообщением «Транзакция отброшена» в качестве ТМХ-команды, где бит режима InTX установлен равным 0, а бит режима TXAbort установлен равным 1. В блоке 419 компонент TMXGC 111 генерирует пакет указателя исходной команды памяти транзакций (STMXIP), ассоциированного с ТМХА-пакетом. Этот STMXIP-пакет предоставляет указатель IP, по которому происходит отбрасывание ТМХ-операции. В одном из вариантов STMXIP-пакет генерируют перед ТМХА-пакетом. В блоке 421 компонент EMGC 105 генерирует пакет указателя целевой команды памяти транзакций (TTMXIP), ассоциированного с ТМХА-пакетом. Этот TTMXIP-пакет предоставляет указатель IP следующей команды, которая должна быть выполнена после отбрасывания ТМХ-операции. В одном из вариантов TTMXIP-пакет генерируют перед ТМХА-пакетом. В блоке 423 компонент EMGC 105 передает на выход эти ТМХА-пакет, ассоциированный STMXIP-пакет и ассоциированный TTMXIP-пакет в качестве IT-пакетов 115 в выходном потоке.

На Фиг. 5 представлена блок-схема микро-архитектуры процессора 500, содержащего логические схемы и устройства для выполнения команд согласно одному или нескольким аспектам настоящего изобретения. В одном из вариантов процессор 500 отслеживает режим выполнения и выполнение операций памяти транзакций в системе трассировки команд. В некоторых вариантах команда согласно одному из вариантов может быть реализована для оперирования с элементами данных, имеющими размер один байт, слово, двойное слово, счетверенное слово и т.д., равно как с различными типами данных, такими как целочисленные данные с обычной и с удвоенной точностью и данные с плавающей запятой, также с обычной и с удвоенной точностью. В одном из вариантов работающий по порядку команд входной блок 501 является частью процессора 500, которая осуществляет выборку команд для исполнения и подготовку этих команд к использованию в процессорном конвейере в дальнейшем. Этот входной блок 501 может содержать несколько модулей. В одном из вариантов блок 526 упреждающей выборки команд выбирает команды из запоминающего устройства и передает их в декодер 528 команд, который в свою очередь декодирует или интерпретирует эти команды. Например, в одном из вариантов этот декодер осуществляет декодирование полученной им команды и преобразует ее в одну или несколько операций, именуемых «микрокомандами» или «микрооперациями» (также обозначаемыми как μор), так что машина может выполнить эти микрооперации.

В других вариантах декодер анализирует команду и разбивает ее на код операции (opcode) и соответствующие данные и поля управления, используемые микроархитектурой для выполнения операций в соответствии с одним из вариантов. В одном из вариантов трассовый кэш 530 принимает декодированные микрооперации и собирает из них упорядоченные программные последовательности или трассы в очереди 534 микроопераций для исполнения. Когда трассовый кэш 530 сталкивается с комплексной командой, ПЗУ (ROM) 532 микрокодов выдает микрооперации, необходимые для выполнения соответствующей операции.

Некоторые команды преобразуются в одну микрооперацию, тогда как другие нуждаются в нескольких микрооперациях для выполнения полной операции. В одном из вариантов, если для выполнения команды нужно больше четырех микроопераций, декодер 528 обращается в ПЗУ ROM 532 микрокодов, чтобы выполнить команду. В одном из вариантов команда может быть декодирована и преобразована в небольшое число микроопераций для обработки в декодере 528 команд. В другом варианте, если для выполнения операции требуется целый ряд микроопераций, эта команда может быть сохранена в ПЗУ ROM 532 микрокодов. Трассовый кэш 530 обращается в точку входа программируемой логической матрицы (programmable logic array (PLA)) для определения правильного указателя микрокоманды с целью считывания из ПЗУ ROM 532 микрокодов последовательностей микрокодов для завершения выполнения одной или нескольких команд согласно одному из вариантов. После того, как ПЗУ ROM 532 микрокодов завершит построение последовательности микроопераций для выполнения какой-либо команды, входной блок 501 машины возобновляет выборку микроопераций из трассового кэша 530.

Механизм 503 внеочередного выполнения команд (не по порядку) представляет собой блок, в котором производится подготовка команд к выполнению. Логическое устройство для выполнения команд не по порядку содержит ряд буферов для «сглаживания» и переупорядочения потока команд с целью оптимизации работы системы, когда эти команды проходят по конвейеру, и происходит их планирование для исполнения. Логическое устройство распределителя назначает буферы и ресурсы машины, которые нужны каждой микрооперации для выполнения. Логическое устройство переименования регистров отображает логические регистры на входы в регистровый файл. Распределитель назначает также вход для каждой микрооперации в одну из двух очередей микроопераций - одну очередь для операций, требующих обращения к памяти, и одну очередь для операций, не требующих обращения к памяти, перед планировщиками команд: планировщиком памяти, быстрым планировщиком 502, планировщиком 504 для медленных/обычных операций с плавающей запятой и простым планировщиком 506 операций с плавающей запятой. Планировщики 502, 504, 506 микроопераций определяют, когда микрооперация готова к выполнению, на основе готовности зависимых регистровых источников входных операндов для этой микрооперации и доступности исполнительных ресурсов, которые нужны для выполнения соответствующих микроопераций. Быстрый планировщик 502 в одном из вариантов может планировать в каждой половине главного тактового периода, тогда как другие планировщики могут осуществлять планирование один раз в каждом главном тактовом периоде процессора. Эти планировщики принимают «арбитражное» решение относительно диспетчирования портов при планировании микроопераций для исполнения.

Между планировщиками 502, 504, 506 и исполнительными модулями 512, 514, 516, 518, 520, 522, 524 в исполнительном блоке 511 располагаются физические регистровые файлы 508, 510. Система имеет раздельные регистровые файлы 508, 510 для целочисленных операций и операций с плавающей запятой соответственно. Каждый регистровый файл 508, 510 в одном из вариантов содержит также схему обхода, направляющую только что полученные результаты, которые еще не были записаны в регистровый файл, к новым зависимым микрооперациям. Регистровый файл 508 для целочисленных операций и регистровый файл 510 для операций с плавающей запятой могут также передавать данные один другому. В одном из вариантов регистровый файл 508 для целочисленных операций разделен на два отдельных регистровых файла, один регистровый файл для 32 младших разрядов (битов) данных и второй регистровый файл для 32 старших разрядов (битов) данных. В одном из вариантов регистровый файл 510 для операций с плавающей запятой имеет входы шириной 128 бит, поскольку команды с плавающей запятой обычно имеют операнды шириной от 64 до 128 бит.

Исполнительный блок 511 содержит исполнительные модули 512, 514, 516, 518, 520, 522, 524, где реально происходит выполнение команд. Эта секция содержит регистровые файлы 508, 510, сохраняющие величины целочисленных операндов данных и операндов данных с плавающей запятой, которые нужны для выполнения микрокоманд. Исполнительный блок 511 может содержать компонент трассировки команд в реальном времени для генерации IT-пакетов. Процессор 500 в одном из вариантов содержит ряд исполнительных модулей: модуль генератора адреса (address generation unit (AGU)) 512, генератор AGU 514, быстрое АЛУ ALU 516, быстрое АЛУ ALU 518, медленное АЛУ ALU 520, АЛУ ALU 522 с плавающей запятой, модуль 524 перемещения плавающей запятой. В одном из вариантов исполнительные модули 522, 524 с плавающей запятой выполняют операции с плавающей запятой, операции мультимедийного расширения ММХ, операции в формате одна команда-множество данных (SIMD), операции с потоковыми SIMD-расширениями (SSE) или другие операции. АЛУ ALU 522 с плавающей запятой в одном из вариантов содержит делитель с плавающей запятой 64-разрядного числа на 64-разрядное число для выполнения микроопераций деления, вычисления корня квадратного и определения остатка. Для описываемых здесь систем и способов обработку команд, содержащих величины с плавающей запятой, может осуществлять аппаратура для операций с плавающей запятой.

В одном из вариантов операции АЛУ передают в исполнительные модули 516, 518 высокоскоростных АЛУ (ALU). Эти быстрые АЛУ ALU 516, 518 в одном из вариантов могут выполнять быстрые операции с эффективной задержкой в половину тактового периода. В одном из вариантов более сложные целочисленные операции передают в медленное АЛУ ALU 520, поскольку это медленное АЛУ ALU 520 содержит аппаратуру для выполнения целочисленных операций, связанных с большой задержкой, таких как умножение, сдвиг, определение логического флага и ветвление. Операции загрузки/сохранения в памяти выполняются генераторами AGU 512, 514 адресов. В одном из вариантов целочисленные АЛУ ALU 516, 518, 520 описаны в контексте выполнения целочисленных операций над 64-разрядными операндами данных. В альтернативных вариантах эти АЛУ ALU 516, 518, 520 могут быть реализованы для поддержки различной разрядности данных, и в том числе 16 бит, 32,128, 256 бит и т.д. Аналогично модули 522, 524 для операций с плавающей запятой могут быть реализованы для поддержки работы с операндами с различной разрядностью. В одном из вариантов модули 522, 524 для операций с плавающей запятой могут оперировать с упакованными операндами данных шириной 128 бит в сочетании с командами SIMD и мультимедийными командами.

В одном из вариантов планировщики 502, 504, 506 микроопераций распределяют (диспетчируют) зависимые операции прежде, чем будет закончено выполнение первичной («родительской») нагрузки. Поскольку планирование и выполнение микроопераций в процессоре 500 осуществляется на основе гипотез (спекулятивно), этот процессор 500 содержит также логические устройства для обработки промахов в памяти. В случае промаха поиска нагрузки данных в кэше данных возможно наличие в конвейере зависимых операций в стадии выполнения, которые предоставили планировщику временно неправильные данные. Механизм повторного выполнения отслеживает и повторно выполняет команды, использовавшие неправильные данные. Зависимые операции должны быть выполнены повторно, а независимым операциям дают возможность завершиться. Планировщики и механизм повторного выполнения в одном из вариантов процессора рассчитаны также для «вылавливания» последовательностей команд для выполнения операций сравнения текстовых строк.

Термин «регистры» может относиться к расположенным в составе процессора областям памяти, используемым как часть команд для идентификации операндов. Другими словами, регистры могут быть используемыми извне процессора (с точки зрения программиста). Однако понятие регистров в каком-либо варианте не следует ограничивать каким-либо конкретным типом схем. Напротив, регистры в любом варианте способны сохранять и предоставлять данные и осуществлять описываемые здесь функции. Описываемые здесь регистры могут быть реализованы посредством схем внутри процессора с использованием различных способов, таких как выделенные физические регистры, динамически назначаемые физические регистры с использованием переименования регистров, сочетания выделенных и динамически назначаемых физических регистров и т.п. В одном из вариантов целочисленные регистры сохраняют 32-разрядные целочисленные данные.

Регистровый файл в одном из вариантов содержит также восемь мультимедийных SIMD-регистров для упакованных данных. Для последующего обсуждения под регистрами понимают регистры данных, рассчитанные на хранение упакованных данных, такие как 64-разрядные ММХ-регистры (также называемые в некоторых случаях 'mm'-регистрами) в микропроцессорах, поддерживающих технологию ММХ™, от корпорации «Интел» (Intel Corporation). Эти ММХ-регистры, доступные и в форме целочисленных регистров, и в форме регистров для чисел с плавающей запятой, могут работать с упакованными элементами данных, сопровождающими команды SIMD и SSE. Аналогично для хранения таких упакованных операндов данных могут быть использованы 128-разрядные ХММ-регистры, относящиеся к технологии SSE2, SSE3, SSE4 или выше (обобщенно именуемой "SSEx"). В одном из вариантов для хранения упакованных данных и целочисленных данных регистрам нет необходимости различать эти два типа данных. В одном из вариантов целочисленные данные и данные с плавающей запятой могут находиться в одном и том же регистровом файле или в разных регистровых файлах. Более того, в одном из вариантов данные с плавающей запятой и целочисленные данные могут находиться в разных регистрах или в одном и том же регистре.

Фиг. 6А иллюстрирует альтернативный пример архитектуры, в соответствии с которой могут работать варианты настоящего изобретения. В одном из вариантов интегральная схема 601 содержит логическое устройство 603 трассировки команд, осуществляющее трассировку команд в трассируемом приложении, режиме или области кода, когда эти команды выполняются интегральной схемой 601; модуль 606 изъятия для отслеживания режима выполнения и выполнения операций памяти транзакций в потоке информации трассировки в реальном времени. Этот модуль изъятия может содержать компонент 605 генератора режима выполнения для генерации нескольких пакетов режима выполнения, описывающих изменения режима выполнения или команд в трассе. Модуль 606 изъятия содержит также компонент 607 счетчика периодических моментов синхронизации для генерации нескольких пакетов, описывающих начало трассируемых команд. Модуль 606 изъятия содержит также компонент 609 конфигурации, позволяющий программе конфигурировать частоту периодических моментов синхронизации. Модуль 606 изъятия может также содержать компонент 611 генератора памяти транзакции (TMXGC) для генерации нескольких ТМХ-пакетов, описывающих изменения состояния ТМХ-команд в трассе. В одном из вариантов модуль 606 изъятия реализует логическое устройство 603 трассировки команд.

В одном из вариантов модуль 606 изъятия содержит логическое устройство ITS для реализации модуля 603 трассировки команд. В одном из вариантов логическое IT-устройство, реализующее компонент 603 трассировки команд, содержит компонент 605 генератора режима выполнения, компонент 607 счетчика периодических моментов синхронизации, компонент 609 конфигурации и компонент 611 генератора памяти транзакции. В одном из вариантов компонент 605 генератора режима выполнения передает на выход пакеты, такие как IT-пакеты 602, показанные на шине 604 данных. В одном из вариантов компонент генератора памяти транзакции также передавать на выход пакеты, такие как IT-пакеты 602, показанные на шине 604 данных. В одном из вариантов логическое устройство, реализующее компонент 603 трассировки команд, может быть осуществлено аппаратно. В одном из вариантов логическое устройство, реализующее компонент 603 трассировки команд, может быть осуществлено в микрокоде. В одном из вариантов логическое устройство, реализующее компонент 603 трассировки команд, может быть осуществлено посредством сочетания аппаратуры и микрокода.

В одном из вариантов интегральная схема представляет собой центральный процессор (CPU). В одном из вариантов этот центральный процессор используется для планшетного компьютера или смартфона.

Согласно одному из вариантов такая интегральная схема 601, таким образом, инициирует трассировку команд (например, посредством модуля 603 трассировки команд) для отслеживания команд трассируемого приложения, режима или области кода, когда эти команды выполняются интегральной схемой 601; генерирует несколько пакетов режима выполнения (ЕМ), описывающих изменение режима выполнения в процессе трассировки команд в момент изменения (например, посредством компонента 605 генератора режима выполнения, управляемого компонентом 603 трассировки команд); эти несколько ЕМ-пакетов содержат двухбитовую структуру в журнале пакетов, за которым следует пакет указателя команд режима выполнения (EMIP), генерируемый для индикации первой команды, которая должна быть выполнена в измененном режиме выполнения; совокупность нескольких пакетов, генерируемых для индикации состояния интегральной схемы 601 в периодический момент синхронизации, управляемый компонентом 607 счетчика периодических моментов синхронизации, содержит несколько пакетов режима выполнения (ЕМ), описывающих состояние режимов и состояние указателя команд в момент, когда происходила генерация пакетов состояния. В одном из вариантов интегральная схема 601 генерирует и передает на выход двухбитовую структуру, используемую для генерации ЕМ-пакета в качестве точки изменения значения режима выполнения, для декодирования пакетов. В одном из вариантов интегральная схема 601 генерирует несколько пакетов памяти транзакции (ТМХ), описывающих начало ТМХ-операции и изменение состояние ТМХ-операции во время трассировки команд в момент изменения (например, посредством компонента 611 генератора памяти транзакции под управлением компонента 603 трассировки команд); несколько ТМХ-пакетов, содержащих двухбитовую структуру указания режимов, в журнале пакетов, за которыми следуют один или оба пакета - пакет указателя исходной команды памяти транзакций (STMXIP) или пакет указателя целевой команды памяти транзакций (TTMXIP); несколько пакетов, генерируемых для индикации состояния интегральной схемы 601 в периодический момент синхронизации, управляемый компонентом 607 счетчика периодических моментов синхронизации, и в том числе несколько пакетов режима выполнения (ЕМ) и пакет указателя команд режима выполнения (EMIP), описывающие состояние режимов и состояние указателя команд, соответственно, в момент генерации пакетов состояния.

В одном из вариантов STMXIP-пакет предоставляет указатель IP ассоциированной команды в начале ТМХ-операции. В другом варианте STMXIP-пакет предоставляет указатель IP ассоциированной команды при изменении статуса ТМХ-операции. В одном из вариантов TTMXIP-пакет предоставляет указатель IP следующей команды, которая должна быть выполнена после ТМХ-операции, когда изменение состояния состоит в отбрасывании ТМХ-операции. В одном из вариантов интегральная схема 601 генерирует и передает на выход двухбитовую структуру указания режима, которая используется для генерации ТМХ-пакета в качестве начальной точки ТМХ-операции и точки изменения состояния ТМХ-операции для выполнения пакета. На Фиг. 6В показано схематичное представление системы 699, в соответствии с которой варианты изобретения могут работать, быть инсталлированы, интегрированы или конфигурированы.

В одном из вариантов система 699 содержит запоминающее устройство 695 и процессор или несколько процессоров 696. Например, запоминающее устройство 695 может сохранять команды, которые должны быть выполнены, а процессор (ы) 696 могут выполнять такие команды. Система 699 содержит шины связи 665 для передачи транзакций, команд, запросов и данных в системе 699 между несколькими периферийными устройствами 670, сопряженными для связи с одной или несколькими шинами 665 связи и/или интерфейсами 675. В системе 699 дополнительно показан дисплейный модуль 680.

В системе 699 выделена интегральная схема 601, которая может быть инсталлирована и конфигурирована в совместимой системе 699 или изготовлена и поставлена отдельно для работы в сочетании с соответствующими компонентами системы 699.

Согласно одному из вариантов система 699 содержит по меньшей мере один дисплейный модуль 680 и интегральную схему 601. Эта интегральная схема 601 может работать в качестве, например, примера или другого вычислительного компонента системы 699. В таком варианте интегральная схема 601 в системе 699 содержит по меньшей мере: шину 604 данных и устройство 603 трассировки команд, имеющее в составе компонент генерации пакетов состояния (не показан) и компонент генерации пакетов событий (не показан) для формирования нескольких IT-пакетов, описывающих трассируемые команды. В одном из вариантов эти IT-пакеты содержат информацию, описывающую состояние процессора и точку синхронизации в трассируемых командах.

Согласно одному из вариантов такая система 699 представляет собой планшетный компьютер или смартфон, в котором дисплейный модуль 680 представляет собой интерфейс с сенсорным экраном в планшетном компьютере или в смартфоне; а также в состав этого планшетного компьютера или компьютера входит интегральная схема 601.

На Фиг. 7 показана блок-схема системы 700 согласно одному из вариантов настоящего изобретения. Система 700 может содержать один или несколько процессоров 710, 715, которые соединены с концентратором 720 контроллера графической памяти (graphics memory controller hub (GMCH)). Необязательная (в качестве опции) природа дополнительных процессоров 715 обозначена на Фиг. 7 штриховыми линиями. В одном из вариантов процессоры 710, 715 отслеживают режим выполнения и выполнение операций памяти транзакций в системе трассировки команд.

Каждый процессор 710, 715 может представлять собой некоторую версию схемы, интегральной схемы, процессора и/или кремниевой интегральной схемы, как описано выше. Однако следует отметить, что маловероятно, чтобы в процессорах 710, 715 имелись модуль интегрального графического логического устройства и интегральный модуль управления памятью. На Фиг. 7 показано, что концентратор GMCH 720 может быть соединен с запоминающим устройством 740, которое может представлять собой, например, динамическое запоминающее устройство с произвольной выборкой (DRAM). Это динамическое ЗУПВ (DRAM) может, по меньшей мере в одном из вариантов, быть ассоциировано с энергонезависимым кэшем.

Концентратор GMCH 720 может представлять собой чипсет или часть чипсета. Этот концентратор GMCH 720 может осуществлять связь с процессорами 710, 715 и управлять взаимодействием между процессорами 710, 715 и запоминающим устройством 740. Концентратор GMCH 720 может также действовать в качестве ускоренного интерфейса шины между процессорами 710, 715 и другими элементами системы 700. По меньшей мере в одном из вариантов концентратор GMCH 720 осуществляет связь с процессорами 710, 715 по многоотводной шине, такой как системная шина (frontside bus (FSB)) 795.

Более того, концентратор GMCH 720 соединен с дисплеем 745 (таким как дисплей в виде плоской панели и дисплей с сенсорным экраном). Концентратор GMCH 720 может содержать интегральный графический ускоритель. Концентратор GMCH 720 соединен также с концентратором контроллера ввода/вывода (input/output (I/O) controller hub (ICH)) 750, который может быть использован для соединения различных периферийных устройств с системой 700. В варианте, изображенном на Фиг. 7, например, показано внешнее графическое устройство 760, которое может представлять собой дискретное графическое устройство, соединенное с концентратором ICH 750 вместе с другим периферийным устройством 770.

В качестве альтернативы в системе 700 могут также быть представлены дополнительные или другие процессоры. Например, совокупность дополнительных процессоров 715 может содержать дополнительные процессоры, такие же как процессор 700, дополнительные процессоры, являющиеся неоднородными или асимметричными относительно процессора 700, ускорители (такие как, например, графические ускорители или цифровые процессоры сигнала (DSP)), программируемые пользователями вентильные матрицы или какие-либо другие процессоры. Между процессорами 710, 715 могут быть разнообразные отличия с точки зрения спектра метрических показателей, включая архитектурные, микро архитектурные, тепловые характеристики, характеристики потребляемой мощности и другие подобные характеристики. Эти отличия могут эффективно проявляться в виде асимметрии и неоднородности между процессорами 710, 715. По меньшей мере в одном из вариантов разнообразные процессоры 710, 715 могут располагаться в одном и том же корпусе интегральной схемы.