Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к вычислительным системам и, в частности, относится к системам и способам предотвращения несанкционированного перемещения стека.

Уровень техники

Перемещение стека часто используют в атаках на основе возвратно-ориентированного программирования (ROP). ROP представляет собой способ перехвата потока выполнения текущего процесса путем использования команды возврата, которая во многих архитектурах процессоров получает из вершины стека адрес следующей исполняемой команды вызывающей подпрограммы. Таким образом, модифицируя возвращаемый адрес в стеке, злоумышленник может изменить поток выполнения текущего процесса на произвольный адрес в памяти.

После перехвата потока выполнения злоумышленник, например, может инициализировать аргументы и выполнить вызов библиотечной функции. Эта технология известна как "возврат в библиотеку". В другом примере злоумышленник может найти в сегменте кода несколько последовательностей команд, которые надо исполнить. Этот подход известен как "технология одолженных кусков кода".

Краткое описание чертежей

Настоящее описание проиллюстрировано на примерах, а не путем ограничения, и оно будет более понятным при обращении к последующему подробному описанию, если рассматривать его вместе с фигурами, на которых:

на фиг. 1 показана высокоуровневая диаграмма компонентов примера вычислительной системы в соответствии с одним или несколькими аспектами настоящего изобретения;

на фиг. 2 показана блок-схема процессора в соответствии с одним или несколькими аспектами настоящего изобретения;

на фиг. 3а-3b схематично показаны элементы микроархитектуры процессора в соответствии с одним или несколькими аспектами настоящего изобретения;

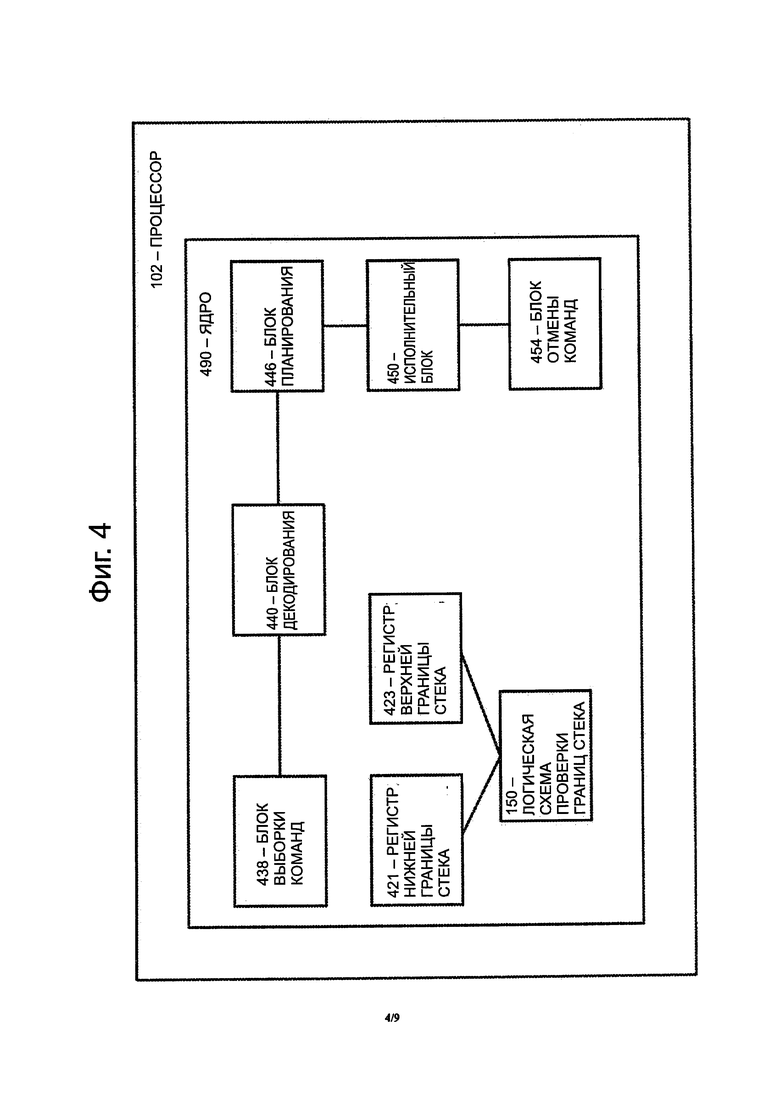

на фиг. 4 схематично показано несколько аспектов примера процессора и других компонентов примера вычислительной системы 100, показанной на фиг. 1, в соответствии с одним или несколькими аспектами настоящего изобретения;

на фиг. 5 схематично показан механизм сегментации памяти, используемый процессором 102 примера вычислительной системы 100, показанной на фиг. 1, в соответствии с одним или несколькими аспектами настоящего изобретения;

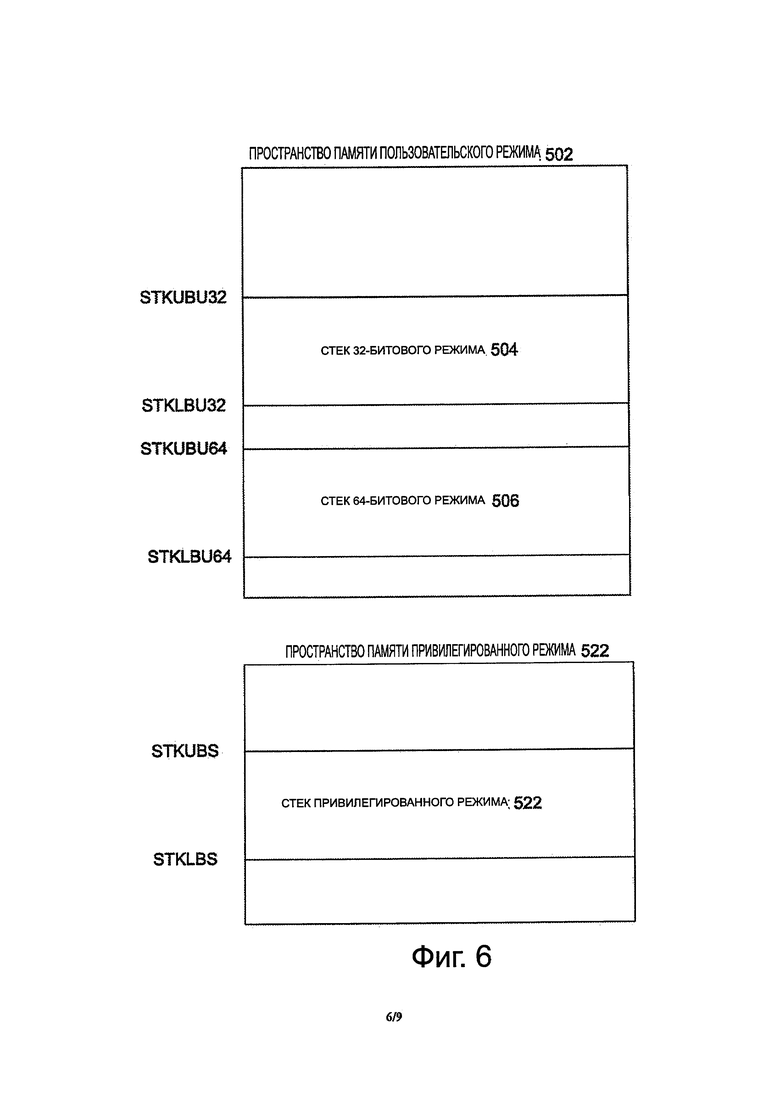

на фиг. 6 схематично показаны уровни привилегий механизма защиты памяти процессора в соответствии с одним или несколькими аспектами настоящего изобретения;

на фиг. 7 схематично показан план памяти, доступной из сегмента стека вычислительной системы 100, показанной на фиг. 1, в соответствии с одним или несколькими аспектами настоящего изобретения;

на фиг. 8а-8b схематично показаны условия, которые должна вычислить логическая схема проверки границ стека, в соответствии с одним или несколькими аспектами настоящего изобретения; и

на фиг. 9 показана блок-схема последовательности операций способа детектирования несанкционированного перемещения стека в соответствии с одним или несколькими аспектами настоящего изобретения.

Подробное описание изобретения

В этом документе описаны вычислительные системы и соответствующие способы детектирования несанкционированного перемещения стека. Несанкционированная модификация стека, или перемещение, может использоваться потенциальным злоумышленником при попытке атаки на основе возвратно-ориентированного программирования (ROP). Последняя может включать в себя несанкционированную модификацию адреса возврата процедуры, хранящегося в стеке, чтобы изменить поток выполнения текущего процесса на произвольный адрес в памяти. Для несанкционированной модификации стека злоумышленник может применять множество способов. Например, способ переполнения буфера включает в себя подачу большего числа входных данных, чем ожидает получить подпрограмма, при предположении, что входной буфер расположен в стеке.

Чтобы предотвратить несанкционированную модификацию стека, в процессоре может быть выполнена пара регистров границ стека, предназначенных для хранения границ стека. Здесь "границы стека" относятся к предварительно заданным адресам в памяти в сегменте стека, представляющим собой нижнюю и верхнюю границы допустимого диапазона адресуемой памяти через сегмент стека.

Процессор может реализовывать логику проверки границ стека путем сравнения адреса памяти, к которому обращаются через сегмент стека, со значениями, хранимыми в регистрах границ стека. Если адрес памяти находится за пределами допустимого диапазона, установленного значениями регистров границ стека, то процессор может записать в регистр состояния стека адрес, к которому обращаются через сегмент стека, и сгенерировать исключение ошибки стека.

В некоторых реализациях процессор может иметь отдельные регистры границ стека и для 32-битового пользовательского режима, и для 64-битового пользовательского режима, и для привилегированного режима. Значения регистров границ стека могут быть переключаемыми в зависимости от контекста с использованием команд сохранения/восстановления состояния процессора (напр., XSAVE/XRSTOR).

Различные аспекты вышеупомянутых способов и систем описаны ниже более подробно на примерах, а не путем ограничения.

В последующем описании изложены многочисленные специфические подробности, такие как примеры специфических типов конфигураций процессоров и систем, специфических аппаратных структур, специфических архитектурных и микроархитектурных подробностей, специфических конфигураций регистров, специфических типов команд, специфических компонентов системы, специфических измерений/высот, специфических ступеней конвейеров процессора и действий, для обеспечения полного понимания настоящего описания. Тем не менее, специалистам очевидно, что не обязательно реализовывать эти специфические детали, чтобы реализовать на практике описанные в этом документе способы. В других случаях хорошо известные компоненты или способы, такие как специфические и альтернативные процессорные архитектуры, специфические логические схемы/код для описанных алгоритмов, специфический микропрограммный код, специфическая работа межсоединения, специфические логические конфигурации, специфические технологии изготовления и материалы, специфические реализации компилятора, специфическое представление алгоритма в коде, специфические технологии/логика выключения и выполнения логических операций и другие специфические рабочие подробности вычислительной системы не были подробно описаны, чтобы избежать ненужного усложнения настоящего описания.

Хотя ниже варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы к другим типам интегральных схем и логических устройств. Аналогичные технологии и идеи описанных в этом документе вариантов осуществления можно применить к другим типам схем или полупроводниковым устройствам, которые могут выигрывать от более высокой пропускной способности конвейера и повышенной производительности. Идеи описанных в этом документе вариантов осуществления применимы к любому процессору или машине, которые осуществляют манипуляции данными. Тем не менее, настоящее раскрытие не ограничено процессорами или машинами, которые выполняют 512-битовые, 256-битовые, 128-битовые, 64-битовые, 32-битовые или 16-битовые операции над данными, и может быть применено к любому процессору и машине, в которых выполняют манипуляции или управление данными. Кроме того, для иллюстрации в последующем описании приведены примеры, а также различные примеры показаны на сопровождающих чертежах. Тем не менее, эти примеры не следует рассматривать в ограничивающем смысле, так как они предназначены только для иллюстрации описанных здесь вариантов осуществления, а не для того, чтобы предоставить исчерпывающий список всех возможных реализаций описанных в этом документе вариантов осуществления.

Хотя в приведенных ниже примерах описаны обращение с командами и их распределение в контексте исполнительных устройств и логических схем, другие варианты осуществления описанных в этом документе систем и способов могут быть выполнены посредством данных или команд, хранимых на машинном материальном носителе, которые при выполнении их машиной заставляют ее выполнять функции в соответствии по меньшей мере с одним из описанных здесь вариантов осуществления. В одном варианте осуществления функции связанные с описанными здесь вариантами осуществления, реализованы в виде исполняемых машиной команд.

Команды могут использоваться для того, чтобы заставить процессор общего назначения или специального назначения, запрограммированный посредством команд, выполнять описанные в этом документе способы. Описанные здесь варианты осуществления могут быть предоставлены в виде компьютерного программного продукта или программного обеспечения, которое может включать в себя машинный носитель информации, на котором хранятся команды, которые можно использовать для программирования компьютера (или других электронных устройств), чтобы он выполнил одну или несколько операций в соответствии с вариантами осуществления, описанными в этом документе. Как вариант, операции вариантов осуществления, описанных в этом документе, могут быть выполнены посредством специальных аппаратных компонентов, которые содержат логическую схему с фиксированной функцией для выполнения операций, или посредством любого сочетания программируемых вычислительных компонентов и аппаратных компонентов с фиксированной функцией.

Команды, используемые для программирования логики для выполнения описанных в этом документе способов, могут храниться в памяти в системе, такой как SDRAM, кэш, флеш-память, или в другом запоминающем устройстве. Более того, команды могут распространяться через сеть или на машинном носителе. Таким образом, машинный носитель может включать в себя любой механизм для хранения или передачи информации в форме, пригодной для чтения машиной (например, компьютером), но не ограничиваясь: флоппи-дискеты, оптические диски, постоянная память на компакт-дисках (CD-ROM) и магнито-оптические диски, постоянные запоминающие устройства (ROM), память с произвольным доступом (RAM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карты, флеш-память, или материальные машинные запоминающие устройства, используемые при передаче информации через Интернет посредством распространяемых электрических, оптических, акустических или других видов сигналов (напр., несущих волн, инфракрасных сигналов, цифровых сигналов, и т.д.). Соответственно, машинный носитель включает в себя любой тип материального носителя, пригодного для хранения или передачи электронных команд или информации в читаемом машиной (напр. компьютером) виде.

Здесь, "процессор" - это устройство, способное выполнять инструкции, кодирующие арифметические, логические операции или операции ввода-вывода. В одном иллюстративном примере процессор может следовать модели архитектуры фон Неймана и может включать в себя арифметико-логическое устройство (ALU), управляющий блок и несколько регистров. В еще одном аспекте процессор может включать в себя одно или несколько процессорных ядер и, следовательно, может быть одноядерным процессором, который обычно может обрабатывать один конвейер команд, либо многоядерным процессором, который может одновременно обрабатывать несколько конвейеров команд. В другом аспекте процессор может быть реализован в виде одной интегральной схемы, двух или нескольких интегральных схем, либо может быть компонентом многокристального модуля (напр., в котором отдельные кристаллы микропроцессора входят в состав одного корпуса интегральной схемы и, следовательно, имеют одно общее гнездо).

На фиг. 1 показана высокоуровневая диаграмма компонентов одного примера вычислительной системы в соответствии с одним или несколькими аспектами настоящего изобретения. Вычислительная система 100 может включать в себя процессор 102, чтобы использовать исполнительные устройства, включающие в себя логику для выполнения алгоритмов обработки данных, в соответствии с описанным в этом документе вариантом осуществления. Система 100 отражает системы обработки данных на основе микропроцессоров PENTIUM III™, PENTIUM 4™, Xeon™, Itanium, XScale™ и/или StrongARM™ от корпорации Intel, Сайта Клара, Калифорния, хотя также можно использовать другие системы (включая ПК, имеющие другие микропроцессоры, инженерные рабочие станции, приставки и т.п.). В одном варианте осуществления пример системы 100 выполняет версию операционной системы WINDOWS™ от корпорации Microsoft, Редмонд, Вашингтон, хотя также можно использовать другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические пользовательские интерфейсы.

Таким образом, описанные в этом документе варианты осуществления не ограничены каким-либо специфическим сочетанием аппаратной схемы и программного обеспечения.

Варианты осуществления не ограничены вычислительными системами. Альтернативные варианты осуществления систем и способов, описанных в этом документе, могут использоваться в других устройствах, таких как карманные устройства, и во встроенных приложениях. Некоторые примеры карманных устройств включают в себя сотовые телефоны, ГР-устройства (Internet Protocol), цифровые камеры, персональные цифровые помощники (PDA) и карманные ПК. Встроенные приложения могут включать в себя микроконтроллеры, процессоры цифровой обработки сигналов (DSP), однокристальные системы, сетевые компьютеры (NetPC), приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая может выполнять одну или несколько команд в соответствии по меньшей мере с одним вариантом осуществления.

В этом проиллюстрированном варианте осуществления процессор 102 включает в себя одно или несколько исполнительных устройств 108 для реализации алгоритма, то есть, для выполнения по меньшей мере одной команды. Один вариант осуществления может быть описан в контексте однопроцессорной настольной или серверной системы, но альтернативные варианты осуществления могут входить в многопроцессорную систему. Система 100 представляет собой пример системной архитектуры концентратора. Вычислительная система 100 включает в себя процессор 102 для обработки сигналов данных. Процессор 102, в качестве одного иллюстративного примера, включает в себя микропроцессор с полным набором команд (CISC), микропроцессор с сокращенным набором команд (RISC), микропроцессор с очень длинной машинной командой (VLIW), процессор, реализующий сочетание наборов команд или любое другое устройство обработки, такое как, например, процессор обработки цифровых сигналов. Процессор 102 соединен с процессорной шиной 110, которая передает сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 (напр., графический ускоритель 112, контроллер-концентратор 116 памяти, память 120, контроллер-концентратор 124 ввода-вывода, беспроводной приемник 126, флеш-BIOS 128, сетевой контроллер 134, звуковой контроллер 136, последовательный порт 138 расширения, контроллер 140 ввода-вывода, и т.д.) выполняют свои обычные функции, которые хорошо известны специалистам в этой области техники.

В одном варианте осуществления процессор 102 включает в себя внутренний кэш 104 1-го уровня (L1). В зависимости от архитектуры процессор 102 может иметь один внутренний кэш или несколько уровней внутренних кэшей. Другие варианты осуществления включают в себя сочетание внутренних и внешних кэшей в зависимости от конкретной реализации и потребностей. Набор 106 регистров предназначен для хранения различных типов данных в различных регистрах, включающих в себя целочисленные регистры, регистры действительных чисел с плавающей точкой, векторные регистры, блоковые регистры, теневые регистры, контрольные регистры, регистры состояния и регистр указателя команды.

Исполнительное устройство 108, включающее в себя логику для выполнения целочисленных операций и операций с плавающей точкой, также находится в процессоре 102. Процессор 102 в одном варианте осуществления включает в себя постоянное запоминающее устройство для микрокода (ucode), предназначенное для хранения микрокода, при исполнении которого выполняются алгоритмы для определенных макрокоманд, или осуществляются сложные сценарии. Здесь, микрокод потенциально является обновляемым, чтобы можно было исправить логические ошибки/внести исправления для процессора 102. Для одного варианта осуществления исполнительное устройство 108 включает в себя логику для работы с упакованным набором 109 команд. При включении упакованного набора 109 команд в набор команд процессора 102 общего назначения вместе с соответствующей схемой для выполнения команд, можно выполнять операции, используемые многими мультимедийными приложениями, с использованием упакованных данных в процессоре 102 общего назначения. Таким образом, многие мультимедийные приложения ускоряются и выполняются более эффективно при использовании всей ширины шины данных процессора для выполнения операций над упакованными данными. Это потенциально ограничивает потребность в передаче меньших единиц данных по шине данных процессора, чтобы выполнить одну или несколько операций, по одному элементу данных за раз. В микроконтроллерах, встроенных процессорах, графических устройствах, процессорах обработки цифровых сигналов и других типах логических схем также могут использоваться альтернативные варианты осуществления исполнительного устройства 108.

В некоторых реализациях процессор 102 также может включать в себя регистр 421 нижней границы стека, регистр 423 верхней границы стека и логическую схему 150 проверки границ стека. В одном иллюстративном примере процессор 102 может включать в себя пару регистров границ стека для двух или более режимов работы, напр., для 32-битового пользовательского режима, для 64-битового пользовательского режима и для привилегированного режима. Функционирование логической схемы проверки границ стека подробно описано ниже.

Система 100 включает в себя память 120. Память 120 включает в себя динамическую память с произвольным доступом (DRAM), статическую память с произвольным доступом (SRAM), флеш-память или другое запоминающее устройство. В памяти 120 хранятся команды 121 и/или данные 123, представленные сигналами данных, которые должны быть выполнены процессором 102. В некоторых реализациях команды 121.могут включать в себя команды, использующие логику 150 проверки границ стека для определения попытки нарушения границ стека, как более подробно описано ниже в этом документе.

Микросхема 116 системной логики соединена с шиной 110 процессора и памятью 120. Микросхема 116 системной логики в показанном варианте осуществления представляет собой контроллер-концентратор памяти (МСН). Процессор 102 может осуществлять связь с МСН 116 через шину 110 процессора. МСН 116 обеспечивает тракт 118 памяти с высокой пропускной способностью для соединения с памятью 120 для хранения команд и данных и для хранения графических команд, данных и текстур. МСН 116 предназначен для направления сигналов данных между процессором 102, памятью 120 и другими компонентами в системе 100, и для передачи сигналов данных между шиной 110 процессора, памятью 120 и вводом-выводом 122 системы. В некоторых вариантах осуществления микросхема 116 системной логики может обеспечить графический порт для соединения с графическим контроллером 112. МСН 116 соединен с памятью 120 через интерфейс 118 памяти. Графическая карта 112 соединена с МСН 116 через ускоренный графический порт (AGP) 114.

Система 100 использует пропиетарную интерфейсную шину 122 для соединения МСН 116 с контроллером-концентратором 130 ввода-вывода (ICH). ICH 130 обеспечивает непосредственные соединения с некоторыми устройствами ввода-вывода через локальную шину ввода-вывода. Локальная шина ввода-вывода представляет собой высокоскоростную шину ввода-вывода для соединения периферии с памятью 120, чипсетом и процессором 102. В качестве некоторых примеров можно привести звуковой контроллер, концентратор 128 микропрограммного обеспечения (флеш-BIOS), беспроводной трансивер 126, запоминающее устройство 124, существующий контроллер ввода-вывода, содержащий интерфейсы пользовательского ввода и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB), и сетевой контроллер 134. Запоминающее устройство 124 может содержать жесткий диск, привод флоппи-дисков, устройство CD-ROM, устройство флеш-памяти или другое запоминающее устройство большой емкости.

Для другого варианта осуществления системы команда в соответствии с одним вариантом осуществления может использоваться с однокристальной системой. Один вариант однокристальной системы содержит процессор и память. Память для одной такой системы представляет собой флеш-память. Флеш-память может быть расположена на том же кристалле, что и процессор, и другие компоненты системы. Кроме того, другие логические блоки, такие как контроллер памяти или графический контроллер, также могут быть расположены на однокристальной системе.

На фиг.2 приведена блок-схема микроархитектуры процессора 200, который включает в себя логические схемы для выполнения команд в соответствии с одним или несколькими аспектами настоящего изобретения. В некоторых вариантах осуществления команда в соответствии с одним вариантом осуществления может быть реализована для оперирования элементами данных, имеющими размер байт, слово, двойное слово, учетверенное слово и т.д., а также такие типы данных, как целочисленный тип или вещественный тип с плавающей точкой одинарной или двойной точности. В одном варианте осуществления по порядку передняя часть 201 представляет собой часть процессора 200, которая получает команды, которые необходимо выполнить, и подготавливает их для дальнейшего использования в конвейере процессора. Передняя часть 201 может включать в себя несколько блоков. В одном варианте осуществления блок 226 опережающей выборки команд получает команды из памяти и подает их в декодер 228 команд, который, в свою очередь, декодирует или интерпретирует их. Например, в одном варианте осуществления декодер декодирует принятую команду в одну или несколько операций, называемых "микрокомандами" или "микрооперациями" (также называемыми uops), которые может исполнять машина. В других вариантах осуществления декодер разбирает команду на код операции и соответствующие данные и управляющие поля, которые используются микроархитектурой, чтобы выполнять операции в соответствии с одним вариантом осуществления. В одном варианте осуществления трассовый кэш 230 берет декодированные микрооперации и собирает их в программные упорядоченные последовательности, или трассы, в очереди 234 кодов операций для исполнения. Когда трассовый кэш 230 встречает сложную команду, микрокодовое ROM 232 предоставляет код операции, необходимой для завершения операции.

Некоторые инструкции конвертируют в единственную микрооперацию, в то время как для других требуется несколько микроопераций для завершения полной операции. В одном варианте осуществления, если для завершения команды требуется более четырех микроопераций, то декодер 228 обращается в микрокодовое ROM 232 для выполнения команды. Для одного варианта осуществления команда может быть декодирована в небольшое число микроопераций для обработки в декодере 228 команды. В другом варианте осуществления команда может быть сохранена в микрокодовом ROM 232, если требуется несколько микроопераций для завершения операции. Трассовый кэш 230 обращается к входной точке программируемой логической матрицы (ПЛМ), чтобы определить корректный указатель на микрокоманду для чтения микрокодовых последовательностей, чтобы завершить одну или несколько команд в соответствии с одним вариантом осуществления из микрокодового ROM 232. После того, как микрокодовый ROM 232 завершает упорядочивание микроопераций для команды, передняя часть 201 машины прекращает получение микроопераций из трассового кэша 230.

Механизм 203 исполнения команд с изменением последовательности представляет собой блок, в котором команды подготавливают для выполнения. Логическая схема исполнения команд с изменением последовательности имеет несколько буферов, чтобы сгладить и переупорядочить поток команд, чтобы оптимизировать производительность по мере их прохождения по конвейеру и планирования для выполнения. Логическая схема выделения выделяет машинные буферы и ресурсы, которые требуются каждой микрооперации для выполнения. Логическая схема использования псевдонимов регистров отображает логические регистры на элементы в наборе регистров. Схема выделения также выделяет элемент для каждой микрооперации в одной из двух очередей микроопераций, одной для операций с памятью и одной для операций не с памятью, перед планировщиками команд: планировщик памяти, быстрый планировщик 202, медленный/общий планировщик 204 операций с плавающей точкой и простой планировщик 206 операций с плавающей точкой. Планировщики 202, 204, 206 микроопераций определяют, когда микрооперация готова для выполнения, исходя из готовности их зависимых источников входных регистровых операндов и доступности ресурсов выполнения, необходимых микрооперациям для завершения их действия. Быстрый планировщик 202 одного варианта осуществления может осуществлять планирование в каждой половине такта основного тактового генератора, в то время как остальные планировщики могут планировать только такты тактового генератора основного процессора. Планировщики выполняют арбитраж распределения портов для планирования выполнения микрокоманд.

Наборы 208, 210 физических регистров расположены между планировщиками 202, 204, 206 и исполнительными устройствами 212, 124, 216, 218, 220, 222, 224 в исполнительном блоке 211. Имеется отдельный набор регистров 208, 210 для целочисленных операций и операций с плавающей точкой соответственно. Каждый набор 208, 210 регистров одного варианта осуществления также включает в себя обходную сеть, которая может пропускать или направлять только что полученные результаты, которые еще не были записаны в набор регистров, на новые зависимые микрокоманды. Набор 208 целочисленных регистров и набор 210 регистров с плавающей точкой также могут передавать данные друг другу. Для одного варианта осуществления набор 208 целочисленных регистров разделен на два отдельных набора регистров, один набор регистров для младших 32 битов данных и второй набор регистров для старших 32 битов данных. Набор 210 регистров с плавающей точкой одного варианта осуществления имеет 128-битовые элементы, потому что команды с плавающей точкой обычно имеют операнды разрядностью от 64 до 128 битов.

Исполнительный блок 211 содержит исполнительные устройства 212, 214, 216 218, 220, 222, 224, в которых и исполняются команды. Этот раздел включает в себя наборы 208, 210 регистров, в которых хранят целочисленные значения операндов и действительные значения операндов с плавающей точкой, которые должны исполнить микрокоманды. Процессор 200 одного варианта осуществления состоит из нескольких исполнительных устройств: блок 212 генерации адресов (AGU), AGU 214, быстрый AGU 216, быстрое ALU 216, быстрое ALU 218, медленное ALU 220, ALU 222 для операций с плавающей точкой, блок 224 перемещения плавающей запятой. Для одного варианта осуществления исполнительные устройства 222, 224 с плавающей запятой выполняют операции с плавающей запятой, ММХ, SIMD и SSE или другие операции ALU 222 для операций с плавающей запятой одного варианта осуществления включает в себя делитель операндов с плавающей запятой 64 бита на 64 бита для микрокоманд выполнения деления, извлечения квадратного корня и нахождения остатка от деления. Для систем и способов, описанных в этом документе, команды, включающие в себя значение с плавающей запятой, могут быть обработаны аппаратурой с плавающей запятой. В одном варианте осуществления операции ALU поступают на высокоскоростные арифметико-логические исполнительные устройства 216, 218. Быстрые ALU 216, 218 одного варианта осуществления могут выполнять быстрые операции с эффективной латентностью, равной половине такта. Для одного варианта осуществления большинство сложных целочисленных операций поступает на медленное ALU 220, так как медленное ALU 220 включает в себя целочисленную исполнительную аппаратуру для операций с большой латентностью, такую как умножитель, регистры сдвига, флаговая логика и обработка ветвлений. Операции загрузки из/сохранения в памяти исполняют ALU 212, 214. Для одного варианта осуществления целочисленные ALU 216, 218, 220 описаны в контексте выполнения целочисленных операций над 64-битовыми операндами данных. В альтернативных вариантах осуществления могут быть реализованы ALU 216, 218, 220 с поддержкой данных различной разрядности, включая 16, 32, 128, 256 и т.д. Аналогично, могут быть реализованы блоки 222, 224 с плавающей запятой с поддержкой диапазона операндов, имеющих различную разрядность. Для одного варианта осуществления блоки 222, 224 с плавающей точкой могут оперировать 128-битовыми упакованными операндами данных в сочетании с SIMD и мультимедийными командами.

В одном варианте осуществления планировщики 202, 204, 206 микрокоманд отправляют зависимые операции до того, как будет завершено исполнение родительской нагрузки. Так как спекулятивное планирование и исполнение микрокоманд происходит в процессоре 200, процессор 200 также включает в себя логику для обработки промахов памяти. Если при загрузке данных из кэша данных происходит промах, то могут иметься зависимые операции в конвейере, которые оставили планировщик с временно некорректными данными. Механизм повтора отслеживает и заново исполняет команды, которые используют некорректные данные. Зависимые операции должны быть повторены, а независимые можно завершить. Планировщики и механизм повтора одного варианта осуществления процессора также сконструированы так, чтобы захватывать последовательности команд для операций сравнения текстовых строк.

Термин "регистры" может относиться к встроенным в процессор ячейкам памяти, которые используют как часть команд для идентификации операндов. Другими словами, регистры могут представлять собой ячейки, которые можно использовать за пределами процессора (с точки зрения программиста). Тем не менее, регистры варианта осуществления не следует ограничивать каким-либо определенным типом схем. Наоборот, регистр варианта осуществления может хранить и предоставлять данные и выполнять описанные в этом документе функции. Описанные в этом документе регистры могут быть реализованы схемой в процессоре с использованием любого числа различных технологий, как, например, специальные физические регистры, динамически выделяемые физические регистры с использованием псевдонимов регистров, сочетание специальных и динамически выделяемых физических регистров и т.д. В одном варианте осуществления в целочисленных регистрах хранят 32-битовые данные. Набор регистров одного варианта осуществления также содержит восемь мультимедийных SIMD регистров для упакованных данных. Для приведенного ниже обсуждения понимается, что регистры представляют собой регистры данных, предназначенные для хранения упакованных данных, такие как 64-битовые регистры ММХ (также в некоторых случаях называемые "mm" регистрами) в микропроцессорах, поддерживающих технологию ММХ™ от корпорации Intel, г. Санта-Клара, Калифорния. Эти ММХ регистры, доступные и в виде целочисленных регистров, и в виде регистров с плавающей точкой, могут оперировать упакованными элементами данных, которые сопровождают команды SIMD и SSE. Аналогично, 128-битовые ХММ регистры, относящиеся к SSE2, SSE3, SSE4 или к более поздней (в общем, называемые "SSEx") технологии, также могут использоваться для хранения таких упакованных операндов данных. В одном варианте осуществления при хранении упакованных данных и целочисленных данных не нужно различать регистры двух типов данных. В одном варианте осуществления целые числа и вещественные числа с плавающей точкой либо содержатся в одном и том же наборе регистров, либо в разных наборах регистров. Более того, в одном варианте осуществления данные с плавающей точкой и целочисленные данные могут храниться в различных регистрах или в одних и тех же регистрах.

На фиг. 3a-3b схематично показаны элементы микроархитектуры процессора в соответствии с одним или несколькими аспектами настоящего изобретения. На фиг. 3a конвейер 400 процессора включает в себя стадию 402 выборки, стадию 303 декодирования длины, стадию 406 декодирования, стадию 408 выделения, стадию 410 переименования, стадию 412 планирования (также известную как стадия диспетчеризации или выдачи), стадию 414 чтения из регистра/памяти, стадию 416 исполнения, стадию 418 обратной записи/записи в память, стадию 422 обработки исключений и стадию 424 подтверждения.

На фиг. 3b стрелками обозначены связи между двумя или несколькими блоками, а направление стрелки указывает на направление потока данных между этими блоками. На фиг. 3b показано процессорное ядро 490, включающее в себя препроцессный блок 430, соединенный с блоком 450 механизма исполнения команд, и оба они соединены с блоком 470 памяти.

Ядро 490 может представлять собой вычислительное ядро с сокращенным набором команд (RISC), ядро с полным набором команд (CISC), ядро с очень длинной машинной командой (VLIW) или гибридное ядро или ядро альтернативного типа. В качестве еще одной опции, ядро 490 может представлять собой ядро специального назначения, такое как, например, сетевое ядро или ядро связи, механизм сжатия, графическое ядро и т.п.

Препроцессный блок 430 включает в себя блок 432 предсказания ветвлений, соединенный с блоком 434 кэша команд, который соединен с буфером 436 быстрого преобразования адреса команд (TLB), который соединен с блоком 438 выборки команд, который соединен с блоком 440 декодирования. Блок декодирования или декодер может декодировать команды и вырабатывать в качестве выхода одну или несколько микроопераций, точек входа микрокода, микрокоманд, других команд или других управляющих сигналов, которые декодируют из исходных команд, иным образом отражают или получают из исходных команд. Декодер может быть реализован с использованием множества различных механизмов. Примеры подходящих механизмов включают в себя, но, не ограничиваясь, таблицы поиска, аппаратные реализации, программируемые логические матрицы (PLA), микрокодовые постоянные запоминающие устройства (ROM) и т.д. Блок 434 кэша команд также соединен с блоком 476 кэша 2 уровня (L2) в блоке 470 памяти. Блок 440 декодирования соединен с блоком 452 переименования/выделения в блоке 450 механизма исполнения команд.

Блок 450 механизма исполнения команд включает в себя блок 452 переименования/выделения, соединенный с блоком 454 отмены команд и набором из одного или нескольких блоков 456 планировщиков. Блоки 456 планировщиков представляют любое число различных планировщиков, включая резервирующие станции, центральное окно команд и т.д. Блоки 456 планировщиков соединены с блоками 458 наборов физических регистров. Каждый блок 458 набора физических регистров представляет один или несколько наборов физических регистров, причем различные наборы хранят один или несколько различных типов данных, таких как скалярные целые числа, скалярные числа с плавающей запятой, упакованные целые, упакованные с плавающей запятой, векторные целые, векторные с плавающей запятой и т.д., состояние (например, указатель команды, которые представляет собой адрес следующей команды, которую надо выполнить) и т.д. Блок(и) 458 наборов физических регистров перекрывается блоком 454 отмены команд, чтобы проиллюстрировать различные способы, которыми можно реализовать использование псевдонимов регистров и исполнение команд с изменением последовательности (например, с использованием буферов переупорядочивания и набора регистров отмены, с использованием будущих наборов, буфера истории и набора регистров отмены; с использованием карт регистров и пула регистров; и т.д.). В общем, архитектурные регистры видны за пределами процессора или с точки зрения программиста. Регистры не ограничены каким-либо известным типом схем. Подходят различные типы регистров, если только они могут хранить и предоставлять данные, как описано в этом документе. Примеры подходящих регистров включают в себя, но не ограничиваясь, специальные физические регистры, динамически выделяемые физические регистры с использованием псевдонимов регистров, сочетания специальных и динамически выделяемых регистров и т.д. Блок 454 отмены команд и блок(и) 458 наборов физических регистров соединены с кластером 460 исполнения. Кластер 460 исполнения включает в себя набор из одного ли нескольких исполнительных устройств 162 и набор из одного или нескольких блоков 464 обращения к памяти. Исполнительные устройства 462 могут выполнять различные операции (напр., сдвиги, сложение, вычитание, умножение) над различными типами данных (напр., скаляр с плавающей точкой, упакованное целое, упакованное с плавающей точкой, целочисленный вектор, вектор с плавающей точкой). Хотя некоторые варианты осуществления могут включать в себя несколько исполнительных устройств, предназначенных для специфических функций или наборов функций, другие варианты осуществления могут включать одно исполнительное устройство или несколько исполнительных устройств, каждое из которых выполняет все функции. Показано, что блоков 456 планировщиков, блоков 458 наборов физических регистров и кластеров 460 исполнения может быть несколько, потому что в некоторых вариантах осуществления создают отдельные конвейеры для определенных типов данных/операций (напр., конвейер целочисленных скаляров, конвейер скаляров с плавающей точкой/упакованных целых/упакованных с плавающей точкой/целочисленных векторов/векторов с плавающей точкой и/или конвейер обращения к памяти, каждый из которых имеет свой блок планировщика, блок наборов физических регистров и/или кластер исполнения - и в случае отдельного конвейера обращения к памяти реализованы некоторые варианты осуществления, в которых кластер исполнения этого конвейера имеет блок(и) 464 обращения к памяти). Также следует понимать, что там, где используют отдельные конвейеры, один или несколько из этих конвейеров может быть конвейером исполнения/выдачи с изменением порядка, а остальные - без изменения порядка.

Набор блоков 464 обращения к памяти соединен с блоком 470 памяти, который включает в себя блок 472 TLB данных, соединенный с блоком 474 кэша данных, соединенным с блоком 476 кэша второго уровня (L2). В одном примере осуществления блоки 464 обращения к памяти могут включать в себя блок загрузки, блок хранения адреса и блок хранения данных, каждый из которых соединен с блоком 472 TLB данных в блоке 470 памяти. Блок 476 кэша L2 соединен с одним или несколькими уровнями кэша и, в конечном счете, с основной памятью.

В качестве примера, типовое использование псевдонимов регистров, архитектура ядра с выдачей/исполнением с изменением порядка может реализовывать конвейер 400 следующим образом: блок 438 выборки команд выполняет стадии 402 и 404 выборки и декодирования длины; блок 440 декодирования выполняет стадию 406 декодирования; блок 452 переименования/выделения выполняет стадию 408 выделения и стадию 410 переименования; блок(и) 456 планировщиков выполняют стадию 412 планирования; блок(и) 458 наборов физических регистров и блок 470 памяти выполняют стадию 414 чтения из регистра/чтения из памяти; кластер 460 исполнения выполняет стадию 416 исполнения; блок 470 памяти и блок(и) 458 наборов физических регистров выполняют стадию 418 обратной записи/записи в память; различные блоки могут быть вовлечены в стадию 422 обработки исключений; и блок 454 отмены команд и блок(и) 458 наборов физических регистров выполняют стадию 424 подтверждения.

Ядро 490 может поддерживать один или несколько наборов инструкций (напр., набор инструкций х86 (с некоторыми расширениями, которые были добавлены в новых версиях); набор инструкций MIPS от MIPS Technologies, г. Саннивейл, шт. Калифорния; набор инструкций ARM (с дополнительными расширениями, такими как NEON) от ARM Holdings, г. Саннивейл, шт. Калифорния).

В некоторых вариантах осуществления ядро может поддерживать многопоточность (выполнение двух или более параллельных наборов операций или потоков) и может делать это несколькими способами, включая многопоточность с квантованием по времени, одновременную многопоточность (когда одно физическое ядро предоставляет логическое ядро для каждого потока, которые одновременно выполняет физическое ядро), или их сочетание (напр., получение и декодирование с квантованием по времени, а затем одновременная многопоточность, как, например, в технологии Intel® Hyperthreading).

Хотя показанный вариант осуществления процессора также включает в себя отдельные блоки 434/474 кэша данных и команд и блок 476 общего кэша L2, альтернативные варианты осуществления могут иметь один внутренний кэш и для команд, и для данных, как, например, внутренний кэш первого уровня (L1) или несколько уровней внутреннего кэша. В некоторых вариантах осуществления система может включать в себя сочетание внутреннего кэша и внешнего кэша, который является внешним по отношению к ядру и/или процессору. Как вариант, весь кэш может быть внешним по отношению к ядру и/или процессору.

На фиг. 4 показана блок-схема примера процессора 102 вычислительной системы 100 в соответствии с одним или несколькими аспектами настоящего изобретения. Со ссылкой на фиг. 4, процессорное ядро 490 может включать в себя блок 202 выборки для выборки команд для исполнения ядром 490. Команды могут быть получены из одного или нескольких запоминающих устройств, таких как память 115. Процессорное ядро 490 может также включать в себя блок 440 декодирования для декодирования полученной команды в одну или несколько микроопераций (uops). Процессорное ядро 490 также может включать в себя блок 446 планирования для хранения декодированной команды, полученной из блока 440 декодирования, пока команда не будет готова к выпуску, напр., пока значения операндов для декодированной команды не станут доступны. Блок 446 планирования может планировать и/или выпускать декодированные команды в исполнительное устройство 450.

Исполнительное устройство 450 может включать в себя один или несколько арифметических и логических блоков (ALU), один или несколько целочисленных исполнительных блоков, один или несколько исполнительных блоков с плавающей запятой и/или других исполнительных устройств. В некоторых реализациях исполнительное устройство 450 может выполнять команды с изменением порядка (ООО). Процессорное ядро 490 может также включать в себя блок 454 отмены команд для отмены исполненных команд после их подтверждения.

В некоторых реализациях процессор 102 также может включать в себя регистр 421 нижней границы стека, регистр 423 верхней границы стека и логическую схему 150 проверки границ стека. В одном иллюстративном примере процессор 102 может включать в себя пару регистров границ стека для каждого режима работы, напр., для 32-битового пользовательского режима, для 64-битового пользовательского режима и для привилегированного режима. Функционирование логической схемы проверки границ стека подробно описано ниже. Хотя на фиг. 4 логическая схема 150 показана внутри ядра 490, логическая схема 150 может быть выполнена в другом месте вычислительной системы 100. Более того, логическая схема 150 и/или некоторые ее компоненты могут быть общими для нескольких процессорных ядер.

В некоторых реализациях процессор 102 может реализовывать сегментацию памяти и/или страничную организацию памяти. Сегментация может обеспечивать механизм для изоляции отдельного кода, данных и модулей стека, так что несколько задач могут выполняться на одном и том же процессоре, не мешая друг другу. Страничная организация памяти может обеспечивать механизм для реализации системы памяти с подкачкой страниц по запросу, системы виртуальной памяти, когда участки среды выполнения задачи отображают при необходимости на физическую память. Страничная организация также может использоваться для обеспечивания изоляции между несколькими задачами.

Как схематично показано на фиг. 5, механизм сегментации может использоваться для разделения памяти, адресуемой процессором 102 (также называемой линейным адресным пространством), на меньшие защищенные адресные пространства, называемые сегментами. Сегменты могут использоваться для хранения кода, данных и стека для задачи и/или для хранения системных структур данных (таких как сегмент состояния задачи (TSS) или локальная таблица дескрипторов (LDT)). Если одновременно выполняется несколько задач, то каждой задаче могут быть назначены свои сегменты. Процессор 102 может обеспечить границы между этими сегментами и гарантировать, что одна задача не помешает выполнению другой задачи путем записи в сегменты другой задачи.

Все сегменты памяти могут содержаться в линейном адресном пространстве процессора. Для определения местоположения байта в отдельном сегменте может предоставляться логический адрес (также называемый дальним указателем). Логический адрес может включать в себя селектор сегмента и смещение. Селектор сегмента представляет собой уникальный идентификатор структуры данных, называемой дескриптором сегмента, расположенной в таблице дескрипторов (такой как глобальная таблица дескрипторов (GTD)). Каждый сегмент может иметь связанный с ним дескриптор сегмента, который определяет размер сегмента, права доступа и уровень привилегий для сегмента, тип сегмента и местоположение первого байта сегмента в линейном адресном пространстве (также называемое базовым адресом сегмента). Смещение логического адреса может быть добавлено к базовому адресу сегмента для определения местоположения байта в пределах сегмента. Таким образом, базовый адрес плюс смещение может дать линейный адрес в линейном адресном пространстве процессора.

Так как многозадачная операционная система может задать линейное адресное пространство намного большего размера, чем экономически обоснованный для содержания сразу всей физической памяти, то необходим некоторый способ "виртуализации" линейного адресного пространства. Эта виртуализация линейного адресного пространства может выполняться посредством механизма процессора страничной организации памяти. Страничная организация поддерживает окружение виртуальной памяти, когда большое линейное адресное пространства симулируется меньшим объемом оперативной памяти (RAM) и некоторым дисковым пространством. Каждый сегмент может быть разделен на страницы заданного размера (напр. 4 Кб), которые могут храниться либо в RAM, либо на диске. Операционная система может поддерживать каталог страниц и набор таблиц страниц для отслеживания страниц. Если задача пытается обратиться к адресу в линейном адресном пространстве, то процессор использует каталог страниц и таблицы страниц, чтобы перевести линейный адрес в физический адрес, а затем выполняет запрошенную операцию (чтение или запись) по этому адресу памяти. Если страница, к которой обращаются, в текущий момент не находится в физической памяти, то процессор прерывает выполнение программы (генерируя исключение ошибки страницы памяти). Операционная система тогда может считать страницу с диска и продолжить выполнение задачи. Если не используется страничная организация, то линейное адресное пространство процессора отображают непосредственно на физическое адресное пространство процессора. Физическое адресное пространство определяют как диапазон адресов, которые может выработать процессор на своей адресной шине.

Процессор 102 может использовать несколько сегментных регистров для поддерживания механизма сегментации. В некоторых реализациях процессор 102 может поддерживать типизацию сегментов, чтобы ограничить операции обращения в память, которые могут выполняться над определенными типами сегментов. Типизация сегментов может поддерживаться путем связывания типов памяти с сегментными регистрами. В одном примере процессор 102 может включать в себя по меньшей мере один регистр сегмента команд (который также может называться CS), два или более регистров сегмента данных (который также может называться DS, ES, FS и GS), и по меньшей мере один регистр сегмента стека (который также может называться SS).

В некоторых реализациях процессор 102 может оперировать в 32-битовом пользовательском режиме, в 64-битовом пользовательском режиме и в привилегированном режиме. В 32-битовом пользовательском режиме процессор 102 может поддерживать сегментацию и опционально страничную организацию памяти. В 64-битовом пользовательском режиме сегментация может быть отключена для создания плоского 64-битового линейного адресного пространства. Процессор может трактовать основание сегмента регистров сегментов, включая CS, DS, ES и SS, как ноль, создавая линейный адрес, который равен эффективному адресу.

В еще одном аспекте процессорный механизм защиты памяти может распознавать несколько уровней привилегий. Привилегированный режим может отличаться от 32-битового пользовательского режима или 64-битового пользовательского режима значением текущего уровня привилегий (CPL). В одном примере, схематически показанном на фиг. 6, уровни привилегий, также называемые кольцами защиты, можно пронумеровать от 0 до 3, при этом большие числа могут означать меньшие привилегии. Кольцо 0 защиты может быть зарезервировано для сегментов, содержащих наиболее привилегированный код, данные и стеки, такие, как ядро операционной системы. Другие кольца защиты могут использоваться для прикладных программ. В некоторых реализациях операционные системы могут использовать подмножество из нескольких колец защиты, напр., кольцо 0 для ядра операционной системы и кольцо 3 для приложений.

Процессор может использовать уровни привилегий для предотвращения доступа процесса, обладающего меньшим уровнем привилегий, к сегменту с большим уровнем привилегий. Текущий уровень привилегий (CLPL) представляет собой уровень привилегий для выполняемого в данный момент процесса. CPL может храниться в битах 0 и 1 сегментных регистров CS и SS. CPL может быть равен уровню привилегий сегмента кода, из которого получают команды. Процессор может изменить CPL, если программное управление передают в сегмент кода с другим уровнем привилегий. Процессор может выполнять проверку уровня привилегий путем сравнения CPL с уровнем привилегий сегмента или логического элемента вызова, к которому осуществляют обращение (уровень привилегий дескриптора, DPL), и/или с запрашиваемым уровнем привилегий (RPL), связанным с селектором сегмента, к которому выполняют обращение. Если процессор обнаруживает нарушение уровня привилегий, то он может выработать исключение общей защиты.

В некоторых реализациях процессор 102 может работать в привилегированном режиме или пользовательском режиме. Значения CPL 0, 1 или 2 могут соответствовать привилегированному режиму, значения CPL, равное 3, может соответствовать пользовательскому режиму. Текущий режим работы может определять, может ли процессор выполнять определенные команды и/или обращаться к определенным страницам памяти.

Как отмечалось выше, процессор 102 может предотвращать несанкционированное перемещение стека, используя пару регистров границ стека, включающую в себя регистр нижней границы стека и регистр верхней границы стека. В одном иллюстративном примере процессор 102 может иметь специальную пару регистров границ стека для 32-битового пользовательского режима, для 64-битового пользовательского режима и для привилегированного режима работы.

В некоторых реализациях процессор 102 может реализовывать логику проверки границ стека для сравнения адреса памяти, к которому обращаются через сегмент стека, со значениями, хранимыми в регистрах границ стека. На фиг. 7 схематично показан план памяти, доступной из сегмента стека вычислительной системы 100. Адресуемое пространство 502 памяти пользовательского режима может включать в себя первый диапазон 504 адресов, зарезервированный для стека 32-битового пользовательского режима, и второй диапазон 506 адресов, зарезервированный для стека 64-битового пользовательского режима. Адресуемое пространство 520 памяти привилегированного режима может включать в себя диапазон 522 адресов, зарезервированных для стека.

Регистр нижней границы стека и регистр верхней границы стека может использоваться для хранения диапазона адресов памяти, адресуемой с использованием сегмента стека. Как схематически показано на фиг. 7, регистры STKLBS и STKUBS могут использоваться для хранения нижней и верхней границ стека в привилегированном режиме, регистры STKLBU32 и STKUBU32 могут использоваться для хранения нижней и верхней границ стека в 32-битовом пользовательском режиме, а регистры STKLBU64 и STKUBU64 могут использоваться для хранения нижней и верхней границ стека в 64-битовом пользовательском режиме.

Логическая схема 150 проверки границ стека может проверять, попадает ли эффективный адрес операции обращения к памяти, которая использует сегмент стека, в допустимый диапазон, заданный парой регистров границ стека, соответствующих текущему режиму работы. Если эффективный адрес находится за пределами допустимого диапазона, установленного значениями регистров границ стека, то процессор может выработать исключение ошибки стека. Адрес, по которому обращаются через сегмент стека, может сохраняться процессором в регистре состояния стека перед генерацией исключения для использования логикой обработки исключений.

В одном иллюстративном примере логическая схема проверки границ стека может использовать сумматоры границ стека для сравнения адреса памяти, к которому выполняют обращение, со значениями нижней и верхней границ. Как вариант, логическая схема проверки границ стека может использовать специальные сумматоры для сравнения адреса памяти, к которому выполняют обращение, со значениями нижней и верхней границ.

В ответ на обнаружение обращения к памяти с использованием сегмента стека, логическая схема проверки границ стека может проверить, попадает ли эффективный адрес операции обращения в память, которая использует сегмент стека, в допустимый диапазон, заданный парой регистров границ стека для текущего режима работы, путем вычисления условий, представленных на фиг. 8а (пользовательский режим работы) и 8b (привилегированный режим работы).

Логическая схема проверки границ стека может проверить, что адрес памяти, к которому выполняют обращение (обозначенный на фиг. 8а-8b через mem_ss), меньше или равен значению, сохраненному в регистре верхней границы стека для текущего режима работы, и больше или равен значению, сохраненному в регистре нижней границы стека для текущего режима работы. Если условие не выполнено, то процессор может сохранить в регистре состояния стека адрес, к которому выполняется обращение через сегмент стека, и сгенерировать исключение ошибки стека.

В еще одном аспекте процессор 102 может содержать два или более регистра, которые можно использовать для адресации сегмента стека, напр., регистр базового указателя и регистр сегмента стека (SS). Процессор 102 может быть выполнен с возможностью задействования и отключения логической схемы проверки границ стека в зависимости от того, какой регистр используется для адресации памяти, к которой осуществляют доступ. В одном иллюстративном примере процессор 102 может задействовать логическую схему проверки границ стека, если адрес памяти, к которому осуществляют доступ, хранится с использованием регистра SP, и отключать логическую схему проверки границ стека, если адрес памяти, к которому осуществляют доступ, хранится в регистре BP.

В еще одном аспекте значения регистров границ стека могут быть переключаемыми в зависимости от контекста с использованием команд сохранения/восстановления состояния процессора (напр., XSAVE/XRSTOR). Команда сохранения состояния процессора (напр., XSAVE) может вызвать сохранение полного или частичного состояния процессора в ячейку памяти, заданную операндом. Команда восстановления состояния процессора (напр., XRSTOR) может вызвать загрузку полного или частичного состояния процессора из ячейки памяти, заданной операндом. Подмножество компонентов состояния процессора, которые надо сохранить/восстановить, может быть задано неявным операндом маски (напр., через пару регистров EDX:EAX). В одном иллюстративном примере процессор может быть сконфигурирован так, чтобы допускать модификацию значений регистров границ стека в только привилегированном регистре.

В некоторых реализациях при выполнении команды XRSTOR процессор может проверить, равно ли ранее сохраненное значение проверки целостности заданному хешу от границ стека и заданного значения ключа:

STK_ICV_S=HASH(STKLBx, STKUBx, STK_x_KEY)

где STK_ICV_S - значение проверки целостности,

HASH - заданная хеш-функция,

STKLBx и STKUBx - соответственно нижняя и верхняя граница стека для текущего режима работы, и

STK_x_KEY - значение ключа для текущего режима работы.

Если значение проверки целостности равно хешу от значений границ стека и значения ключа, то процессор может восстановить значения границы стека из памяти; в противном случае процессор может присвоить предварительно заданные значения границ соответствующим регистрам границ стека. Начальные значения проверки целостности, значения ключа и значения границ стека могут быть установлены операционной системой, напр., во время создания потока или процесса.

В еще одном аспекте процессор 102 может также реализовывать пару команд для задействования/отключения логической схемы проверки границ стека, и бит состояния, показывающий задействована ли логическая схема проверки границ стека или отключена. В ответ на получение команды задействования проверки стека (STKENB) процессор 102 может установить бит STKENABLE и задействовать обнаружение попыток несанкционированного перемещения стека посредством логической схемы проверки границ стека. В ответ на получение команды отключения проверки стека процессор 102 может очистить бит STKENABLE и отключить обнаружение нарушения границ стека посредством логической схемы проверки границ стека.

В некоторых реализациях операционная система, запущенная на вычислительной системе 100, может задействовать логическую схему проверки стека путем выдачи команды включения проверки стека. Операционная система также может установить значения регистров границ стека для каждого выполняемого процесса и/или потока. Значения регистров границ стека могут быть частью записи контекста потока/процесса, и, таким образом, переключение контекста с использованием команд XSAVE/XRSTOR может охватывать сохранение/восстановление значений границ стека вместе со значением указателя стека.

На фиг. 9 показана блок-схема последовательности операций способа детектирования несанкционированного перемещения стека в соответствии с одним или несколькими аспектами настоящего изобретения. Способ 900 может быть выполнен вычислительной системой, которая может содержать аппаратное обеспечение (напр., схему, специальную логику и/или программируемую логику), программное обеспечение (напр., команды, выполняемые на вычислительной системе для аппаратного моделирования) или их сочетание. Способ 900 и/или каждая из его функций, процедур, подпрограмм или операций может быть выполнен одним или несколькими физическими процессорами вычислительной системы, выполняющей способ. Две или более функций, процедур, подпрограмм или операций способа 900 могут быть выполнены параллельно или по порядку, который может отличаться от описанного выше порядка. В одном примере, как показано на фиг. 9, способ 900 может быть выполнен вычислительной системой, показанной на фиг. 1.

Со ссылкой на фиг. 9, на этапе 910 процессор вычислительной системы 100 может сохранить в регистре нижней границы стека адрес в памяти, обозначающий нижнюю границу памяти, адресуемой через сегмент стека.

На этапе 920 процессор может сохранить в регистре верхней границы стека адрес в памяти, обозначающий верхнюю границу памяти, адресуемой через сегмент стека. Как отмечалось выше, в некоторых реализациях процессор может иметь специальную пару регистров границ стека, включающую в себя регистр нижней границы стека и регистр верхней границы стека для 32-битового пользовательского режима, 64-битового пользовательского режима и привилегированного режима.

В ответ на определение на этапе 930 обращения в память через сегмент стека процессор на этапе 940 может проверить, что адрес памяти, к которому обращаются, находится в диапазоне, заданном регистрами границ стека, путем вычисления условий, представленных на фиг. 8а (для пользовательского режима работы) и 8b (для привилегированного режима работы).

Если адрес памяти, к которому обращаются, попадает в допустимый диапазон, то процесс продолжается на этапе 950; в противном случае на этапе 960 процессор может сохранить адрес памяти, к которому обращаются, в регистре состояния стека.

На этапе 970 процессор может сгенерировать исключение ошибки стека.

Следующие примеры показывают различные реализации в соответствии с одним или несколькими аспектами настоящего изобретения.

Пример 1 представляет собой систему обработки данных, содержащую: регистр нижней границы стека, выполненный с возможностью хранить первый адрес памяти, причем первый адрес памяти обозначает нижнюю границу памяти, адресуемой через сегмент стека; регистр верхней границы стека, выполненный с возможностью хранить второй адрес памяти, причем второй адрес памяти обозначает верхнюю границу памяти, адресуемой через сегмент стека; и логическую схему проверки границ стека, выполненную с возможностью определять несанкционированное перемещение стека путем сравнения адреса памяти, к которому обращаются через сегмент стека, по меньшей мере с первым адресом памяти и вторым адресом памяти.

В примере 2 логическая схема проверки границ стека системы обработки данных примера 1 может содержать первый сумматор, выполненный с возможностью сравнивать адрес памяти, к которому обращаются через сегмент стека, с первым адресом памяти, и второй сумматор, выполненный с возможностью сравнивать адрес памяти, к которому обращаются через сегмент стека, со вторым адресом памяти.

В примере 3 логическая схема проверки границ стека системы обработки данных примера 1 может быть также сконфигурирована так, чтобы генерировать исключение ошибки стека в ответ по меньшей мере на одно из следующего: определение, что адрес памяти, к которому обращаются через сегмент стека, меньше, чем первый адрес памяти, или определение, что адрес памяти, к которому обращаются через сегмент стека, больше, чем второй адрес памяти.

В примере 4 система обработки данных примера 1 может также содержать регистр состояния стека, а логическая схема проверки границ стека может быть также сконфигурирована так, чтобы сохранять в регистре состояния стека адрес памяти, к которому обращаются через сегмент стека.

В примере 5 система обработки данных примера 1 может быть сконфигурирована так, чтобы работать по меньшей мере в одном из следующих режимов: 32-битовый пользовательский режим, 64-битовый пользовательский режим или привилегированный режим; и система обработки данных также содержать по меньшей мере одно из следующего: первый регистр нижней границы стека и первый регистр верхней границы стека для 32-битового пользовательского режима, второй регистр нижней границы стека и второй регистр верхней границы стека для 64-битового пользовательского режима, и третий регистр нижней границы стека и третий регистр верхней границы стека для привилегированного режима.

В примере 6 логическая схема проверки границ стека системы обработки данных примера 1 может быть также сконфигурирована так, чтобы в ответ на получение команды сохранения состояния процессора сохранять в специальной ячейке памяти значения регистра нижней границы стека и регистра верхней границы стека.

В примере 7 логическая схема проверки границ стека системы обработки данных примера 1 может быть также сконфигурирована так, чтобы в ответ на получение команды восстановления состояния процессора загружать из специальной ячейки памяти значения регистра нижней границы стека и регистра верхней границы стека.

В примере 8 логическая схема проверки границ стека системы обработки данных примера 1 может быть также сконфигурирована так, чтобы проверять, совпадает ли значение проверки целостности со значением заданной хеш-функции от значения регистра нижней границы стека, значения верхней границы стека и заданного значения ключа.

В примере 9 система обработки данных примера 1 может быть сконфигурирована так, чтобы работать по меньшей мере в одном из следующих режимов: пользовательский режим или привилегированный режим; а логическая схема проверки границ стека может быть сконфигурирована так, чтобы отключать изменение значений регистра нижней границы стека и регистра верхней границы стека при работе в пользовательском режиме.

В примере 10 система обработки данных примера 1 может также содержать регистр базового указателя (BP) и регистр указателя стека (SP); а логическая схема проверки границ стека может быть сконфигурирована так, чтобы сохранять адрес памяти, к которому обращаются через сегмент стека, используя SP регистр или BP регистр.

В примере 11 логическая схема проверки границ стека системы обработки данных примера 10 может быть также сконфигурирована так, чтобы задействовать определение несанкционированного перемещения стека, если адрес памяти, к которому обращаются, сохранен с использованием SP регистра; и может быть также сконфигурирована так, чтобы отключать определение несанкционированного перемещения стека, если адрес памяти, к которому обращаются, сохранен с использованием BP регистра.

В примере 12 логическая схема проверки границ стека системы обработки данных примера 1 может быть также сконфигурирована так, чтобы в ответ на получение команды задействования проверки стека задействовать определение несанкционированного перемещения стека; и может быть также сконфигурирована так, чтобы в ответ на получение команды отключения проверки стека отключать определение несанкционированного перемещения стека.

Пример 13 представляет собой способ определения несанкционированного перемещения стека, содержащий следующее: посредством системы обработки данных сохраняют первый адрес памяти в регистре нижней границы стека, причем первый адрес памяти обозначает нижнюю границу памяти, адресуемой через сегмент стека; сохраняют второй адрес памяти в регистре верхней границы стека, причем второй адрес памяти обозначает верхнюю границу памяти, адресуемой через сегмент стека; определяют обращение к памяти через сегмент стека; и сравнивают адрес памяти, к которому обращаются через сегмент стека, по меньшей мере с первым адресом памяти и вторым адресом памяти, чтобы обнаружить несанкционированное перемещение стека.

В примере 14 способ примера 13 может также содержать следующее: сохраняют в регистре состояния стека адрес памяти, к которому обращаются через сегмент стека.

В примере 15 способ примера 13 может также содержать следующее: определяют, что адрес памяти, к которому обращаются через сегмент стека, меньше, чем первый адрес памяти; и генерируют исключение ошибки стека.

В примере 16 способ примера 13 может также содержать следующее: определяют, что адрес памяти, к которому обращаются через сегмент стека, больше, чем второй адрес памяти; и генерируют исключение ошибки стека.

В примере 17 способ примера 13 может также содержать следующее: принимают команду сохранения состояния процессора; и сохраняют в памяти значение регистра нижней границы стека и значение регистра верхней границы стека.

В примере 18 способ примера 13 может также содержать следующее: принимают команду восстановления состояния процессора; и загружают из памяти значение регистра нижней границы стека и значение регистра верхней границы стека.

В примере 19 способ примера 13 может также содержать следующее: принимают команду восстановления состояния процессора; определяют, что значение проверки целостности совпадает со значением заданной хеш-функции от значения регистра нижней границы стека, значения верхней границы стека и заданного значения ключа; и загружают значения границ стека в регистр нижней границы стека и регистр верхней границы стека.

Пример 20 представляет собой устройство, содержащее память и систему обработки данных, соединенную с памятью, причем система обработки данных сконфигурирована так, чтобы выполнять способ любого из примеров 13-19.

Пример 21 представляет собой машинный постоянный носитель информации, содержащий исполняемые команды, при выполнении которых системой обработки данных эта система обработки данных выполняет следующие операции: сохраняют первый адрес памяти в регистре нижней границы стека, причем первый адрес памяти обозначает нижнюю границу памяти, адресуемой через сегмент стека; сохраняют второй адрес памяти в регистре верхней границы стека, причем второй адрес памяти обозначает верхнюю границу памяти, адресуемой через сегмент стека; определяют обращение к памяти через сегмент стека; и сравнивают адрес памяти, к которому обращаются через сегмент стека, по меньшей мере с первым адресом и вторым адресом, чтобы обнаружить попытку нарушения границ стека.

В примере 22 машинный постоянный носитель информации примера 21 также может содержать исполняемые команды, заставляющие вычислительную систему сохранять в регистре состояния стека адрес памяти, к которому обращаются через сегмент стека.

В примере 22 машинный постоянный носитель информации примера 21 также может содержать исполняемые команды, заставляющие вычислительную систему определять, что адрес памяти, к которому обращаются через сегмент стека, меньше, чем первый адрес памяти, и генерировать исключение ошибки стека.

В примере 24 машинный постоянный носитель информации примера 21 также может содержать исполняемые команды, заставляющие вычислительную систему определять, что адрес памяти, к которому обращаются через сегмент стека, больше, чем второй адрес памяти, и генерировать исключение ошибки стека.

В примере 25 машинный постоянный носитель информации примера 21 также может содержать исполняемые команды, заставляющие вычислительную систему принимать команду сохранения состояния процессора и сохранять в памяти значение регистра нижней границы стека и значение регистра верхней границы стека.

В примере 26 машинный постоянный носитель информации примера 21 также может содержать исполняемые команды, заставляющие вычислительную систему принимать команду восстановления состояния процессора и загружать из памяти значение регистра нижней границы стека и значение регистра верхней границы стека.

В примере 27 машинный постоянный носитель информации примера 21 также может содержать исполняемые команды, заставляющие вычислительную систему принимать команду восстановления состояния процессора; определять, что значение проверки целостности совпадает со значением заданной хеш-функции от значения регистра нижней границы стека, значения верхней границы стека и заданного значения ключа; и загружать значения границ стека в регистр нижней границы стека и регистр верхней границы стека.

Некоторые части подробного описания представлены в терминах алгоритмов и символьных представлений операций над битами данных в компьютерной памяти. Эти алгоритмические описания и представления представляют собой средство, используемое специалистами в области обработки данных, чтобы наиболее эффективно донести сущность своей работы другим специалистам. Под алгоритмом здесь и в целом понимается непротиворечивая последовательность операций, приводящих к желаемому результату. Операции - это требуемые физические манипуляции физическими величинами. Обычно, хотя не обязательно, эти величины принимают форму электрических или магнитных сигналов, которые можно хранить, передавать, сочетать, сравнивать и манипулировать ими иными способами. Временами удобно, в основном по причинам повсеместного использования, называть эти сигналы битами, значениями, элементами, символами, знаками, термами, числами и т.п.

Тем не менее, следует иметь в виду, что все эти и аналогичные термины надо связывать с подходящими физическими величинами, и что они представляют собой всего лишь удобные метки, примененные к этим величинам. Если специально не указано обратное, как очевидно из вышеприведенного обсуждения, понятно, что в описании, обсуждения, использующие термины, такие как "зашифрование", "расшифрование", "сохранение", "предоставление", "извлечение", "получение", "прием", "аутентификация", "удаление", "исполнение", "запрашивание", "передача" и т.п., относятся к действиям и процессам вычислительной системы или аналогичного электронного вычислительного устройства, которые манипулируют и преобразуют данные, представленные в виде физических (напр., электронных) величин в регистрах и запоминающих устройствах вычислительной системы, в другие данные, также представленные в виде физических величин в запоминающих устройствах или регистрах вычислительной системы или других таких устройствах хранения, передачи информации или устройствах отображения.

Подразумевается, что слова "пример" или "примерный" используют в этом документе, для обозначения примера, образца или иллюстрации. Любой аспект или конструкция, описанная в этом документе как "пример" или "примерная", не обязательно должна толковаться в качестве предпочтительной или преимущественной по сравнению с другими аспектами или конструкциями. Наоборот, использование слов "пример" или "примерный" предназначено для представления концепций в определенной форме. Полагается, что используемый в этой заявке термин "или" означает включающее "или", а не исключающее "или". То есть, если иное не сказано или не ясно из контекста, то полагается, что "X включает в себя А или В" означает любую из естественных включающих перестановок То есть, если X включает в себя А; X включает в себя В; или X включает в себя и А, и В, то "X включает в себя А или В" удовлетворяет любому из вышесказанных случаев. Кроме того, следует понимать, что использование в этой заявке и прилагаемой формуле изобретения неопределенных артиклей означает "один или несколько", если не сказано или не ясно из контекста, что имеется в виду форма единственного числа. Более того, не предполагается, что использование термина "вариант осуществления" или "один вариант осуществления" или "реализация" или "одна реализация" означает один и тот же вариант осуществления или реализацию, если это не указано. Также, термины "первый", "второй", "третий", "четвертый" и т.д., используемые в этом документе, рассматриваются в качестве меток для различения различных элементов и не обязательно имеют порядковое значение в соответствии с их числовым обозначением.

Описанные в этом документе варианты осуществления также относятся к устройству для выполнения действий. Это устройство может быть специально построено для требуемых целей, либо оно может содержать компьютер общего назначения, приводимый в действие по выбору, либо может быть реконфигурировано компьютерной программной, хранимой в компьютере. Такая компьютерная программа может храниться на постоянном машинной носителе информации, таком как любой тип дисков, включая флоппи-диски, оптические диски, CD-ROM и магнито-оптические диски, постоянные запоминающие устройства (ROM), запоминающие устройства с произвольным доступом (RAM), EPROM, EEPROM, магнитные или оптические карты, флеш-память или носитель любого типа, пригодный для хранения электронных команд. Следует считать, что термин "машинный носитель информации" включает в себя один носитель или несколько носителей (напр., централизованная или распределенная база данных и/или соответствующие кэши и серверы), которые хранят один или несколько наборов команд. Также следует считать, что термин "машинный носитель" включает в себя любой носитель, который может хранить, кодировать или переносить набор команд для выполнения машиной, и которые заставляют машину выполнять любую одну или несколько методологий настоящих вариантов осуществления. Также следует считать, что термин "машинный носитель информации" включает в себя, но не ограничиваясь, твердотельную память, оптические носители, магнитные носители, любой носитель, который может хранить набор команд для выполнения машиной, и которые заставляют машину выполнять любую одну или несколько методологий настоящих вариантов осуществления.

Алгоритмы и отображения, представленные в этом документе, не являются присущими какому-либо определенному компьютеру или иному устройству. С программами в соответствии с изложенными идеями можно использовать различные системы общего назначения, либо может быть удобно построить более специализированное устройство для выполнения действий требуемого способа. Требуемая структура различных таких систем будет понятна из приведенного ниже описания. Кроме того, настоящие варианты осуществления не описаны со ссылкой на какой-либо определенный язык программирования. Понятно, что можно использовать множество языков программирования для реализации идей вариантов осуществления, описанных в этом документе.

В приведенном выше описании изложено множество специфических деталей, таких как примеры специфических систем, компонентов, способов и т.д., чтобы обеспечить более хорошее понимание нескольких вариантов осуществления. Тем не менее, специалистам в области техники понятно, что по меньшей мере некоторые варианты осуществления можно использовать на практике без этих специфических деталей. В других случаях широко известные компоненты или способы не описаны подробно, или представлены в формате простой блок-схемы, чтобы предотвратить ненужного загромождения настоящих вариантов осуществления. Таким образом, изложенные выше специфические детали являются только примерными. Конкретные реализации могут отличаться от этих примерных деталей, но все еще будут попадать под объем настоящих вариантов осуществления.

Следует понимать, что приведенное выше описание полагается иллюстративным, а не ограничивающим. Специалистам в области техники будут очевидны многие другие варианты осуществления по прочтении и понимании вышеприведенного описания. Поэтому, объем настоящих вариантов осуществления, должен определяться со ссылкой на прилагаемую формулу изобретения со всеми правомочными эквивалентами.

Группа изобретений относится к вычислительной технике. Техническим результатом является предотвращение несанкционированной модификации стека. Способ содержит этапы, на которых: посредством системы обработки данных сохраняют первый адрес памяти в регистре нижней границы стека, причем регистр нижней границы стека связан с по меньшей мере одним из следующих режимов: 32-битовый пользовательский режим, 64-битовый пользовательский режим или привилегированный режим, первый адрес памяти обозначает нижнюю границу памяти, адресуемой через сегмент стека; сохраняют второй адрес памяти в регистре верхней границы стека, причем регистр верхней границы стека связан с по меньшей мере одним из следующих режимов: 32-битовый пользовательский режим, 64-битовый пользовательский режим или привилегированный режим, второй адрес памяти обозначает верхнюю границу памяти, адресуемой через сегмент стека; определяют обращение к памяти через сегмент стека; и детектируют несанкционированное перемещение стека путем сравнения адреса памяти, к которому обращаются через сегмент стека, по меньшей мере с первым адресом памяти и вторым адресом памяти. 3 н. и 16 з.п. ф-лы, 11 ил.

1. Система обработки данных, содержащая:

регистр нижней границы стека для по меньшей мере одного из следующих режимов: 32-битовый пользовательский режим, 64-битовый пользовательский режим или привилегированный режим, выполненный с возможностью хранить первый адрес памяти, причем первый адрес памяти обозначает нижнюю границу памяти, адресуемой через сегмент стека;