Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), СВЧ-усилителях, компараторах, непрерывных стабилизаторах напряжения и т.п.).

В современной микроэлектронике находят применение классические дифференциальные операционные усилители (ДУ) с двумя резисторами в коллекторной цепи входных транзисторов [1-17]. Данная архитектура является основой широкого класса аналоговых и цифровых устройств и является базовой как для существующих, так и для принципиально новых нанотехнологий [10].

Наиболее близким по технической сущности к заявляемому устройству является входной дифференциальный каскад в устройстве по патенту US 6.285.245 fig. 1.

Существенный недостаток известного ДУ, архитектура которого присутствует также в других усилительных каскадах [1-17], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Ку) получается небольшим (Kymax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными. Поэтому для повышения Ку применяются так называемые динамические нагрузки (ДН), например, на биполярных транзисторах, которые требуют для обеспечения линейного режима работы UДН=0,8÷1,6 В статического напряжения между источником питания и выходом ДН. Причем, численные значения UДН равны 0,8 В для простейших динамических нагрузок, имеющих, к сожалению, невысокое выходное сопротивление:

где UЭрли - напряжение Эрли выходного р-n-р транзистора ДН;

Iэ=I0 - статический ток эмиттера р-n-р выходного транзистора ДН.

Для интегральных транзисторов UЭрли=20÷30 В. Следовательно, при I0=1 мА применение классических динамических нагрузок не позволяет получить Ку>200÷300. Более высокие выходные сопротивления RДН реализуются в токовых зеркалах Вильсона или каскодных схемах. Однако они работают только в том случае, когда статическое напряжение между выводами такой динамической нагрузки более чем 2Uэб≥1,6 В. При низковольтном питании это не приемлемо. Кроме этого, не все техпроцессы (например, внедряемый в России SGB25VD) допускают использование р-n-р транзисторов. Для других технологий (НПО «Интеграл» г.Минск) применение р-n-р транзисторов не рекомендуется в условиях радиационного воздействия на микроэлектронное изделие.

Таким образом, при малых напряжениях питания, а особенно в тех случаях, когда требуется получить более-менее значительные амплитуды выходного напряжения, известные схемотехнические решения ДУ не эффективны.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании.

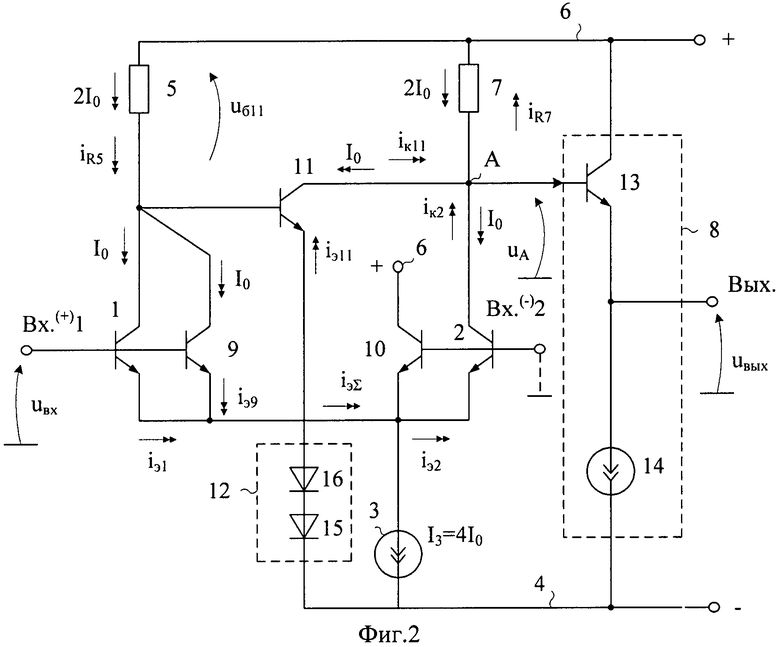

Поставленная задача решается тем, что в дифференциальном операционном усилителе с малым напряжением питания фиг.1, содержащем первый 1 и второй 2 входные транзисторы, объединенные эмиттеры которых через первый 3 токостабилизирующий двухполюсник соединены с шиной первого 4 источника питания, коллектор первого 1 входного транзистора через первый 5 двухполюсник коллекторной нагрузки связан с шиной второго 6 источника питания, коллектор второго 2 входного транзистора через второй 7 двухполюсник коллекторной нагрузки связан с шиной второго 6 источника питания и соединен со входом буферного усилителя 8, предусмотрены новые элементы и связи - в схему введены третий 9 и четвертый 10 входные транзисторы, а также дополнительный транзистор 11, база третьего 9 входного транзистора соединена с базой первого 1 входного транзистора, эмиттер третьего 9 входного транзистора соединен с эмиттером первого 1 входного транзистора, коллектор третьего 9 входного транзистора соединен с базой вспомогательного транзистора 11 и коллектором первого 1 входного транзистора, база четвертого 10 входного транзистора соединена с базой второго 2 входного транзистора, эмиттер четвертого 10 входного транзистора соединен с эмиттером второго 2 входного транзистора, коллектор четвертого 10 входного транзистора соединен с шиной второго 6 источника питания, коллектор дополнительного транзистора 11 соединен со входом буферного усилителя 8, а эмиттер дополнительного транзистора 11 подключен к шине первого 4 источника питания через цепь согласования потенциалов 12. В частном случае буферный усилитель реализован на транзисторе 13 и двухполюснике 14, а цепь согласования потенциалов 12 содержит два р-n перехода 15 и 16.

На фиг.1 показана схема ДУ-прототипа.

Схема заявляемого устройства, соответствующего п.1 и п.2 формулы изобретения, показана на фиг.2.

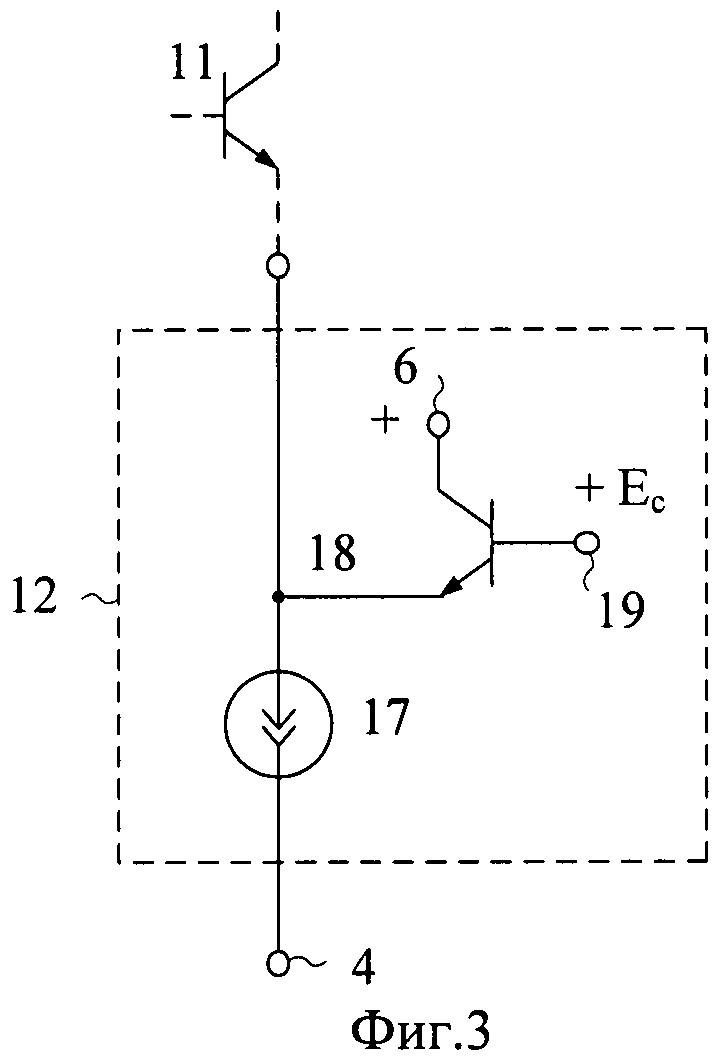

На фиг.3 показана схема цепи согласования потенциалов 12 в соответствии с п.3 формулы изобретения.

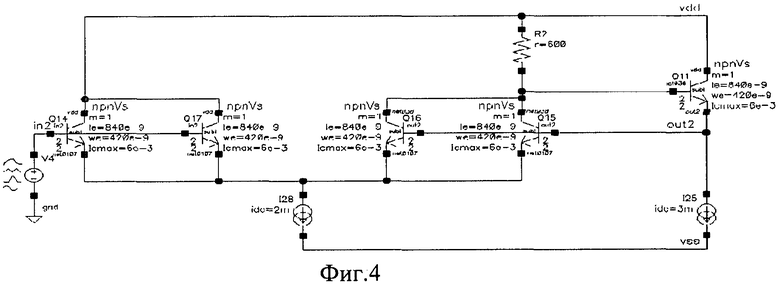

На фиг.4 представлена схема ДУ-прототипа фиг.1 в среде компьютерного моделирования Cadence на моделях SiGe интегральных транзисторов, а на фиг.5 - заявляемого ДУ фиг.2.

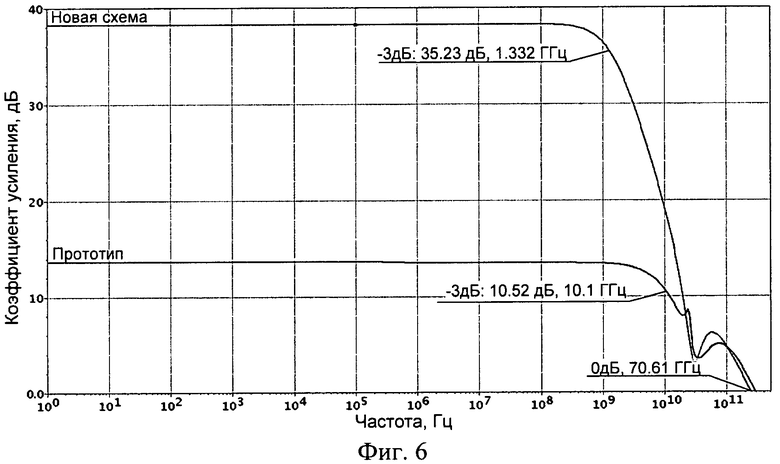

График фиг.6 характеризует частотную зависимость коэффициента усиления по напряжению (Ку) ДУ фиг.4 и фиг.5.

Дифференциальный операционный усилитель с малым напряжением питания фиг.2 содержит первый 1 и второй 2 входные транзисторы, объединенные эмиттеры которых через первый 3 токостабилизирующий двухполюсник соединены с шиной первого 4 источника питания, коллектор первого 1 входного транзистора через первый 5 двухполюсник коллекторной нагрузки связан с шиной второго 6 источника питания, коллектор второго 2 входного транзистора через второй 7 двухполюсник коллекторной нагрузки связан с шиной второго 6 источника питания и соединен со входом буферного усилителя 8. В схему введены третий 9 и четвертый 10 входные транзисторы, а также дополнительный транзистор 11, база третьего 9 входного транзистора соединена с базой первого 1 входного транзистора, эмиттер третьего 9 входного транзистора соединен с эмиттером первого 1 входного транзистора, коллектор третьего 9 входного транзистора соединен с базой вспомогательного транзистора 11 и коллектором первого 1 входного транзистора, база четвертого 10 входного транзистора соединена с базой второго 2 входного транзистора, эмиттер четвертого 10 входного транзистора соединен с эмиттером второго 2 входного транзистора, коллектор четвертого 10 входного транзистора соединен с шиной второго 6 источника питания, коллектор дополнительного транзистора 11 соединен со входом буферного усилителя 8, а эмиттер дополнительного транзистора 11 подключен к шине первого 4 источника питания через цепь согласования потенциалов 12.

На фиг.2, в соответствии с п.2 формулы изобретения, цепь согласования потенциалов 12 содержит N>1 последовательного выключенных прямосмещенных р-n переходов. В частных случаях в качестве этой цепи могут применяться стабилитроны.

На фиг.3, в соответствии с п.3 формулы изобретения, цепь согласования потенциалов 12 содержит вспомогательный токостабилизирующий двухполюсник 17, вспомогательный транзистор 18 и дополнительный источник напряжения смещения 19, связанный с базой вспомогательного транзистора 18, причем эмиттер вспомогательного транзистора 18 соединен со вспомогательным токостабилизирующим двухполюсником 17, а его коллектор связан с шиной второго 6 источника питания.

Схема ДУ-прототипа в среде Cadance на моделях SiGe транзисторов приведена на фиг.4, а заявляемого ДУ - на фиг.5.

Амплитудно-частотные характеристики сравниваемых ДУ (фиг.4, фиг.5) приведены на фиг.6.

Статический режим ДУ фиг.2 устанавливается первым 3 токостабилизирующим двухполюсником, в качестве которого могут применяться как резисторы, так и более совершенные схемы источников тока с малыми выходными проводимостями.

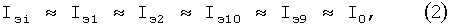

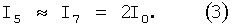

Если выбрать ток I3=4I0, то статические токи эмиттеров транзисторов 1, 9, 10, 2 и двухполюсников 5 и 7

Таким образом, при введении транзисторов 9, 10, а также за счет подключения коллектора транзистора 10 к источнику питания 6 в схеме фиг.2 созданы условия, при которых эмиттерные токи транзисторов 1, 9, 10, 2 одинаковы. Это минимизирует напряжение смещения нуля ДУ, которое зависит от идентичности эмиттерных токов транзисторов 1, 9 и 10, 2.

Следовательно, схема фиг.2 (так же как и ДУ фиг.1) имеет малый нулевой уровень, характеризующийся э.д.с. смещения нуля.

Рассмотрим работу ДУ фиг.2 на переменном токе.

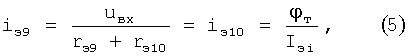

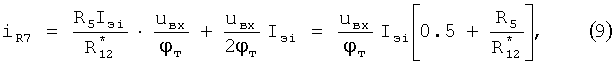

Положительное изменение входного напряжения uвх приводит к изменению эмиттерных токов транзисторов 1, 9 и 2, 10:

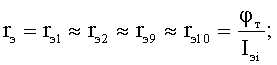

где rэi - сопротивление эмиттерного перехода i-го транзистора при статическом эмиттерном токе Iэi;

φт≈25 мВ - температурный потенциал.

Причем суммарное изменение токов общей эмиттерной цепи iэΣ=iэ9+iэ1=iэ10+iэ2.

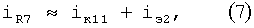

Приращения iэ1, iэ9 и iэ2 передаются в двухполюсники коллекторной нагрузки 5 и 7:

где  iк11≈iэ11 - приращение коллекторного тока транзисторов 11, вызванное изменением напряжения на первом 5 двухполюснике коллекторной нагрузки:

iк11≈iэ11 - приращение коллекторного тока транзисторов 11, вызванное изменением напряжения на первом 5 двухполюснике коллекторной нагрузки:

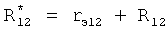

где  - эквивалентное сопротивление в эмиттерной цепи транзистора 11.

- эквивалентное сопротивление в эмиттерной цепи транзистора 11.

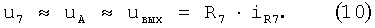

Таким образом, суммарное приращение тока через двухполюсник 7 и напряжение на нем:

В этой связи коэффициент усиления ДУ фиг.2:

В ДУ-прототипе:

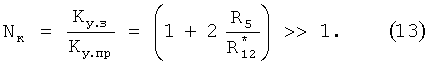

Следовательно, выигрыш по Ку, который дает предлагаемое техническое решение:

Данные теоретические выводы подтверждаются результатами компьютерного моделирования фиг.6, которые показывают, что предлагаемый усилитель имеет в 10 раз более высокое усиление.

Реализация цепи согласования в соответствии с п.3 формулы изобретения (фиг.3) создает дополнительные преимущества в обеспечении более высокой температурной стабильности статического режима заявляемого ДУ.

Таким образом, в предлагаемом ДУ фиг.2 при низкоомных резисторах коллекторной нагрузки 5 и 7 реализуются более высокие значения коэффициента усиления по напряжению.

Заявляемая схема особенно перспективна для использования в микроэлектронных SiGe изделиях СВЧ-устройств.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.541.464

2. Патентная заявка WO 2004/102789

3. Патент США №5.389.893

4. Патент Японии JP 53-142849

5. А.св. СССР 1102019

6. Патентная заявка WO 2005/077525

7. Патентная заявка США №2006/0181348

8. Патентная заявка WO 2006/077525

9. Патент Англии GB 2419052

10. Патентная заявка США №2008/0290941

11. Патент WO 96/21271

12. Патентная заявка США 2009/0108882 fig. 3

13. Патент Японии JP 55030218

14. Патент Англии GB 1350352

15. Патент Японии JP 54-47467

16. Патент Японии JP 55099810

17. Патент ФРГ DE 2821942

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432666C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2435293C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2400924C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2436226C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2439787C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2513482C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446556C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), СВЧ-усилителях, компараторах, непрерывных стабилизаторах напряжения и т.п.). Технический результат - повышение предельных значений коэффициента усиления по напряжению ДУ при низковольтном питании. Дифференциальный операционный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), объединенные эмиттеры которых через первый (3) токостабилизирующий двухполюсник соединены с шиной первого (4) источника питания (ИП), коллектор первого (1) входного Т через первый (5) двухполюсник коллекторной нагрузки (ДН) связан с шиной второго (6) ИП, коллектор второго (2) входного Т через второй (7) ДН связан с шиной второго (6) ИП и соединен со входом буферного усилителя (8). В схему введены третий (9) и четвертый (10) входные Т, а также дополнительный Т (11), база третьего (9) входного Т соединена с базой первого (1) входного Т, эмиттер третьего (9) входного Т соединен с эмиттером первого (1) входного Т, коллектор третьего (9) входного Т соединен с базой вспомогательного Т (11) и коллектором первого (1) входного Т, база четвертого (10) входного Т соединена с базой второго (2) входного Т, эмиттер четвертого (10) входного Т соединен с эмиттером второго (2) входного Т, коллектор четвертого (10) входного Т соединен с шиной второго (6) ИП, коллектор дополнительного Т (11) соединен со входом буферного усилителя (8), а эмиттер дополнительного Т (11) подключен к шине первого (4) ИП через цепь согласования потенциалов (12). 2 з.п. ф-лы, 6 ил.

1. Дифференциальный операционный усилитель с малым напряжением питания, содержащий первый (1) и второй (2) входные транзисторы, объединенные эмиттеры которых через первый (3) токостабилизирующий двухполюсник соединены с шиной первого (4) источника питания, коллектор первого (1) входного транзистора через первый (5) двухполюсник коллекторной нагрузки связан с шиной второго (6) источника питания, коллектор второго (2) входного транзистора через второй (7) двухполюсник коллекторной нагрузки связан с шиной второго (6) источника питания и соединен со входом буферного усилителя (8), отличающийся тем, что в схему введены третий (9) и четвертый (10) входные транзисторы, а также дополнительный транзистор (11), база третьего (9) входного транзистора соединена с базой первого (1) входного транзистора, эмиттер третьего (9) входного транзистора соединен с эмиттером первого (1) входного транзистора, коллектор третьего (9) входного транзистора соединен с базой вспомогательного транзистора (11) и коллектором первого (1) входного транзистора, база четвертого (10) входного транзистора соединена с базой второго (2) входного транзистора, эмиттер четвертого (10) входного транзистора соединен с эмиттером второго (2) входного транзистора, коллектор четвертого (10) входного транзистора соединен с шиной второго (6) источника питания, коллектор дополнительного транзистора (11) соединен со входом буферного усилителя (8), а эмиттер дополнительного транзистора (11) подключен к шине первого (4) источника питания через цепь согласования потенциалов (12).

2. Дифференциальный операционный усилитель по п.1, отличающийся тем, что цепь согласования потенциалов (12) содержит N>1 последовательно выключенных прямосмещенных р-n переходов.

3. Дифференциальный операционный усилитель по п.1, отличающийся тем, что цепь согласования потенциалов (12) содержит вспомогательный токостабилизирующий двухполюсник (17), вспомогательный транзистор (18) и дополнительный источник напряжения смещения (19), связанный с базой вспомогательного транзистора (18), причем эмиттер вспомогательного транзистора (18) соединен со вспомогательным токостабилизирующим двухполюсником (17), а его коллектор связан с шиной второго (6) источника питания.

| US 6285245 В1, 04.09.2001 | |||

| Дифференциальный усилитель | 1981 |

|

SU1083341A2 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 5886577 А, 23.03.1999. | |||

Авторы

Даты

2011-10-27—Публикация

2010-10-15—Подача