му входу токоразностного каскада, выход токоразностного каскада через восьмой резистор соединен с эмиттером третьего дополнительного транзистора, база которого соединена с базой первого транзистора четвертого генератора тока и непосредственно с базой четвертого дополнительного транзистора, эмиттер которого через последовательно соединенные четвертый источник напряжения смещения и девятый резистор, точка соединения которых является выходом дифференциального усилителя, псудключен к соответствующей шине источника питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| Операционный усилитель | 1983 |

|

SU1160530A1 |

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2092969C1 |

| Усилитель | 1988 |

|

SU1656669A1 |

| Регулятор напряжения для генератора переменного тока | 1980 |

|

SU1005261A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

| Усилитель | 1980 |

|

SU987795A1 |

| Дифференциальный усилитель | 1987 |

|

SU1501256A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ по авт.св. № 764100, кл. отличающийся тем, что, с целью уменьшения напряжения смещения нуля, четвертый генератор тока выполнен на первом, втором, третьем, четвертом, пятом транзисторах, имеющих один тип проводимости, и на шестом, седьмом, восьмом транзисторах; имеющих другой тип проводимости, на первом, втором, третьем, четвертом и пятом резисторах и первом источнике напряжения смещения, при этом эмиттер первого транзистора подключен к коллектору третьего транзистора и через первый резистор - к объединенным базам второго и третьего и коллектору четвертого транзистора, база первого транзистора подключена к коллектору второго транзистора и через второй резистор - к соответствующей шине источника питания, коллектор первого транзистора подключен к объединенным коллектору восьмого и базе шестого транзисторов, объединенные соответственно база и эмиттер которых являются первым выходом четвертого генератора тока, причем эмиттер восьмого транзистора соединен с соответствующей шиной источника питания, а коллектор шестого транзистора - с общей шиной, база четвертого транзистора подключена к эмиттерам второго транзистора и транзисторов выходного каскада и через первый источник напряжения смещения - к общей шине, эмиттер четвертого транзистора через третий резистор подключен к эмиттеру третьего транзистора, а через четвертый резистор - к эмиттеру седьмого и коллектору пятого транзисторов, объединенные соответственно коллектор, и база которых являются вторым выходом четвертого генератора тока, при этом база седьмого транзистора соединена с общей шиной, а эмиттер пятого транзистора через пятый резисторс соответствующей шиной источника питания, а также введены первый,второй,тре(/) а также введены первый, второй, треС тий и четвертый дополнительные транзисторы, включенные по схеме с общим коллектором, токоразностный каскад, второй, третий и четвертый источники напряжения смещения, прямосмещенный диод, шестой, седьмой, восьмой и 00 00 девятый резисторы, при этом базы первого и второго дополнительных транзисторов подключены соответственее но к коллекторам транзисторов выход4 ного каскада, эмиттер первого дополнительного транзистора соединен через второй источник напряжения смещения с инвертирующим входом токоразностно го каскада и через шестой резистор с общей шиной, эмиттер второго дополнительного транзистора через последовательно соединенные третий источник напряжения смещения прямосмещенный диод и седьмой резистор соединен с общей шиной, причем точка соединения прямосмещенного диода и седьмого резистора подключена к неинвертирующе

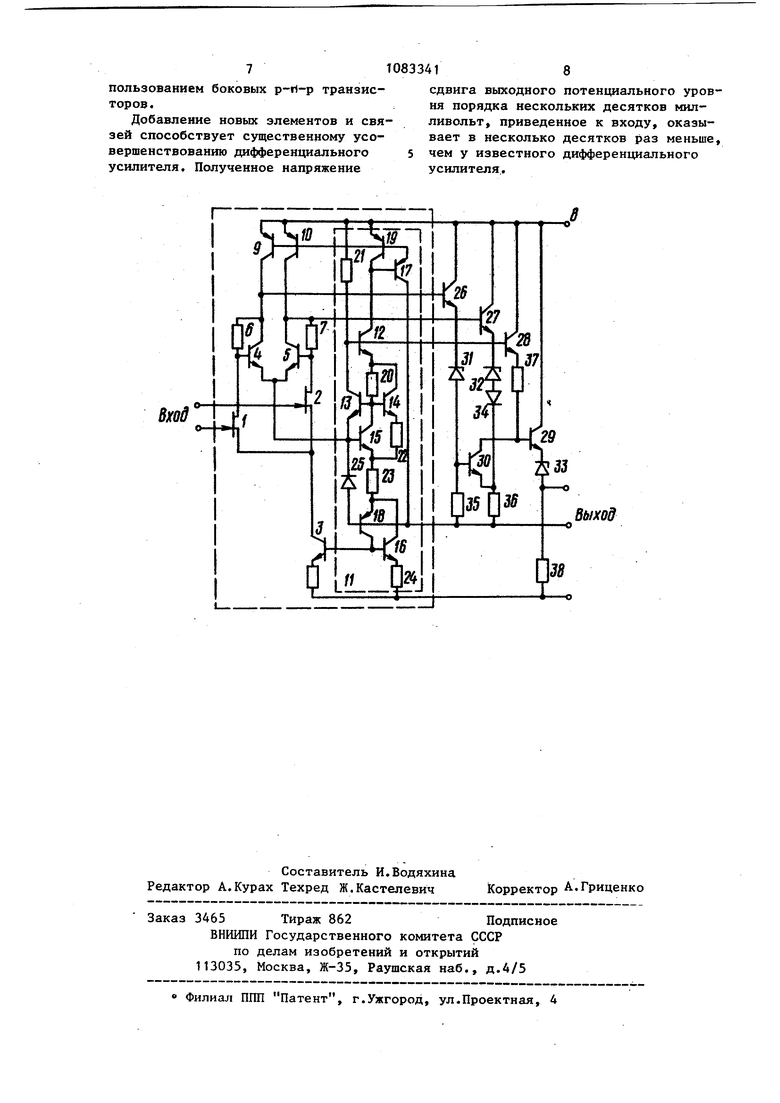

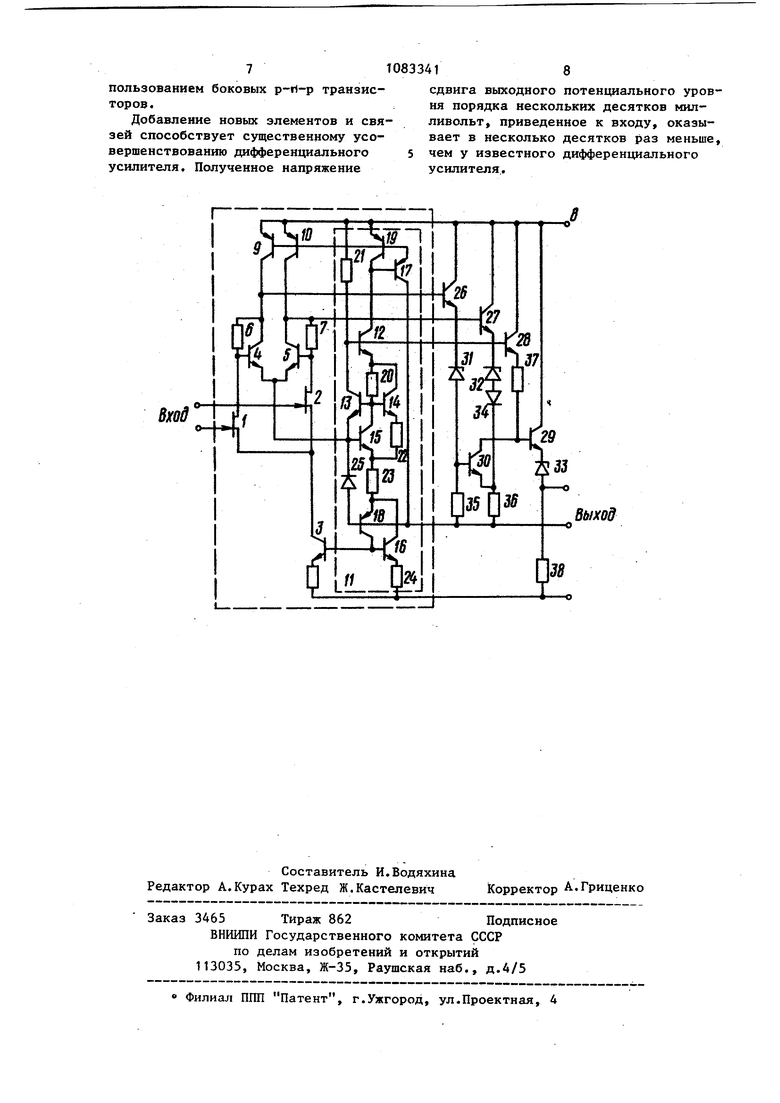

Изобретение относится к усилительной технике и может использоваться в качестве микросхемы широкополосных усилителей. По основному авт.св. № 764100 известен дифференциальный усилитель, содержащий источник питания, входной дифференциальный каскад на транзисторах с первым генератором тока на транзисторе в общей змиттерной цепи и выходные каскады на транзисторах, включенных по схеме с общим эмиттером причем коллектор транзистора каждого плеча входного дифференциального кас1сада соединен непосредственно с баЗОЙ, а через резистор - с коллектором транзистора соответствующего выходного каскада, между соответствующей шиной источника питания и коллек тором транзистора каждого выходного каскада включены соответственно второй и третий генераторы тока на транзисторах, базы которых объединены и через четвертый генератор тока соединены с базой транзистора первого генератора тока 1 Недостатком известного устройства является большое напряжение смещения обусловленное большим сдвигом выходного потенциального уровня. Цель изобретения - уменьшение напряжения смещения нуля. Поставленная цель достигается тем что в дифференциальном усилителе, со держащем источник питания, входной дифференциальный каскад на транзисторах с первым генератором тока на тра зисторе в общей эмиттерной цепи и вы ходные каскады на транзисторах, вклю ченных по схеме с общим эмиттером, причем коллектор транзистора каждого плеча входного дифференциального каскада соединен непосредственно с базой, а через резистор - с коллектором транзистора соответствующего выходного каскада, между соответствующей шиной источника питания и коллектором транзистора каждого вьгходного каскада включены соответственно второй и третий генераторы тока на транзисторах, базы которых объединены и через четвертый генератор тока соединены с базой транзистора первого генератора тока, четвертый генератор тока выполнен на первом, втором, третьем, четвертом и пятом транзисторах, имеющих один тип проводимости, и на шестом, седьмом, восьмом транзисторах, имеющих другой тип проводимости, на первом, втором, третьем, четвертом и пятом резисторах и первом источнике напряжения смещения, при этом эмиттер первого транзистора подключен к коллектору третьего транзистора и через первый резистор - к объединенным базам второго и третьего и коллектору четвертого транзисторов, база первого транзистора подключена к коллектору второго транзистора и через второй резистор - к соответствующей шине источника питания, коллектор первого транзистора подключен к объединенньм коллектору восьмого и базе шестого транзисторов, объединенные соответственно база и эмиттер которых являются nepBtiiM выходом четвертого генератора тока, причем эмиттер восьмого транзистора соединен с соответствующей щиной источника питания, а коллектор шестого транзистора - с общей шиной, база четвертого транзистора подключена к эмиттерам второго транзистора и транзисторов выходного каскада и через первый источник напряжения смещения - к общей шине, эмиттер четвергого транзистора через третий резистор подключен к эмиттеру третьего транзистора, а через четвертый резистор - к эмиттеру седьмого и коллектору пятого транзисторов, объединенные соответственно коллектор и база которьгх являются вторым выходом четвертого генератора тока, при этом база седьмого транзистора соединена с общей шиной, а эмиттер пятого транзистора через пятый резистор - с соответствующей шиной источника питания, а также введены первый, второй, третий и четвертый дополнительные транзисторы, включенные по схеме с общим коллектором, токоразностный каскад, второй, третий и четвертый источники напряжения смещения, прямосмещенный диод, шестой, седьмой, восьмой и девя тый резисторы, при этом базы первого и второго дополнительных, транзисторов подключены соответственна к коллекторам транзисторов выходного каскада эмиттер первого дополнительного транзистора соединен через второй источник напряжения смещения с инвертирующим входом токоразностного каскада и через шестой резистор - с общей шиной эмиттер второго дополнительного транзистора через последовательно соеди ненные третий источник напряжения см щения, прямосмещенный диод и седьмой резистор соединен с общей шиной, при чем точка соединения прямосмещенного диода и седьмого резистора подключена к неинвертирующему входу токоразностного каскада, выход токоразност- ного каскада через восьмой резистор соединен с эмиттером третьего дополнительного транзистора, база которог соединена с базой первого транзистор четвертого генератора тока и непосредствен 1О - с базой четвертого допол нительного транзистора, эмиттер которого через последовательно соединенные четвертый источник напряжения смещения и девятый резистор, точка соединения которых является выходом дифференциального усилителя, подключен к соответствующей шине источника питания. На чертеже представлена принципиальная электрическая схема дифференциального усилителя. Дифференциальный усилитель содержит входной дифференциальный каскад на транзисторах 1 и 2 с первым генератором 3 тока в общей эмиттерной це пи, выходные каскады на транзисторах 4и 5, включенных по схеме с общим эмиттером, причем коллекторы транзи.сторов 1 и 2 соединены с базами транзисторов 4 и 5, а через резисторы 6 и 7 - с коллекторами транзисторов 4 и 5соответственно, шину 8 источника питания, второй и третий генераторы тока на транзисторах У и 10, которые включены между коллекторами транзисторов 4 и 5 и шиной 8 источника питания соответственно, четвертый генератор 11 тока, включенный между объединенными базами транзисторов 9 и 10 и базой транзистора первого генератора 3 тока, при этом четвертый генератор 11 тока выполнен на первом, втором, третьем, четвертом, пятом транзисторах 12-16, имеющих один тип проводимости, и на шестом, седьмом, восьмом транзисторах 17-19, имеющих другой тип проводимости, на первом, втором, третьем, четвертом и пятом резисторах 20-24 и первом источнике 25 напряжения смещения, а также первый, второй, третий, четвертый дополнительные транзисторы 26-29, включенные по схеме с. общим коллектором, токоразностньш каскад 30, второй, третий, четвертый источники 31-33 напряжения смещения, прямосмещенный диод 34, шестой, седьмой, восьмой девятый резисторы 35-38. Дифференциальный усилитель работает следующим образом. При подаче входного сигнала один из транзисторов 1,2 входного дифференциального каскада закрывается, а другой открывается. На коллекторах транзисторов 4,5 выходных каскадов формируются потенциалы, величина которых фиксирована относительно потенциала нулевой шины. Для выполнения условия работоспособности дифференциального усилителя необходимо во всем рабочем диапазоне обеспечить величину токов генераторов токов на транзисторах 9 и 10, , соединенных с коллекторами транзисторов 4 и 5, несколько большей величины, чем ток генератора 3 тока, что достигается посредством связи через четвертый генератор 11 тока. Таким образом, разности коллекторных токов транзисторов 1 и 9, 2 и 10, которые определяют минимальный ток коллекторов соответствующих транзисторов 4 и 5 выходных каскадов, остаются неизменными во всем рабочем диапазоне дифференциального усилителя, что, в свою

очередь, позволяет минимизировать потребляемую им мощности.

Поскольку генератор 11 тока вьфабатывает ток -Z). , который однозначно определяет ток генераторов тока на транзисторах 9, 10 и генератора 3 тока, то предположим, что Iz. 1-,где, I(j, соответственн генераторов тока на транзисторах 9, 10 и генератора 3 тока.

Тогда токи транзисторов 4 и 5 выходных каскадов равны

При подаче на вход дифференциального усилителя нулевого входного сигнала потенциалы коллекторов транзисторов 4 и 5 выходных каскадав ( U,4 и,.с) соответственно равны

...Л.,

где Од - падение напряжения на соответствующем резисторе.

Для того, чтобы .x 0 необходимо

Запишем выражение (3) в том виде

UK4--f- 634 A25 Считая, что напряжения на все эмиттерных переходах транзисторов и прямосмещенном диоде 34 равны между .собой, а также равны между собой и напряжения первого, второго, третье го, четвертого источников 25-33 напряжения смещения, с учетом выражения (1) можно сделать вывод, JITO -и 2Ь - - - о - ТОКИ соответственно первого и второго д полнительных транзи торов 26 и 27. Упомянутые равенства легко обесп чить соответствующим выбором площадей переходов в микросхеме предлага мого дифференциального усилителя пр заданных -токах. Определим ток, протекающий через токоразностный каскад 30 2б 6ЭЗО(2-Г )R3 , откуда /R3g f Usb / RBb Сдвиг вьпсодного потенциального уровня определяется потенциалом баз третьего дополнительного транзистор 28 8Ь,,и,,-и,,-и„,

(4) R3b

pssVRse / Как следует из выражения (4), при выполнении следующих условий p,o L BiL-f., (SI R20 R37 2 R35 VR36 / R22 R36 выходной потенциал при нулевом входном сигнале будет также нулевым,т.е. Условие (5) легко вьщерживать во всем рабочем диапазоне. При изготовлении дифференциального усилителя в виде монолитной микросхемы следует также ожидать хорошей повторяемости результатов, так как отношение сопротивлений резисторов поддерживается с большой точностью (0,5-2%). Кроме обеспечения нуля на выходе дополнительно введенный токоразностный каскад 30 способствует увеличению общего коэффициента усиления по напряжению, что ведет к еще большему уменьшению напряжения смещения. В дифференциальном усилителе четвертый генератор 11 тока выполнен таким образом, чтобы при В (ко уффициент передачи тока базы транзисторов) р-п-р транзисторов даже порядка не кольких единиц зависимость 0 . --f (.-,) была однозначной, при ..; 1этом предполагалось, что В Условие независимости выходного уровня от 0 транзисторов вплоть до Bpt,pO;1 особенно важно при изготовлении дифференциального усилителя в виде монолитной Ю1кросхемы с ис7пользованием боковых p-ri-p транзисторов. Добавление новых элементов и свя зей способствует существенному усовершенствованию дифференциального усилителя. Полученное напряжение Т083341 сдвига выходного потенциального уровня порядка нескольких десятков милливольт, приведенное к входу, оказывает в несколько десятков раз меньше, 5 чем у известного дифференциального усилителя..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дифференциальный усилитель | 1977 |

|

SU764100A1 |

Авторы

Даты

1984-03-30—Публикация

1981-12-15—Подача