Область, к которой относится изобретение

[0001] Настоящее изобретение относится к устройствам восприятия изображения, устройствам отображения излучения и системам восприятия изображения, которые являются подходящими для медицинского осмотра или промышленного неразрушающего контроля и, более конкретно, к устройству восприятия изображения, устройству отображения излучения и системе восприятия изображения, способной считывать сигнал, выведенный из планарного детектора в качестве цифровых данных, используя схему считывания с низким шумом.

Уровень техники

[0002] В настоящее время устройства отображения излучения, использующие планарный детектор (в дальнейшем именуемый как Детектор с Плоским Экраном (FPD)), изготовленные из полупроводникового материала, на практике являются устройствами восприятия изображения, используемыми для медицинского осмотра изображения или неразрушающего контроля, используя рентгеновские лучи. Устройства отображения излучения, использующие FPD, могут выполнять цифровое фотографирование посредством преобразования излучения, такого как рентгеновские лучи, которые прошли через объект испытаний, такой как пациент, в аналоговый электрический сигнал с помощью FPD, и посредством преобразования этого аналогового электрического сигнала в цифровой сигнал изображения. Детекторы FPD могут использоваться как цифровые устройства восприятия изображения для фиксации неподвижного изображения (фиксация обычного изображения) и фиксации движущегося изображения (флюороскопия).

[0003] Патент США № 6538591 и выложенный патент Японии №2000-188724 раскрывают схемы вывода сигнала (схемы считывания), используемые в устройствах восприятия изображения, как описано выше. Патент США № 6538591 раскрывает устройство передачи сигнала для последовательного считывания параллельных сигналов от множества усилителей вычисления в качестве последовательного сигнала, используя переключатель считывания и преобразование последовательного сигнала, переданного с помощью усилителя буфера вывода, в цифровые данные с помощью блока схемы аналого-цифрового (A/D) преобразования (ADC). Патент Японии № 2000-188724 раскрывает схему, полученную посредством расположения усилителя с программируемым усилением (PGA) в каскаде этапе до усилителя буфера вывода в устройстве передачи сигнала, раскрытом в патенте США №6538591. Устройство передачи сигнала, раскрытое в патенте США №6538591, и схема, раскрытая в патенте Японии №2000-188724, имеют превосходное свойство отношения сигнала к шуму (S/N) и высокую скорость считывания, и являются подходящими для численного увеличения пикселей.

[0004] Схемы вывода сигнала, раскрытые в патенте США № 6538591 и патенте Японии № 2000-188724, требуются для достижения дополнительного уменьшения размера элемента сигнала и более высокой степени интеграции. Соответственно, необходимо дополнительное уменьшение размера элементов, используемых в схемах вывода сигнала. Однако когда маленькие элементы используются в схеме вывода сигнала, имеет место шум 1/f (мерцание). Шум 1/f может быть уменьшен посредством увеличения размера элемента. Однако справедливо и обратное. Таким образом, когда используются маленькие элементы, шум 1/f не может быть уменьшен. В таком случае шум 1/f, вызванный усилителем буфера вывода, блоком PGA или ADC, которые расположены в каскадах, следующих за коммутатором считывания, генерирует низкочастотное искажение изображения. В частности, поскольку устройства отображения излучения требуют широкого динамического диапазона, необходимо использовать схему считывания с низким уровнем шума в этих устройствах отображения излучения.

Сущность изобретения

[0005] Настоящее изобретение обеспечивает устройство восприятия изображения и систему восприятия изображения, способную уменьшать искажение (артефакт), вызванное шумом 1/f, на захваченном изображении, даже если маленькие элементы используются в схемах вывода сигнала.

[0006] Устройство восприятия изображения согласно варианту осуществления настоящего изобретения включает в себя: блок обнаружения, имеющий матрицу пикселей для преобразования излучения или света в аналоговые электрические сигналы; схему считывания, сконфигурированную для выполнения операции обработки сигнала, чтобы считывать аналоговые электрические сигналы, выведенные из матрицы пикселей на основании "строка за строкой"; аналого-цифровой преобразователь (A/D), сконфигурированный для преобразования пиксельных сигналов, переданных от схемы считывания, в пиксельные данные, которые являются цифровыми данными; блок обработки коррекции, сконфигурированный для выполнения обработки коррекции в отношении пиксельных данных; и блок управления, сконфигурированный для управления схемой считывания, A/D преобразователем и блоком обработки коррекции. Схема считывания включает в себя блок сброса, сконфигурированный для выведения сигнала сброса на A/D преобразователь. Блок управления управляет схемой считывания, A/D преобразователем и блоком обработки коррекции таким образом, что схема считывания выводит множество сигналов сброса на A/D преобразователь в период, в течение которого выполняется операция обработки сигнала заранее определенной строки, A/D преобразователь преобразует множество сигналов сброса во множество частей данных сброса, которые являются частями цифровых данных, в этот период, и блок обработки коррекции усредняет множество частей данных сброса, выведенных от преобразователя A/D, и выполняет обработку вычитания с усредненными данными сброса и пиксельными данными, выведенными от A/D преобразователя.

[0007] Система восприятия изображения согласно варианту осуществления настоящего изобретения включает в себя: устройство восприятия изображения; и блок отображения, способный отображать изображение с данными изображения, захваченными устройством восприятия изображения.

[0008] Способ управления устройством восприятия изображения, включающим в себя блок обнаружения, в котором матрица пикселей преобразовывает излучение или свет в аналоговые электрические сигналы, схему считывания, сконфигурированную для выполнения операции обработки сигнала, чтобы считывать аналоговые электрические сигналы, выведенные из матрицы пикселей на основании "строка-за-строкой", A/D преобразователь, сконфигурированный для преобразования пиксельного сигнала, переданного от схемы считывания, в пиксельные данные, которые являются цифровыми данными, и блок обработки коррекции, сконфигурированный для выполнения обработки коррекции в отношении пиксельных данных, включает в себя этапы: управление схемой считывания, чтобы выводить множество сигналов сброса, выведенных от блока сброса, включенного в схему считывания, и чтобы выводить пиксельный сигнал на A/D преобразователь в период, в течение которого выполняется операция обработки сигнала заранее определенной строки; управление A/D преобразователем, чтобы преобразовывать пиксельный сигнал, выведенный от схемы считывания, в пиксельные данные, которые являются цифровыми данными, и чтобы преобразовывать множество сигналов сброса, выведенных из схемы считывания, во множество частей данных сброса, которые являются частями цифровых данных, в этот период; и управление блоком обработки коррекции, чтобы усреднять множество частей данных сброса, выведенных от A/D преобразователя, в этот период, и чтобы выполнять обработку вычитания с пиксельными данными, выведенными от A/D преобразователя, и с усредненными данными сброса.

[0009] Согласно варианту осуществления настоящего изобретения возможно обеспечить устройство восприятия изображения и систему восприятия изображения, способную уменьшать искажение, вызванное шумом 1/f, на захваченном изображении, даже если используются маленькие элементы.

[0010] Дополнительные признаки настоящего изобретения станут очевидными для специалиста в данной области техники из нижеследующего описания примерных вариантов осуществления со ссылками на прилагаемые чертежи.

Краткое описание чертежей

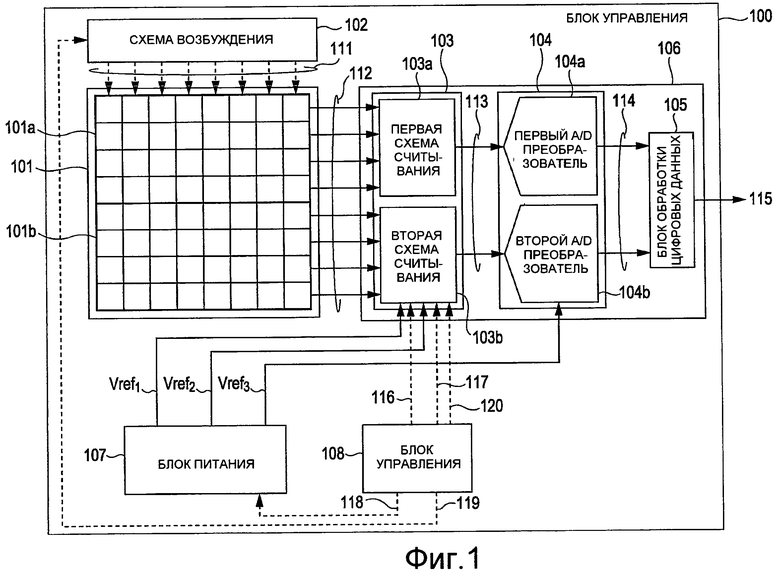

[0011] Фиг.1 является схематической блок-схемой устройства восприятия изображения, согласно первому варианту осуществления настоящего изобретения.

[0012] Фиг.2A и 2B являются схематическими диаграммами эквивалентных схем устройства восприятия изображения, согласно первому варианту осуществления настоящего изобретения.

[0013] Фиг.3 является временной диаграммой, описывающей операцию восприятия изображения, выполняемую устройством восприятия изображения, согласно первому варианту осуществления настоящего изобретения.

[0014] Фиг.4A является блок-схемой, иллюстрирующей блок обработки коррекции, включенный в устройство восприятия изображения, согласно первому варианту осуществления настоящего изобретения.

[0015] Фиг.4B является временной диаграммой, описывающей обработку коррекции, выполняемую устройством восприятия изображения, согласно первому варианту осуществления настоящего изобретения.

[0016] Фиг.5A и 5B являются примерными изображениями, которые иллюстрируют результат варианта осуществления настоящего изобретения.

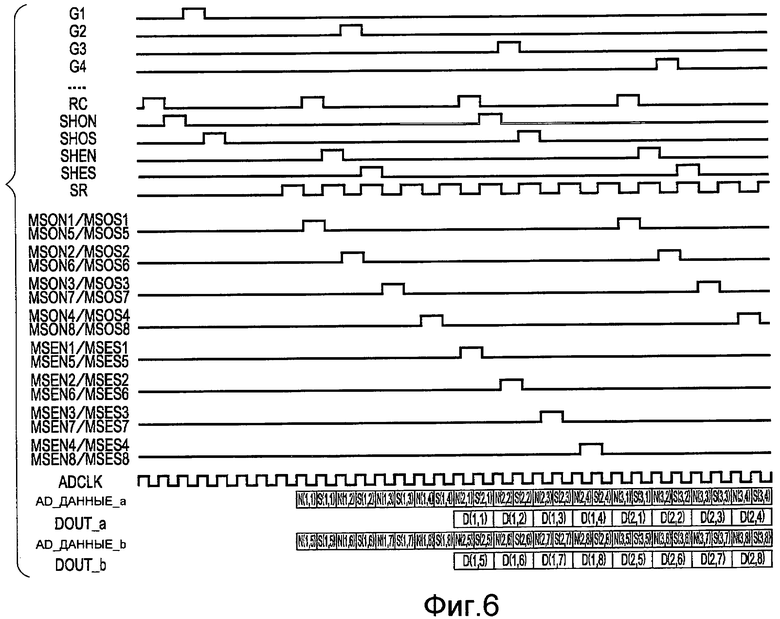

[0017] Фиг.6 является временной диаграммой, описывающей операцию восприятия изображения, выполняемую устройством восприятия изображения, согласно второму варианту осуществления настоящего изобретения.

[0018] Фиг.7 является блок-схемой, иллюстрирующей блок обработки коррекции, включенный в устройство восприятия изображения, согласно второму варианту осуществления настоящего изобретения.

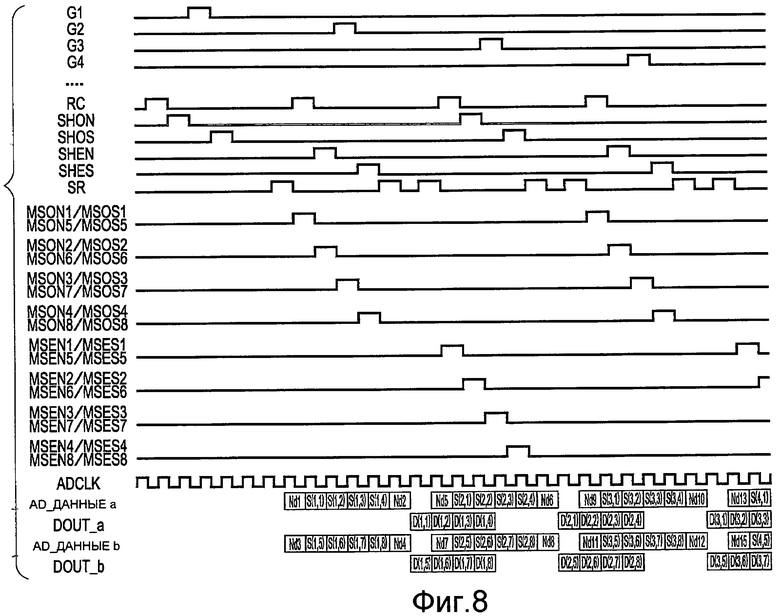

[0019] Фиг.8 является временной диаграммой, описывающей операцию восприятия изображения, выполняемую устройством восприятия изображения, согласно третьему варианту осуществления настоящего изобретения.

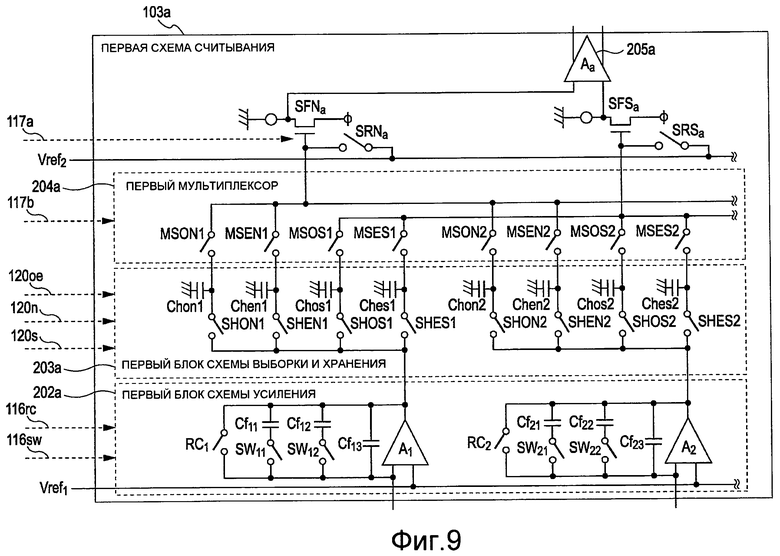

[0020] Фиг.9 является диаграммой эквивалентной схемы для схемы считывания, включенной в устройство восприятия изображения, согласно четвертому варианту осуществления настоящего изобретения.

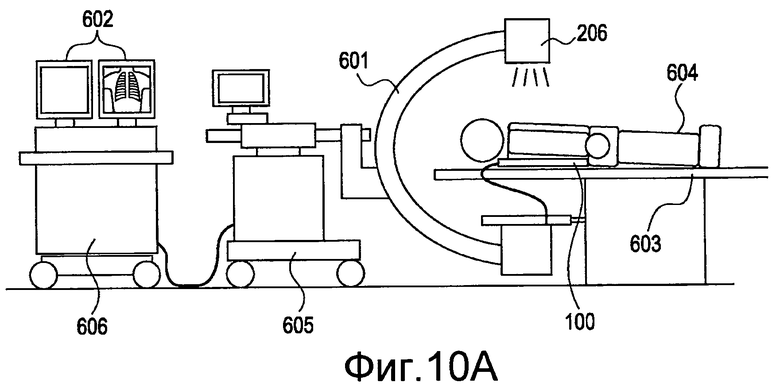

[0021] Фиг.10A и 10B являются схематическими диаграммами, описывающими систему отображения излучения, использующую устройство восприятия изображения, согласно варианту осуществления настоящего изобретения.

Описание вариантов осуществления

[0022] Варианты осуществления настоящего изобретения описаны подробно ниже со ссылками на сопроводительные чертежи.

Первый вариант осуществления

[0023] Фиг.1 является схематической блок-схемой устройства восприятия изображения, согласно первому варианту осуществления настоящего изобретения. Ссылаясь на фиг.1, устройство 100 восприятия (воспроизведения) изображения включает в себя блок 101 обнаружения, в котором множество пикселей, чтобы преобразовать излучение или свет в аналоговый электрический сигнал, компонуется в матрицу, и схему 102 возбуждения для управления блоком 101 обнаружения, чтобы вынуждать блок 101 обнаружения выводить аналоговый электрический сигнал. В первом варианте осуществления для простоты объяснения блок 101 обнаружения включает в себя пиксели в матрице из восьми рядов x восьми столбцов, и разделяется на первую группу 101а пикселей, включающую в себя четыре столбца пикселей, и вторую группу 101b пикселей, включающую в себя четыре столбца пикселей. Пиксельный сигнал, который является аналоговым электрическим сигналом, выведенным от пикселя, включенным в первую группу 101a пикселей, считывается первой схемой 103a считывания. Пиксельный сигнал 113, выведенный из первой схемы 103a считывания, преобразуется в цифровые данные 114 посредством первого A/D преобразователя 104a. Аналоговый электрический сигнал, выведенный от второй группы 101b пикселей, считывается второй схемой 103b считывания и затем преобразуется в цифровые данные посредством второго A/D преобразователя 104b. Части цифровых данных, выведенных от первого A/D преобразователя 104a и второго A/D преобразователя 104b, подвергаются обработке сигнала (описана ниже), цифровой мультиплексированной обработке, коррекции смещения и т.д. в блоке 105 обработки цифровых данных, и затем выводятся в качестве цифрового сигнала изображения. Секция 106 обработки сигнала включает в себя блок 103 схемы считывания, включающий в себя первую схему 103a считывания и вторую схему 103b считывания, блок 104 A/D преобразования, включающий в себя первый A/D преобразователь 104a и второй A/D преобразователь 104b, и блок 105 обработки цифровых данных. Устройство 100 восприятия изображения дополнительно включает в себя блок 107 питания, чтобы подавать соответствующее смещение к секции 106 обработки сигнала. Блок 107 питания подает опорное напряжение Vref1, Vref2 или Vref3 к блоку 103 схемы считывания и блоку 104 A/D преобразования. Устройство 100 восприятия изображения дополнительно включает в себя блок 108 управления для управления по меньшей мере одним из: секцией 106 обработки сигнала и блоком 107 питания. Блок 108 управления подает сигнал 118 управления к блоку 107 питания, подает сигналы 116, 117 и 120 управления к блоку 103 схемы считывания и подает сигнал 119 управления возбуждением к схеме 102 возбуждения. В ответ на сигнал 119 управления возбуждением схема 102 возбуждения подает сигнал 111 возбуждения к блоку 101 обнаружения.

[0024] Фиг.2A является схематической диаграммой эквивалентной схемы устройства восприятия изображения, согласно первому варианту осуществления настоящего изобретения. На фиг.2A используются те же самые ссылочные позиции, чтобы идентифицировать части, которые уже описаны со ссылками на Фиг.1, и поэтому их описание будет опущено. Блок 101 обнаружения включает в себя пиксели 201, скомпонованные в матрицу. Ссылаясь на фиг.2A, количество пикселей 201 в матрице является 8 x 8 пикселей, которые компонуются в восьми строках и восьми столбцах. Каждый из пикселей 201 включает в себя элемент S преобразования, чтобы преобразовывать излучение или свет в электрический заряд, и элемент переключения T, чтобы выводить электрический сигнал, соответствующий электрическому заряду. В качестве элемента преобразования S для преобразования света в электрический заряд предпочтительно используется фотоэлектрический элемент преобразования, например, фотодиод PIN, который главным образом изготовлен из аморфного кремния и расположен на электроизоляционной подложке, такой как стеклянная подложка. В качестве элемента преобразования S для преобразования излучения в электрический заряд предпочтительно используется элемент косвенного преобразования, полученный посредством обеспечения преобразователя длины волны для преобразования излучения в свет обнаруживаемого диапазона спектра на входной стороне излучения вышеописанного фотоэлектрического элемента преобразования или элемента прямого преобразования, чтобы непосредственно преобразовывать излучение в электрический заряд. В качестве элемента переключения T предпочтительно используется транзистор, имеющий вывод управления и два главных вывода. Когда фотоэлектрический элемент преобразования расположен на электроизоляционной подложке в пикселе, тонкопленочный транзистор (TFT) используется как элемент переключения T. Один электрод элемента преобразования S электрически связан с одним из двух главных выводов элемента переключения T, и другой электрод элемента преобразования S электрически связан с блоком 107 подачи смещения через общую линию. Элементы переключения T, включенные во множество пикселей в направлении строки, например элементы переключения Т11-Т18, по отдельности имеют выводы управления, электрически связанные с линией G1 возбуждения в первой строке. Сигнал возбуждения для управления проводящим состоянием элемента переключения подается от схемы 102 возбуждения к элементу переключения T с помощью линии возбуждения на основании "строка-за-строкой". Элементы переключения T, включенные во множество пикселей в направлении столбца, например элементы переключения Т11-Т81, по отдельности имеют другие главные выводы, электрически связанные с сигнальной линией Sig1 в первом столбце. Когда элемент переключения T находится в проводящем состоянии, элемент переключения T выводит электрический сигнал, соответствующий электрическому заряду элемента преобразования S, на блок 103 схемы считывания по сигнальной линии. Множество сигнальных линий Sig1-Sig8, скомпонованных в направлении столбца, передает электрические сигналы, выведенные от множества пикселей в блоке 101 обнаружения, на блок 103 схемы считывания параллельно. В первом варианте осуществления блок 101 обнаружения делится на первую группу 101a пикселей и вторую группу 101b пикселей, каждая из которых имеет четыре столбца пикселей. Аналоговые электрические сигналы, выведенные от пикселей в первой группе 101a пикселей, считываются параллельно первой схемой 103a считывания в блоке 103 схемы считывания, и аналоговые электрические сигналы, выведенные от пикселей во второй группе 101b пикселей, считываются параллельно второй схемой 103b считывания в блоке 103 схемы считывания.

[0025] Первая схема 103a считывания включает в себя первый блок 202a схемы усиления для усиления электрических сигналов, которые выводятся параллельно от первой группы 101a пикселей, и первый блок 203a схемы выборки и хранения для формирования выборок и хранения электрического сигнала, переданного от первого блока 202a схемы усиления. Вторая схема 103b считывания аналогично включает в себя второй блок 202b схемы усиления и второй блок 203b схемы выборки и хранения. Первая схема 103a хранения дополнительно включает в себя первый мультиплексор 204a для последовательного приема электрических сигналов, которые выводятся параллельно из первого блока схемы 203a выборки и хранения, и для выведения последовательного сигнала в качестве сигнала изображения, и первый усилитель 205a с переменным усилением, который является буфером вывода для выполнения преобразования полного сопротивления (импеданса) над сигналом изображения, и для выведения преобразованного сигнала. Аналогично вторая схема 103b считывания дополнительно включает в себя второй мультиплексор 204b и второй усилитель 205b с переменным усилением. Электрический сигнал, переданный от пикселя, вводится в первый усилитель 205a с переменным усилением или второй усилитель 205b с переменным усилением через буфер SFS сигнала. Компонент шума вводится в первый усилитель 205a с переменным усилением или второй усилитель 205b с переменным усилением через буфер SFN шума. Первый усилитель 205a с переменным усилением выполняет вычитание, используя электрический сигнал, переданный от пикселя, и компонент шума, и выводит результат вычитания на первый A/D преобразователь 104a. Второй усилитель 205b с переменным усилением аналогично выполняет вычитание, используя электрический сигнал, переданный от пикселя, и компонент шума, и выводит результат вычитания на второй A/D преобразователь 104b. Блок 107 питания подает опорное напряжение Vref3 на первый A/D преобразователь 104a и второй A/D преобразователь 104b. В настоящем описании опорное напряжение Vref2 вводится от блока 107 питания в логические вентили буферов SFS сигнала первой схемы 103a считывания и второй схемы 103b считывания с помощью переключателей SRS сброса в заранее определенное время. Опорное напряжение Vref2 вводится от блока 107 питания на логические вентили буферов SFN шума первой схемы 103a считывания и второй схемы 103b считывания с помощью переключателей SRN сброса в заранее определенное время. Таким образом, переключатель SR сброса подает опорное напряжение Vref2 на логический вентиль буфера SF в заранее определенное время, чтобы сбросить вход усилителя с переменным усилением.

[0026] Блок 108 управления подает сигнал 116 управления на первый блок 202a схемы усиления и второй блок 202b схемы усиления, подает сигнал 117a управления к переключателям SRS сброса и переключателям SRN сброса, подает сигнал 117b управления к первому мультиплексору 204a и второму мультиплексору 204b, подает сигналы 120s, 120n и 120 управления к первому блоку 203a схемы выборки и хранения и второму блоку 203b схемы выборки и хранения, подает сигнал 129 управления к первому A/D преобразователю 104a и второму A/D преобразователю 104b и подает сигнал 130 управления к блоку 105 обработки цифровых данных.

[0027] Фиг.2B является диаграммой эквивалентной схемы, описывающей блок 103 схемы считывания подробно. Блок 202 схемы усиления снабжается схемой усиления, соответствующей каждой сигнальной линии. Схема усиления включает в себя усилитель А вычисления для усиления электрического сигнала (пиксельного сигнала), считываемого от пикселя, и для выведения усиленного сигнала, интегральный конденсатор Cf и переключатель RC сброса, для сброса интегрального конденсатора Cf. Усилитель A вычисления принимает электрический сигнал, выведенный от инвертирующего входного терминала, и выводит усиленный электрический сигнал с выходного терминала. Опорное напряжение Vref1 вводится от блока 107 питания в неинвертирующий входной терминал усилителя A вычисления. Интегральный конденсатор Cf включен между инвертирующим входным терминалом и выходным терминалом усилителя A вычисления, и соединяется параллельно с переключателем RC сброса. Блок 203 схемы выборки и хранения снабжается схемой выборки и хранения сигнала нечетной строки, схемой выборки и хранения сигнала четной строки, схемой выборки и хранения шума нечетной строки и схемой выборки и хранения шума четной строки. Эти схемы выборки и хранения соответствуют каждой схеме усиления. Схема выборки и хранения сигнала нечетной строки включает в себя переключатель SHOS формирования выборок для формирования выборок электрического сигнала, выведенного от пикселя в строке с нечетным номером, и конденсатор Chos формирования выборок для хранения пиксельного сигнала строки с нечетным номером. Схема выборки и хранения сигнала четной строки включает в себя переключатель SHES формирования выборок для формирования выборок электрического сигнала, выведенного от пикселя в строке с четным номером и конденсатор Ches формирования выборок для хранения пиксельного сигнала строки с четным номером. Схема выборки и хранения шума нечетной строки включает в себя переключатель SHON формирования выборок для формирования выборок компонента шума усилителя вычисления до формирования выборок пиксельного сигнала строки с нечетным номером, и конденсатор Chon формирования выборок для хранения сигнала шума. Схема выборки и хранения шума четной строки включает в себя переключатель SHEN формирования выборок для формирования выборок компонента шума усилителя вычисления до формирования выборок пиксельного сигнала строки с четным номером, и конденсатор Chen формирования выборок для хранения сигнала шума. Мультиплексор 204 включает в себя переключатель MSOS для схемы выборки и хранения сигнала нечетной строки, переключатель MSES для схемы выборки и хранения сигнала четной строки, переключатель MSON для схемы выборки и хранения шума нечетной строки и переключатель MSEN для схемы выборки и хранения шума четной строки. Эти переключатели соответствуют каждой схеме усиления. Мультиплексор 204 последовательно выбирает эти переключатели, таким образом, преобразовывая параллельные сигналы пикселя или параллельные сигналы шума в последовательности сигналов.

[0028] Работа устройства восприятия изображения, согласно варианту осуществления настоящего изобретения, описана ниже со ссылками на фиг.2A, 2B и 3. Фиг.3 является временной диаграммой, описывающей операцию восприятия изображения устройства восприятия изображения, согласно первому варианту осуществления настоящего изобретения.

[0029] Сначала устройство 100 восприятия изображения выполняет операцию вывода пикселя на основании "строка-за-строкой". Когда блок 101 обнаружения подвергается излучению или свету, каждый элемент преобразования S генерирует электрический заряд, соответствующий излучению или свету. Когда блок 108 управления подает сигнал 116 управления к переключателю RC сброса, переключатель RC сброса сбрасывает интегральный конденсатор Cf и блок схемы усиления сбрасывается. Когда блок 108 управления подает сигналы 120n и 120oe управления к блоку схемы выборки и хранения, переключатель SHON формирования выборок схемы выборки и хранения шума нечетной строки включается, и компонент шума блока усиления сброса передается на конденсатор Chon формирования выборок. Когда переключатель SHON формирования выборок выключается, компонент шума сохраняется в конденсаторе Chon формирования выборок. Когда схема 102 возбуждения подает сигнал возбуждения на линию G1 возбуждения в первой строке, включаются элементы переключения T11-T18. В результате аналоговые электрические сигналы, соответствующие электрическим зарядам, генерируемым элементами преобразования S11-S14 в первой строке, передаются параллельно от пикселей к первой схеме 103a считывания через сигнальные линии Sig1-Sig4, соответственно, и аналоговые электрические сигналы, соответствующие электрическим зарядам, генерируемым элементами преобразования S15-S18 в первой строке, передаются параллельно от пикселей ко второй схеме 103b считывания через сигнальные линии Sig5-Sig8, соответственно. Когда блок 108 управления подает сигналы 120s и 120oe управления к блоку схемы выборки и хранения, переключатель SHOS формирования выборок схемы выборки и хранения сигнала нечетной строки включается, и считанный пиксельный сигнал передается конденсатору Chos формирования выборок через схему усиления. В это время компонент шума схемы усиления добавляется к пиксельному сигналу. Когда переключатель SHOS формирования выборок выключается, пиксельный сигнал, включающий в себя компонент шума, сохраняется в конденсаторе Chos формирования выборок.

[0030] Затем устройство 100 восприятия изображения выполняет следующую операцию обработки сигнала. Когда блок 108 управления подает сигнал 117a управления к переключателям SRS и SRN сброса, переключатели SRS и SRN сброса включаются, опорное напряжение Vref2 подается к логическим вентилям буферов SFS и SFN сигнала, и входы первого усилителя 205a с переменным усилением и второго усилителя 205b с переменным усилением сбрасываются. Таким образом, переключатели SRS и SRN сброса являются блоками сброса для выведения сигнала сброса на A/D преобразователь. В это время первый A/D преобразователь 104a и второй A/D преобразователь 104b преобразовывают выходные сигналы первого усилителя 205a с переменным усилением и второго усилителя 205b с переменным усилением в цифровые данные Nd1 и цифровые данные Nd4, и выводят цифровые данные Nd1 и цифровые данные Nd4 на блок 105 обработки цифровых данных, соответственно. Цифровые данные Nd1 и цифровые данные Nd4 включают в себя компоненты шума 1/f первого усилителя 205a с переменным усилением и второго усилителя 205b с переменным усилением, соответственно, и являются данными сброса первого усилителя 205a с переменным усилением и данными сброса второго усилителя 205b с переменным усилением, соответственно. Когда переключатели SRS и SRN сброса выключаются, первый A/D преобразователь 104a и второй A/D преобразователь 104b преобразовывают выходные сигналы первого усилителя 205a с переменным усилением и второго усилителя 205b с переменным усилением в цифровые данные Sd1 и цифровые данные Sd4, и выводят цифровые данные Sd1 и цифровые данные Sd4 на блок 105 обработки цифровых данных, соответственно. Эта операция называется операцией вывода данных псевдосброса.

[0031] Когда переключатели SRS и SRN сброса снова включаются, опорное напряжение Vrefa подается к логическим вентилям буферов SFS и SFN сигнала, и входы первого усилителя 205a с переменным усилением и второго усилителя 205b с переменным усилением снова сбрасываются. В это время в ответ на сигнал 129 управления, переданный от блока 108 управления, первый A/D преобразователь 104a и второй A/D преобразователь 104b преобразовывают выходные сигналы первого усилителя 205a с переменным усилением и второго усилителя 205b с переменным усилением в цифровые данные N (1, 1) и цифровые данные N (1, 5) и выводят цифровые данные N (1, 1) и цифровые данные N (1, 5) на блок 105 обработки цифровых данных, соответственно. Так же как цифровые данные Nd1 и цифровые данные Nd4, цифровые данные N (1, 1) и цифровые данные N (1, 5) включают в себя компоненты шума 1/f первого усилителя 205a с переменным усилением и второго усилителя 205b c переменным усилением, соответственно, и являются данными сброса первого усилителя 205a с переменным усилением и данными сброса второго усилителя 205b c переменным усилением, соответственно. Эта операция называется операцией вывода данных сброса.

[0032] Когда блок 108 управления подает сигнал 117b управления к каждому мультиплексору, включаются переключатель MSOS1 и переключатель MSON1 в первом мультиплексоре 204a. В результате пиксельные сигналы, включающие в себя компоненты шума, выведенные от пикселей в первом столбце, вводятся в первый усилитель 205a с переменным усилением через буфер SFS сигнала, и компоненты шума вводятся в первый усилитель 205a с переменным усилением через буфер SFN шума. Переключатели MSOS5 и MSON5 во втором мультиплексоре 204b включаются одновременно. В результате пиксельные сигналы, включающие в себя компоненты шума, выведенные от пикселей в пятом столбце, вводятся во второй усилитель 205b с переменным усилением через буфер SFS сигнала, и компоненты шума вводятся во второй усилитель 205b с переменным усилением через буфер SFN шума. Каждый усилитель с переменным усилением вычисляет разность между пиксельным сигналом, включающим в себя компонент шума, и компонентом шума, усиливает результат вычисления и выводит усиленный пиксельный сигнал. В результате компонент шума каждой схемы усиления удаляется из вывода схемы усиления. Первый A/D преобразователь 104a преобразовывает выходной пиксельный сигнал вывода в цифровые данные S (1, 1) и выводит цифровые данные S (1, 1) на блок 105 обработки цифровых данных. Второй A/D преобразователь 104b преобразовывает выходной пиксельный сигнал в цифровые данные S (1, 5) и выводит цифровые данные S (1, 5) на блок 105 обработки цифровых данных. Каждые из цифровых данных S (1, 1) и цифровых данных S (1, 5) являются данными, полученными посредством добавления компонента шума 1/f переменного усилителя к пиксельному сигналу. Эта операция называется операцией вывода пиксельных данных.

[0033] Затем операция вывода данных сброса выполняется снова. Цифровые данные N (1, 2) и цифровые данные N (1, 6) выводятся от первого A/D преобразователя 104a и второго A/D преобразователя 104b на блок 105 обработки цифровых данных, соответственно.

[0034] Операция вывода пиксельных данных выполняется над вторым столбцом и шестым столбцом. Цифровые данные S (1, 2) и цифровые данные S (1, 6) выводятся от первого A/D преобразователя 104a и второго A/D преобразователя 104b на блок 105 обработки цифровых данных, соответственно.

[0035] Операция вывода данных сброса, операция вывода пиксельных данных для третьего столбца и седьмого столбца, операция вывода данных сброса и операция вывода пиксельных данных для четвертого столбца и восьмого столбца последовательно выполняются в этом порядке. В результате цифровые данные N (1, 3), цифровые данные N (1, 7), цифровые данные S (1, 3), цифровые данные S (1, 7), цифровые данные N (1, 4), цифровые данные N (1, 8), цифровые данные S (1, 4) и цифровые данные S (1, 8) выводятся на блок 105 обработки цифровых данных.

[0036] Затем операция вывода данных псевдосброса выполняется два раза. Цифровые данные Nd2, цифровые данные Nd5, цифровые данные Sd5, цифровые данные Sd5, цифровые данные Nd3, цифровые данные Nd6, цифровые данные Sd3 и цифровые данные Sd6 выводятся на блок 105 обработки цифровых данных.

[0037] Блок 105 обработки цифровых данных выполняет обработку коррекции, которая описана ниже в соответствии с этими частями данных, выведенными от A/D преобразователей и частей скорректированных выходных пиксельных данных D (1, 1)-D (1, 4) и D (1, 5)-D (1, 8).

[0038] Таким образом, операция обработки сигнала в блоках строк включает в себя операцию вывода данных псевдосброса, операцию вывода данных сброса и операцию вывода пиксельных данных в блоках столбцов, и операцию вывода

данных псевдосброса, выполняемую два раза. Посредством операции вывода пикселя в блоках строк и операции обработки сигнала в блоках строк достигается операция считывания пикселя в блоках строк. Операция считывания пикселя в блоках строк повторяется таким образом, чтобы была достигнута операция считывания единственного изображения.

[0039] В первом варианте осуществления выполняется операция вывода пикселя второй строки, в то время как выполняется операция обработки сигнала первой строки. Как в случае первой строки, интегральный конденсатор Cf сбрасывается переключателем RC сброса таким образом, чтобы схема усиления была сброшена. Когда включается переключатель SHEN формирования выборок схемы выборки и хранения шума четной строки, компонент шума схемы усиления сброса передается на конденсатор Chen формирования выборок. Когда выключается переключатель SHEN формирования выборок, компонент шума сохраняется в конденсаторе Chen формирования выборок. Когда схема 102 возбуждения подает сигнал возбуждения на линию G 2 возбуждения во второй строке, включаются элементы переключения T21-T28 во второй строке. Аналоговые электрические сигналы, соответствующие электрическим зарядам, генерируемым элементами преобразования S21 -S24 во второй строке, по отдельности передаются параллельно от пикселей к первой схеме 103a считывания через сигнальные линии Sig1-Sig4. Аналоговые электрические сигналы, соответствующие электрическим зарядам, генерируемым элементами преобразования S25-S28 во второй строке, по отдельности передаются параллельно от пикселей ко второй схеме 103b считывания с помощью сигнальных линий Sig5-Sig8. Когда включается переключатель SHES формирования выборок схемы выборки и хранения сигнала четной строки, считываемый пиксельный сигнал передается конденсатору Ches формирования выборок через схему усиления. Затем компонент шума схемы усиления добавляется к пиксельному сигналу. Когда выключается переключатель SHES формирования выборок, пиксельный сигнал, включающий в себя компонент шума, сохраняется в конденсаторе Ches формирования выборок. В операции вывода пиксельных данных второй строки, так же как в случае операции вывода пиксельных данных первой строки, выполняется операция, аналогичная операции, выполняемой в соответствии с первой строкой, за исключением того, что переключатель MSES и переключатель MSEN в каждом мультиплексоре включается последовательно. Поскольку выполняются вышеописанная операция вывода и вышеописанная операция обработки сигнала, возможно выполнить следующую операцию вывода в блоках строк, в то время как выполняется последняя операция обработки сигнала в блоках строк. Соответственно, по сравнению со случаем, в котором выполняется следующая операция вывода в блоках строк после того, как последняя операция обработки сигнала в блоках строк была закончена, время, требуемое для операции считывания единственного изображения, может быть уменьшено.

[0040] Ниже обработка коррекции, выполняемая блоком 105 обработки цифровых данных, описана со ссылками на Фиг.4A и Фиг.4B. Фиг.4A является блок-схемой, описывающей блок 400 обработки коррекции, включенный в блок 105 обработки цифровых данных. Фиг.4B является временной диаграммой, описывающей обработку коррекции, выполняемую блоком 400 обработки коррекции. В первом варианте осуществления блок 400 обработки коррекции предоставляется для каждого A/D преобразователя. В следующем описании предполагается, что блок 400 обработки коррекции предоставляется для первого A/D преобразователя 104a. Однако блок 400 обработки коррекции может выполнять обработку коррекции в соответствии с данными, полученными посредством выполнения цифрового мультиплексирования частей данных, выведенных от первого и второго A/D преобразователей.

[0041] Блок 400 обработки коррекции включает в себя блок 401 обработки данных сброса, блок 402 обработки пиксельных данных и сумматор 403. Блок 401 обработки данных сброса включает в себя множество элементов 411-414 задержки, сумматор 415 и множитель 416. Блок 402 обработки пиксельных данных включает в себя множество элементов 421 и 422 задержки.

[0042] В ответ на сигнал 130 управления, переданный от блока 108 управления, N_CLK подается к элементам 411-414 задержки в блоке 401 обработки данных сброса, и S_CLK подается к элементам 421 и 422 задержки в блоке 402 обработки пиксельных данных. Цифровые данные Nd1, выведенные от первого A/D преобразователя 104a, вводятся в блок 400 обработки коррекции и сохраняются в элементе 411 задержки в блоке 401 обработки данных сброса, в соответствии с нарастанием (передним фронтом) сигнала N_CLK. Затем цифровые данные Sd1 вводятся в блок 400 обработки коррекции и сохраняются в элементе 421 задержки в блоке 402 обработки пиксельных данных, в соответствии с передним фронтом S_CLK. Затем цифровые данные N (1, 1) вводятся в блок 400 обработки коррекции и сохраняются в элементе 411 задержки, в соответствии с передним фронтом N_CLK, и цифровые данные Nd1 сохраняются в элементе 412 задержки. Затем цифровые данные S (1, 1) вводятся в блок 400 обработки коррекции и сохраняются в элементе 421 задержки, в соответствии с передним фронтом S_CLK. Затем цифровые данные N (1, 2) вводятся в блок 400 обработки коррекции и сохраняются в элементе 411 задержки, в соответствии с передним фронтом N_CLK, цифровые данные N (1, 1) сохраняются в элементе 412 задержки, цифровые данные Nd1 сохраняются в элементе 413 задержки. Затем цифровые данные S (1, 2) вводятся в блок 400 обработки коррекции и сохраняются в элементе 421 задержки, в соответствии с передним фронтом S_CLK, и цифровые данные S (1, 1) сохраняются в элементе 422 задержки и затем выводятся от элемента 422 задержки для сумматора 403. Затем цифровые данные N (1, 3) вводятся в блок 400 обработки коррекции и сохраняются в элементе 411 задержки, в соответствии с передним фронтом N_CLK, цифровые данные N (1, 2) сохраняются в элементе 412 задержки, цифровые данные N (1, 1) сохраняются в элементе 413 задержки и цифровые данные Nd1 сохраняются в элементе 414 задержки. Выходные сигналы элементов 411-414 задержки выводятся на сумматор 415 и затем суммируются сумматором 415. Четверть (0,25) результата суммирования вычисляется умножителем 416 для усреднения и затем выводится на сумматор 403. Сумматор 403 выполняет обработку вычитания с данными, выведенными от блока 402 обработки пиксельных данных, и данными, выведенными от блока 401обработки данных сброса, и выводит скорректированные пиксельные данные D (1, 1). Ниже приведен один возможный пример того, как скорректированные пиксельные данные могут быть вычислены. А именно, скорректированные пиксельные данные D (1, 1) вычисляются следующим образом: S (1, 1)-(Ndi+N (1, 1)+N (1, 2)+N (1, 3))/4. Скорректированные пиксельные данные D (1, 2) аналогично вычисляются следующим образом: S (1, 2)-(N (1, 1)+N (1, 2)+N (1, 3)+N (1, 4))/4. Таким образом, при обработке коррекции в период, в который выполняется операция обработки сигнала в блоках строк, блок схемы считывания подает множество сигналов сброса на A/D преобразователь. A/D преобразователь преобразовывает сигналы сброса во множество частей данных сброса. Блок обработки коррекции усредняет части данных сброса, выведенных от A/D преобразователя. Блок обработки коррекции получает скорректированные пиксельные данные посредством выполнения обработки вычитания с пиксельными данными заранее определенной строки, выведенными от A/D преобразователя в тот же период, и усредненными данными сброса. Другими словами, обработка вычитания включает в себя вычитание усредненных данных сброса из пиксельных данных заранее определенной строки, выведенных от A/D преобразователя во время заранее определенного периода. Усредненные данные сброса и пиксельные данные выводятся по существу в одно и то же время (одновременно) в течение заранее определенного периода (например, один период сигнала синхронизации), как примерно иллюстрировано на Фиг.4B заштрихованными частями данных.

[0043] В первом варианте осуществления две части данных сброса, которые располагаются близко от пиксельных данных во времени, которые должны подвергаться обработке коррекции, и получены до пиксельных данных, и две части данных сброса, которые располагаются близко от пиксельных данных во времени и получены после пиксельных данных, то есть всего четыре части данных сброса, усредняются. Однако количество частей данных сброса этим не ограничивается. При условии, что количество частей данных сброса, полученных перед целевыми пиксельными данными коррекции, является таким же, что и количество частей данных сброса, полученных после целевых пиксельных данных коррекции, любое количество частей данных сброса может использоваться. Аналогично в вышеупомянутом описании четверть (0.25) результата дополнения вычисляется умножителем 416, чтобы усреднить и затем вывести на сумматор 403. Вычисление умножителя 416 не ограничивается четвертью; другие проценты могут быть определены, например, на основании величины шума 1/f.

[0044] Результат настоящего изобретения описан ниже со ссылками на фиг.5A и фиг.5B. Фиг.5A является диаграммой, иллюстрирующей полученное изображение, когда не выполняется вышеописанная обработка коррекции. Фиг.5B является диаграммой, иллюстрирующей полученное изображение, когда выполняется вышеописанная обработка коррекции. Сравнивая фиг.5A с фиг.5B, должно быть оценено, что когда не выполняется вышеописанная обработка коррекции (фиг.5A), шум в форме горизонтальных полос становится заметным. Напротив, в полученном изображении, когда выполняется вышеописанная обработка коррекции (фиг.5B), шум в форме полос является незаметным. Причина этого эффекта заключается в том, что подавляется высокочастотный компонент шума посредством усреднения частей данных сброса, включающих в себя высокочастотный компонент шума и компонент низкочастотного шума 1/f. Таким образом, можно полагать, что усреднение этих частей данных сброса равнозначно фильтру низких частот (LPF) этих частей данных сброса. Соответственно, шум, включенный в данные сброса, полученные после усреднения, является почти низкочастотным шумом 1/f. Когда число частей данных сброса, которые должны быть усреднены, увеличивается, степень точности LPF улучшается. Посредством выполнения обработки вычитания с пиксельными данными, включающими в себя компонент низкочастотного шума 1/f, и данными сброса, полученными после усреднения, возможно эффективно удалить компонент шума 1/f из пиксельных данных. Можно полагать, что обработка вычитания равнозначна высокочастотному фильтру (HPF) пиксельных данных. Таким образом, в вышеописанной обработке коррекции оба LPF и HPF могут быть выполнены над каждым из элементов пиксельных данных, но не используя фактические аппаратные средства фильтрования для каждого элемента пикселя. Когда части данных, которые должны использоваться для обработки вычитания, располагаются близко друг от друга во времени, степень HPF увеличивается. Посредством уменьшения компонента шума 1/f, который является причиной шума в форме полос, искажение на получающемся изображении может быть по существу уменьшено. Таким образом, используя блок 400 обработки коррекции для выполнения вышеописанной обработки коррекции, даже если используются схема считывания или A/D преобразователь, имеющий маленький размер элемента, возможно уменьшить искажение, вызванное шумом 1/f, генерируемым схемой считывания или A/D преобразователем в отношении захваченного изображения.

[0045] В первом варианте осуществления выводятся пиксельные данные, используя параллельно два блока схемы считывания и два A/D преобразователя, один из которых соответствует первой группе 101а пикселей, и другой из которых соответствует второй группе 101b пикселей. В этом случае характеристика шума набора из первой схемы 103a считывания и первого A/D преобразователя 104a и характеристика шума набора из второй схемы 103b считывания и второго A/D преобразователя 104b могут отличаться друг от друга. В отношении захваченного изображения этап изображения может генерироваться первой группой 101a пикселей и второй группой 101b пикселей. Когда выполняется вышеописанная обработка коррекции, возможно эффективно уменьшить шум, вызванный каждым блоком схемы считывания и каждым A/D преобразователем. Соответственно, даже если блоки схемы считывания используются параллельно, и A/D преобразователи используются параллельно, генерация такого этапа изображения может быть подавлена.

Второй вариант осуществления

[0046] Ниже второй вариант осуществления настоящего изобретения описан со ссылками на фиг.6 и фиг.7. Устройство, используемое во втором варианте осуществления, является тем же самым, что и устройство, которое используется в первом варианте осуществления, за исключением блока обработки коррекции. Операция, выполняемая во втором варианте осуществления, отличается от операции, выполняемой в первом варианте осуществления. Подробное описание конфигурации и операции, которые были уже описаны в первом варианте осуществления, будет опущено.

[0047] Фиг.6 является временной диаграммой, описывающей операцию восприятия изображения, согласно второму варианту осуществления. Фиг.7 является блок-схемой, описывающей блок 700 обработки коррекции, согласно второму варианту осуществления. В операции по обработке сигнала, согласно второму варианту осуществления, не выполняется операция вывода данных псевдосброса. Соответственно, период времени, требуемый для операции обработки сигнала и операции считывания во втором варианте осуществления, является более коротким, чем этот период времени в первом варианте осуществления. При обработке коррекции согласно второму варианту осуществления выполняется усреднение, используя все части данных сброса, полученных посредством операции обработки сигнала в блоках строк. Блок 700 обработки коррекции включает в себя блок 701 обработки данных сброса, блок 702 обработки пиксельных данных и сумматор 703. Блок 701 обработки данных сброса включает в себя сумматор 711, элемент 712 задержки и умножитель 713. N_CLK, иллюстрированный на фиг.4B, подается к элементу 712 задержки. Например, блок 702 обработки пиксельных данных состоит из регистра "первым пришел - первым обслужен" (FIFO). S_CLK, иллюстрированный на фиг.4B, подается к блоку 702 обработки пиксельных данных.

[0048] Цифровые данные N (1, 1), выведенные от первого A/D преобразователя 104a, вводятся в блок 700 обработки коррекции и сохраняются в элементе 712 задержки в блоке 701 обработки данных сброса, в соответствии с передним фронтом N_CLK. Затем цифровые данные S (1, 1) вводятся в блок 700 обработки коррекции и сохраняются в FIFO в блоке 702 обработки пиксельных данных, в соответствии с передним фронтом S_CLK. Затем цифровые данные N (1, 2) вводятся в блок 700 обработки коррекции. Сумматор 711 суммирует цифровые данные N (1, 2) и цифровые данные N (1, 1) и сохраняет результат суммирования в элементе 712 задержки в соответствии с передним фронтом N_CLK. Затем цифровые данные S (1, 2) вводятся в блок 700 обработки коррекции и сохраняются в FIFO, в соответствии с передним фронтом S_CLK. Затем цифровые данные N (1, 3) вводятся в блок 700 обработки коррекции. Сумматор 711 суммирует цифровые данные N (1, 3), цифровые данные N (1, 1) и цифровые данные N (1, 2) и сохраняет результат дополнения в элементе 712 задержки, в соответствии с передним фронтом N_CLK. Затем цифровые данные S (1, 3) вводятся в блок 700 обработки коррекции и сохраняются в FIFO, в соответствии с нарастанием S_CLK. Затем цифровые данные N (1, 4) вводятся в блок 700 обработки коррекции. Сумматор 711 суммирует цифровые данные N (1, 4), цифровые данные N (1, 1), цифровые данные N (1, 2) и цифровые данные N (1, 3) и сохраняет результат дополнения в элементе 712 задержки, в соответствии с передним фронтом N_CLK. Четверть результата дополнения вычисляется умножителем 713 для усреднения, и затем вводится на сумматор 703. Затем цифровые данные S (1, 4) вводятся в блок 700 обработки коррекции и сохраняются в FIFO, в соответствии с передним фронтом S_CLK. Цифровые данные S (1, 1) вводятся от FIFO в сумматор 703. Сумматор 703 выполняет обработку вычитания с выходными данными от блока 702 обработки пиксельных данных и выходными данными от блока 701 обработки данных сброса и выводит скорректированные пиксельные данные D (1, 1). Скорректированные пиксельные данные D (1, 1) вычисляются следующим образом: S (1, 1)-(N (1, 1)+N (1, 2)+N (1, 3)+N (1, 4))/4. Скорректированные пиксельные данные D (1, 2) вычисляются следующим образом: S (1, 2)-(N (1, 1)+N (1, 2)+N (1, 3)+N (1, 4))/4.

[0049] Во втором варианте осуществления, когда число пикселей в направлении строки увеличивается, увеличивается степень точности LPF по сравнению с первым вариантом осуществления. Обработка коррекции может быть выполнена более эффективно. Поскольку операция вывода данных псевдосброса не выполняется, возможно уменьшить период времени, требуемый для операции обработки сигнала и операции считывания, по сравнению с первым вариантом осуществления. Однако поскольку обработка коррекции пиксельных данных не может быть запущена до тех пор, пока все части данных сброса не будут введены в блок 700 обработки коррекции на основании "строка-за-строкой", период времени, требуемый для обработки коррекции, может быть увеличен.

Третий вариант осуществления

[0050] Третий вариант осуществления настоящего изобретения описан со ссылками на фиг.8. В третьем варианте осуществления операция, выполняемая в третьем варианте осуществления, отличается от операции, выполняемой в первом и втором вариантах осуществления. Подробное описание конфигурации и операции, которые были уже описаны в первом и втором вариантах осуществления, опущено.

[0051] Фиг.8 является временной диаграммой, описывающей операцию восприятия изображения согласно третьему варианту осуществления. Первая операция вывода данных псевдосброса выполняется до того, как будет выполнена первая операция вывода пиксельных данных в периоде операции обработки сигнала в блоках строк. Вторая операция вывода данных псевдосброса выполняется после того, как была выполнена последняя операция вывода пиксельных данных. Операция вывода данных сброса не выполняется между операциями вывода пиксельных данных. Соответственно, период времени, требуемый для операции обработки сигнала и операции считывания в третьем варианте осуществления, является более коротким, чем период времени в первом и втором вариантах осуществления. При обработке коррекции согласно третьему варианту осуществления выполняется усреднение, используя части данных сброса, полученных посредством операции вывода данных псевдосброса в блоках строк. Скорректированные пиксельные данные D (1, 1) вычисляются следующим образом: S (1, 1)-(Ndl+Nd2)/2. Скорректированные пиксельные данные D (1, 2) вычисляются следующим образом: S (1, 2)-(Ndi+Nd2)/2.

[0052] В третьем варианте осуществления, поскольку операция вывода данных сброса не выполняется между операциями вывода пиксельных данных, возможно уменьшить период времени, требуемый для операции обработки сигнала и операции считывания, по сравнению с первым и вторым вариантами осуществления. Однако, поскольку обработка коррекции пиксельных данных не может быть запущена до тех пор, пока данные сброса, полученные в последней операции вывода данных сброса, не будут введены в блок обработки коррекции, может быть увеличен период времени до того, как будет запущена обработка коррекции.

Четвертый вариант осуществления

[0053] Ниже четвертый вариант осуществления настоящего изобретения описан со ссылками на фиг.9. В четвертом варианте осуществления схема считывания имеет конфигурацию, отличающуюся от описанной в первом варианте осуществления, и способ использования схемы считывания отличается от способа, описанного в первом варианте осуществления. Различие между четвертым вариантом осуществления и первым вариантом осуществления описано со ссылками на первую схему 103a считывания.

[0054] Фиг.9 является диаграммой эквивалентной схемы, описывающей схему считывания согласно четвертому варианту осуществления. В четвертом варианте осуществления в качестве первого блока 202a схемы усиления используется схема усиления, имеющая переменный коэффициент усиления. Блок 108 управления переключается между коэффициентами усиления блока 202 схемы усиления, в соответствии с режимом захвата изображения. Например, в устройстве отображения излучения, подходящем для отображения диагностики, блок 108 управления может переключаться между коэффициентами усиления блока 202 схемы усиления, в соответствии с режимом флюороскопии (режим фиксации (захвата) движущегося изображения) или режимом фиксации обычного изображения (режим фиксации неподвижного изображения) посредством подачи сигнала 116sw управления блоку 202 схемы усиления. В четвертом варианте осуществления управляется коэффициент усиления блока 202 схемы усиления таким образом, чтобы коэффициент усиления, используемый десять раз в режиме фиксации обычного изображения, был установлен в режиме флюороскопии.

[0055] Когда коэффициент усиления блока 202 схемы усиления является высоким, шум, включенный в пиксельные данные, является самым сильным шумом, генерируемым блоком 101 обнаружения и блоком 202 схемы усиления. Соответственно, воздействие компонента шума 1/f, генерируемого первым усилителем 205a с переменным усилением и первым A/D преобразователем 104a, становится относительно малым. Искажение, вызванное шумом 1/f, становится незначительным на изображении.

[0056] В четвертом варианте осуществления блок 108 управления управляет блоком 103 схемы считывания и блоком 400 обработки коррекции таким образом, чтобы вышеописанная обработка коррекции не была выполнена в первом режиме фиксации изображения, в котором коэффициент усиления блока 202 схемы усиления является высоким, и вышеописанная обработка коррекции выполняется во втором режиме фиксации изображения, в котором коэффициент усиления блока 202 схемы усиления является низким. Когда шум в форме полос равен или меньше, чем одна десятая случайного шума на изображении, полученном, когда не выполняется обработка коррекции, обработка коррекции может не выполняться. Когда шум в форме полос больше, чем одна десятая случайного шума, обработка коррекции обязательно должна быть выполнена. Аналогично, когда часть этапа изображения равна или меньше, чем одна десятая случайного шума на изображении, полученном, когда не выполняется обработка коррекции, обработка коррекции не может быть выполнена. Когда часть этапа изображения больше, чем одна десятая случайного шума, обработка коррекции обязательно должна быть выполнена. Определяется заранее, выполняется ли обработка коррекции в каждом режиме фиксации изображения на основании вышеописанных критериев, и блок 108 управления выполняет вышеописанную обработку управления.

[0057] Таким образом, обработка управления выполняется таким образом, чтобы обработка коррекции не была выполнена в режиме фиксации изображения, в котором не требуется обработка коррекции. В результате возможно уменьшить период времени, требуемый для операции фиксации изображения, и возможно увеличить скорость передачи кадра считывания. Например, наиболее желаемо, чтобы скорость передачи кадра считывания могла быть увеличена во флюороскопии, как в четвертом варианте осуществления, чтобы уменьшить воздействие излучения на пациента.

Примерное применение

[0058] Фиг.10A и фиг.10B иллюстрируют примерное применение мобильной системы отображения излучения согласно варианту осуществления настоящего изобретения. Фиг.10A является схематической диаграммой, иллюстрирующей систему отображения излучения, использующую мобильное устройство отображения излучения, способное выполнять флюороскопию и фиксацию неподвижного изображения. Фиг.10A иллюстрирует случай, в котором устройство 100 восприятия изображения удалено от кронштейна 601 типа С, и фиксация изображения выполняется устройством 206 генерирования излучения, расположенным на кронштейне 601 типа С. Кронштейн 601 типа С держит устройство 206 генерирования излучения и устройство 100 восприятия изображения. Блок 602 отображения может показывать изображение с данными изображения, захваченными устройством 100 восприятия изображения. Кровать 603 используется для размещения объекта 604 испытания. Тележка 605 позволяет устройству 206 генерирования излучения, устройству восприятия изображения и кронштейну 601 типа С перемещаться. Мобильное устройство 606 управления может управлять устройством 206 генерирования излучения, устройством 100 восприятия изображения и кронштейном 601 типа С. Мобильное устройство 606 управления может выполнять обработку изображения в отношении сигнала изображения, захваченного устройством 100 восприятия изображения, и передавать генерируемые данные изображения на блок 602 отображения. Данные изображения, генерируемые мобильным устройством 606 управления, могут быть переданы на удаленное место с помощью блока передачи, такого как телефонная линия. Поэтому возможно показывать изображение на экране отображения в удаленном месте, например комнате врача, с данными изображения, или хранить данные изображения в блоке хранения, таком как оптический диск в комнате врача. Это позволяет врачу в комнате врача выполнять медицинский осмотр. Переданные данные изображения могут быть записаны на рентгенограмму посредством аппарата для проявления рентгенограммы. Блок 108 управления может быть полностью или частично обеспечен в устройстве 100 восприятия изображения или может быть обеспечен в мобильном устройстве 606 управления.

[0059] Фиг.10B является диаграммой, иллюстрирующей систему отображения излучения, использующую мобильное устройство отображения излучения, способное выполнять флюороскопию и фиксацию неподвижного изображения. Фиг.10B иллюстрирует случай, в котором устройство 100 восприятия изображения удалено от кронштейна 601 типа С, и фиксация изображения выполняется устройством 607 генерирования излучения, не используя устройство 206 генерирования излучения, расположенное на кронштейне 601 типа С. Блок 108 управления может управлять не только устройством 206 генерирования излучения, но также и устройством 607 генерирования излучения.

[0060] Вариант осуществления настоящего изобретения может быть реализован посредством выполнения программы, например, компьютером. Кроме того, носитель для доставки вышеописанной программы в компьютер, например считываемый компьютером носитель записи, такой как компакт диск (CD-ROM), хранящий вышеописанную программу, или носитель передачи, такой как Интернет, для передачи вышеописанной программы могут быть включены в объем настоящего изобретения. Программа может быть применена как вариант осуществления настоящего изобретения. Программа, носитель записи, носитель передачи и программный продукт включены в объем настоящего изобретения. В вышеописанных вариантах осуществления блок обработки цифровых данных в устройстве 100 восприятия изображения выполняет обработку коррекции. Однако внешнее устройство устройства 100 восприятия изображения, например мобильное устройство 606 управления, может выполнять обработку коррекции.

[0061] В то время как настоящее изобретение было описано с ссылками на примерные варианты осуществления, должно быть понятно, что изобретение не ограничивается раскрытыми примерными вариантами осуществления. Например, по меньшей мере один вариант осуществления настоящего изобретения был описан как устройство отображения изображения, подходящее для отображения при медицинском осмотре или промышленном неразрушающем контроле. Другие варианты осуществления могут быть подходящими для отображения в обычной фотографии или даже в экспериментальной физике. Для этой цели излучение, описанное в настоящем описании, может включать в себя рентгеновский луч, электромагнитную волну, такую как γ -луч, α-луч и β-луч. Соответственно, объем охраны следующей формулы изобретения должен получить самую широкую интерпретацию, чтобы охватить все такие модификации и эквивалентные структуры, и функции.

Изобретения относится к средствам захвата изображения. Техническим результатом является снижение уровня шума на захваченном изображении. Результат достигается тем, что устройство восприятия изображения включает в себя блок обнаружения, в котором матрица пикселей преобразовывает излучение или свет в аналоговые электрические сигналы, схему считывания, сконфигурированную для выполнения операции обработки сигнала посредством считывания аналоговых электрических сигналов на основании "строка-за-строкой", A/D преобразователь, сконфигурированный для преобразования пиксельного сигнала, выведенного от схемы считывания, в пиксельные данные, и блок обработки коррекции, сконфигурированный для коррекции пиксельных данных. Блок управления выполняет обработку управления таким образом, чтобы схема считывания выводила сигналы сброса на A/D преобразователь в период, в который выполняется операция обработки сигнала заранее определенной строки, A/D преобразователь преобразует сигналы сброса в части данных сброса в упомянутый период, и блок обработки коррекции усредняет части данных сброса, выведенных от A/D преобразователя, и выполняет вычитание с усредненными данными сброса и пиксельными данными, выведенными от A/D преобразователя. 3 н. и 12 з.п. ф-лы, 14 ил.

1. Устройство восприятия изображения, содержащее:

блок обнаружения, имеющий матрицу пикселей для преобразования излучения или света в аналоговые электрические сигналы;

схему считывания, сконфигурированную для выполнения операции обработки сигнала, для считывания аналоговых электрических сигналов, выводимые из матрицы пикселей на основании "строка-за-строкой";

аналого-цифровой (A/D) преобразователь, сконфигурированный для преобразования пиксельного сигнала, переданного от схемы считывания, в пиксельные данные, которые являются цифровыми данными;

блок обработки коррекции, сконфигурированный для выполнения обработки коррекции в отношении пиксельных данных; и

блок управления, сконфигурированный для управления схемой считывания, A/D преобразователем и блоком обработки коррекции,

в котором схема считывания включает в себя блок сброса, сконфигурированный для выведения сигнала сброса на A/D преобразователь, и

в котором блок управления управляет схемой считывания, A/D преобразователем и блоком обработки коррекции таким образом, чтобы схема считывания выводила множество сигналов сброса на A/D преобразователь в период, в который выполняется операция обработки сигнала заранее определенной строки, A/D преобразователь преобразует множество сигналов сброса во множество частей данных сброса, которые являются частями цифровых данных, в упомянутый период, и блок обработки коррекции усредняет множество частей данных сброса, выведенных от A/D преобразователя, и выполняет обработку вычитания с усредненными данными сброса и пиксельными данными, выведенными от A/D преобразователя.

2. Устройство восприятия изображения по п.1, в котором схема считывания, сконфигурированная для выполнения операции обработки сигнала, дополнительно сконфигурирована для выполнения операции вывода данных сброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса на блок обработки коррекции, и для выполнения операции вывода пиксельных данных, чтобы заставить схему считывания и A/D преобразователь выводить пиксельные данные.

3. Устройство восприятия изображения по п.1, в котором блок обработки коррекции усредняет множество частей данных сброса, удовлетворяющих условию, что множество частей данных располагается близко от пиксельных данных во времени, и количество частей данных сброса до и после пиксельных данных является одним и тем же.

4. Устройство восприятия изображения по п.3, в котором операция обработки сигнала дополнительно включает в себя операцию вывода данных псевдосброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса до первой операции вывода пиксельных данных, выполняемой в упомянутый период, или после последней операции вывода пиксельных данных, выполняемой в упомянутый период.

5. Устройство восприятия изображения по п.2, в котором блок обработки коррекции усредняет все из множества частей данных сброса, выведенных от A/D преобразователя в упомянутый период.

6. Устройство восприятия изображения по п.2, в котором операция обработки сигнала включает в себя первую операцию вывода данных псевдосброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса до первой операции вывода пиксельных данных, выполняемой в упомянутый период, и вторую операцию вывода данных псевдосброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса после последней операции вывода пиксельных данных, выполняемой в упомянутый период, и не включает в себя операцию вывода данных сброса между первой операцией вывода пиксельных данных и последней операцией вывода пиксельных данных, и в котором блок обработки коррекции усредняет данные сброса, выведенные в первой операции вывода данных псевдосброса, и данные сброса, выведенные во второй операции вывода данных псевдосброса.

7. Устройство восприятия изображения по п.1, в котором устройство восприятия изображения имеет множество режимов фиксации изображения, и

в котором блок управления управляет схемой считывания, A/D преобразователем и блоком обработки коррекции таким образом, чтобы обработка коррекции не была выполнена в одном из множества режимов фиксации изображения, в котором шум в форме полос составляет не больше, чем одну десятую случайного шума на изображении, полученном, когда не выполняется обработка коррекции, и обработка коррекции выполняется в другом одном из множества режимов фиксации изображения, в котором шум в форме полос составляет больше, чем одну десятую случайного шума на изображении.

8. Система восприятия изображения, содержащая:

устройство восприятия изображения по п.1; и блок отображения, способный отображать изображение с данными изображения, полученными упомянутым устройством восприятия изображения.

9. Способ управления устройством восприятия изображения, включающим в себя блок обнаружения, в котором матрица пикселей преобразовывает излучение или свет в аналоговые электрические сигналы, схему считывания, сконфигурированную для выполнения операции обработки сигнала, чтобы считывать аналоговые электрические сигналы, выведенные из матрицы пикселей на основании "строка-за-строкой", A/D преобразователь, сконфигурированный для преобразования пиксельного сигнала, переданного от схемы считывания, в пиксельные данные, которые являются цифровыми данными, и блок обработки коррекции, сконфигурированный для выполнения обработки коррекции в отношении пиксельных данных, при этом способ управления содержит этапы:

управление схемой считывания, чтобы выводить множество сигналов, выведенных от блока сброса, включенного в схему считывания, и чтобы выводить пиксельный сигнал на A/D преобразователь в период, в который выполняется операция обработки сигнала заранее определенной строки;

управление A/D преобразователем, чтобы преобразовывать пиксельный сигнал, выведенный от схемы считывания, в пиксельные данные, которые являются цифровыми данными, и чтобы преобразовывать множество сигналов сброса, выведенных от схемы считывания, во множество частей данных сброса, которые являются частями цифровых данных в упомянутый период; и

управление блоком обработки коррекции, чтобы усреднять множество частей данных сброса, выведенных от A/D преобразователя в упомянутый период, и чтобы выполнять обработку вычитания с пиксельными данными, выведенными из A/D преобразователя, и усредненными данными сброса.

10. Способ управления по п.9, в котором операция обработки сигнала включает в себя операцию вывода данных сброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса на блок обработки коррекции, и операцию вывода пиксельных данных, чтобы заставить схему считывания и A/D преобразователь выводить пиксельные данные.

11. Способ управления по п.9, в котором блок обработки коррекции усредняет множество частей данных сброса, удовлетворяющих условию, что множество частей данных сброса располагается близко от пиксельных данных во времени, и количество частей данных сброса до и после пиксельных данных является одним и тем же.

12. Способ управления по п.11, в котором операция обработки сигнала дополнительно включает в себя операцию вывода данных псевдосброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса до первой операции вывода пиксельных данных, выполняемой в упомянутый период, или после последней операции вывода пиксельных данных, выполняемой в упомянутый период.

13. Способ управления по п.10, в котором усреднение выполняется, используя все из множества частей данных сброса, выведенных из A/D преобразователя в упомянутый период.

14. Способ управления по п.10, в котором операция обработки сигнала включает в себя первую операцию вывода данных псевдосброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса до первой операции вывода пиксельных данных, выполняемой в упомянутый период, и вторую операцию вывода данных псевдосброса, чтобы заставить схему считывания и A/D преобразователь выводить данные сброса после последней операции вывода пиксельных данных, выполняемой в упомянутый период, и не включает в себя операцию вывода данных сброса между первой операцией вывода пиксельных данных и последней операцией вывода пиксельных данных, и

в котором усредняются данные сброса, выведенные в первой операции вывода данных псевдосброса, и данные сброса, выведенные во второй операции вывода данных псевдосброса.

15. Способ управления по п.9, в котором устройство восприятия изображения имеет множество режимов фиксации изображения, и в котором не выполняется обработка коррекции в одном из множества режимов фиксации изображения, в котором шум в форме полос равен или меньше, чем одна десятая случайного шума на изображении, полученном, когда не выполняется обработка коррекции, и обработка коррекции выполняется в другом одном из множества режимов фиксации изображения, в котором шум в форме полос является больше, чем одна десятая случайного шума на изображении.

| JP 2000013811 А, 14.01.2000 | |||

| Устройство для загрузки и выгрузки гофманских печей | 1937 |

|

SU54478A1 |

| US 2004113180 A1, 17.06.2004 | |||

| US 2003169196 A1, 11.09.2003 | |||

| СПОСОБ СЧИТЫВАНИЯ СИГНАЛЬНОГО ЗАРЯДА С МАТРИЧНОГО ПЗИ-ФОТОПРИЕМНИКА | 2007 |

|

RU2339118C1 |

Авторы

Даты

2011-11-27—Публикация

2010-06-29—Подача