Изобретение относится к области цифровой вычислительной техники и предназначено для разработки и конструирования специализированных устройств для обработки и анализа сигналов разнообразной природы с помощью непрерывного вейвлет-преобразования.

Известны устройства для вычисления дискретного вейвлет-преобразования сигнала, содержащие цепочку пар фильтров высокой и низкой частоты, после каждой из которых производится децимация сигнала в 2 раза (см., например, «Введение в вейвлет-преобразование» R.Polikar, пер. с англ. В.Грибунин, изд. АВТЭКС, СПб., с.53, http://autex.spb.ru/wavelet/). Алгоритмы, на которых основаны эти устройства, характеризуются высоким быстродействием, небольшими аппаратурными затратами, но они основаны на отбрасывании части информации, которую относят к избыточной. Это обоснованно применимо, когда решается задача реконструкции сигнала по его вейвлет-преобразованию. Но для задач, отличных от реконструкции, например анализа данных, требуется полная информация о вейвлет-спектре. Если заранее не известно, какую информацию считать избыточной, то применение алгоритмов дискретного вейвлет-преобразования в таких случаях может приводить к потере полезной информации.

Полную информацию о вейвлет-спектре анализируемых данных получают с помощью алгоритмов непрерывного вейвлет-преобразования (НВП). При реализации этих алгоритмов на ЭВМ требуется оцифровка анализируемого сигнала, поэтому такие алгоритмы называют дискретизированным непрерывным вейвлет-преобразованием или дискретным вейвлет-преобразованием с произвольным шагом дискретизации.

Наиболее близким к заявляемому техническому решению является устройство быстрого вычисления дискретного вейвлет-преобразования сигнала с произвольным шагом дискретизации масштабных коэффициентов (Патент РФ №2246132, МПК G06F 17/14, опубл. 10.02.2005). В качестве прототипа выбран второй вариант устройства.

Устройство состоит из аналого-цифрового преобразователя, вход которого является входом устройства, вычислителя быстрого преобразования Фурье, формирователя аналитического сигнала (устройство обнуления отрицательных частот), делителя, первого постоянного запоминающего устройства, матричного перемножителя, второго постоянного запоминающего устройства, вычислителя двумерного обратного преобразования Фурье и управляющего устройства.

Недостатком устройства является сложность реализации и, как следствие, большие аппаратурные затраты. Так, например, только перечисленный в качестве одного из блоков вычислитель быстрого преобразование Фурье является сложным арифметическим устройством, содержащим регистры, умножители и сумматоры (см., например, Патент РФ №2190874, МПК G06F 17/14, опубл. 10.10.2002). Еще более сложным является перечисленный в составе устройства вычислитель двумерного обратного преобразования Фурье.

Задачей изобретения является упрощение конструкции устройства при сохранении его быстродействия для дискретизированного непрерывного вейвлет-преобразования данных.

Поставленная задача достигается тем, что устройство для вычисления дискретизированного непрерывного вейвлет-преобразования содержит, также как в прототипе, управляющее устройство и аналого-цифровой преобразователь, вход которого является входом устройства.

Согласно изобретению веден блок ячеек однородной структуры размером J×K, где J - максимальное количество масштабов по времени, К - максимальное количество сдвигов по времени дискретизированного непрерывного вейвлет-преобразования, причем каждая из ячеек содержит блок адресации, связанный через магистраль общая шина с выходом управляющего устройства, интегратор, выход которого подключен к блоку адресации, а вход связан с выходом умножителя, первый вход которого соединен с магистралью общая шина, а второй подключен к выходу блока сдвиговых регистров, вход которого соединен с блоком адресации, при этом вход управляющего устройства подключен к выходу аналого-цифрового преобразователя.

Использование ячеек однородной структуры, реализующих однотипные вычисления параллельно, позволяет легко наращивать их количество в зависимости от объема решаемой задачи. Однотипность вычислений в ячейках снижает сложность конструкции устройства. Параллельность вычислений обеспечивает как минимум сохранение высокого быстродействия.

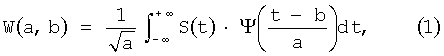

Непрерывное вейвлет-преобразование произвольного сигнала S(t) описывается уравнением:

где W(a,b) - искомая переменная;

t - время;

- некоторая функция с определенными свойствами (вейвлет);

- некоторая функция с определенными свойствами (вейвлет);

b - сдвиг по времени;

а - масштаб по времени (соответствующий частоте).

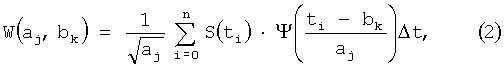

Для оцифрованного с равномерным шагом сигнала, имеющего конечные пределы по времени, интеграл в уравнении (1) аппроксимируется конечной суммой:

где i, j, k - индексы по времени t, по масштабу а, по сдвигу по времени b;

n - количество шагов по времени;

Δt - шаг по времени;

S(ti) - оцифрованный сигнал (данные).

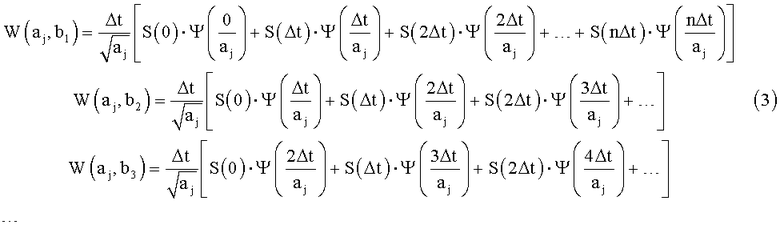

Если принять начальный момент времени нулевым, а сдвиг по времени равным шагу по времени (что соответствует наибольшей разрешающей способности НВП), то уравнение (2) можно записать в виде системы уравнений:

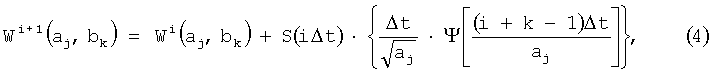

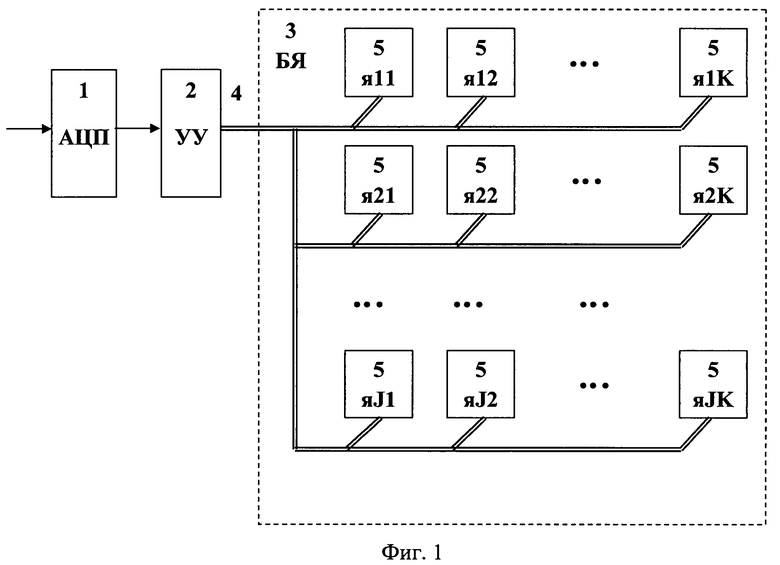

Очевидно, что все выражения, на которые должны умножаться данные S(iΔt), могут быть вычислены заранее и занесены в виде коэффициентов для блока умножения. Систему уравнений (3) можно записать в виде итерационной формулы:

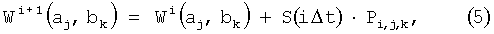

или

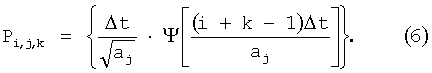

где

Формула (5) легко реализуется с помощью цифрового интегратора. Следовательно, объединяя блок умножения данных на заранее известные коэффициенты с цифровым интегратором в одну вычислительную ячейку, можно вычислить одну точку двумерного массива дискретизированного вейвлет-преобразования. Объединяя далее такие ячейки в однородную структуру размером J×K, где J - максимальное количество масштабов по времени, К - максимальное количество сдвигов по времени, можно получать дискретизированное непрерывное вейвлет-преобразование данных в полном объеме.

Таким образом, вычисление дискретизированного непрерывного вейвлет-преобразования оцифрованных данных распределяется между синхронно-параллельно работающими ячейками однородной структуры. На вход каждой ячейки синхронно подаются оцифрованные данные, подлежащие НВП, которые умножаются на заранее подготовленные коэффициенты (6), хранящиеся в каждой ячейке, и накапливаются в интеграторе в соответствии с формулой (4). Каждая ячейка однородной структуры дает одно значение дискретизированного непрерывного вейвлет-преобразования W(aj, bk), поэтому вся однородная структура ячеек размером J×K даст полный спектр значений НВП.

Техническим результатом является упрощение конструкции и снижение аппаратурных затрат при сохранении высокого быстродействия устройства для вычисления дискретизированного непрерывного вейвлет-преобразования.

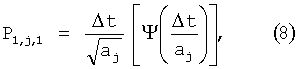

На фиг.1 представлена схема устройства для вычисления дискретизированного непрерывного вейвлет-преобразования.

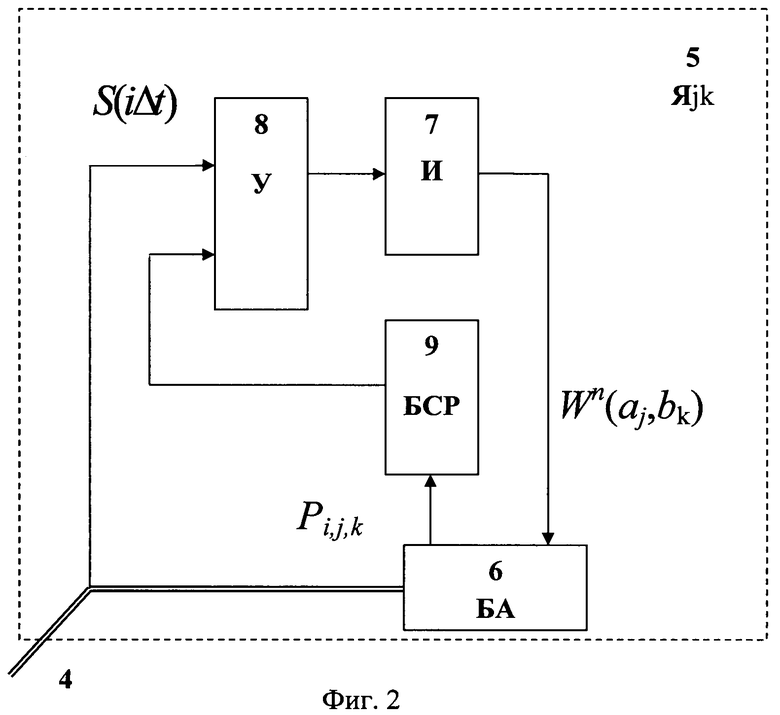

На фиг.2 представлена схема ячейки однородной структуры, входящей в состав устройства для вычисления дискретизированного непрерывного вейвлет-преобразования.

Устройство для вычисления дискретизированного непрерывного вейвлет-преобразования содержит аналого-цифровой преобразователь 1 (АЦП), вход которого является входом устройства, а выход соединен с входом управляющего устройства 2 (УУ), выход которого через магистраль общая шина 4 связан с блоком ячеек однородной структуры 3 (БЯ), который содержит J×K ячеек однородной структуры 5 (Яjk), где J - максимальное количество масштабов по времени дискретизированного непрерывного вейвлет-преобразования, К - максимальное количество сдвигов по времени дискретизированного непрерывного вейвлет-преобразования. Каждая ячейка 5(Яjk) соединена с магистралью общая шина 4.

Ячейка однородной структуры 5(Яjk) для устройства дискретизированного непрерывного вейвлет-преобразования содержит блок адресации 6 (БА), связанный с магистралью общая шина 4, интегратор 7 (И), выход которого подключен к блоку адресации 6 (БА), а вход связан с выходом умножителя 8 (У), первый вход которого соединен с магистралью общая шина 4, а второй подключен к выходу блока сдвиговых регистров 9(БСР), вход которого соединен с блоком адресации 6(БА).

Перечисленные элементы ячейки однородной структуры могут быть реализованы на базе цифровых интегральных микросхем, например, серии К500-К531 (Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги. Справочник. Т4, 2001), а также на базе ПЛИС или полузаказных БИС на основе БМК, выпускаемых, например, фирмами «Ангстрем» (www.angstrem.ru), «Модуль» (www.module.ru). Аналого-цифровой преобразователь и устройство управления могут быть реализованы на любых микросхемах, имеющих электрическое и логическое сопряжение с элементами, выбранными для реализации ячеек.

Устройство для вычисления дискретизированного непрерывного вейвлет-преобразования работает следующим образом. Процесс решения состоит из двух циклов: цикла обмена данными ячеек однородной структуры 5(Яjk) с управляющим устройством 2 (УУ) и цикла итераций, в котором ячейки вычисляют значения искомой величины.

В цикле обмена данными управляющее устройство 2 (УУ) через магистраль общая шина 4 передает каждой ячейке заранее рассчитанные внешним устройством коэффициенты уравнения Pi,j,k. В каждой ячейке блок адресации 6 (БА) сверяет адрес, указанный в магистрали с собственным адресом, и, если они совпадают, записывает эти данные в блок сдвиговых регистров 9 (БСР). В этом же цикле, если он не первый, из интегратора 7 (И) считывается накопленный за предыдущий цикл результат расчета Wn(aj, bk).

В цикле итераций анализируемый сигнал S(t) поступает на вход аналого-цифрового преобразователя 1 (АЦП), с выхода которого дискретная выборка S(iΔt) длиной n отсчетов поступает на вход управляющего устройства 2 (УУ), с выхода которого синхронно передается на входы всех ячеек блока 3 (БЯ) через магистраль общая шина 4.

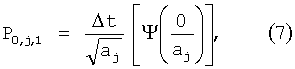

Рассмотрим цикл итераций на первом слое ячеек (k=1). В начальный момент времени (i=0), входной сигнал S(0) подается на первый вход умножителя 8 (У) всех ячеек блока 3 (БЯ) через магистраль общая шина 4. На второй вход умножителя 8 (У) в это время подается с выхода блока сдвиговых регистров 9 (БСР) значение хранящегося там коэффициента

который умножается на входной сигнал S(0), и результат W1(aj,b1) передается в интегратор 7 (И).

На втором шаге по времени на первый вход умножителя 8 (У) всех ячеек блока 3 (БЯ) через магистраль общая шина 4 подается входной сигнал S(Δt). На второй вход умножителя 8 (У) в это время подается с выхода блока сдвиговых регистров 9 (БСР) значение следующего хранящегося коэффициента

который умножается на входной сигнал S(Δt) и передается в интегратор 7 (И), где складывается с хранящимся там предыдущим значением, и в результате получается W2(аj,b1).

Аналогично цикл итераций выполняется и на следующих шагах по времени, пока не достигает заданного количества шагов по времени n. Результат Wn(aj,b1) считывается из интегратора 7 (И) в следующем цикле обмена данными ячеек однородной структуры 5(Яjk) с управляющим устройством 2 (УУ).

Таким же образом в цикле итераций синхронно и параллельно работают все ячейки однородной структуры, в результате чего получается массив значений дискретизированного непрерывного вейвлет-преобразования Wn(aj,bk).

Устройство управления 2 (УУ) осуществляет синхронизацию работы блоков 1 (АЦП), 3(БЯ), магистрали общая шина 4, а также производит индикацию полученного результата либо передает этот результат для индикации во внешнее устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБНАРУЖЕНИЯ УЗКОПОЛОСНЫХ ШУМОВЫХ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ НА ОСНОВЕ НЕПРЕРЫВНОГО ВЕЙВЛЕТ-ПРЕОБРАЗОВАНИЯ | 2012 |

|

RU2510037C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ УЗКОПОЛОСНЫХ ШУМОВЫХ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ НА ОСНОВЕ ВЫЧИСЛЕНИЯ ИНТЕГРАЛЬНОГО ВЕЙВЛЕТ-СПЕКТРА | 2007 |

|

RU2367970C2 |

| Анализатор спектра с линейным предсказанием | 1985 |

|

SU1275315A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ШУМОВЫХ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ В ВИДЕ ЗВУКОРЯДА НА ОСНОВЕ ВЫЧИСЛЕНИЯ ИНТЕГРАЛЬНОГО ВЕЙВЛЕТ-СПЕКТРА | 2011 |

|

RU2464588C1 |

| УСТАНОВЛЕНИЕ ТРАКТОВ ВЫЗОВОВ СЕТЕЙ СВЯЗИ В ШИРОКОПОЛОСНЫХ СЕТЯХ СВЯЗИ | 1993 |

|

RU2117403C1 |

| АДРЕСУЕМАЯ ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 2010 |

|

RU2427033C1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СЛОЖНЫХ ШИРОКОПОЛОСНЫХ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ С ФИЛЬТРАЦИЕЙ В МАСШТАБНО-ВРЕМЕННОЙ ОБЛАСТИ НА ОСНОВЕ ДИСКРЕТНОГО ВЕЙВЛЕТ-ПРЕОБРАЗОВАНИЯ | 2010 |

|

RU2439601C1 |

| Способ и устройство преобразования сигналов произвольной формы с использованием пилообразных ступенчатых вейвлетов | 2017 |

|

RU2682860C2 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

Изобретение относится к области цифовой вычислительной техники и может быть использовано в специализированных устройствах для обработки и анализа сигналов с использованием непрерывного вейвлет-преобразования. Техническим результатом является упрощение конструкции устройства при сохранении его быстродействия для дискретизированного непрерывного вейвлет-преобразования данных. Устройство содержит управляющее устройство, аналого-цифровой преобразователь, блок ячеек однородной структуры размером J×K, где J - максимальное количество масштабов по времени, К - максимальное количество сдвигов по времени дискретизированного непрерывного вейвлет-преобразования, при этом каждая из ячеек содержит блок адресации, интегратор, умножитель, блок сдвиговых регистров. 2 ил.

Устройство для вычисления дискретизированного непрерывного вейвлет-преобразования, содержащее управляющее устройство и аналого-цифровой преобразователь, вход которого является входом устройства, отличающееся тем, что введен блок ячеек однородной структуры размером J×K, где J - максимальное количество масштабов по времени, К - максимальное количество сдвигов по времени дискретизированного непрерывного вейвлет-преобразования, причем каждая из ячеек содержит блок адресации, связанный через магистраль общая шина с выходом управляющего устройства, интегратор, выход которого подключен к блоку адресации, а вход связан с выходом умножителя, первый вход которого соединен с магистралью общая шина, а второй подключен к выходу блока сдвиговых регистров, вход которого соединен с блоком адресации, при этом вход управляющего устройства подключен к выходу аналого-цифрового преобразователя.

| СПОСОБ И УСТРОЙСТВО БЫСТРОГО ВЫЧИСЛЕНИЯ ДИСКРЕТНОГО ВЕЙВЛЕТ-ПРЕОБРАЗОВАНИЯ СИГНАЛА С ПРОИЗВОЛЬНЫМ ШАГОМ ДИСКРЕТИЗАЦИИ МАСШТАБНЫХ КОЭФФИЦИЕНТОВ | 2003 |

|

RU2246132C2 |

| Дренажное устройство паросепараторов | 1939 |

|

SU57033A1 |

| US 6424986 B1, 23.07.2002 | |||

| US 2007156801 A1, 05.07.2007. | |||

Авторы

Даты

2011-12-20—Публикация

2010-07-01—Подача