Изобретение относится к области цифровой вычислительной техники и предназначено для разработки и конструирования специализированных устройств для решения дифференциальных уравнений, содержащих частные производные по пространственным и временной координатам, а также для решения систем линейных алгебраических уравнений.

Известен процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных, содержащий решающие блоки, регистры, блок памяти команд, блок памяти данных, блок микропрограммного управления и блоки оповещения (Авторское свидетельство СССР №1280385, МПК3 G06F 15/32, опубл. 30.12.1986, бюл. №48). Это устройство отличается универсальностью при реализации различных типов итерационных процедур вычислений, но его недостатком является избыточность и сложность реализации небольших задач и замедление решения из-за последовательной работы блока микропрограммного управления.

Известна ячейка однородной структуры для решения дифференциальных уравнений в частных производных, содержащая два интегратора, блок масштабных интеграторов, сумматор приращений (Авторское свидетельство СССР №783811, МПК3 G06G 7/56, опубл. 30.11.1980). Это устройство отличаются простотой реализации, высоким быстродействием, но требуют внешнего коммутационного устройства, которое должно обеспечивать ввод коэффициентов уравнения в ячейку и вывод из ячейки результатов решения.

Прототипом выбрана ячейка однородной структуры для решения дифференциальных уравнений в частных производных (патент РФ №2359322, МПК G06F 7/13, G06F 7/64, опубл. 20.06.2009), которая содержит интегратор, блок масштабных интеграторов, выходы которого соединены с входами сумматора приращений, следящий интегратор, выход которого соединен с входом интегратора и с одним из входов блока масштабных интеграторов, а вход следящего интегратора подключен к выходу сумматора приращений, ключевой элемент и блок формирования приращений от искомой переменной с предыдущих шагов по времени, выход которого соединен с одним из входов сумматора приращений, а вход с выходом ключевого элемента, первый вход которого соединен с выходом интегратора, а второй служит входом для сигнала управления, и выходом ячейки для соединения со входами других ячеек однородной структуры является выход следящего интегратора, а входами ячейки для соединения с выходами других ячеек - входы блока масштабных интеграторов. Это устройство отличается возможностью решения дифференциальных уравнений, содержащих частные производные не только по пространственным координатам, но и по времени, простотой реализации, высоким быстродействием, но требует внешнего коммутационного устройства, которое должно обеспечивать ввод коэффициентов уравнения в ячейку и вывод из ячейки результатов решения. При увеличении количества совместно работающих ячеек возрастает сложность реализации этого коммутационного устройства, которая снижает эффект от простоты реализации самих ячеек.

Задачей изобретения является расширение арсенала технических средств аналогичного назначения.

Поставленная задача достигается тем, что адресуемая ячейка однородной структуры для решения дифференциальных уравнений' в частных производных содержит, также как в прототипе, интегратор, блок масштабных интеграторов, выходы которого соединены со входами сумматора приращений, следящий интегратор, выход которого соединен со входом интегратора и с одним из входов блока масштабных интеграторов, при этом вход следящего интегратора подключен к выходу сумматора приращений, ключевой элемент и блок формирования приращений от искомой переменной с предыдущих шагов по времени, выход которого соединен с одним из входов сумматора приращений, а вход с выходом ключевого элемента, первый вход которого соединен с выходом интегратора, причем выходом ячейки для соединения со входами других ячеек однородной структуры является выход следящего интегратора, а входами ячейки для соединения с выходами других ячеек являются входы блока масштабных интеграторов.

Согласно изобретению введены регистр уникального адреса ячейки, блок совпадения и блок распределения, выходы которого связаны со входом для ввода коэффициентов в блок масштабных интеграторов, вторым входом ключевого элемента, входом для ввода начального значения в интегратор, а входы подсоединены к магистрали «общая шина», выходу интегратора для вывода из ячейки результатов решения и выходу блока совпадения, первый вход которого соединен с выходом регистра уникального адреса, а второй вход связан с магистралью «общая шина».

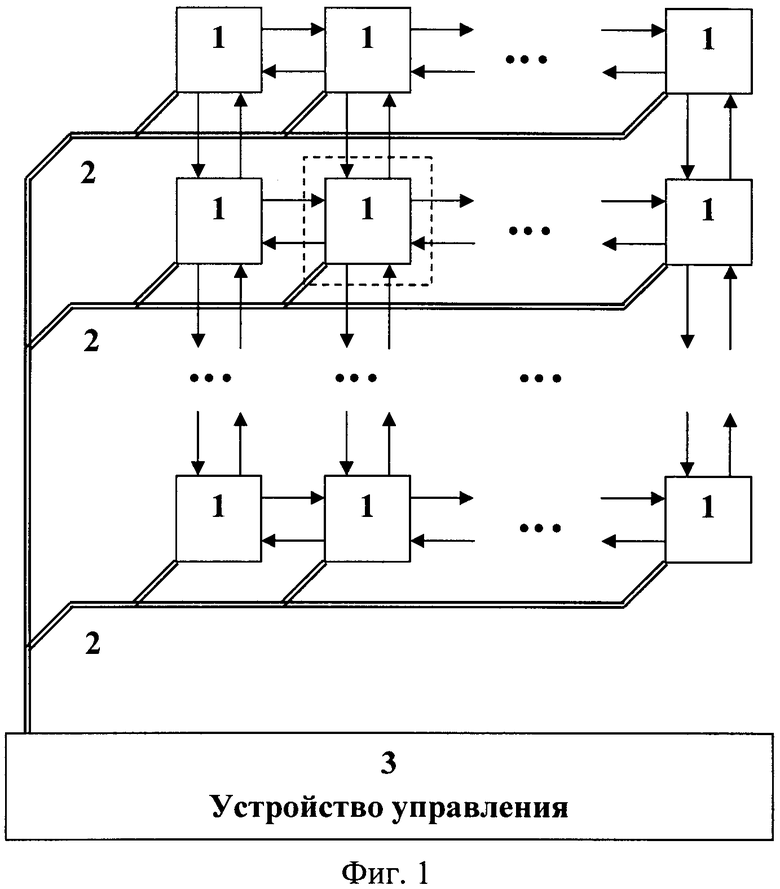

Схема соединения ячеек с устройством управления, которое обеспечивает подачу управляющих сигналов, запись коэффициентов уравнения в ячейки и считывание из ячеек результатов решения, производится по магистрали «общая шина» (фиг.1). Операции обмена данными между перечисленными элементами ячейки и линиями данных в магистрали «общая шина» производятся только в том случае, если адрес, установленный на адресных линиях магистрали, совпадает с уникальным адресом ячейки, занесенным предварительно в регистр уникального адреса.

Это позволяет увеличивать количество ячеек и решать более сложные и масштабные задачи без изменения схемы коммутации.

Таким образом, введение регистра уникального адреса ячейки, блока совпадения и блока распределения дает в качестве технического результата возможность увеличивать количество совместно работающих ячеек и решать более сложные и масштабные задачи без изменения схемы коммутации, что решает задачу расширения арсенала технических средств аналогичного назначения.

На фиг.1 представлена схема соединения ячеек между собой. Выход каждой ячейки 1 связан со входами соседних ячеек, причем каждая ячейка соединена с магистралью «общая шина» 2, которая подключена к устройству управления 3.

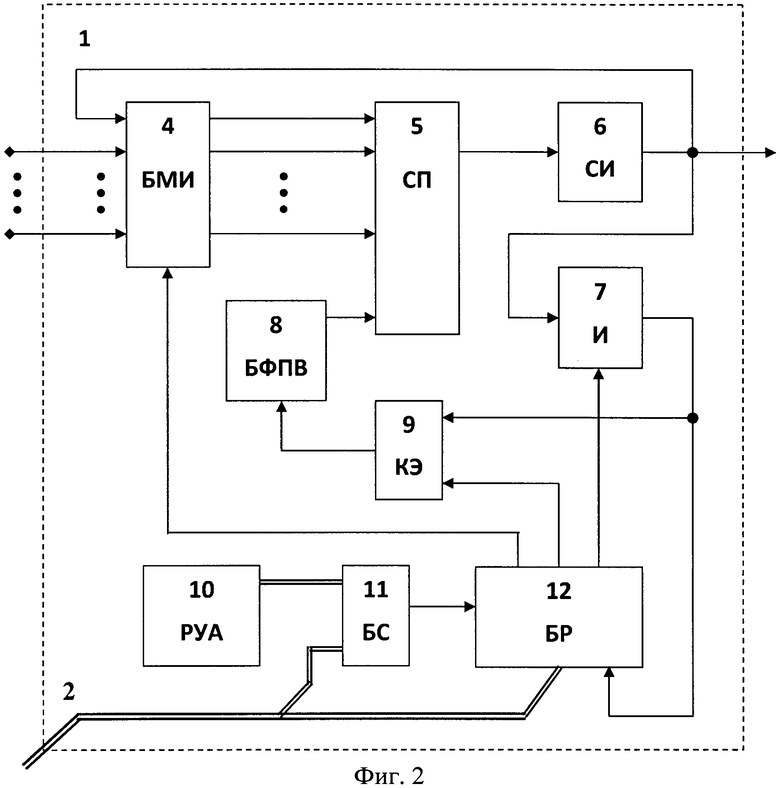

На фиг.2 представлена схема адресуемой ячейки однородной структуры для решения дифференциальных уравнений в частных производных.

Адресуемая ячейка однородной структуры для решения дифференциальных уравнений в частных производных 1 содержит блок масштабных интеграторов 4 (БМИ), сумматор приращений 5 (СП), следящий интегратор 6 (СИ), интегратор 7 (И), блок формирования приращений переменной с предыдущих шагов по времени 8 (БФПВ), ключевой элемент 9 (КЭ), регистр уникального адреса 10 (РУА), блок совпадения 11 (БС) и блок распределения 12 (БР).

Выходы блока масштабных интеграторов 4 (БМИ) связаны со входами сумматора приращений 5 (СП), выход которого соединен со входом следящего интегратора 6 (СИ), выход которого подключен к одному из входов блока масштабных интеграторов 4 (БМИ) и к входу интегратора 7 (И), выход которого связан с первым входом ключевого элемента 9 (КЭ) и с одним из входов блока распределения 12 (БР), другие входы которого подключены к магистрали «общая шина» 2 и к выходу блока совпадения 11 (БС), входы которого подсоединены к магистрали «общая шина» 2 и к выходу регистра уникального адреса 10 (РУА). Выходы блока распределения 12 (БР) связаны со входом для ввода коэффициентов в блок масштабных интеграторов 4 (БМИ), входом для ввода начального значения в интегратор 7 (И), вторым входом ключевого элемента 9 (КЭ), выход которого соединен со входом блока формирования приращений переменной с предыдущих шагов по времени 8 (БФПВ), выход которого соединен с одним из входов сумматора приращений 5 (СП). Выходом ячейки для соединения со входами других ячеек однородной структуры является выход следящего интегратора 6 (СИ), а входами ячейки для соединения с выходами других ячеек являются входы блока масштабных интеграторов 4 (БМИ).

Перечисленные элементы могут быть реализованы на базе цифровых интегральных микросхем, например, серии К500-К531 (Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги. Справочник. Т4, 2001) или заказных ПЛИС, выпускаемых, например, фирмами «Ангстрем» (www.angstrem.ru), «Модуль» (www.module.ru). Для регистра уникального адреса 10 (РУА) целесообразно использовать постоянное или перепрограммируемое запоминающее устройство энергонезависимого типа.

Адресуемая ячейка однородной структуры для решения дифференциальных уравнений в частных производных 1 работает следующим образом. В ячейку предварительно заносят код в регистр уникального адреса 10 (РУА), который для каждой ячейки, объединенной в одну схему, должен быть различным и должен сохраняться постоянным весь период эксплуатации этой схемы соединения ячеек.

Процесс решения состоит из двух циклов: цикла обмена данными ячейки 1 с магистралью «общая шина» 2 и цикла вычисления значения искомой переменной. Последний цикл полностью аналогичен описанному в прототипе циклу вычислений.

Цикл обмена данными ячейки 1 с магистралью «общая шина» 2 протекает следующим образом. После подачи сигнала управления в магистраль «общая шина» 2 от внешнего устройства управления 3, общего для всех ячеек 1 в схеме, цикл вычисления заканчивается и начинается цикл обмена данными с магистралью. Блок совпадения 11 (БС) сравнивает код в адресных линиях магистрали «общая шина» 2 с кодом регистра уникального адреса 10 (РУА) и в случае их совпадения подает разрешающий сигнал на блок распределения 12 (БР).

Если это первый шаг по времени интегрирования, признак которого также устанавливается магистрали «общая шина» 2, то блок распределения 12 (БР) распределяет последовательно поступающие из магистрали «общая шина» 2 начальные значения коэффициентов решаемого уравнения в блок масштабных интеграторов 4 (БМИ), начальное значение искомой переменной в интегратор 7 (И). Если ячейку используют в качестве граничной, то в интегратор 7 (И) заносят граничные значения.

На всех последующих шагах по времени интегрирования дифференциального уравнения в частных производных блок распределения 12 (БР) во время цикла обмена данными подает открывающий сигнал на второй вход ключевого элемента 9 (КЭ), и полученное значение искомой переменной из интегратора 7 (И) передается в блок формирования приращений переменной с предыдущих шагов по времени 8 (БФПВ) для использования его на следующем шаге по времени. Одновременно из магистрали «общая шина» 2 через блок распределения 12 (БР) могут поступать измененные внешним устройством управления 3 значение коэффициентов для блока масштабных интеграторов 4 (БМИ), что позволяет организовать решение дифференциальных уравнений с переменными коэффициентами.

Переданные значения в цикле обмена данными используются в следующем цикле вычисления, который реализует следующий шаг интегрирования по времени.

Если на второй вход ключевого элемента 9 (КЭ) постоянно подавать закрывающий сигнал, то в блок формирования приращений переменной с предыдущих шагов по времени 8 (БФПВ) значение, накопленное в интеграторе 7 (И), не попадает и, следовательно, приращения на выходе блока 8 (БФПВ) отсутствуют, что позволяет организовать решение дифференциальных уравнений, не имеющих частной производной по времени (эллиптического типа).

Эту итерационную процедуру из двух циклов повторяют далее до тех пор, пока не закончится заданное время интегрирования или заданное количество шагов. Итоговый результат вычислений накапливается в интеграторе 7 (И) и передается через блок распределения 12 (БР) в магистраль «общая шина» 2. Через магистраль «общая шина» 2 также подается общий для всех ячеек сигнал сброса, по которому все регистры, имеющиеся в элементах ячейки, обнуляются.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ С ПЕРЕМЕННЫМИ КОЭФФИЦИЕНТАМИ | 2009 |

|

RU2419141C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 2007 |

|

RU2359322C1 |

| Ячейка однородной структуры для решения дифференциальных уравнений в частных производных | 1979 |

|

SU783811A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДИСКРЕТИЗИРОВАННОГО НЕПРЕРЫВНОГО ВЕЙВЛЕТ-ПРЕОБРАЗОВАНИЯ | 2010 |

|

RU2437147C1 |

| Устройство для решения линейных систем алгебраических уравнений | 1985 |

|

SU1325464A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Ячейка интегрирующей структуры для решения уравнения лапласа | 1975 |

|

SU574733A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Цифровое устройство для решения систем линейных алгебраических уравнений | 1975 |

|

SU559241A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

Изобретение относится к области цифровой вычислительной техники и предназначено для разработки и конструирования специализированных устройств для решения дифференциальных уравнений, содержащих частные производные по пространственным и временным координатам, а также для решения систем линейных алгебраических уравнений. Техническим результатом является увеличение количества совместно работающих ячеек без изменения схемы коммутации. Адресуемая ячейка однородной структуры содержит интегратор, блок масштабных интеграторов, сумматор приращений, следящий интегратор, ключевой элемент, блок формирования приращений от искомой переменной с предыдущих шагов по времени, регистр уникального адреса ячейки, блок совпадения и блок распределения. 2 ил.

Адресуемая ячейка однородной структуры для решения дифференциальных уравнений в частных производных с переменными коэффициентами, содержащая интегратор, блок масштабных интеграторов, выходы которого соединены со входами сумматора приращений, следящий интегратор, выход которого соединен со входом интегратора и с одним из входов блока масштабных интеграторов, при этом вход следящего интегратора подключен к выходу сумматора приращений, ключевой элемент и блок формирования приращений от искомой переменной с предыдущих шагов по времени, выход которого соединен с одним из входов сумматора приращений, а вход с выходом ключевого элемента, первый вход которого соединен с выходом интегратора, причем выходом ячейки для соединения со входами других ячеек однородной структуры является выход следящего интегратора, а входами ячейки для соединения с выходами других ячеек являются входы блока масштабных интеграторов, отличающаяся тем, что в нее введены регистр уникального адреса ячейки, блок совпадения и блок распределения, выходы которого связаны со входом для ввода коэффициентов в блок масштабных интеграторов, вторым входом ключевого элемента, входом для ввода начального значения в интегратор, а входы подсоединены к магистрали «общая шина», выходу интегратора для вывода из ячейки результатов решения и выходу блока совпадения, первый вход которого соединен с выходом регистра уникального адреса, а второй вход связан с магистралью «общая шина».

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 2007 |

|

RU2359322C1 |

| СПОСОБ ЧИСЛЕННОГО РЕШЕНИЯ СИСТЕМЫ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2003 |

|

RU2242791C2 |

| Ячейка однородной структуры для решения дифференциальных уравнений в частных производных | 1979 |

|

SU783811A1 |

| US 2002059160 A1, 16.05.2002 | |||

| JP 2000020502 A, 21.01.2000. | |||

Авторы

Даты

2011-08-20—Публикация

2010-03-03—Подача