Область техники

Настоящее изобретение относится к устройству контроля цифровой обработки и, более конкретно, к устройству контроля цифровой обработки, подходящему для контроля выходной мощности ядерного реактора.

Уровень техники

Для кипящего ядерного реактора в последнее время было разработано устройство, в котором применяется FPGA (программируемая пользователем вентильная матрица) для монитора диапазона мощности (PRM), используемого для измерения нейтронного потока внутри ядерного реактора в рабочем режиме, вывода мощности монитора пускового диапазона нейтронов (SRNM) и им подобных. FPGA является разновидностью логической интегральной схемы с возможностью написания индивидуальной логической схемы.

Как показано на фиг.2, монитор диапазона средней мощности (APRM), монитор диапазона локальной мощности (LPRM) и другие составляют вышеуказанный монитор диапазона мощности (PRM), составленный из модулей, каждый из которых составлен из различных плат. Эти компоненты в целом образуют устройство цифровой обработки и контроля для контроля выходной мощности ядерного реактора. Устройство цифровой обработки и контроля составлено из множества модулей (см. патентный документ 1).

Список ссылочных документов

Патентный документ 1: Выложенная заявка №2007-3399 на японский патент.

Сущность изобретения

Техническая задача

В случае обычных модулей платы разрабатываются для каждого модуля. Таким образом, обслуживание и проверка необходима для каждого из модулей. Так, плата, используемая в одном модуле, не может использоваться в другом модуле. Таким образом, например, когда в результате обслуживания и проверки модуля обнаруживается необходимость в замене платы, необходимо использовать плату для вышеописанного модуля. Соответственно, необходима подготовка различных типов плат для замены в соответствии с типом модуля. Таким образом, обслуживание и проверка является сложной и дорогостоящей.

Таким образом, задачей настоящего изобретения является обеспечение устройства цифровой обработки и контроля с улучшенными возможностями обслуживания и экономической эффективностью, в котором количество типов необходимых плат сокращено благодаря универсальности плат.

Решение задачи

Для решения вышеописанной задачи, согласно объекту настоящего изобретения, обеспечивается устройство контроля цифровой обработки, содержащее: множество модулей, каждый из которых включает в себя основную плату с установленными главной управляющей FPGA и управляющей FPGA для управления подплатой, соединенную с разъемом, и подплату обработки интерфейса «человек-машина» с установленной FPGA обработки интерфейса; и материнскую плату, соединенную с каждым из множества модулей, причем на каждой подплате множества модулей установлено устройство хранения данных, которое хранит информацию подплаты интерфейса «человек-машина», и каждая FPGA множества модулей выполнена с возможностью записывать данные передачи в заданный участок области передачи и имеет общий протокол передачи для совместного использования данных передачи между модулями.

Согласно другому объекту настоящего изобретения обеспечивается устройство контроля цифровой обработки, содержащее: множество модулей, каждый из которых включает в себя основную плату с установленными главной управляющей FPGA и управляющей FPGA для управления подплатой, соединенную с разъемом, и подплату обработки интерфейса «человек-машина»; и материнскую плату, соединенную с каждым из множества модулей, причем на каждой основной плате множества модулей установлено устройство хранения данных, хранящее информацию подплаты интерфейса «человек-машина».

Согласно еще одному объекту настоящего изобретения обеспечивается устройство контроля цифровой обработки, содержащее: множество модулей, каждый из которых включает в себя основную плату с установленной главной управляющей FPGA, соединенную с разъемом, и подплату обработки ввода-вывода с установленной FPGA обработки ввода-вывода и элементом ввода-вывода; и материнскую плату, соединенную с каждым из множества модулей, причем: на каждой подплате множества модулей установлено устройство хранения данных, хранящее информацию ввода-вывода, связанную с элементами, внешними для подплаты; и каждая FPGA множества модулей выполнена с возможностью записывать данные передачи в заданный участок области передачи и имеет общий протокол передачи для совместного использования данных передачи между модулями.

Согласно еще одному объекту настоящего изобретения обеспечивается устройство контроля цифровой обработки, содержащее: множество модулей, каждый из которых включает в себя основную плату с установленной главной управляющей FPGA, соединенную с разъемом, и подплату обработки ввода-вывода с установленной FPGA обработки ввода-вывода и элементом ввода-вывода; и материнскую плату, соединенную с каждым из множества модулей, причем: по меньшей мере на одной из подплат множества модулей установлен элемент ввода-вывода и не установлены FPGA, EPROM и EEPROM; главная управляющая FPGA основной платы модуля выполнена с возможностью выполнения процесса внешнего ввода-вывода; и каждая FPGA множества модулей записывает данные передачи в заданный участок области передачи и имеет общий протокол передачи для совместного использования данных передачи между модулями.

Преимущества изобретения

В соответствии с настоящим изобретением появляется возможность уменьшить количество типов необходимых плат благодаря универсальности плат, а также увеличить экономическую эффективность и упростить обслуживание.

Краткое описание чертежей

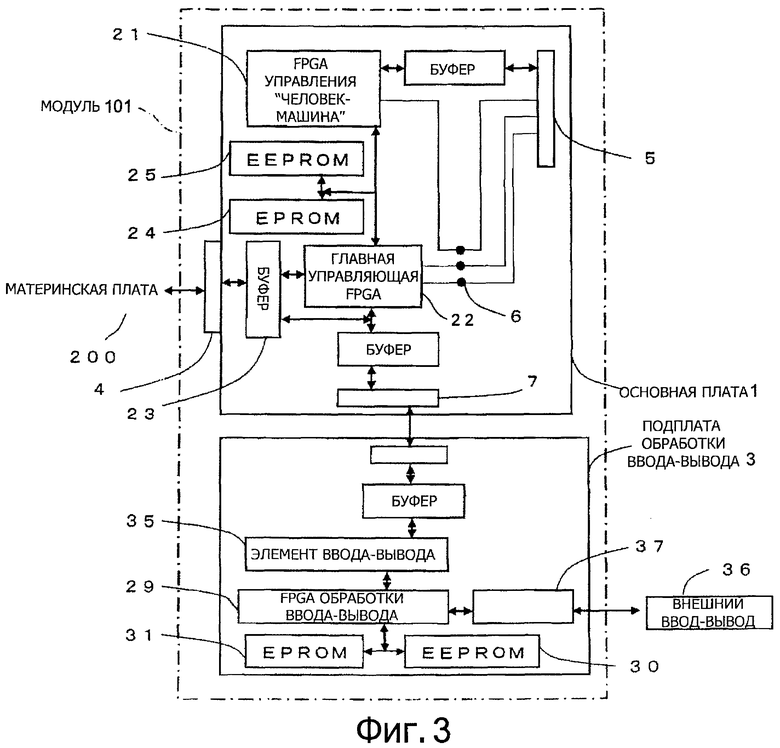

Фиг.1 - схема, показывающая конфигурацию устройства контроля цифровой обработки по первому варианту реализации настоящего изобретения.

Фиг.2 - схема, показывающая конфигурацию устройства контроля цифровой обработки, составленного из множества модулей.

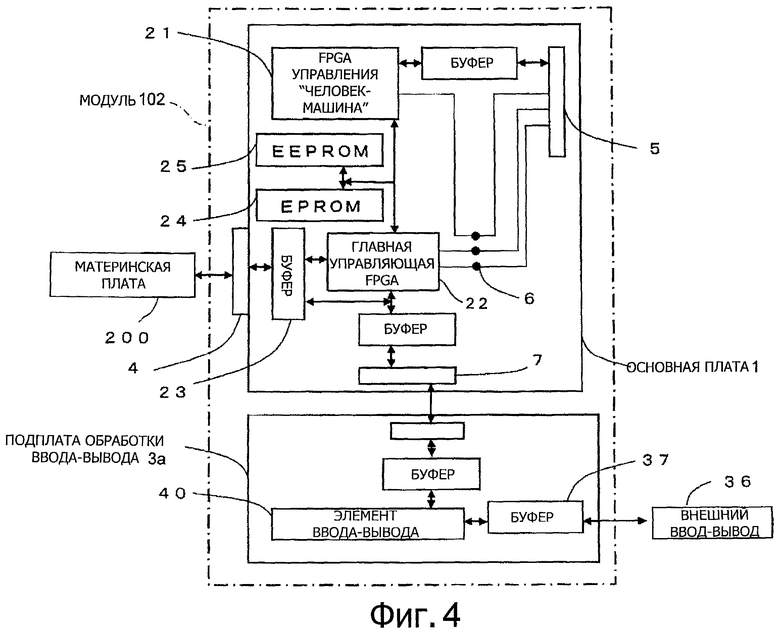

Фиг.3 - схема, показывающая конфигурацию устройства контроля цифровой обработки по четвертому варианту реализации настоящего изобретения.

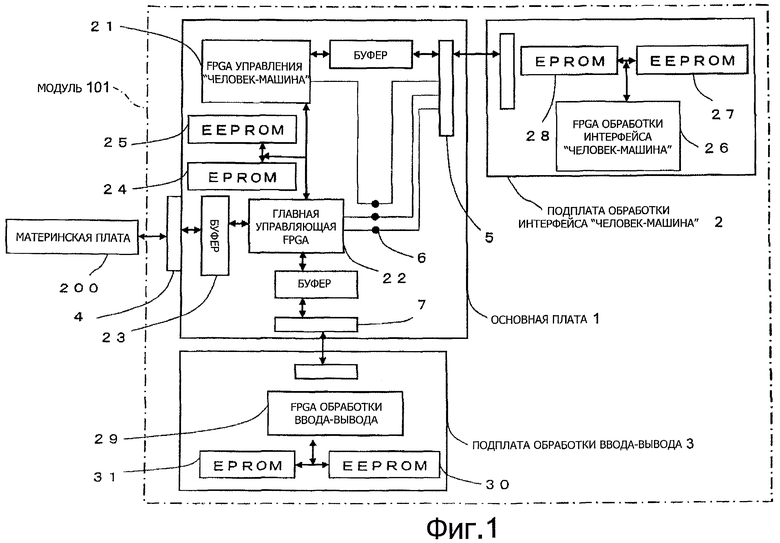

Фиг.4 - схема, показывающая конфигурацию устройства контроля цифровой обработки по пятому варианту реализации настоящего изобретения.

Подробное описание изобретения

Далее описано устройство контроля цифровой обработки согласно вариантам реализации настоящего изобретения со ссылками на сопроводительные чертежи. Одинаковые или похожие компоненты представлены одинаковыми ссылочными позициями и повторно не описываются.

Первый вариант реализации

Первый вариант реализации будет описан со ссылками на фиг.1 и 2.

В целом, как показано на фиг.2, устройство контроля, которое контролирует поток нейтронов в ядерном реакторе, состоит из множества модулей. Например, устройство контроля составлено из множества модулей, включающих в себя монитор диапазона средней мощности (APRM), которым служит модуль А, монитор диапазона локальной мощности (LPRM), которым служит модуль В, модуль ввода-вывода, которым служит модуль С, и т.д.

На фиг.1 показан пример конфигурации одного из модулей, модуля 101. Модуль 101 включает в себя основную плату 1, соединенную с разъемом 4, который соединен с материнской платой 200; подплату 2 обработки интерфейса «человек-машина», соединенную с основной платой 1 через интерфейс 5 соединения подплаты; подплату 3 обработки ввода-вывода, соединенную с основной платой 1 через интерфейс 7 соединения подплаты. Основная плата 1 и подплаты 2 и 3 соединяются через линии электропитания и линии передач.

Основная плата 1 включает в себя FPGA 21 управления «человек-машина», главную управляющую FPGA 22, буфер 23 внешнего интерфейса, EEPROM 24 (электрически стираемое программируемое ПЗУ) для сохранения параметров, которые могут изменяться, EPROM 25 (стираемое программируемое ПЗУ) для сохранения параметров, которые не меняются, например начальных данных, и т.д.

Аналогично подплата обработки интерфейса «человек-машина» снабжена FPGA 26 обработки интерфейса «человек-машина», EEPROM 27 и EPROM 28. Подплата 3 обработки ввода-вывода снабжена FPGA 29 обработки ввода-вывода, EEPROM 30 и EPROM 31.

Чтобы выполнять передачу между платами, каждая из FPGA 22, 26 и 29 выделяет области передачи, в которые записываются данные. Содержание областей передачи может быть разделено на следующие пять областей с (A1) по (A5).

(А1) Область данных для записи главного управления основной платы

(А2) Область данных для записи управления «человек-машина» основной платы

(A3) Область данных обработки интерфейса «человек-машина»

(А4) Область данных обработки ввода-вывода

(A5) Область данных для записи информации другого модуля

Так как содержание выделенных областей передачи используется совместно, каждая из FPGA 22, 26 и 29 делает ссылку на необходимые данные для выполнения обработки интерфейса «человек-машина» и обработки ввода-вывода.

Например, когда подплатой является подплата 2 обработки интерфейса «человек-машина», таблица, куда записываются данные, которыми обмениваются с подплатой 2, выполнена в соответствии со спецификацией ячеек памяти и регистров. Следующая информация интерфейса «человек-машина» приводится в таблице: используется или нет первый светодиод (не показан); используется или нет второй светодиод (не показан); светится первый светодиод или нет; светится второй светодиод или нет; используется или нет первый переключатель (не показан); используется или нет второй переключатель (не показан). Таким образом, становится возможным передавать данные в подобных форматах передачи на любую подплату, даже если она отличается количеством светодиодов и переключателей. Таким же способом могут быть переданы данные, даже если они являются последовательными или параллельными данными.

Даже когда подплатой является подплата 3 обработки ввода-вывода, канал выделяется аналогично. И даже если подплаты различаются количеством цифровых входов/выходов и т.п., возможность передачи остается.

Согласно настоящему первому варианту реализации на основной плате 1, подплате 2 обработки интерфейса «человек-машина» и подплате 3 обработки ввода-вывода установлены FPGA. Каждая FPGA выделяет области передачи, в которые записываются данные. Содержание выделенных областей передачи используется совместно. Таким образом, каждая FPGA имеет возможность выполнять обработку интерфейса «человек-машина» и обработку ввода-вывода, ссылаясь на необходимые данные. В результате, даже если конфигурация подплаты меняется, существует возможность реализовать модуль ввода-вывода и модуль интерфейса «человек-машина» для внешней части, которая поддерживает изменения.

Например, процесс передачи/отображения на подплате 2 обработки интерфейса «человек-машина» выполняется на основе EPROM (или EEPROM) подплаты, которая хранит информацию интерфейса «человек-машина», такую как статус использования переключателей подплаты 2 и статус отображения светодиодов. Таким образом, процесс, выполняемый FPGA подплаты 2, однозначно определен и универсальность плат с 1 по 3 дополнительно улучшается. В результате, даже если в модуле произойдет сбой, можно быстро провести операции обслуживания, ремонта и проверки, например замену плат, так как платы очень универсальны.

Модуль 101 в настоящем первом варианте реализации включает в себя основную плату 1, подплату 2 обработки интерфейса «человек-машина» и подплату 3 обработки ввода-вывода. Однако подплата 3 обработки ввода-вывода не является обязательной. Таким образом, модуль может быть составлен из основной платы 1 и подплаты 2 обработки интерфейса «человек-машина». Даже в этом случае будут получены результаты, описанные выше.

Второй вариант реализации

Согласно вышеописанному первому варианту реализации FPGA установлены на каждой из плат с 1 по 3. Согласно второму варианту реализации FPGA не установлены на подплаты 2 или 3, а только на основную плату 1 (не показано). В данном случае, например, процесс передачи/отображения на подплате 2 обработки интерфейса «человек-машина» выполняется на основе EPROM (или EEPROM) основной платы, которая хранит информацию интерфейса «человек-машина», такую как статус использования переключателей или светодиодов подплаты 2. Согласно второму варианту реализации обработка посредством FPGA основной платы 1 однозначно определена и универсальность основной платы и подплат дополнительно повышается.

Третий вариант реализации

Согласно третьему варианту реализации обеспечивается диагностическая подплата (не показана) для подтверждения и захвата состояния основной платы 1 и информации внутри области передачи данных. Для этого, как показано на фиг.1, тестовые штекеры 6 соединены с FPGA 21 и 22 основной платы 1, которые передают информацию о состоянии основной платы 1 и информацию внутри области передачи данных на диагностическую подплату через интерфейс 5 соединения подплаты.

Согласно третьему варианту реализации становится возможным захватить состояние подплаты ввода-вывода и других модулей на основе состояния основной платы 1 и информации внутри области передачи данных, делая возможным выполнение диагностики каждой платы внутри модуля.

Четвертый вариант реализации

Четвертый вариант реализации будет описан со ссылкой на фиг.3.

В модуле 101, показанном на фиг.3, FPGA 29 обработки ввода-вывода подплаты 3 хранит состояние внешнего входного сигнала, который был принят элементом 35 ввода-вывода подплаты 3, и сообщает FPGA 22 основной платы 1 входное состояние (процесс ввода извне). Основная плата 1 передает информацию о внешнем выходном запросе на подплату 3. В FPGA 29 обработки ввода-вывода на подплате 3 обработка сигнала выполняется для вывода вовне (процесс вывода вовне). Основная плата 1 и подплата 3 соединены между собой множеством сигнальных линий для передачи информации.

В случае контактного входного сигнала:

Модуль реализован так, что: на подплате обработки ввода-вывода, для сигналов от внешнего ввода-вывода 36 (например, контактных входных сигналов множества каналов), входное состояние контакта обнаруживается в FPGA 29 обработки ввода-вывода через буфер 37 и элемент 35 ввода-вывода (где установлено множество оптронных соединителей); входное состояние контакта передается на основную плату 1, используя параллельные сигналы или битовую последовательность ON/OFF последовательных сигналов; обработка сигналов выполняется в главной управляющей FPGA 22.

В случае контактного выходного сигнала:

Для осуществления контактного выхода внешнего ввода-вывода 36, который, например, является множеством каналов, модуль реализован так, что: запрос от FPGA 22 основной платы 1 принимается FPGA 29 обработки ввода-вывода подплаты 3 (используя параллельные или последовательные сигналы); контактный вывод выполняется вовне через элемент 35 ввода-вывода (на котором установлено множество реле PhotoMOS) и буфер.

В случае аналогового входного сигнала (1):

Когда поступает внешний сигнал ввода-вывода, который, например, является электрическим током, модуль реализован так, что: с помощью FPGA 29 обработки ввода-вывода подплаты 3, выполненной с функцией аналого-цифрового преобразования, оцифрованные входные данные передаются на основную плату 1 (входной уровень передается параллельными и последовательными сигналами); обработка сигнала выполняется в главной управляющей FPGA 22.

В случае аналогового входного сигнала (2):

В описанном выше аналоговом входном сигнале (1) модуль реализуется так, что: с помощью элемента аналого-цифрового преобразования, установленного в элементе 35 ввода-вывода, оцифрованные данные принимаются FPGA 29 обработки ввода-вывода на подплате 3 и передаются на основную плату 1; обработка сигналов выполняется главной управляющей FPGA 22.

В случае аналогового выходного сигнала (1):

Модуль реализуется так, что: в ответ на запрос от основной платы 1 FPGA 29 обработки ввода-вывода подплата 3 выполнена с функцией цифроаналогового преобразования, и аналоговый вывод производится вовне.

В случае аналогового выходного сигнала (2):

В описанном выше аналоговом выходном сигнале (1) модуль реализуется так, что: с помощью элемента цифроаналогового преобразования, установленного в элементе 35 ввода-вывода, аналоговый вывод производится от FPGA 29 обработки ввода-вывода на подплате 3 через цифроаналоговый преобразователь и буфер в ответ на запрос от основной платы 1.

В случае ввода/вывода внешней передачи (например, RS488):

Модуль реализован так, что когда последовательные сигналы данных поступают на внешний ввод-вывод 36, FPGA 29 обработки ввода-вывода подплаты 3 выполнена с функцией обработки сигнального интерфейса основной платы 1 и производится обработка ввода-вывода передачи внешнего ввода-вывода.

Также возможна реализация модуля, имеющего множество функций ввода-вывода в FPGA 29 обработки ввода-вывода, где множество упомянутых функций внешнего ввода-вывода выполнены в соответствии с таблицей набора функций в EPROM 31 или EEPROM 30.

В связи с вышесказанным согласно настоящему варианту реализации FPGA 21 управления «человек-машина» на фиг.3 не является обязательной.

Пятый вариант реализации

Пятый вариант реализации будет описан со ссылкой на фиг.4.

В модуле 102 настоящего варианта реализации элемент 40 ввода-вывода установлен вместо FPGA 29 на подплате 3 по четвертому варианту реализации; главная управляющая FPGA 22 на основной плате 1 выполнена с функцией обработки данных. Подобным образом реализуется модуль ввода-вывода.

В случае контактного входа (оптронный соединитель установлен в качестве элемента 40 ввода-вывода):

Оптронный соединитель установлен в элементе 40 ввода-вывода подплаты 3а. Числовая обработка входного сигнала от оптронного соединителя выполняется в FPGA 22 основной платы 1. Таким образом, возможна реализация модуля, выполняющего обработку ввода от внешних контактов.

В случае контактного выхода (реле PhotoMOS установлено в качестве элемента 40 ввода-вывода):

Реле PhotoMOS установлено в элемент 40 ввода-вывода подплаты 3а. FPGA 22 основной платы 1 выполнена с функцией, позволяющей реле PhotoMOS выполнять контактный вывод. Таким образом, возможна реализация модуля, выполняющего вывод на внешние контакты.

Аналоговый вход (элемент аналого-цифрового преобразования установлен в качестве элемента 40 ввода-вывода):

Элемент аналого-цифрового преобразования установлен в элементе 40 ввода-вывода подплаты 3а. FPGA 22 основной платы 1 выполнена с функцией обработки входных данных от элемента аналого-цифрового преобразования. Таким образом, возможна реализация модуля аналогового ввода.

Аналоговый выход (элемент цифроаналогового преобразования установлен в качестве элемента 40 ввода-вывода):

Элемент цифроаналогового преобразования установлен в качестве элемента 40 ввода-вывода подплаты 3а. FPGA 22 основной платы 1 выполнена с функцией, выполняющей вывод выходных данных на элемент цифроаналогового преобразования. Таким образом, возможна реализация модуля аналогового вывода.

Внешняя передача (например, RS488) (элемент RS485 обработки передачи установлен в качестве элемента 40 ввода-вывода):

Элемент RS485 обработки передачи установлен в качестве элемента 40 ввода-вывода подплаты 3а. FPGA 22 основной платы 1 выполнена с функцией обработки данных входных/выходных данных передачи. Таким образом, возможна реализация модуля внешней передачи.

В связи с вышесказанным согласно данному варианту реализации FPGA 21 управления человек-машина на фиг.4 не является обязательной.

Список номеров ссылочных позиций

1: Основная плата

2: Подплата обработки интерфейса «человек-машина»

3, 3а: Подплата обработки ввода-вывода

4: Разъем

5, 7: Интерфейс соединения подплаты

6: Тестовые штекеры

21: FPGA управления «человек-машина»

22: Главная управляющая FPGA

23: Буфер внешнего интерфейса

24: EEPROM

25: EPROM

26: FPGA обработки интерфейса «человек-машина»

27: EEPROM

28: EPROM

29: FPGA обработки ввода-вывода

30: EEPROM

31: EPROM

35: Элемент ввода-вывода

36: Внешний ввод-вывод

37: Буфер

40: Элемент ввода-вывода

101, 102: Модуль

200: Материнская плата

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПОНОВКА СХЕМЫ ДЛЯ КИП-СИСТЕМЫ БЕЗОПАСНОСТИ | 2015 |

|

RU2703221C2 |

| СРЕДСТВО МАРШРУТИЗАЦИИ ДЛЯ ПОДВОДНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2006 |

|

RU2427963C2 |

| СИСТЕМА КОМПЛЕКСНОГО МОНИТОРИНГА КЛИМАТА | 2022 |

|

RU2787073C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ СОЕДИНЕНИЯ С ВОЗМОЖНОСТЬЮ ПЕРЕДАЧИ ДАННЫХ ПОЛЕВЫХ УСТРОЙСТВ С УДАЛЕННЫМ ТЕРМИНАЛЬНЫМ БЛОКОМ | 2017 |

|

RU2743506C2 |

| БОРТОВАЯ ИНФОРМАЦИОННАЯ СИСТЕМА | 2009 |

|

RU2402439C1 |

| СИСТЕМА И СПОСОБ УПРАВЛЕНИЯ ПРОГРАММИРУЕМЫМ МУЛЬТИМЕДИЙНЫМ КОНТРОЛЛЕРОМ | 2006 |

|

RU2483461C2 |

| ПЕРЕНОСНОЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2007 |

|

RU2340926C1 |

| СРЕДСТВО МАРШРУТИЗАЦИИ ДЛЯ ПОДВОДНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2006 |

|

RU2419229C2 |

| Система управления машиной блочно-модульного построения | 2023 |

|

RU2801738C1 |

| УСТРОЙСТВА, СИСТЕМЫ И СПОСОБЫ, ОТНОСЯЩИЕСЯ К PLC | 2007 |

|

RU2419826C2 |

Изобретение относится к устройству контроля цифровой обработки. Техническим результатом является расширение функциональных возможностей контроля и цифровой обработки данных, за счет использования FPGA технологии. Устройство цифровой обработки и контроля включает в себя множество модулей и материнскую плату, соединенную с каждым модулем. Каждый модуль включает в себя: основную плату, соединенную с разъемом и имеющую установленные на ней FPGA для главного управления и FPGA для управления подплатой, подплату для обработки интерфейса «человек-машина» и установленную на ней FPGA для обработки интерфейса. Каждая подплата имеет устройства хранения данных для хранения информации подплаты об интерфейсе «человек-машина». Каждая из FPGA записывает данные передачи в заданные участки области передачи и имеет общий протокол передачи для совместного использования данных передачи между соответствующими модулями. 4 н. и 1 з.п. ф-лы, 4 ил.

1. Устройство контроля цифровой обработки, содержащее:

множество модулей, каждый из которых включает в себя соединенную с разъемом основную плату с главной управляющей FPGA и FPGA для управления подплатой и подплату обработки интерфейса «человек-машина» с FPGA обработки интерфейса; и

материнскую плату, соединенную с каждым из множества модулей, при этом на каждой подплате множества модулей установлено устройство хранения данных, хранящее информацию подплаты об интерфейсе «человек-машина»;

каждая FPGA множества модулей выполнена с возможностью записывать данные передачи в заданный участок области передачи и имеет общий протокол передачи для совместного использования данных передачи между модулями.

2. Устройство контроля цифровой обработки, содержащее:

множество модулей, каждый из которых включает в себя соединенную с разъемом основную плату с главной управляющей FPGA и FPGA для управления подплатой и подплату обработки интерфейса «человек-машина»; и материнскую плату, соединенную с каждым из множества модулей, при этом на каждой основной плате множества модулей установлено устройство хранения данных, хранящее информацию подплаты об интерфейсе «человек-машина».

3. Устройство контроля цифровой обработки, содержащее:

множество модулей, каждый из которых включает в себя соединенную с разъемом основную плату с главной управляющей FPGA и подплату обработки ввода-вывода с FPGA обработки ввода-вывода и элементом ввода-вывода; и

материнскую плату, соединенную с каждым из множества модулей, при этом:

на каждой подплате множества модулей установлено устройство хранения данных, хранящее информацию ввода-вывода, связанную с элементом, внешним для подплаты;

каждая FPGA множества модулей выполнена с возможностью записывать данные передачи в заданный участок области передачи и имеет общий протокол передачи для совместного использования данных передачи между модулями.

4. Устройство контроля цифровой обработки, содержащее:

множество модулей, каждый из которых включает в себя соединенную с разъемом основную плату с главной управляющей FPGA и подплату обработки ввода-вывода с FPGA обработки ввода-вывода и элементом ввода-вывода; и

материнскую плату, соединенную с каждым из множества модулей, при этом по меньшей мере на одной из подплат множества модулей установлен элемент ввода-вывода и не установлены FPGA, EPROM и EEPROM;

главная управляющая FPGA основной платы модуля выполнена с возможностью выполнения процесса внешнего ввода-вывода;

каждая FPGA множества модулей выполнена с возможностью записывать данные передачи в заданный участок области передачи и имеет общий протокол передачи для совместного использования данных передачи между модулями.

5. Устройство контроля цифровой обработки по любому из пп.1-4, дополнительно содержащее подплату диагностики, подключаемую и отсоединяемую от FPGA основной платы по меньшей мере одного из множества модулей, и выполненную с возможностью при подключении выполнять диагностику после приема информации о состоянии основной платы и информации внутри области передачи данных.

| Режущий аппарат для косилок, жаток и других уборочных машин | 1945 |

|

SU66644A1 |

| US 2006237835 A1, 26.10.2006 | |||

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| US 2008028187 A1, 31.01.2008. | |||

Авторы

Даты

2012-03-20—Публикация

2009-06-01—Подача